- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Best practice for K8x QSPI Dual-Quad Address Ranges

Best practice for K8x QSPI Dual-Quad Address Ranges

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Best practice for K8x QSPI Dual-Quad Address Ranges

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Though I'd share...

The K8x QSPI peripheral can accept one or two QSPI flash devices, or a dual-die device (which is really only two identical flash dies and one chip). Each can have a maximum size of 64MB.

In some NXP K8x QSPI peripheral examples the second die address range starts where the first ends. So for example:

2x 32MB dies would have:

Bank-A: 0x68000000-0x69FFFFFF

Bank-B: 0x6A000000-0x6BFFFFFF

and 2x 16MB dies would have:

Bank-A: 0x68000000-0x68FFFFFF

Bank-B: 0x69000000-0x69FFFFFF

This arrangement is no longer ideal with the latest Segger Flasher-ARM/J-Flash.

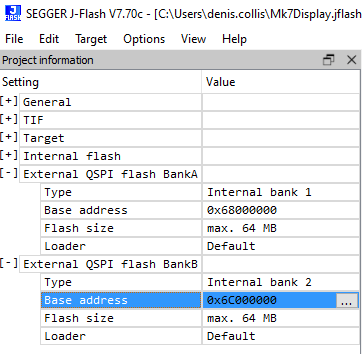

In earlier J-Flash versions (many moons ago) I recall the ability to change these addresses, but this is no longer allowed. Instead, the full 64MB is always allocated for each bank, and it cannot be changed.

Bank-A now always starts at 0x68000000 and Bank-B always starts at 0x6C000000 and it then follows that in the examples above:

2x 32MB dies should have:

Bank-A: 0x68000000-0x69FFFFFF

Bank-B: 0x6C000000-0x6DFFFFFF

and 2x 16MB dies should have:

Bank-A: 0x68000000-0x68FFFFFF

Bank-B: 0x6C000000-0x6CFFFFFF

...which seems to be the best-practice is you want successful production programming of your products.

Cheers!

Denis