- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 製品フォーラム

- :

- デジタルシグナルコントローラ

- :

- Signal Timing for SC18IS600IPW/S8

Signal Timing for SC18IS600IPW/S8

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Signal Timing for SC18IS600IPW/S8

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello All,

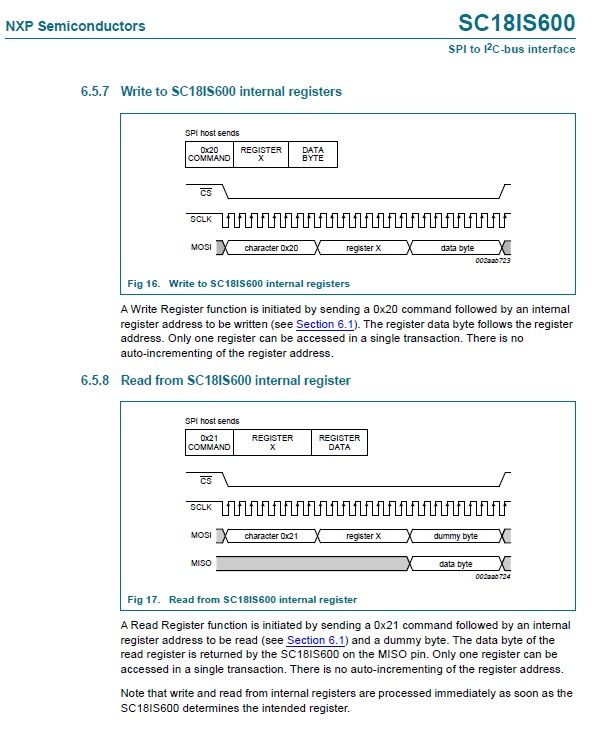

Our team is wanting to confirm the command method for read/write commands for the internal registers. When sending the Write and Read commands, the MISO appears to be shifted one byte to the right when compared to the MOSI. Could this be something to do with MSB first or LSB first, or possibly something else causing this?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jonathan,

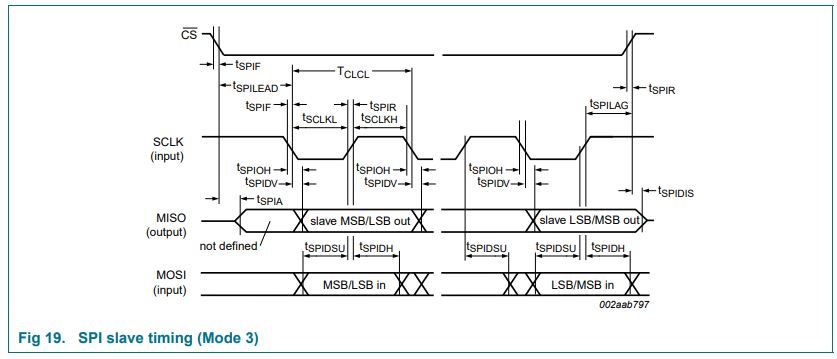

Please make sure you are using SPI Mode 3. This means that the SCLK signal should be idle high and data is clocked in and out on the rising clock edge.

Best regards,

Tomas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Tomas,

Thank you very much for your response. We still were not able to get it to work even after checking that we were using SPI Mode 3. We also tried putting a minimum of 8 uS (Tspiclkw) between each byte as suggested by MikeThompson in the following post, but the echoed data did not change :

Do you have any other suggestions to try looking into that might be causing the echoed data that is 1 byte shifted to the right?

Best Regards,

Jonathan

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello JonDen

I'm so glad to see that I'm not the only one facing this issue ! when i read to verify the value of the internal registers the last bit of data is always "0".

For example, I'm writing 0xFF to the IOConfig register but when i read the value its 0xFE or writing to the same register 0X01 reading 0x00.

To verify that the problem is in the read function and not the write function i set GPIO0 to low-> high-> low and i can see it changes.

Using:

FTDI: FT4232HL

SPI mode:3

Clock frequency:100Khz

Did you buy any change managed to solve this ?