- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- 製品フォーラム

- :

- デジタルシグナルコントローラ

- :

- How to use PTN3460I slave mode

How to use PTN3460I slave mode

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I want to bridge the video of the Host PC from PTN3460I to DP to LVDS and display it on the LCD with a resolution of 1920x1080.

We are aware that there are two ways to set DPCD, especially EDID from Display Port.

Depending on the level of DEV_CFG, the I2C setting of PTN3460I can be selected as master (MSBus) or slave (DDCBus).

1. DEV_CFG: Read EDID from HIGH → AUX via I2C from the external EEPROM of PTN3460I.

2. DEV_CFG: LOW → Read EDID from the built-in flash of PTN3460I via SRAM after reset release.

I would like to set it to DEV_CFG: LOW and use the default EDID 4 of the built-in flash, but the host PC will recognize it as a resolution of 800x480.

Question

-----------------------------------------

Q1 Why is it recognized as a resolution of 800x480?

Q2 Is it okay to set the MsBus at any time?

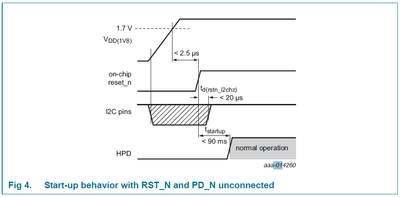

Does it have anything to do with the 90ms period from when RST_N and PD_N become High until HPD is output?

External terminal setting

DEV_CFG: L

CFG1: H

CFG2: L

CFG3: L

CFG4: L

Configuration register settings

Reg 0x80: 0x0B

Reg 0x84: 0x09

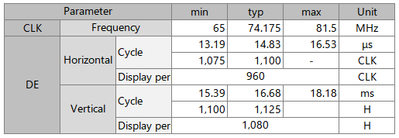

LCD Timing characteristics

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Q1 Why is it recognized as a resolution of 800x480?

[r]:You can try to verify EDID4 content by IIC.

Q2 Is it okay to set the MsBus at any time?

[r]PTN3460I I2C pins are not failsafe and cannot be connected to the SMBus if the

SMBus has active communications during VDD33 supply switch ON. In the application

there MUST be no MS_I2C traffic during supply rise-up

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Q1 Why is it recognized as a resolution of 800x480?

[r]:You can try to verify EDID4 content by IIC.

Q2 Is it okay to set the MsBus at any time?

[r]PTN3460I I2C pins are not failsafe and cannot be connected to the SMBus if the

SMBus has active communications during VDD33 supply switch ON. In the application

there MUST be no MS_I2C traffic during supply rise-up

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

"during VDD33 supply switch ON" is the recognition after tstsrtup.

When communication was performed from SMBus after this period, it was possible to write to the register and it could be recognized by the Host PC at 1920x1080 pixels.

However, the liquid crystal has not been able to display anything yet.

When I checked the EDID reading result of the HostPC, the contents of the default EDID No. 4 were read normally.

Does this mean that EDID No 4 does not match the EDID required for my LCD?

Or is it because there is something missing in the settings in the configuration register?

Register setting (default value is adopted if not described)

|Offset| Value|

| 0x8F| 0x0C| /* PWM default bitcount:12 */

| 0x92| 0x1E| /* PWM default freq:30 */

| 0x90| 0x70| /* Register 0x90 0x91: PWM value registers */

| 0x91| 0xFF| /* Write PWM value 0x07FF to register 0x90, 0x91 */

| 0x81| 0x0B| /* Set dual LVDS channel, VESA 24 bpp (bit per pixel) */

| 0x84| 0x09| /* Emulated EDID selection:4, emulation ON, EDID is read from internal flash */

Best regards,

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Firstly I think you need confirm your LCD suit for EDID4 configuration(1920 x 1080 @60Hz) or not.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you for helping.

It is solved.

Revised the LCD timing Power On sequence.