- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 製品フォーラム

- :

- ColdFire/68Kマイクロコントローラとプロセッサ

- :

- MCF52254 internal pull-up default state

MCF52254 internal pull-up default state

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Team,

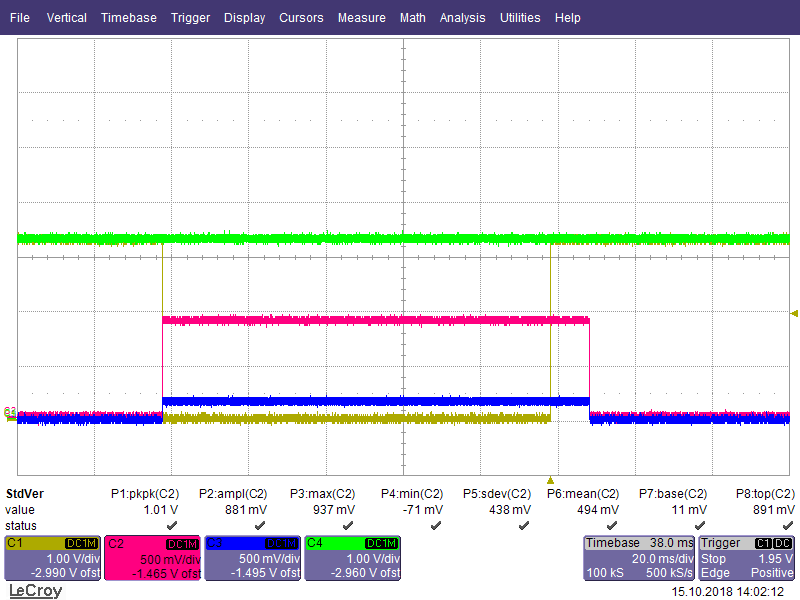

One of our project uses MCF52254 PTA2 pin as a PWM output to control the LCD back light, every time when powered up, there is a short pulse at the pin, this will cause a flicker of the back light. I probed the signals, I supposed the pulse is caused by internal pull up.

C1: Reset pin

C2: PTA2(PWM pin)

C3: Another PWM pin with lower pull down resistor

C4: 3.3V MCU supply

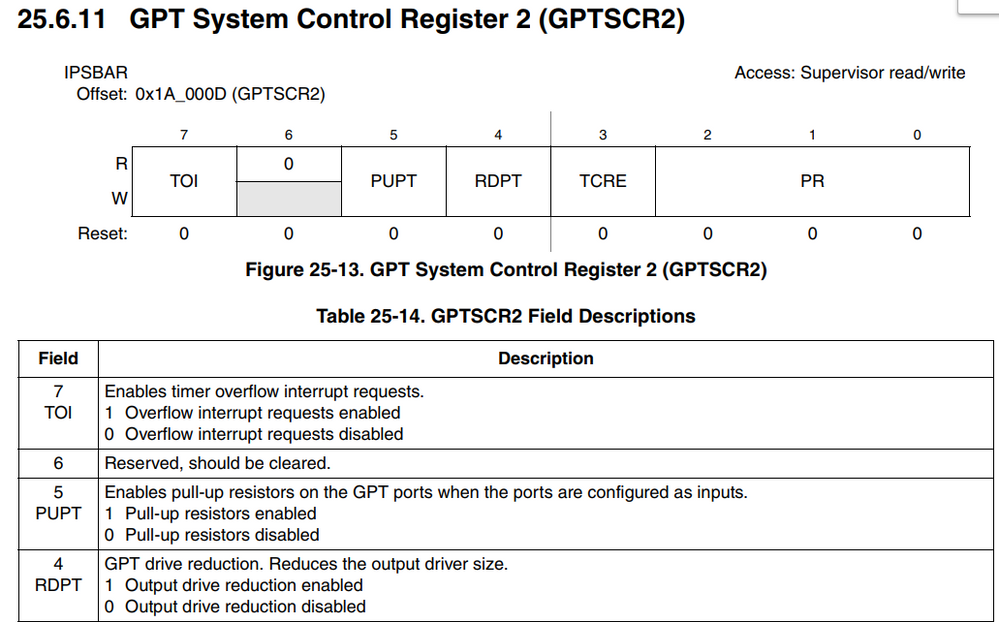

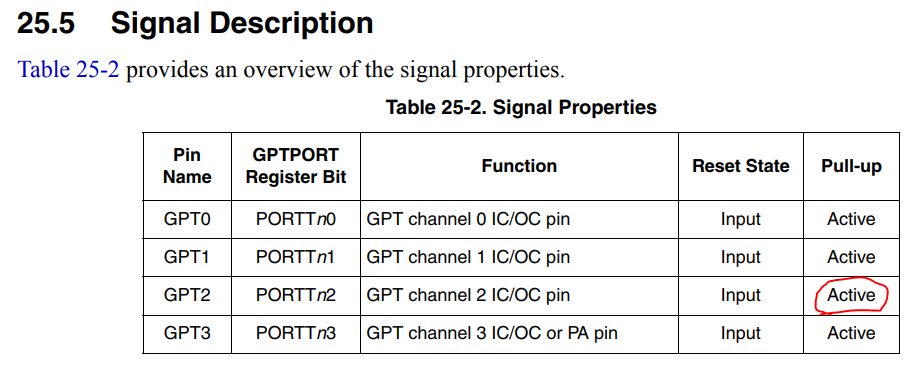

I checked the manual, it says the initial state of pull-up is disabled:

But another table in the manual says the initial state of the pull-up is enabled:

So, what is the exat state of the internal pull-up during power up? How can we disable the internal pull up?

Thanks and regards!

Wesley Xu

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

This is pin J10 on the 14 pin MAPBGA. It has the functions "GPT2/PWM5/PTA2". The pin name in Figure 15.1 is "ICOC[2] / PTA[2] / PWM5", with "ICOC being "IC/OC" elsewhere. Its function is controlled by PTAPAR. This defaults to ZERO on Reset, which selects GPT2. This is detailed in "Table 2-1. Pin Functions by Primary and Alternate Purpose".

The power-up state of the GPTs are detailed in the sections you've found, and it says the reset state of that bit should be "disabled" when the GPT has the pin. But the reset state of PTPAR is "00" and than means GPIO.

There's also "Note 2" and "Note 8" on the entry in Table 2.1. "Note 2" says GPIOs have pullups. "Note 8" says the GPT module controls the pullup when it is in charge. But it resets as a GPIO.

Therefore the reset state of that pin (and all pins that are GPIOs) is high. That's just what the chip does. Your hardware design either has to treat the reset state (which is "high") as the "Inactive State", or you have to add a pulldown on that pin. So add an inverter or a pulldown. There's no other way, unless you want to build a resistor/capacitor/diode circuit to force the PWM off for 20ms or more after reset.

> How can we disable the internal pull up?

You can't.

> however it will been default to GPIO (PTA2) after reset if not configured as primary function(GPT2).

> So for your case, please make sure if you had set the GPT function correctly.( By Pin Assignment Registers).

It will unconditionally default to GPIO. It doesn't matter if it was configured for PWM before the reset, it is going to be GPIO during and after until the code can get around to changing it. Which by the trace takes about 10ms. The assignment can't be changed by anything DURING Reset. So the backlight flashes on for the 100ms Reset time plus the 10ms code time.

Tom

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I am pretty sure that the manual has a little confused. Let me try to clarify.

First, most of the pins associated with the external interface may be used for several different functions. When

not used for their primary function, many of the pins may be used as general-purpose digital I/O pins. The PAT2 pin primary function is GPT signal, however it will been default to GPIO (PTA2) after reset if not configured as primary function(GPT2).

All GPIO function will have internal pull-up enabled at reset. So for your case, please make sure if you had set the GPT function correctly.( By Pin Assignment Registers).

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

This is pin J10 on the 14 pin MAPBGA. It has the functions "GPT2/PWM5/PTA2". The pin name in Figure 15.1 is "ICOC[2] / PTA[2] / PWM5", with "ICOC being "IC/OC" elsewhere. Its function is controlled by PTAPAR. This defaults to ZERO on Reset, which selects GPT2. This is detailed in "Table 2-1. Pin Functions by Primary and Alternate Purpose".

The power-up state of the GPTs are detailed in the sections you've found, and it says the reset state of that bit should be "disabled" when the GPT has the pin. But the reset state of PTPAR is "00" and than means GPIO.

There's also "Note 2" and "Note 8" on the entry in Table 2.1. "Note 2" says GPIOs have pullups. "Note 8" says the GPT module controls the pullup when it is in charge. But it resets as a GPIO.

Therefore the reset state of that pin (and all pins that are GPIOs) is high. That's just what the chip does. Your hardware design either has to treat the reset state (which is "high") as the "Inactive State", or you have to add a pulldown on that pin. So add an inverter or a pulldown. There's no other way, unless you want to build a resistor/capacitor/diode circuit to force the PWM off for 20ms or more after reset.

> How can we disable the internal pull up?

You can't.

> however it will been default to GPIO (PTA2) after reset if not configured as primary function(GPT2).

> So for your case, please make sure if you had set the GPT function correctly.( By Pin Assignment Registers).

It will unconditionally default to GPIO. It doesn't matter if it was configured for PWM before the reset, it is going to be GPIO during and after until the code can get around to changing it. Which by the trace takes about 10ms. The assignment can't be changed by anything DURING Reset. So the backlight flashes on for the 100ms Reset time plus the 10ms code time.

Tom