- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- CodeWarrior

- :

- QorIQ用CodeWarrior

- :

- Re: U-boot NOR Flash

U-boot NOR Flash

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

U-boot NOR Flash

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi All,

I am using T4240RDB-64B machine with codeWarrior Flashprogrammer V10.7. And I got the following log when flash the u-boot. I want to give restricted address range for program.

How to find the flash start address and end address for u-boot to t4240rdb-64b machine.

Flash Log:

l::target -lc "Peacock_10thDec-core00_RAM_T4160_Connect"

fl::target -b 0x0 0x100000

fl::target -v off -l off

cmdwin::fl::device -d "S29GL01GP" -o "128Mx8x1" -a 0xe8000000 0xefffffff

cmdwin::fl::erase all

Beginning Operation ...

-------------------------

Performing target initialization ...

Downloading Flash Device Driver ...

Reading flash ID ...

Erasing entire flash ...

Erasing ...

Erase Command Succeeded

fl::target -lc "Peacock_10thDec-core00_RAM_T4160_Connect"

fl::target -b 0x0 0x100000

fl::target -v off -l off

cmdwin::fl::device -d "S29GL01GP" -o "128Mx8x1" -a 0xe8000000 0xefffffff

cmdwin::fl::erase all

Beginning Operation ...

-------------------------

Performing target initialization ...

Downloading Flash Device Driver ...

Reading flash ID ...

Erasing entire flash ...

Erasing ...

Erase Command Succeeded

cmdwin::fl::image -f "C:\\Logi\\Work\\Projects\\BEL\\QorIQ_VPX\\Software\\T4160\\Zumi Solutions\\Uboot images\\181213\\u-boot-nor-2016.01+fslgit-r0.bin" -t "Auto Detect" -re off -oe on -o 0xe8000000

cmdwin::fl::erase image

Beginning Operation ...

-------------------------

Auto-detection is successful.

File is of type Binary/Raw Format.

Downloading Flash Device Driver ...

Reading flash ID ...

Erasing Sector 0xE8000000 to 0xE801FFFF

Erasing Sector 0xE8020000 to 0xE803FFFF

Erasing Sector 0xE8040000 to 0xE805FFFF

Erasing Sector 0xE8060000 to 0xE807FFFF

Erasing Sector 0xE8080000 to 0xE809FFFF

Erasing Sector 0xE80A0000 to 0xE80BFFFF

Erasing ...

Erase Command Succeeded

cmdwin::fl::write

-------------------------

Programming file C:\Logi\Work\Projects\BEL\QorIQ_VPX\Software\T4160\Zumi Solutions\Uboot images\181213\u-boot-nor-2016.01+fslgit-r

0.bin

Auto-detection is successful.

File is of type Binary/Raw Format.

Downloading Flash Device Driver ...

Reading flash ID ...

Auto-detection is successful.

File is of type Binary/Raw Format.

Downloading 0x00010000 bytes to be programmed at 0xE8000000

Downloading 0x00010000 bytes to be programmed at 0xE8010000

Downloading 0x00010000 bytes to be programmed at 0xE8020000

Downloading 0x00010000 bytes to be programmed at 0xE8030000

Downloading 0x00010000 bytes to be programmed at 0xE8040000

Downloading 0x00010000 bytes to be programmed at 0xE8050000

Downloading 0x00010000 bytes to be programmed at 0xE8060000

Downloading 0x00010000 bytes to be programmed at 0xE8070000

Downloading 0x00010000 bytes to be programmed at 0xE8080000

Downloading 0x00010000 bytes to be programmed at 0xE8090000

Downloading 0x00010000 bytes to be programmed at 0xE80A0000

Downloading 0x00010000 bytes to be programmed at 0xE80B0000

Executing program ....

Executing program .....

Executing program ......

Executing program .......

Executing program ........

Executing program .........

Executing program ..........

Executing program ...........

Executing program ............

Executing program .............

Executing program ..............

Executing program ...............

Executing program ................

Executing program .................

Executing program ..................

Executing program ...................

Executing program ....................

Executing program .....................

Executing program ......................

Executing program .......................

Executing program ........................

Executing program .........................

Executing program ..........................

Executing program ...........................

Executing program ............................

Executing program .............................

Executing program ..............................

Executing program ...............................

Executing program ................................

Executing program .................................

Executing program ..................................

Executing program ...................................

Executing program ....................................

Executing program .....................................

Executing program ......................................

Executing program .......................................

Executing program ........................................

Executing program .........................................

Executing program ..........................................

Executing program ...........................................

Executing program ............................................

Executing program .............................................

Executing program ..............................................

Executing program ...............................................

Executing program ................................................

Executing program .................................................

Executing program ..................................................

Executing program ...................................................

Executing program ....................................................

Executing program .....................................................

Executing program ......................................................

Executing program .......................................................

Executing program ........................................................

Executing program .........................................................

Executing program ..........................................................

Executing program ...........................................................

Executing program ............................................................

Executing program .............................................................

Executing program ..............................................................

Executing program ...

Executing program ....

Executing program .....

Executing program ......

Executing program .......

Executing program ........

Executing program .........

Executing program ..........

Executing program ...........

Executing program ............

Executing program .............

Executing program ..............

Executing program ...............

Executing program ................

Executing program .................

Executing program ..................

Executing program ...................

Executing program ....................

Executing program .....................

Executing program ......................

Executing program .......................

Executing program ........................

Executing program .........................

Executing program ..........................

Executing program ...........................

Executing program ............................

Executing program .............................

Executing program ..............................

Executing program ...............................

Executing program ................................

Executing program .................................

Executing program ..................................

Executing program ...................................

Executing program ....................................

Thank you for all your support ....!

Regards,

VinothS

Vinothkumar Sekar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Look at the Table 110 of SDK 2.0 -1703 documentation:

https://www.nxp.com/docs/en/supporting-information/QORIQ-SDK-2.0-IC-REV0.pdf

This Table shows NOR Flash memory map for SDK 2.0.

Have a great day,

Pavel Chubakov

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Pavel,

Thank you for your response.

I followed table 110 for memory map and I used the "0xEFF40000 to 0xEFFFFFFF" for uboot erase and program action.

But, still I got Sector Protection Error.

Please give some more details to fix the following errors,

Error: Erase failed. Flash driver reports the following error(s): Sector Protection Error

Error: Erase failed. Flash driver reports the following error(s): Sector Protection Error

Thanks & Regards,

VinothS

Vinothkumar Sekar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Pavel,

Any Update ?

Still I struggled in same place.

Regards, VinothS

Vinothkumar Sekar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Vinothkumar,

I am using p2020 RDB and i got various errors while programming BIN file onto it. Additionally, it would say "program successful" in flash programmer but "0 bytes written".

Finally, what worked for me is following-

1. As it is RDB, i imported the xml file (in flash programmer-> task) for RDB from the installation path. As urs is T4240, import in 'task' the xml file from PA/bin/plugin/support/targettask/flashprogrammer/QorIQ_T4240/T2040RDB_NOR_Flash.xml. This wil automatically select the various options needed for the NOR on your RDB

2.In 'add program/verifyaction' tab,give the path of the bin file

check 'erase sector before program'

check 'restrict to address in this range' and give start and end address as start & end address of your NOR flash

check 'apply address offset' and give address as onto which location you want to burn the bin file. For Ex- my flash addr range is 0xff00_0000 - 0xffff_ffff. so i gave this start( 0xff00_0000) and end(0xffff_ffff) address in 'restrict to address in this range' . And i wanted to burn bin at "0xff04_0000' .

So i gave the ''apply address offset' as "0xff04_0000 "

3.Run the task

Actually, The following thread helped me and worked

https://community.nxp.com/thread/391994

Even i observed that if any slight mistake/mismatch in xml for the flash, the flash programmer wont be able to write/erase etc as per user's desire.

I hope this helps. But if it is your custom board then u need to work out on xml. I have not done it yet for custom board. i need to do that next.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Monali,

Thank you for your quick reply with detailed explanation.

Thanks & Regards,

VinothS

Vinothkumar Sekar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

i hope it helps. It should if you using RDB

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

please let me know if it works. Though i have not gotten any error related to sector protection ever

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Monali,

I will reply once I done.

Thanks & Regards,

VinothS

Vinothkumar Sekar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Monali,

Do you have experience in DDR initialization using codewarrior or lauterbach?

If you done please provide the steps?

Regards, VinothS

Vinothkumar Sekar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

No i dont have .sorry.

P2020 RM please download from fresscale. it is very huge to send.

Following is the content of P10xx-P20xxRDB_P2020_init_sram_flash.tcl:

proc envsetup {} {

# Environment Setup

radix x

config hexprefix 0x

config MemIdentifier v

config MemWidth 32

config MemAccess 32

config MemSwap off

}

#-------------------------------------------------------------------------------

# Main

#-------------------------------------------------------------------------------

envsetup

variable SPR_GROUP "e500 Special Purpose Registers/"

variable SSP_GROUP "Standard Special Purpose Registers/"

variable LA_GROUP "Local Access/"

variable ELBC_GROUP "Enhanced Local Bus Controller/"

variable CAM_GROUP "regPPCTLB1/"

variable GPR_GROUP "General Purpose Registers/"

variable LACCS_GROUP "Local-Access Registers-Configuration, Control, and Status Registers/"

variable L2_SRAM_GROUP "L2 Look-Aside Cache SRAM/"

#######################################################################

# set interrupt vectors

# IVPR (compatible to the Flash)

reg ${SPR_GROUP}IVPR = 0xFFFF0000

# debug - (a valid instruction should exist to be fetched)

reg ${SPR_GROUP}IVOR15 = 0x0000F000

# program

reg ${SPR_GROUP}IVOR6 = 0x0000F700

#######################################################################

# Set a breakpoint at the reset address

reg ${SPR_GROUP}IAC1 = 0xfffffffc

reg ${SPR_GROUP}DBCR0 = 0x40800000

reg ${SPR_GROUP}DBCR1 = 0x00000000

reg ${SSP_GROUP}MSR = 0x02000200

config runcontrolsync off

go

wait 50

config runcontrolsync on

stop

reg ${SPR_GROUP}DBCR0 = 0x41000000

reg ${SPR_GROUP}IAC1 = 0x00000000

##################################################################################

# move CCSR at 0xE0000000

# CCSRBAR

# bit 8 - 23 - BASE_ADDR

variable CCSRBAR_addr [format %x [expr {[reg ${LACCS_GROUP}CCSRBAR %x] << 12 }]]

mem p:$CCSRBAR_addr = 0x000e0000

#######################################################################

# invalidate BR0

reg ${ELBC_GROUP}BR0 = 0x00001000

# ABIST off

# L2ERRDIS[MBECCDIS]=1 L2ERRDIS[SBECCDIS]=1

reg ${L2_SRAM_GROUP}L2ERRDIS = 0x0000000C

# activate debug interrupt and enable SPU

reg ${SSP_GROUP}MSR = 0x02000200

##################################################################################

#

# Memory Map

#

# 0x00000000 0x0003FFFF SRAM 256K

# 0xE0000000 0xE00FFFFF CCSRBAR Space 1M

# 0xF8000000 0xF80FFFFF LocalBus NAND FLASH 1M

# 0xFF000000 0xFFFFFFFF LocalBus NOR FLASH 16M

#

##################################################################################

# MMU initialization

# define 1MB TLB1 entry 1: 0xE0000000 - 0xE00FFFFF; for CCSR Space, non cacheable

reg ${CAM_GROUP}L2MMU_CAM1 = 0x500003CAFC080000E0000000E0000001

# define 16MB TLB1 entry 2: 0xFF000000 - 0xFFFFFFFF; for Local Bus, cache inhibited

reg ${CAM_GROUP}L2MMU_CAM2 = 0x70000FCAFC080000FF000000FF000001

# define 256KB TLB1 entry 3: 0x00000000 - 0x0003FFFF; for internal chip SRAM

reg ${CAM_GROUP}L2MMU_CAM3 = 0x400001C0FC0800000000000000000001

# define 1MB TLB1 entry 7: 0xF8000000 - 0xF80FFFFF; for NAND, cache inhibited

reg ${CAM_GROUP}L2MMU_CAM7 = 0x500003CAFC080000F8000000F8000001

##################################################################################

# disable Boot Page Translation Register

reg ${LACCS_GROUP}BPTR = 0x00000000

# Invalidate again BR0 to prevent flash data damage in case

# the boot sequencer re-enables CS0 access

reg ${ELBC_GROUP}BR0 = 0x00001000

##################################################################################

# configure internal SRAM at 0x00000000

# L2CTL

# bit 0 = 0 - L2E: L2 SRAM disabled

# bit 2-3 = 10 - L2SIZ: = 512K

# bit 13-15 = 010 - L2SRAM: One half is SRAM (256K)

reg ${L2_SRAM_GROUP}L2CTL = 0x20020000

# L2SRBAR0

# bit 0-17 = BASE addr: 0x00000000

reg ${L2_SRAM_GROUP}L2SRBAR0 = 0x00000000

# L2SRBAREA0

# bit 28-31 = EXTENTED BASE addr: 0x00000000

reg ${L2_SRAM_GROUP}L2SRBAREA0 = 0x00000000

# L2CTL

# bit 0 = 1 - L2E: L2 SRAM enable

reg ${L2_SRAM_GROUP}L2CTL = 0xA0020000

##################################################################################

#

# Memory Windows

#

# 0xFF000000 0xFFFFFFFF LAW0 Local Bus NOR FLASH - 16M

# 0xF8000000 0xF80FFFFF LAW5 Local Bus NAND FLASH 1M

#

##################################################################################

# configure local access windows

# LAWBAR0 - Local Bus

# bit 8 - 31 = 0xFF000000 - base addr

reg ${LA_GROUP}LAWBAR0 = 0x000ff000

# LAWAR0

# bit 0 = 1 - enable window

# bit 7-11 = 00100 - Local Bus

# bit 26 - 31 = 011011 16M - size

reg ${LA_GROUP}LAWAR0 = 0x80400017

# LAWBAR5 - Local Bus

# bit 8 - 31 = 0xF8000000 - base addr

reg ${LA_GROUP}LAWBAR5 = 0x000f8000

# LAWAR5

# bit 0 = 1 - enable window

# bit 7-11 = 00100 - Local Bus

# bit 26-31 = 010011 1M - size

reg ${LA_GROUP}LAWAR5 = 0x80400013

##################################################################################

# configure Local Bus memory controller

# CS0 - Flash

# BR0 base address at 0xF8000000, port size 16 bit, GPCM, valid

reg ${ELBC_GROUP}BR0 = 0xFF001001

# OR0 16MB flash size

reg ${ELBC_GROUP}OR0_GPCM = 0xFF000FF7

# CS1 - NAND Flash

# BR1 base address at 0xF8000000, port size 8 bit, FCM, valid

reg ${ELBC_GROUP}BR1 = 0xF8000C21

# OR1 1MB size

reg ${ELBC_GROUP}OR1_GPCM = 0xFFF80396

# LBCR

reg ${ELBC_GROUP}LBCR = 0x40000000

# LCRR

reg ${ELBC_GROUP}LCRR = 0x80000008

####################################################################

# interrupt vectors initialization

###

# interrupt vectors in internal SRAM

#

# IVPR (default reset value)

reg ${SPR_GROUP}IVPR = 0x00000000

# interrupt vector offset registers

# IVOR0 - critical input

reg ${SPR_GROUP}IVOR0 = 0x00000100

# IVOR1 - machine check

reg ${SPR_GROUP}IVOR1 = 0x00000200

# IVOR2 - data storage

reg ${SPR_GROUP}IVOR2 = 0x00000300

# IVOR3 - instruction storage

reg ${SPR_GROUP}IVOR3 = 0x00000400

# IVOR4 - external input

reg ${SPR_GROUP}IVOR4 = 0x00000500

# IVOR5 - alignment

reg ${SPR_GROUP}IVOR5 = 0x00000600

# IVOR6 - program

reg ${SPR_GROUP}IVOR6 = 0x00000700

# IVOR8 - system call

reg ${SPR_GROUP}IVOR8 = 0x00000c00

# IVOR10 - decrementer

reg ${SPR_GROUP}IVOR10 = 0x00000900

# IVOR11 - fixed-interval timer interrupt

reg ${SPR_GROUP}IVOR11 = 0x00000f00

# IVOR12 - watchdog timer interrupt

reg ${SPR_GROUP}IVOR12 = 0x00000b00

# IVOR13 - data TLB errror

reg ${SPR_GROUP}IVOR13 = 0x00001100

# IVOR14 - instruction TLB error

reg ${SPR_GROUP}IVOR14 = 0x00001000

# IVOR15 - debug

reg ${SPR_GROUP}IVOR15 = 0x00001500

# IVOR32 - SPE-APU unavailable

reg ${SPR_GROUP}IVOR32 = 0x00001600

# IVOR33 - SPE-floating point data exception

reg ${SPR_GROUP}IVOR33 = 0x00001700

# IVOR34 - SPE-floating point round exception

reg ${SPR_GROUP}IVOR34 = 0x00001800

# IVOR35 - performance monitor

reg ${SPR_GROUP}IVOR35 = 0x00001900

# put a valid opcode at debug and progrm exception vector address

mem v:0x00000700 = 0x48000000

mem v:0x00001500 = 0x48000000

#############

#

# activate debug interrupt and enable SPU

reg ${SSP_GROUP}MSR = 0x02000200

############

#

# time base enable

# HID0

reg ${SPR_GROUP}HID0 = 0x00004000

# NAND Flash settings

#

# FMR

reg ${ELBC_GROUP}FMR = 0x0000F020

######

# CW debugger settings

#

#Trap debug event enable

reg ${SPR_GROUP}DBCR0 = 0x41000000

# set the PC at the reset address (for debug-->connect)

reg ${GPR_GROUP}PC = 0xFFFFFFFC

# for debugging starting at program entry point when stack is not initialized

reg ${GPR_GROUP}SP = 0x0000000F

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Monali,

Thank you.

Vinothkumar Sekar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Vinothkumar,

Do u have any docs of preboot loader and what it actually does. And what happens after the control comes to 0xfffffffc after reset?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Monali,

Now I am trying through lauterbach trace32 debugger. I will update once I done through codewarrior.

Vinothkumar Sekar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi All,

From s29GL01GS datasheet, Flash Chip: S29GL01GS and Device ID: 227E

From S29GL01GP.XML,

fl::target -lc "Peacock_10thDec-core00_RAM_T4160_Connect"

fl::target -b 0x0 0x20000

fl::target -v off -l off

cmdwin::fl::device -d "S29GL01GP" -o "64Mx16x1" -a 0xe8000000 0xefffffff

cmdwin::fl::protect all off

Beginning Operation ...

-------------------------

Performing target initialization ...

Downloading Flash Diagnostics Driver ...

Reading flash ID ...

Unprotecting all sectors...

Unprotecting ...

Unprotecting ....

Unprotecting .....

Unprotecting ......

Unprotecting .......

Unprotecting ........

Unprotecting .........

Unprotect Command Succeeded

cmdwin::fl::image -f "C:\\Logi\\Work\\Projects\\BEL\\QorIQ_VPX\\Software\\T4160\\Zumi Solutions\\Uboot images\\181213\\u-boot-nor-2016.01+fslgit-r0.bin" -t "Auto Detect" -re off -oe on -o 0xe8000000

cmdwin::fl::erase image

-------------------------

Auto-detection is successful.

File is of type Binary/Raw Format.

Downloading Flash Device Driver ...

Reading flash ID ...

Erasing Sector 0xE8000000 to 0xE801FFFF

Erasing Sector 0xE8020000 to 0xE803FFFF

Erasing Sector 0xE8040000 to 0xE805FFFF

Erasing Sector 0xE8060000 to 0xE807FFFF

Erasing Sector 0xE8080000 to 0xE809FFFF

Erasing Sector 0xE80A0000 to 0xE80BFFFF

Erasing ...

Error: Erase failed. Flash driver reports the following error(s): Sector Protection Error

Error: Erase failed. Flash driver reports the following error(s): Sector Protection Error

Thank you for everyone help....!

Regards,

VinothS

Vinothkumar Sekar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

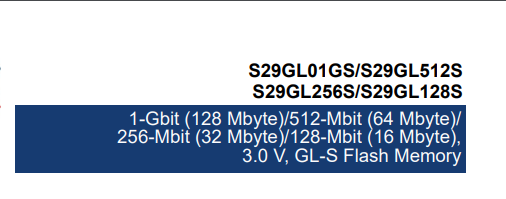

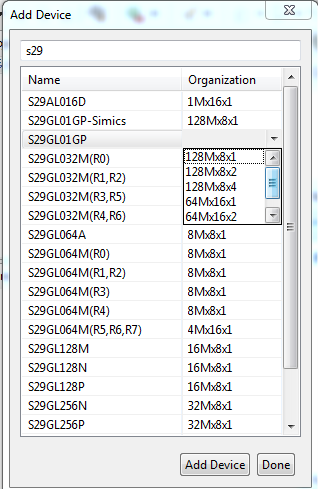

Hi All,

What is the difference between S29GL01GS and S29GL512S Flash Device ?

I am using S29GL01GS and I select Organization as 64MX16X1.

or

I Want to Select Organization as 128MX8X1.

Which one I want to select to program using CodeWarrior Flashprogrammer?

Thank you for all your support........!

Regards, VinothS

Vinothkumar Sekar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi All,

Still I am struggled with the organization selection for S29GL01GS

And I followed this datasheet,

http://www.cypress.com/file/177976/download

From that which Organization want to select for CodeWarrior Flashprogrammer.

Thank for all your support.......!

Regards, VinothS

Vinothkumar Sekar