- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- CodeWarrior

- :

- QorIQ用CodeWarrior

- :

- HRESET

HRESET

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

We are trying to run the bare board example program of CodeWarrior on the T4240QDS.

HRESET is alaways on. Any clues on how to resolve this issue?

Any help will be appreciated.

Regards,

avt,chris

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

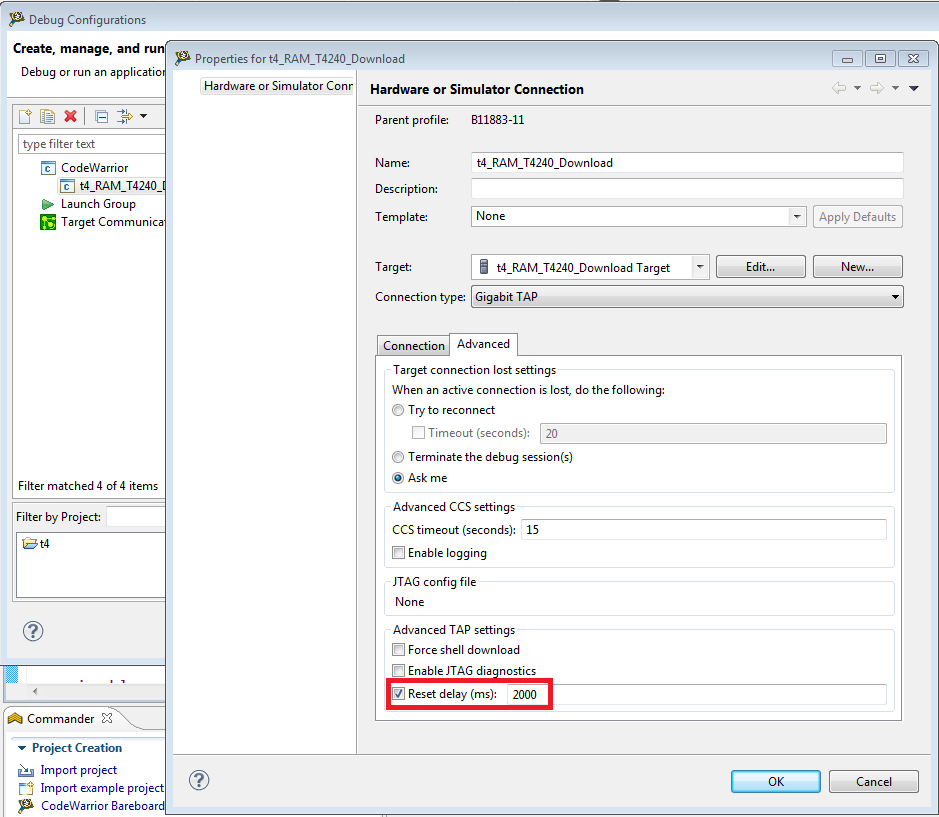

Could you try from CW, to add 2 sec Reset delay when connect to the board? Using some fpga version this is required by CW to connect to the board.

But, please make sure a valid fpga is programmed to the board.

Adrian

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

As for me, I am curious about it as well.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

As for me, I am curious about it as well.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Please provide the fpga version displayed by uboot for your board.

Adrian

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Adrian,

Thanks for your answer.

We worked on a bareboard of t4240qds, and just burn the fpga stp file: (file A)T4240QDS_Qixis_sys_cntrl_FPGA_140410\designer\QixMin_T4240QDS.stp .

There's no uboot running on this board. We want to program target board, but met something wrong with CodeWarrior TAP.

CW TAP can show the right MAC address when type in "findcc cwtaps -usb" on ccs console.

Q2: We tried to downgrade FPGA to this version, (file B)T4240QDS_2013_0509_1415.stp . Quote this link: CW won't debug T4240QDS: fails to reset target . And then got another messege: "IDCODE verify failed."

Both file A and file B IDCODE are the same string, 0653A1CF. IDCODE read from device : 1253A1CF .(we programmed file A before.)

This confused us, how to downgrade FPGA to file B.

thank you for your any suggetions.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

For FPGA version 5 (T4240QDS_2013_0509_1415_V5), CW should works with no issues. I attached the image I used.

For FPGA version 6 (T4240QDS_2014_0522_1552_V6), CW will need a 2sec Reset delay (Go to Debug Configuration -> Edit -> Advanced -> Reset delay).

Adrian

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Adrian,

The message: "IDCODE verify failed." shows again and again. We can't program these stp files. I don't known why and how ?

We got another errors when running CW debug:

A.

"Error launching t4240qds-core00_RAM_T4240_Download

CCSProtocolPlugin : Failed to correctly configure the JTAG chain"

B.

"Error launching t4240qds-core00_RAM_T4240_Download

CCSProtocolPlugin::Could not connect to the requested core #0."

Our ccs.cfg set to below lines:

“

delete all

config cc cwtap

config port 41475

ccs::config_chain t4240

ccs::reset_to_debug

ccs::all_run_mode

”

More infomations:

Three leds on our target board, label RESERT_RED, HRESET, SLEEP show some diff status,

When power on target board:

SLEEP blinking yellow, HRESER on red, RESET_RED off.

And more than 10 seconds later ,these leds always on till power off.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Did you used a flashpro programmer to program fpga files? If yes, this is not good, because a valid fpga image must be programmed on the board.

Adrian

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Could you try from CW, to add 2 sec Reset delay when connect to the board? Using some fpga version this is required by CW to connect to the board.

But, please make sure a valid fpga is programmed to the board.

Adrian

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Adrian,

We set the reset delay as 2000ms, but still can't connect target board, and the HRESET led still on.

The fpga is valid , when we found the diff stp files(mentioned above) worked not the same.

Would you please send us the whole fpga source files/projects, we want to compile the fpga step by step ourself.

Best wishes

chris

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Unfortunately I don't have the source code for fpga, only the binary to be programmed into the board. You could open a service request and ask for source code.

Adrian

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Adrian,

Thank you for your patience to answer.

Chris

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Adrian,

Yes, we used the flashpro v4 to program fpga file on the board. The fpga file:T4240QDS_Qixis_sys_cntrl_FPGA_140410\designer\QixMin_T4240QDS.stp shows it was made on day 04/10/2014.