- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- CodeWarrior

- :

- CodeWarrior for QorIQ

- :

- CWTAP_GDB_P1010_P4080 (P1010 and P4080 XML and Initialization for GDB debugging)

CWTAP_GDB_P1010_P4080 (P1010 and P4080 XML and Initialization for GDB debugging)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

CWTAP_GDB_P1010_P4080 (P1010 and P4080 XML and Initialization for GDB debugging)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm using the P1010RDB along with a CodeWarrior TAP and Power Architecture TIP.

I'm having a little trouble understanding the settings for the TLB1 entries.

I downloaded the CW_TAP_GDB_P1010_P4080 (filename gdb_test_ccs_365.tar.gz), I found the only documentation explaining the three longwords (96 bits) displayed for a TLB1 table entry are in the comments as follows in the bin/p1010_init.gdb file:

# 0 20 21 29 39 40 41

# data format of l2mmu_cam = EPN(20)::TS::TID(8)::MASK(10)::IPROT::VALID::IPROT_dup::

# RPN(24)::UR::UW::UX::SR::SW::SX::X(2)::WIMGE(5)::U(4)::TSIZE(4)::SHEN::IPROT::spare

# 42 66 67 68 69 70 71 72 74 79 83 87 88 89

After the comment above the p1010_init.gdb file sets the TLB1 entrys:

echo Set TLBs\n

set $mmu_l2_tlb1_2={0xE0000000, 0x1FC38000, 0x07140A80}

set $mmu_l2_tlb1_3={0xFE000000, 0x7FC3F800, 0x07140E80}

set $mmu_l2_tlb1_4={0xFF000000, 0x7FC3FC00, 0x07140E80}

set $mmu_l2_tlb1_5={0x80000003, 0xFFC20000, 0x07141480}

set $mmu_l2_tlb1_6={0xEFC00000, 0x0FC3BF00, 0x07140880}

set $mmu_l2_tlb1_7={0xEFB00000, 0x0FC3BEC0, 0x07140880}

I examined the contents of the TLB before any of the modifications were written above (I placed an "info registers" before the first "set $mmu_l2_tlb1_2 ...") and it shows the following for the zero'th entry in TLB1:

mmu_l2_tlb1_0 {0xfffff000, 0x1c3ffff, 0xc71402c0}

As I understand it this entry should be mapping the last 4 Kbytes of memory space (flash) that encompasses the reset vector (0xFFFFFFFC).

The TLB1 definition in the comments show the 'spare' field is the least significant 7 bits of the 3rd word.

Why does the default TLB1 entry 0 have a bit set in this 'spare' field?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

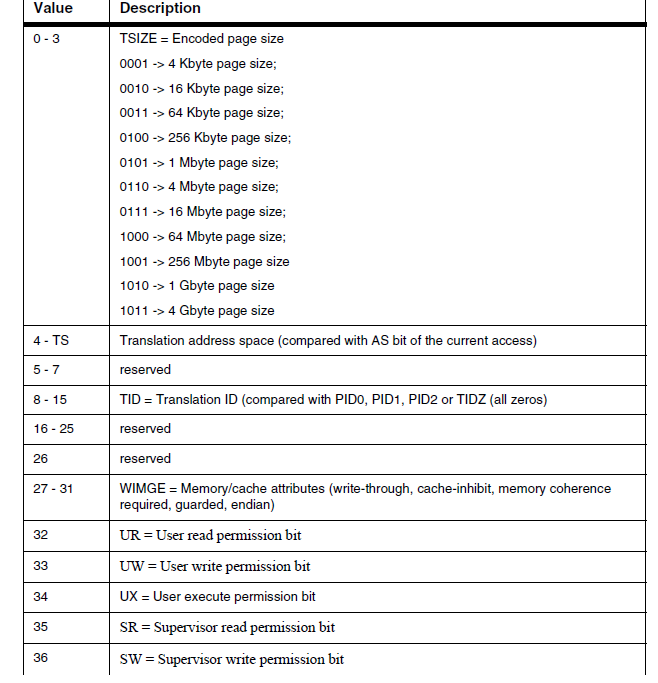

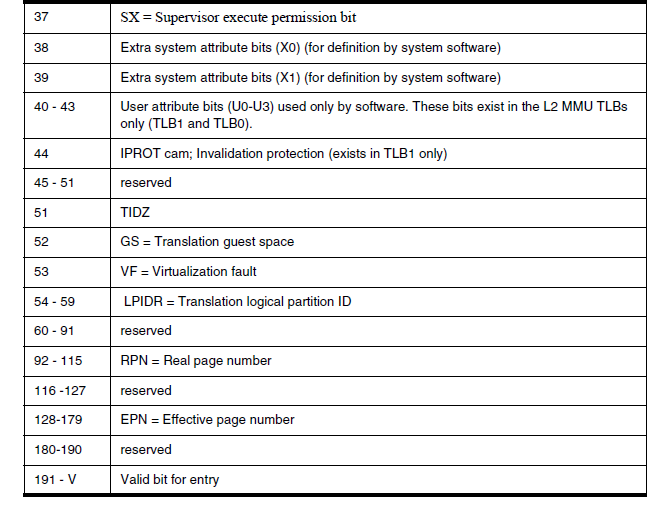

Please refer to the following detailed information of TLB1 register.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The internal representation of the TLB entry is interesting, but it doesn't really answer how the 3 longwords (96 bits) of the TLB entry as viewed in GDB map into the 191 bits of the internal TLB entry.

Also, I specifically was interested in why a spare field seemed to have a bit set in it by default (as viewed in GDB).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The internal representation of the TLB entry is interesting, but it doesn't really answer how the 3 longwords (96 bits) of the TLB entry as viewed in GDB map into the 191 bits of the internal TLB entry.

Did anyone find out how this mapping from 191 to 96 bits takes place ? I haven't been able to find any documentation regarding this transformation.