- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

Implementing a software reset by writing to SRS register on S08 MCUs

Implementing a software reset by writing to SRS register on S08 MCUs

1 Introduction.

This document provides tips and tricks for implementing a Software Reset by writing to the SRS register of some MC9S08 MCUs.

2 Detailed Description.

Watchdog module (Computer Operating Properly: COP) provides a secure method of ensure that the microcontroller is properly executing the programmed code, because it provides a specific time window before requiring clearing the timer; if a code-runaway condition or blocking code situations happens, the watchdog won’t be cleared, and a Reset will occur.

This characteristic could be also used as software reset implementation. There are many versions of the COP module, and each of them has its own SRS configuration register and clearing mechanism. Below you can find two variations of the SRS register description:

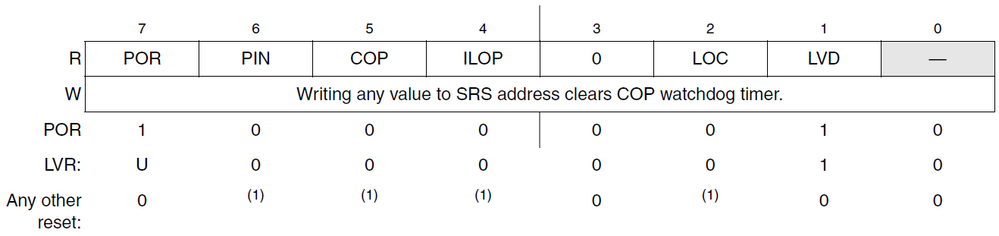

- “Writing any value to SRS address clears the Watchdog timer”: It is included in devices like the S08AW60, S08JM60, and S08QE32. Figure 1 shows the register description of S08JM60 device:

Figure 1: SRS register on S08JM60 device.

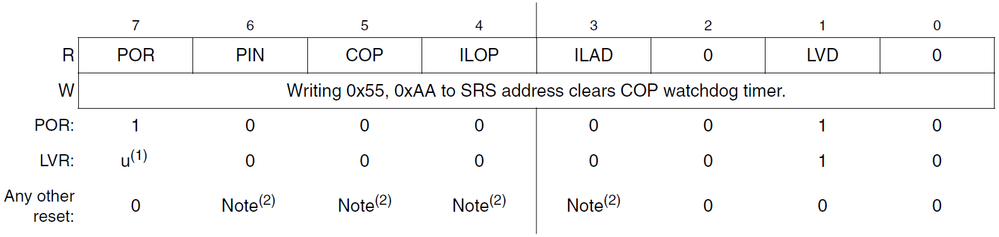

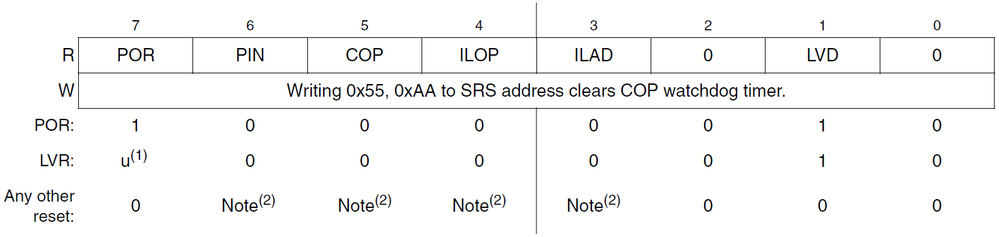

- “Writing 0x55 -> 0xAA sequence to SRS address clears the Watchdog timer”: It is included in devices like the S08DZ128, S08MM128 and S08SG8. Figure 2 shows the register description of S08SG8 device:

Figure 2: SRS register on S08SG8 device.

Taking as reference the second case, it is possible to generate a Software Reset by writing a value different than 0x55 or 0xAA, to SRS register. It is based on the following sentence, included on the Watchdog description section of device’s Datasheet/Reference Manual:

“The COP counter is reset by writing 0x0055 and 0x00AA (in this order) to the address of SRS during the selected timeout period. Writes do not affect the data in the read-only SRS. As soon as the write sequence is done, the COP timeout period is restarted. If the program fails to do this during the time-out period, the MCU will reset. Also, if any value other than 0x0055 or 0x00AA is written to SRS, the MCU is immediately reset.”

However, there are some conditions that could cause that the reset is not such immediate. If the COP is cleared (writing 0x55 and then 0xAA) and the 1 KHz clock is being used as COP clock, there is a window of 1 or 2 clock cycles after the timer clear when the circuitry is resetting the counter. If a write of bad data is done right after the timer clear within such 1-2 clock window (1-2 ms) the COP will not be reset until the next write (of any value).

3 Solutions.

It is more common that this issue happens in periodic tasks. So, in order to fix it, the following workarounds could be implemented:

- Execute the bad write before clearing the COP. A useful test could be running a main loop and enabling a push button; if button is pressed, application writes a bad value to SRS register. This is asynchronous to the periodic task and would resultin a reset “immediately”.

- Change to Bus clock for COP clock and change COPT bits to 11 for the longest time out (which is longer than 12.5 ms periodic task to clear). Then, the window after the timer clear is only 2 Bus cycles (that aren’t enough to execute the write instructions) and any subsequent bad write is seen as a bad write and the reset happens “immediately”.