#### KW45 & K32W1 MINIMUM BOM

CONFIDENTIAL AND PROPRIETARY

SECURE CONNECTIONS FOR A SMARTER WORLD

# KW45 & K32W148 HVQFN48 – 7X7

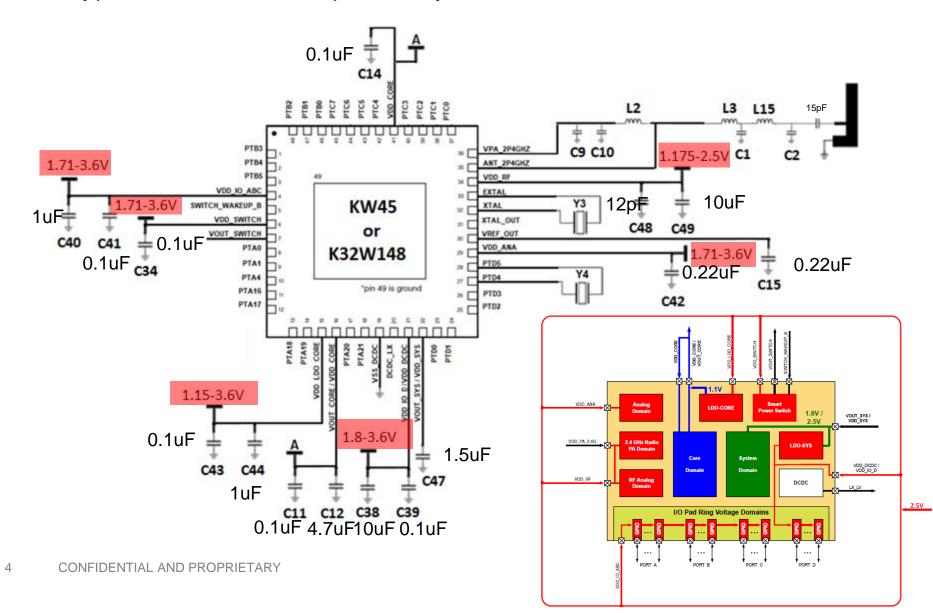

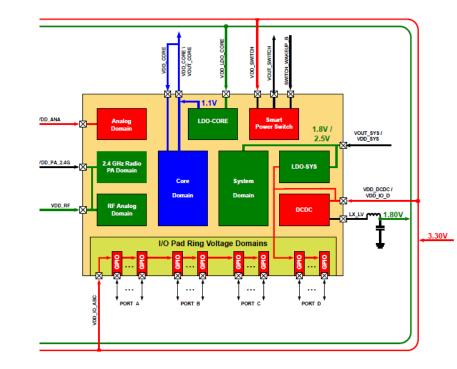

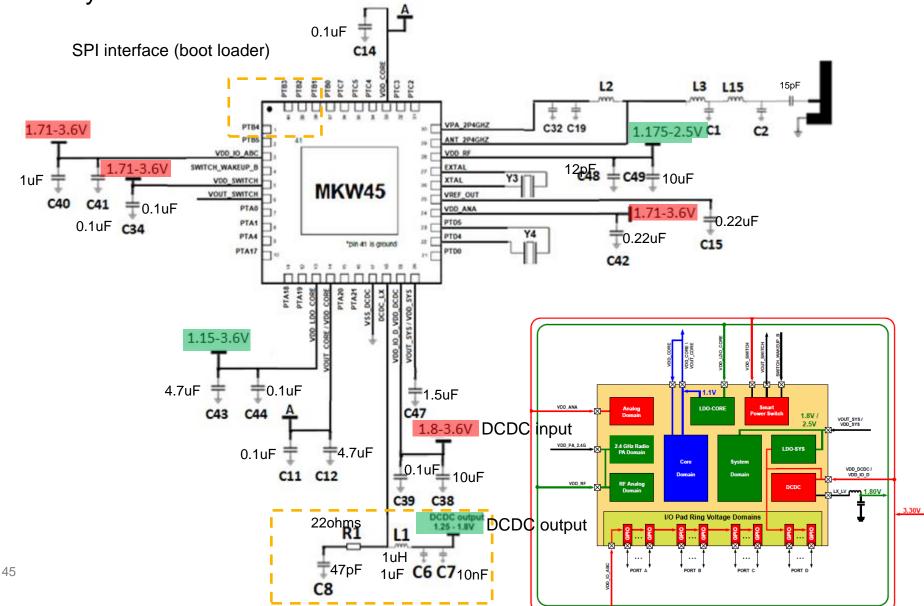

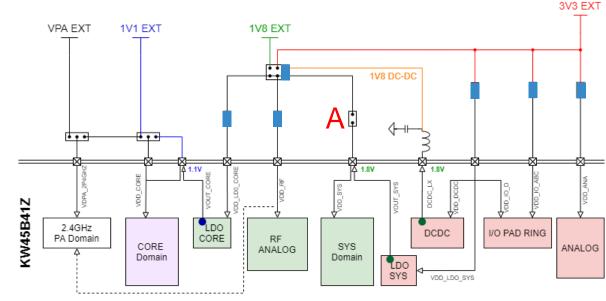

### **Power config diagram – DCDC Bypass**

#### Configuration

- Bypass DCDC

- External 3.3 V for LDO-CORE, LDO-SYS, VDD\_IO

- Generate VPA\_2PGHZ internally from VDD\_RF

| Regulator | Output               | Input volt           | age range                                 |  |

|-----------|----------------------|----------------------|-------------------------------------------|--|

| DCDC      | 1.8V to 2.5 V        | 1.8V t               | o 2.5 V                                   |  |

| LDO-SYS   | 1.8 / 2.5 V          | / 2.5 V 1.8~3.6 V    |                                           |  |

| LDO-CORE  | 1.05/1.1/1.15 V      | 1.71~3.6 V (Enable); | 1.71~3.6 V (Enable); 0.84~1.21 V (Bypass) |  |

| VPA_2P4GH | Z Tx Output<br>Power | VPA source           | VDD_RF                                    |  |

| 0.9 V     | +1.8 dBm             |                      | 1.175 ~3.6 V                              |  |

| 1.525 V   | +7 dBm               | External or internal | 1.8 ~ 3.6 V                               |  |

| 2.2 V     | +10 dBm              |                      | 2.475~3.6 V                               |  |

**Note:** VPA\_2P4GHZ voltage depends on Tx power level. It can be powered externally or internally.

00100 1.1V VDD AN/ LDO-CORE 1.8V / VOUT\_SYS / VDD\_SYS 2.5V VDD\_PA\_2.4G 2.4 GHz Ra LDO-SYS PA Domai Core System VDD\_DCDC/ VDD\_IO\_D Domain Domain VDD BE RF Analo DCDC LX LV I/O Pad Ring Voltage Domains ... •••

VPA\_2P4GHZ voltage depends on Tx power level. It can be powered externally or internally. For internal generation, VDD\_RF voltage must be equal to or exceed VPA + 275 mV.

Warning: Do not connect the pin VDD\_SYS (internal connection)

2.5V

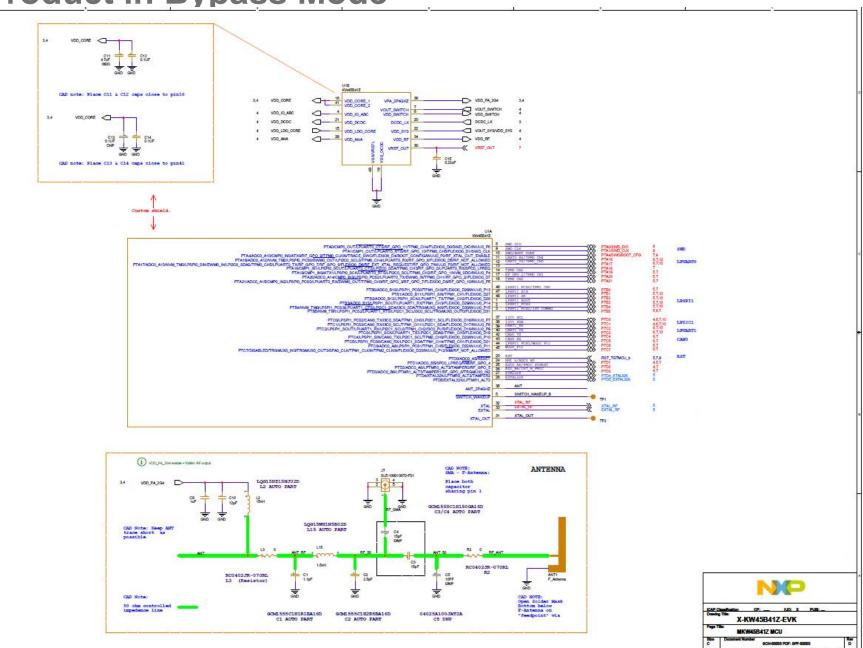

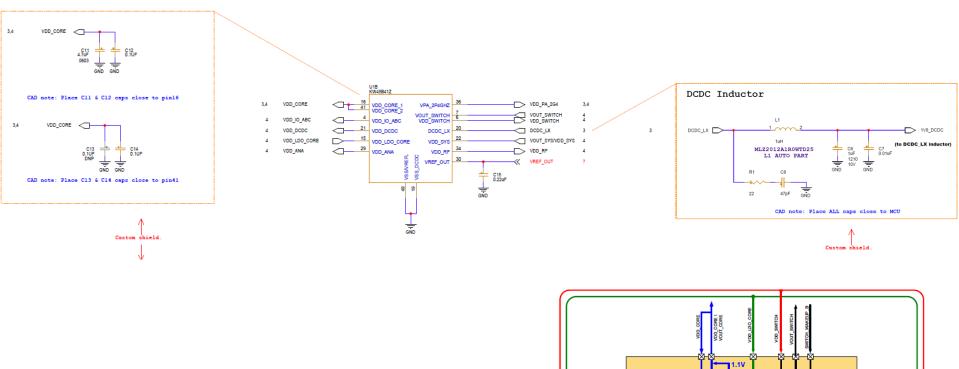

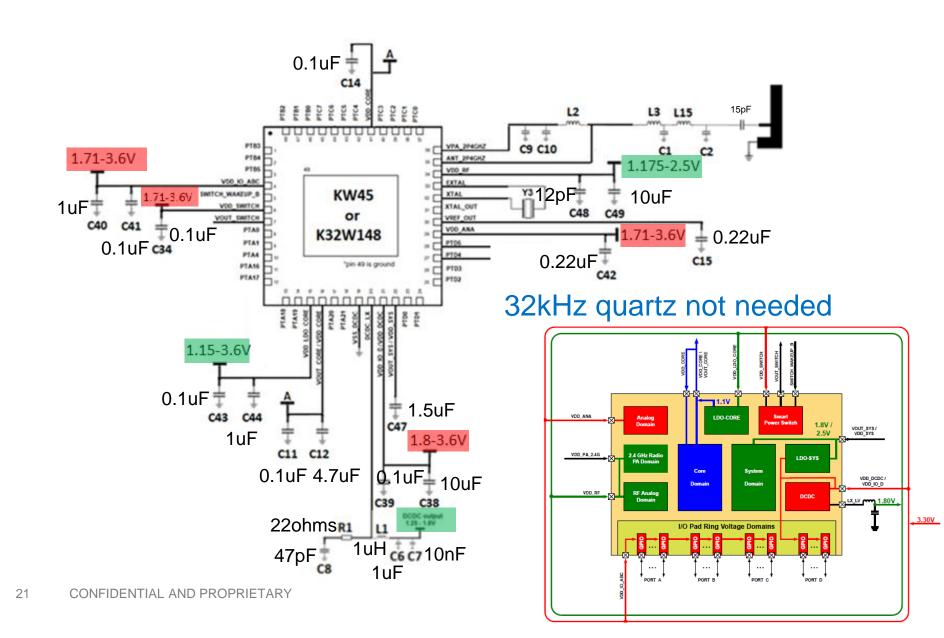

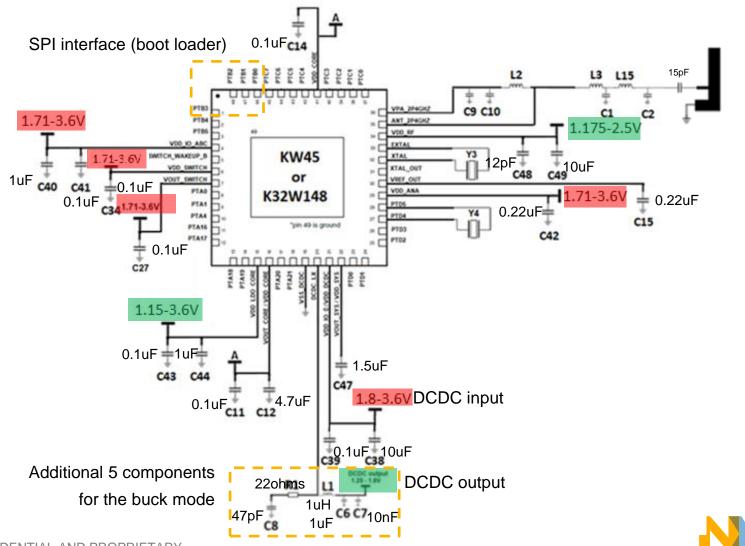

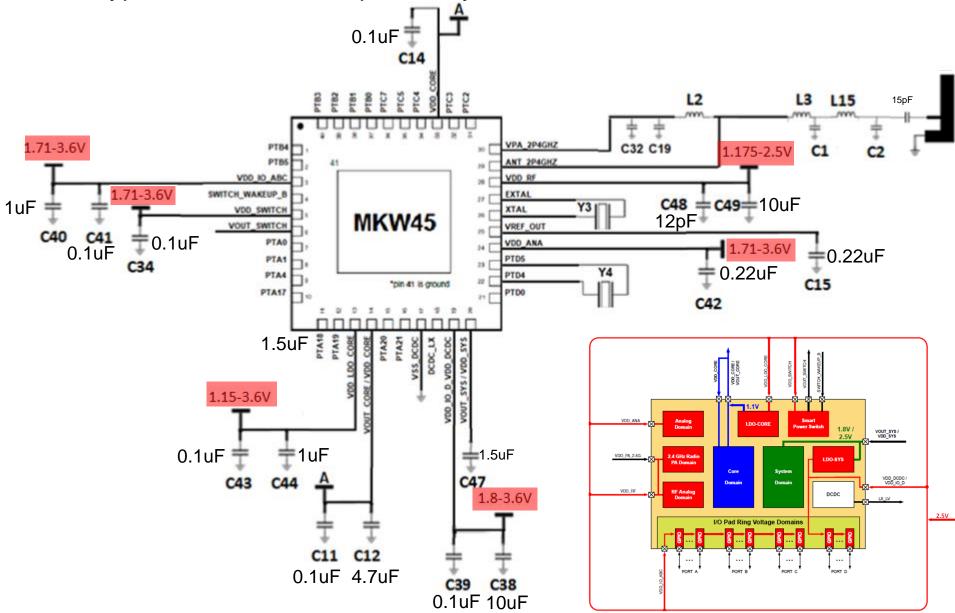

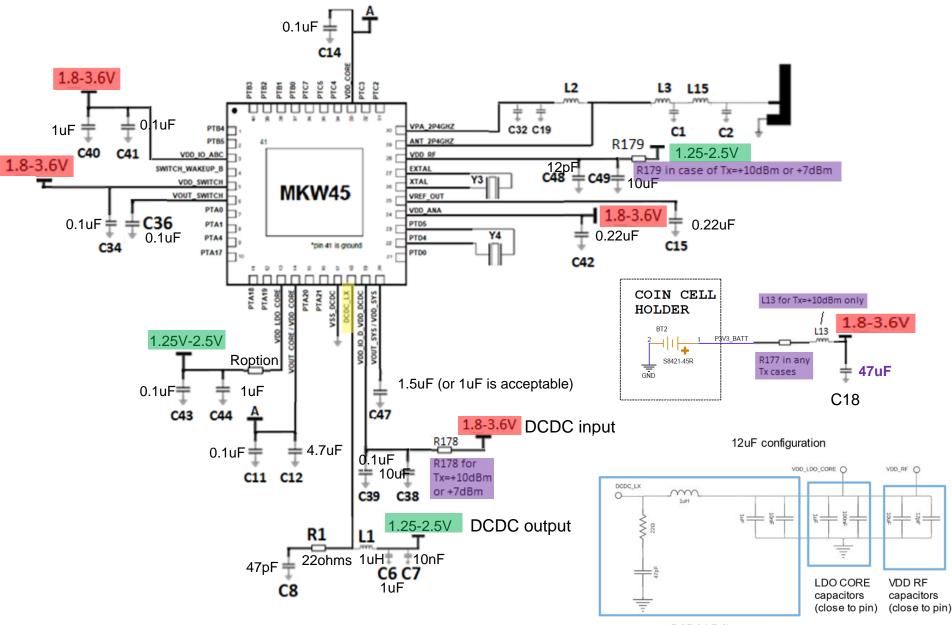

#### **DCDC Bypass Schematic**

#### HVQFN48 – 7x7

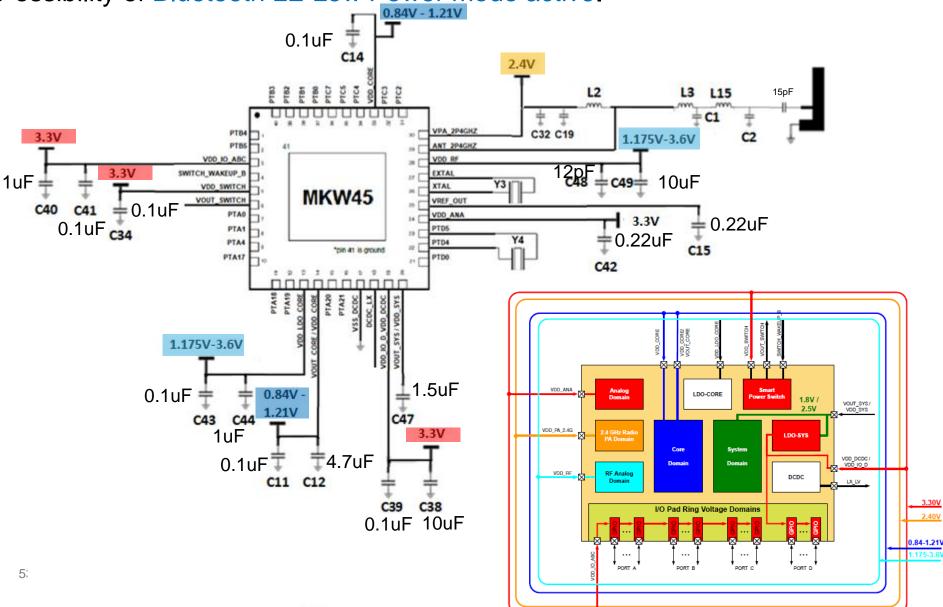

DCDC bypass mode with the possibility of Bluetooth LE Low Power mode active.

#### **Product in Bypass Mode**

**HVQFN48 – 7x7**

April 19, 2022

Sheet 3 d

5

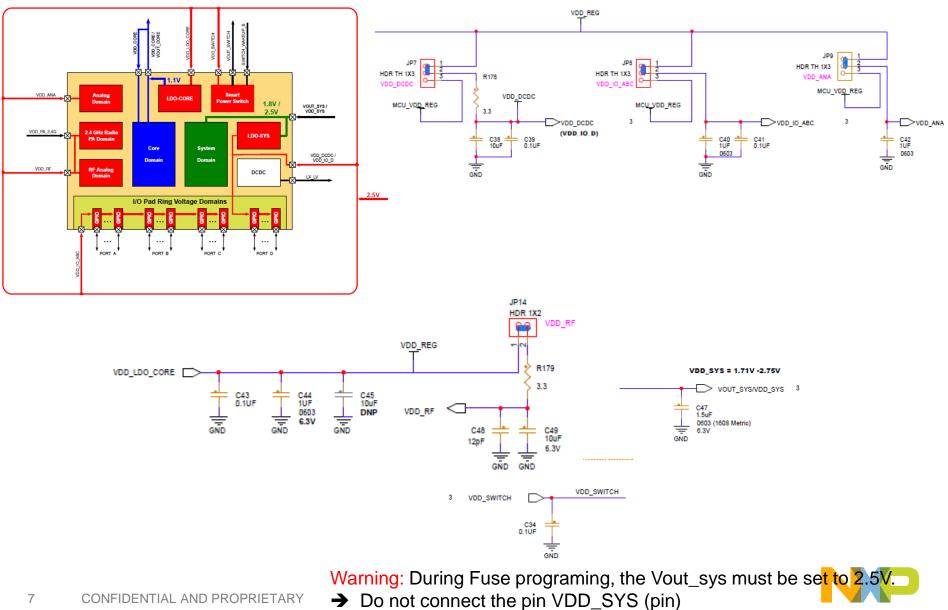

#### **Evaluation board – Recommendation - Bypass**

#### **Evaluation board – Recommendation - Bypass**

7 CONFIDENTIAL AND PROPRIETARY

→ It's done internaly on the IC

### **DCDC Bypass BOM**

#### HVQFN48 – 7x7

#### Bluetooth LE Low Power mode option available (32kHz populated)

| Reference                              | Value               |  |

|----------------------------------------|---------------------|--|

| C11,C14,C34,C39,C41,C43                | 0.1uF               |  |

| C40,C44                                | 1uF                 |  |

| C12                                    | 4.7uF               |  |

| C15,C42                                | 0.22uF              |  |

| C48                                    | 12pF                |  |

|                                        | 1.5uF               |  |

| C47                                    | (or 1uF acceptable) |  |

| C38,C49                                | 10uF                |  |

| Printed IFA antenna                    | 2.4GHZ              |  |

|                                        | KW45B41Z            |  |

| U1                                     | Or                  |  |

|                                        | K32W148             |  |

| Y3                                     | 32MHz               |  |

| Y4                                     | 32.768 kHz          |  |

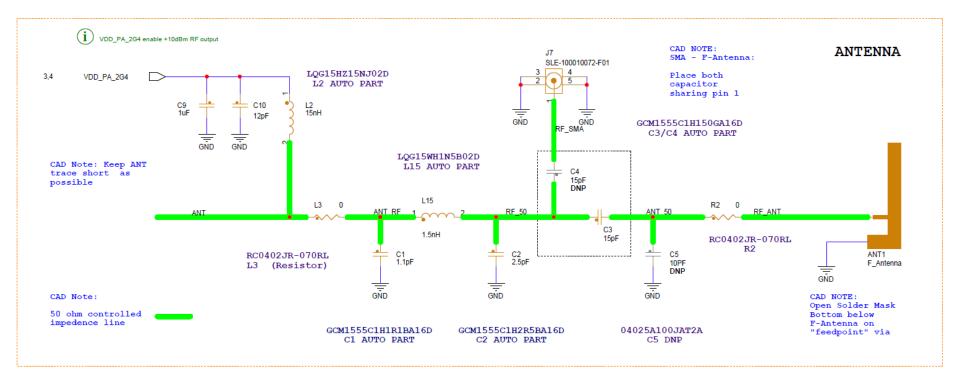

| RF matching (whatever the RF output po | wer)                |  |

| С9                                     | 1 uF                |  |

| C10                                    | 12 pF               |  |

| L2 (LQG15HZ15NJ02D)                    | 15 nH               |  |

| L3 (resistor shunt)                    | 0 ohm               |  |

| C1 (GCM1555C1H1R1BA16)                 | 1.1 pF              |  |

| L15 ( <i>LQG15WH1N5B02</i> )           | 1.5nH               |  |

| C2 (GCM1555C1H2R5BA16)                 | 2.5 pF              |  |

Note: C38,C40, C42, and C46 have different values from the schematic. This is due to the LPC current probe which need bigger decoupling capacitors.

8

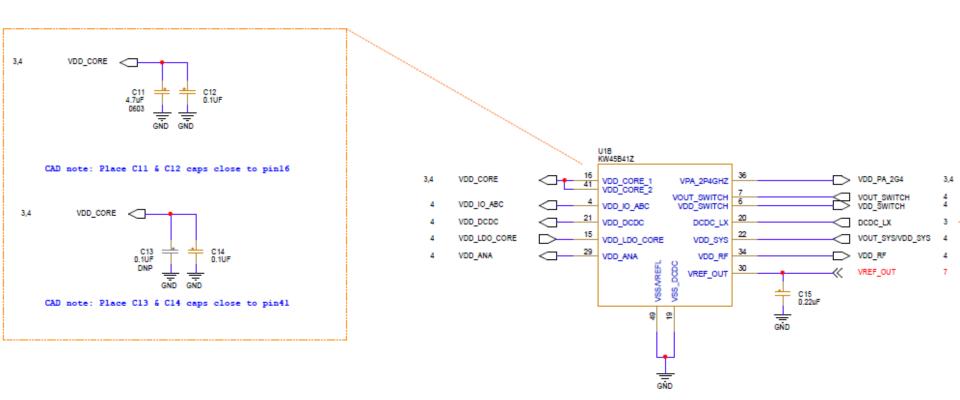

### **DCDC Bypass Pin configuration**

HVQFN48 – 7x7

| Pin Number | Pin Name         | Bypass connection                              |

|------------|------------------|------------------------------------------------|

| 4          | VDD_IO_ABC       | 1.71-3.6V                                      |

| 6          | VDD_SWITCH       | 1.71-3.6V                                      |

| 7          | VOUT_SWITCH      | Floating (when not used)                       |

| 15         | VDD_LDO_CORE     | 1.15-3.6V                                      |

|            |                  | 0.95-1.1V (Mid drive) or                       |

| 16         | VDD_CORE1        | 1.04-1.21V (Normal drive or safe mode voltage) |

| 20         | DCDC_LX          | Floating (not used)                            |

| 21         | VDD_DCDC         | 1.8-3.6V                                       |

| 22         | VOUT_SYS/VDD_SYS | Floating (except the decoupling capacitor)     |

| 29         | VDD_ANA          | 1.71-3.6V                                      |

| 30         | VREF_OUT         | Floating (except the decoupling capacitor)     |

| 34         | VDD_RF           | 1.175-2.5V                                     |

| 36         | VPA_2P4GHZ       | 0.9-2.4V                                       |

|            |                  | 0.95-1.1V (Mid drive) or                       |

| 41         | VDD_CORE2        | 1.04-1.21V (Normal drive or safe mode voltage) |

| 49         | VSS              | GND                                            |

| 19         | VSS_DCDC         | GND                                            |

Warning: → Do not connect the pin VDD\_SYS (internal connection)

Bluetooth LE Low Power mode option available (32kHz populated)

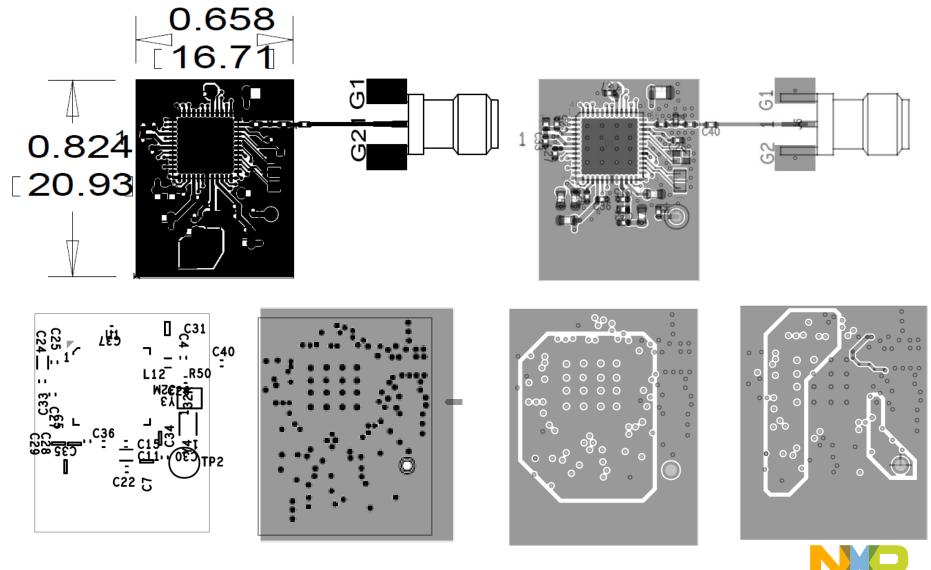

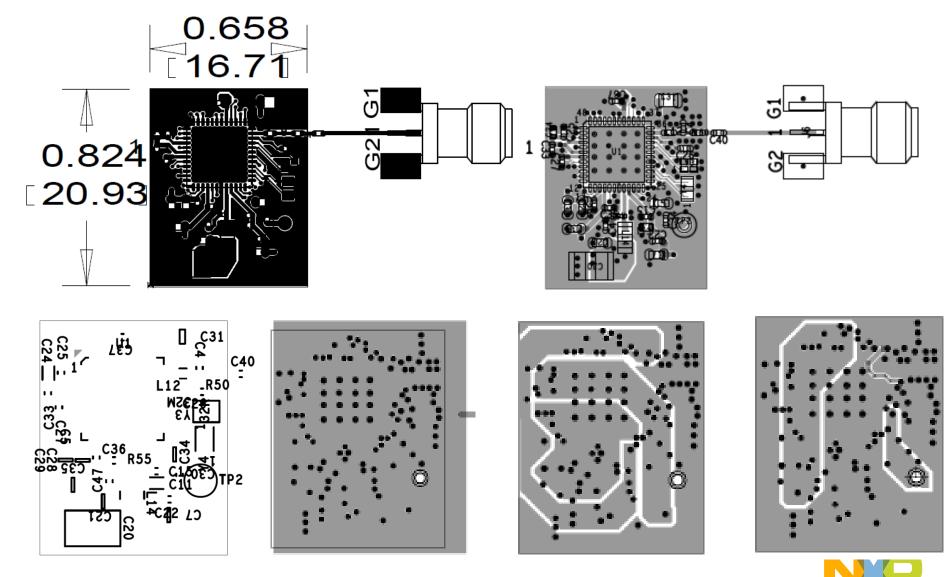

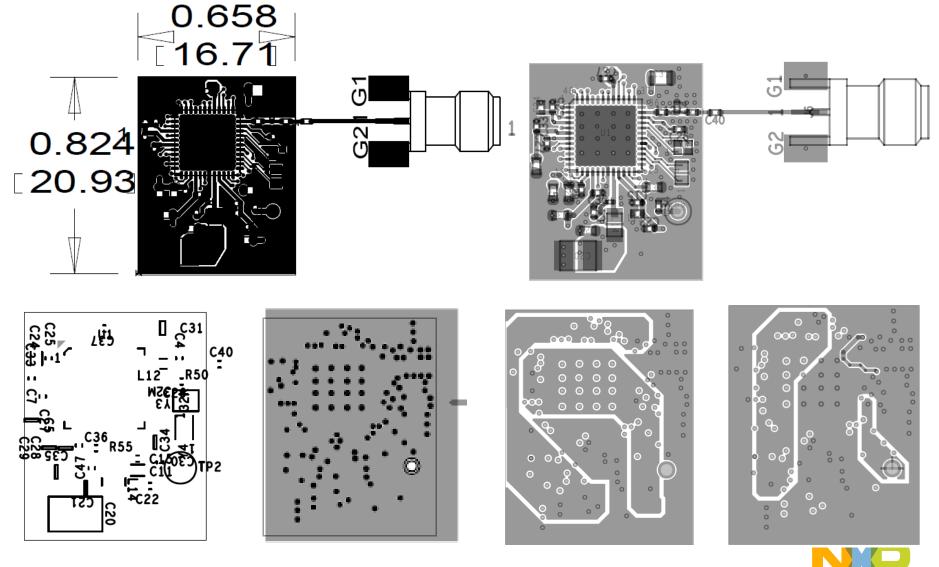

#### Layout example on bypass mode HVQFN48WF – 7x7

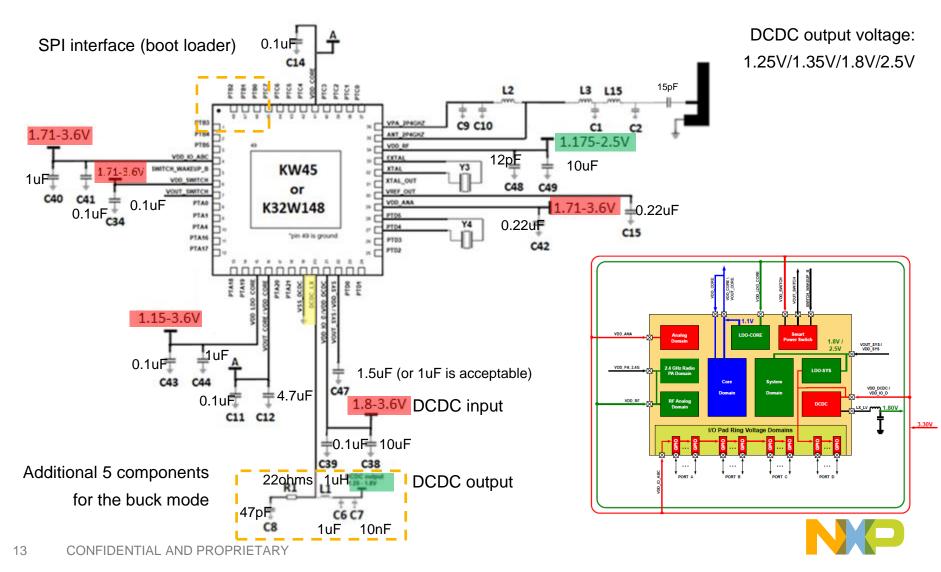

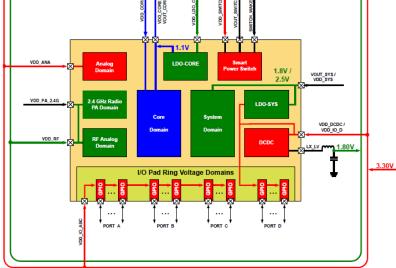

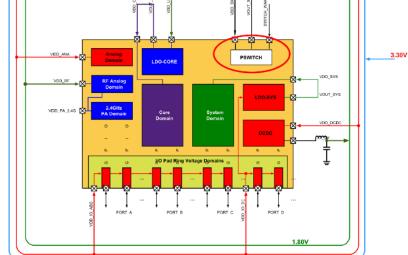

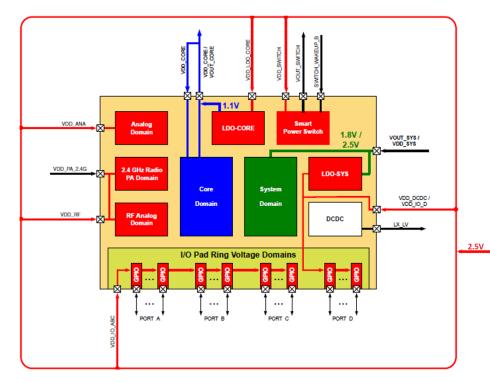

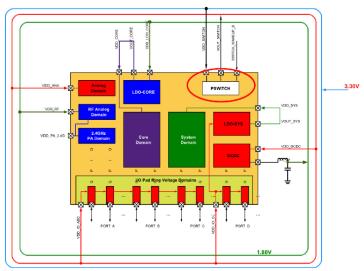

### **EVK – Power config diagram – DCDC Buck**

1.175 ~3.6 V

1.8 ~ 3.6 V

2.475~3.6 V

#### Configuration

Bypass DCDC

0.9 V

1.525 V

2.2V

- External 3.3 V for LDO-CORE, LDO-SYS, VDD\_IO

- Generate VPA\_2PGHZ internally from VDD\_RF

+1.8 dBm

+7 dBm

+10 dBm

| Regulator                           | Output              | Input volta          | age range            |

|-------------------------------------|---------------------|----------------------|----------------------|

| DCDC                                | 1.25/1.35/1.8/2.5 V | 1.71~3.6 V; >= 0     | output + 500 mV      |

| LDO-SYS                             | 1.8 / 2.5 V         | 1.8~                 | 3.6 <mark>V</mark>   |

| LDO-CORE                            | 1.05/1.1/1.15V      | 1.71~3.6 V (Enable); | 0.84~1.21 V (Bypass) |

| VPA_2P4GHZ Tx Output VPA source VDI |                     | VDD_RF               |                      |

**Note:** VPA\_2P4GHZ voltage depends on Tx power level. It can be powered externally or internally. For internal generation, it can support up to +7 dBm and VDD\_RF voltage must meet specific voltage range.

VPA\_2P4GHZ voltage depends on Tx power level. It can be powered externally or internally. For internal generation, VDD\_RF voltage must be equal to or exceed VPA + 275 mV.

External or internal

Warning: During Fuse programing, the Vout sys must be set to 2.5V. → Do not connect the pin VDD\_SYS (internal connection)

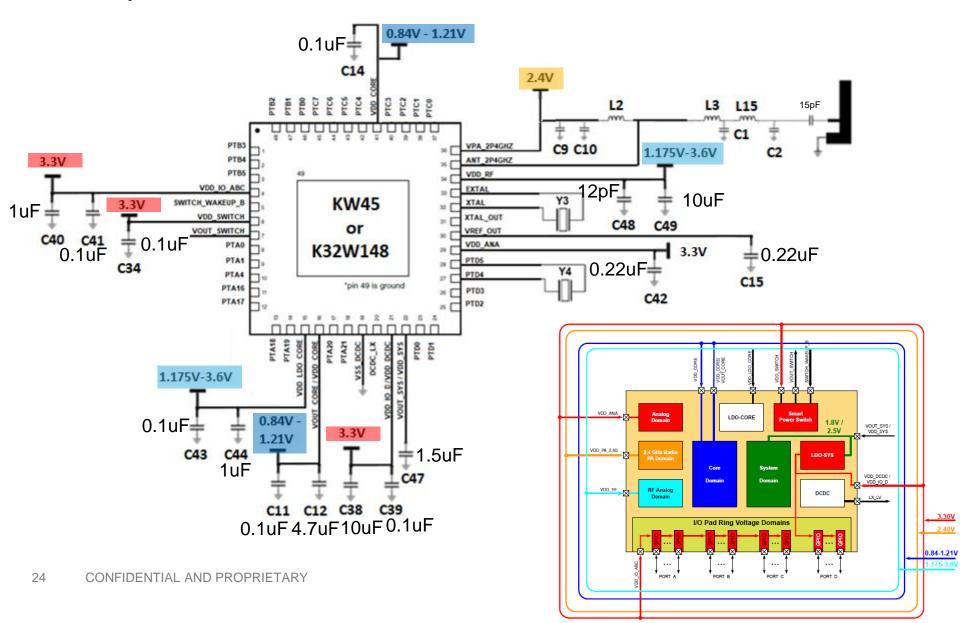

#### **Product in Buck Mode**

#### HVQFN48 - 7x7

Possibility of Bluetooth LE Low Power mode active in case 32kHz is populated.

#### **Product in Buck Mode**

**HVQFN48 – 7x7**

April 19, 2022

Steel 3 d

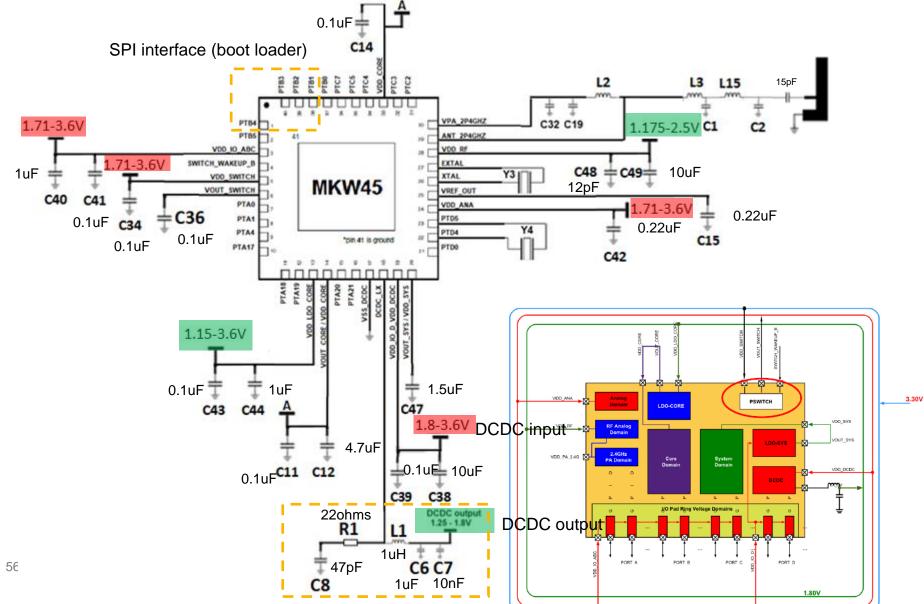

#### **Evaluation board – Recommendation**

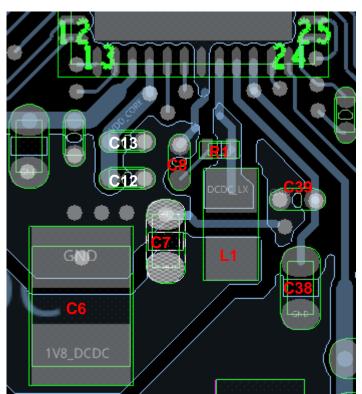

Recommanded DCDC inductor (L1): MLZ2012A1R0WTD25

#### **Evaluation board – Recommendation - Buck**

16 CONFIDENTIAL AND PROPRIETARY

Do not connect the pin VDD\_SYS (pin)

It's done internaly on the IC

#### **DCDC Buck BOM**

#### HVQFN48 – 7x7

#### Bluetooth LE Low Power mode option available (32kHz populated)

| Reference                             | Value          |

|---------------------------------------|----------------|

| C38,C49                               | 10uF           |

| C6,C40,C44                            | 1uF            |

| C11,C14,C34,C39,C41,C43               | 0.1uF          |

| C12                                   | 4.7uF          |

| C15,C42                               | 0.22uF         |

| C7                                    | 10nF           |

| C8                                    | 47pF           |

| C48                                   | 12pF           |

| C47                                   | 1.5uF (or 1uF) |

| Printed IFA antenna                   | 2.4GHZ         |

| R1                                    | 22 ohms        |

| L1 (MLZ2012A1R0WTD25)                 | 1uH            |

| , , , , , , , , , , , , , , , , , , , | KW45B41Z       |

| U1                                    | Or             |

|                                       | K32W148        |

| Y3                                    | 32MHz          |

| Y4                                    | 32.768 kHz     |

| <b>RF matching</b> (whatever the RF output power) |        |

|---------------------------------------------------|--------|

| С9                                                | 1 uF   |

| C10                                               | 12 pF  |

| L2 (LQG15HZ15NJ02D)                               | 15 nH  |

| L3 (resistor shunt)                               | 0 ohm  |

| C1 (GCM1555C1H1R1BA16)                            | 1.1 pF |

| L15 ( <i>LQG15WH1N5B02</i> )                      | 1.5nH  |

| C2 (GCM1555C1H2R5BA16)                            | 2.5 pF |

Note: C38,C40, C42, and C46 have different values from the schematic. This is due to the LPC current probe which need bigger decoupling capacitors.

### **DCDC Buck Pin configuration**

#### HVQFN48 – 7x7

| Pin Number | Pin Name         | Buck connection                                |

|------------|------------------|------------------------------------------------|

| 4          | VDD_IO_ABC       | 1.71-3.6V                                      |

| 6          | VDD_SWITCH       | 1.71-3.6V                                      |

| 7          | VOUT_SWITCH      | Floating (when not used)                       |

| 15         | VDD_LDO_CORE     | 1.15-3.6V                                      |

|            |                  | 0.95-1.1V (Mid drive) or                       |

| 16         | VDD_CORE1        | 1.04-1.21V (Normal drive or safe mode voltage) |

| 20         | DCDC_LX          | 1.71-3.6V                                      |

| 21         | VDD_DCDC         | 1.8-3.6V                                       |

| 22         | VOUT_SYS/VDD_SYS | Floating (except the decoupling capacitor)     |

| 29         | VDD_ANA          | 1.71-3.6V                                      |

| 30         | VREF_OUT         | Floating (except the decoupling capacitor)     |

| 34         | VDD_RF           | 1.175-2.5V                                     |

| 36         | VPA_2P4GHZ       | 0.9-2.4V                                       |

|            |                  | 0.95-1.1V (Mid drive) or                       |

| 41         | VDD_CORE2        | 1.04-1.21V (Normal drive or safe mode voltage) |

| 49         | VSS              | GND                                            |

| 19         | VSS_DCDC         | GND                                            |

Warning: → Do not connect the pin VDD\_SYS (internal connection)

Bluetooth LE Low Power mode option available (32kHz populated)

### Layout example on buck mode HVQFN48 – 7x7

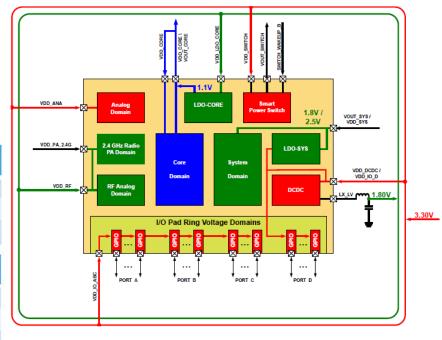

# BUCK MODE NO BLUETOOTH LE LOW POWER MODE

#### **Product in Buck Mode**

#### HVQFN48 – 7x7

### **DCDC Buck BOM**

#### HVQFN48 – 7x7

#### No Bluetooth LE Low Power mode.

| Reference                             | Value          |                                                   |       |

|---------------------------------------|----------------|---------------------------------------------------|-------|

| C38,C49                               | 10uF           |                                                   |       |

| C6,C40,C44                            | 1uF            |                                                   |       |

| C11,C14,C34,C39,C41,C43               | 0.1uF          |                                                   |       |

| C12                                   | 4.7uF          |                                                   |       |

| C15,C42                               | 0.22uF         |                                                   |       |

| C7                                    | 10nF           | <b>RF matching</b> (whatever the RF output power) |       |

| C8                                    | 47pF           | C9                                                | 1 ul  |

| C48                                   | 12pF           | C10                                               | 12 p  |

| C47                                   | 1.5uF (or 1uF) | L2 (LQG15HZ15NJ02D)                               | 15 n  |

| Printed IFA antenna                   | 2.4GHZ         | L3 (resistor shunt)                               | 0 oh  |

| R1                                    | 22 ohms        | C1 (GCM1555C1H1R1BA16)                            | 1.1 p |

| L1 (MLZ2012A1R0WTD25)                 | 1uH            | L15 ( <i>LQG15WH1N5B02</i> )                      | 1.5n  |

| · · · · · · · · · · · · · · · · · · · | KW45B41Z       | C2 (GCM1555C1H2R5BA16)                            | 2.5 p |

| U1                                    | Or             |                                                   |       |

|                                       | K32W148        |                                                   |       |

| Y3                                    | 32MHz          |                                                   |       |

|                                       |                |                                                   |       |

Note: C38,C40, C42, and C46 have different values from the schematic. This is due to the LPC current probe which need bigger decoupling capacitors.

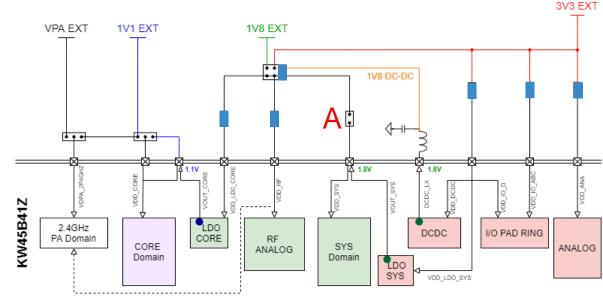

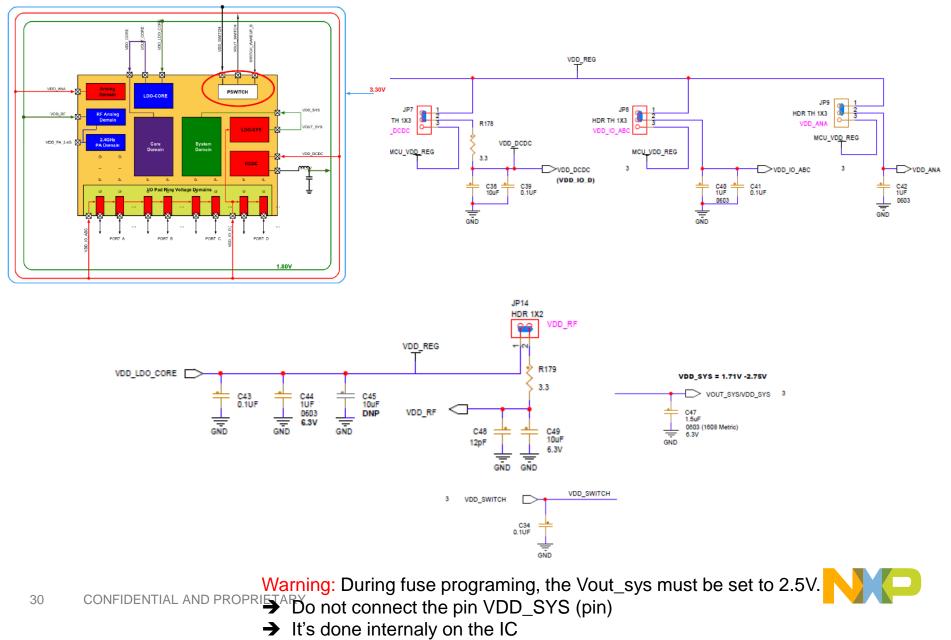

**PMIC SUPPLY**

#### KW45 – PMIC supply

HVQFN48 – 7x7

#### Possibility of Bluetooth LE Low Power mode active.

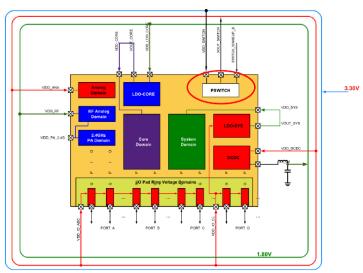

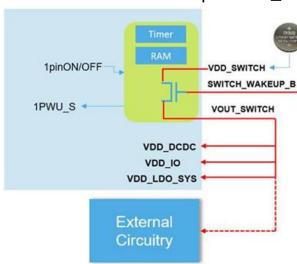

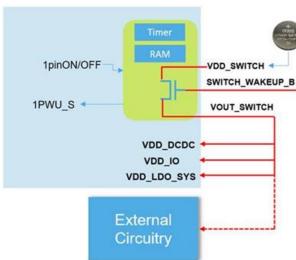

## **POWER SWITCH**

### KW45-EVK – Power config diagram – Power Switch

#### SMART POWER SWITCH LOW POWER USE CASE <100 NA TOTAL LEAKAGE CURRENT

#### Configuration

- · External 3.3 V supply to Smart Power Switch

- Power switch output connected to

- DCDC, LDO-SYS, VDD\_ANA and VDD\_IO

- DCDC output connected to

- LDO-CORE, VDD\_RF

#### Usage

- Software can disable smart power switch in Deep Power Down modes

- Reenable Switch from:

- External wakeup pin

- Internal timer with FRO16K

- Standby RAM regulator support 8KB RAM retention

- Can configure to disable during manufacturing process that disconnects battery from device in order to maximize battery life

Warning: During fuse programing, the Vout sys must be set to 2.5V. → Do not connect the pin VDD\_SYS (pin) jumper on A

#### SMART POWER SWITCH ULTRA LOW POWER & FLEXIBLE

#### Performance

- <100 nA (typ) leakage current when OFF (no RAM retention, timer disabled)</li>

- <700 nA (typ) leakage current when OFF (8KB RAM retention + timer )

- 40 mA active output current capability

#### Flexible

- Can be used to power partial or entire chip supply

- Can be used to power external circuits saving BOM costs

#### Configurable power control

- One external wakeup pin (SWITCH\_WAKEUP\_B) to enable power switch

- Internal Timer timeout (from 7.8125ms to 1s) to enable power switch

- Dedicated register bits to control power switch in Low Power mode / Active mode

#### Data storage

Support up to 8KB RAM retention

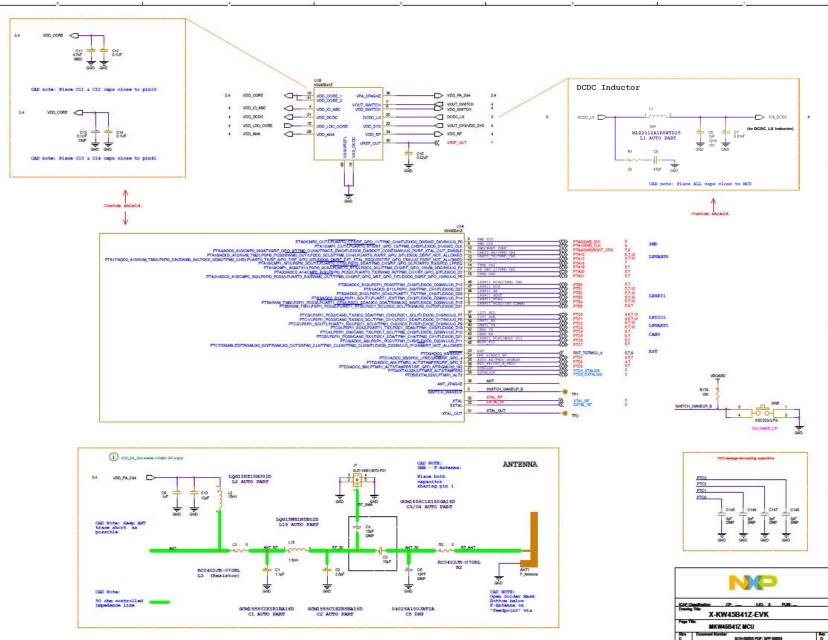

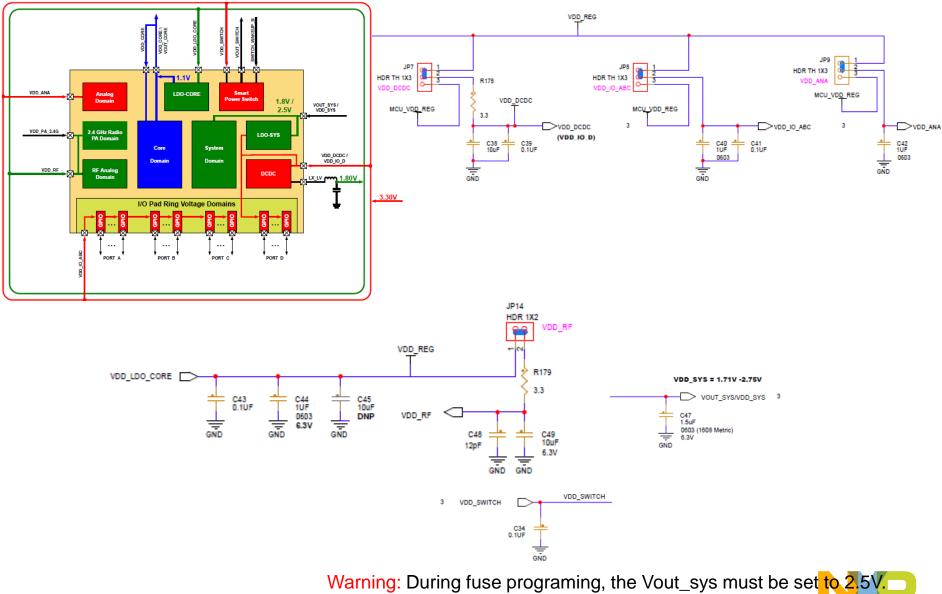

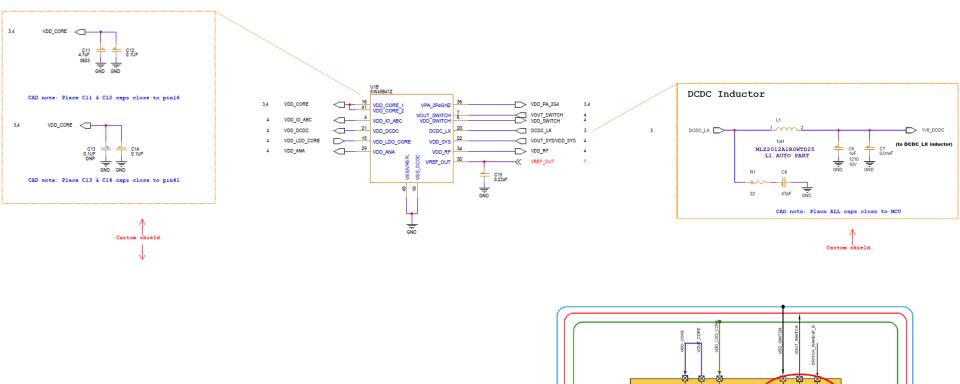

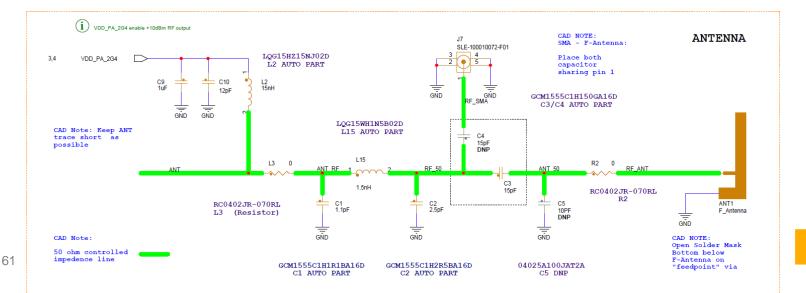

#### **Power switch schematic**

#### HVQFN48 - 7x7

DCDC buck mode with the possibility of Bluetooth LE Low Power mode active.

#### **Product in Power Switch (Buck)**

#### VDD\_00RE < 3.4 47%F UHB KW45041Z DCDC Inductor CAD note: Flace Cl1 & Cl2 caps close to pin16 3.4 VDD. CORE VPA 2PAGIC > VDD PA 204 3.4 OUT\_SWITCH VOD IO ADC 1 V00\_0\_A00 L1 3.4 V00\_0085 21 100\_0000 VDD\_DCDC -AL 2000 DODG LX DCDC\_LX 🕞 D 1V8\_DCDC VDD\_LDD\_CORE VOD\_SYS VOUT\_SYSVDD\_SYS 1.14 (to DCDC\_LX inductor) VCD\_ANA C13 0.1UF > VDD\_RF C6 1uF 1210 GND C14 0.1UF VDD\_ANA VDD RF MLZ2012A1R0WTD25 C7 0.01uF L1 AUTO PART VREF\_CUT 30 VRDF\_OUT 0.224 C8 CAD note: Flace Cl3 & Cl4 caps close to pin41 and 47pF 22 CAD note: Place ALL caps close to MCU -14 Custom a PTADOMPO, OUT CRUMPTE CTORE GPO 11TPNC, OHMFLEXOD, DO PTANOMPI, OUT CRUMPTE, RTORE, GPO, 10TPND, OHMFL 190 PTANADCO ALOCMPO NUATXORF\_GPO STEND PTANSADCO ALONYM THELPSPE POSSEWING OUT PTA:0 PTA:0 PTA:0 PTA:0 PTA:0 PTA:0 PTA:0 LPURAD PTAIT/ADCO A13NVM THEAPSPIE SIN/FAMO INLPECO PTA21(ADC0 A15)CMP0 (N2)LPS/PI0 PTD: PTD: PTD: PTD: PTD: PTD: 5.7 5.7,40 5.7,40 5.7,40 5.7,40 5.7,40 5.7,40 5.7,40 LPSPI1 PTENNIN THOLPSPH POSS 522 PTCOLPSPH POSSICAND TX0000 SDATTEN1 CHOLEDOCI LPI2C1 1471 LPURATI CNID PTCZORABLEDTRGMUKO INSTRGMUKO OUTSGFAG CUNTPMI CUK RST\_TGTMCU\_S PTDJ PTDJ PTDJ PTDJ RTDJ\_STALSOK PTDG\_EXTALSOK 2.51 45,7 PTD-SACCO 05/0PC PTDNADCO BOLPTMR1 ALT ANT ANT IPAGET 35 SWITCH, WAKEUP, D -------KTAL, RF XTAL EXTAL A KINA W KTAL OUT XTAL OUT ---(1) VIEL PA\_20H ANALH + VOSIN RF CALLS CAD NOTE: SNA - F-Antenna ANTENNA LOGI SHELSNJO2D Place both 3.4 V00,PA264 capacitor sharing pin 1 C10 107 GCM1555C1#150GA16D C3/C4 AUTO PART -- and LOGISWEINSDO2D LIS AUTO PART CAD Note: Entrane abort CH 15pF DNP L15 12 R2 0 70.79 DC ANT 03 10eF 1.50 RC0402JR-070RL R2 RC0402JR-070RL L3 (Resistor) C2 2.5p CS 10PF C1 1.1pF 눎 CAD Note 50 ohm controlled impedance line CAP CI CP: IUC: X QCM15555C1H1R1BA16D GOM 555C1 122558416D 04025A100JAT2A X-KW45B41Z-EVK C1 AUTO PART C2 AUTO PART CS DNP MKW45B41Z MCU ACHURTER DIE- SEE AND

**HVQFN48 – 7x7**

April 19, 2022

liter 1

#### **Evaluation board – Recommendation**

Recommanded DCDC inductor (L1): MLZ2012A1R0WTD25

#### **Evaluation board – Recommendation - Buck**

### Power Switch (DCDC Buck) BOM HVQFN48 – 7x7

Bluetooth LE Low Power mode option available (32kHz populated)

| Reference                             | Value          |

|---------------------------------------|----------------|

| C38,C49                               | 10uF           |

| C6,C40,C44                            | 1uF            |

| C11,C14,C27,C34,C36,C39,C41,C43       | 0.1uF          |

| C12                                   | 4.7uF          |

| C15,C42                               | 0.22uF         |

| C7                                    | 10nF           |

| C8                                    | 47pF           |

| C48                                   | 12pF           |

| C47                                   | 1.5uF (or 1uF) |

| Printed IFA antenna                   | 2.4GHZ         |

| R1                                    | 22 ohms        |

| L1 (MLZ2012A1R0WTD25)                 | 1uH            |

| , , , , , , , , , , , , , , , , , , , | KW45B41Z       |

| U1                                    | Or             |

|                                       | K32W148        |

| Y3                                    | 32MHz          |

| Y4                                    | 32.768 kHz     |

| RF matching (whatever the RF output power) |        |  |  |

|--------------------------------------------|--------|--|--|

| C9                                         | 1 uF   |  |  |

| C10                                        | 12 pF  |  |  |

| L2 (LQG15HZ15NJ02D)                        | 15 nH  |  |  |

| L3 (resistor shunt)                        | 0 ohm  |  |  |

| C1 (GCM1555C1H1R1BA16)                     | 1.1 pF |  |  |

| L15 ( <i>LQG15WH1N5B02</i> )               | 1.5nH  |  |  |

| C2 (GCM1555C1H2R5BA16)                     | 2.5 pF |  |  |

Note: C38,C40, C42, and C46 have different values from the schematic. This is due to the LPC current probe which need bigger decoupling capacitors.

### Power Switch (DCDC buck) Pin configuration HVQFN48WF – 7x7

| Pin Number | Pin Name         | Bypass connection                              |

|------------|------------------|------------------------------------------------|

| 4          | VDD_IO_ABC       | 1.71-3.6V                                      |

| 5          | SWITCH_WAKEUP_B  | 0-0.7V (connected to ground to be active)      |

| 6          | VDD_SWITCH       | 1.71-3.6V                                      |

| 7          | VOUT_SWITCH      | 1.71-3.6V                                      |

| 15         | VDD_LDO_CORE     | 1.15-3.6V                                      |

|            |                  | 0.95-1.1V (Mid drive) or                       |

| 16         | VDD_CORE1        | 1.04-1.21V (Normal drive or safe mode voltage) |

| 20         | DCDC_LX          | 1.71-3.6V                                      |

| 21         | VDD_DCDC         | 1.8-3.6V                                       |

| 22         | VOUT_SYS/VDD_SYS | Floating (except the decoupling capacitor)     |

| 29         | VDD_ANA          | 1.71-3.6V                                      |

| 30         | VREF_OUT         | Floating (except the decoupling capacitor)     |

| 34         | VDD_RF           | 1.175-2.5V                                     |

| 36         | VPA_2P4GHZ       | 0.9-2.4V                                       |

|            |                  | 0.95-1.1V (Mid drive) or                       |

| 41         | VDD_CORE2        | 1.04-1.21V (Normal drive or safe mode voltage) |

| 49         | VSS              | GND                                            |

| 19         | VSS_DCDC         | GND                                            |

Warning: During fuse programing, the Vout sys must be set to 2.5V.

→ Do not connect the pin VDD\_SYS (internal connection)

Note: To reach RF output power higher than +7dBm, VPA\_2P4GHZ must be supplied to 2.425V minimum.

### Layout example on buck mode HVQFN48WF – 7x7

# **KW45 ONLY HVQFN40 – 6X6**

### KW45 - EVK – Power config diagram – DCDC Bypass

#### Configuration

- Bypass DCDC

- External 3.3 V for LDO-CORE, LDO-SYS, VDD\_IO

- Generate VPA\_2PGHZ internally from VDD\_RF

| Regulator  | Output                | Input voltage range  |                      |

|------------|-----------------------|----------------------|----------------------|

| DCDC       | 1.8V to 2.5 V         | 1.8V to 2.5 V        |                      |

| LDO-SYS    | 1.8 / 2.5 V 1.8~3.6 V |                      |                      |

| LDO-CORE   | 1.05 / 1.1 / 1.15 V   | 1.71~3.6 V (Enable); | 0.84~1.21 V (Bypass) |

| VPA_2P4GHZ | Z Tx Output<br>Power  | VPA source           | VDD_RF               |

| 0.9 V      | +1.8 dBm              |                      | 1.175 ~3.6 V         |

| 1.525 V    | +7 dBm                | External or internal | 1.8 ~ 3.6 V          |

| 2.2 V      | +10 dBm               |                      | 2.475~3.6 V          |

**Note:** VPA\_2P4GHZ voltage depends on Tx power level. It can be powered externally or internally.

VPA\_2P4GHZ voltage depends on Tx power level. It can be powered externally or internally. For internal generation, VDD\_RF voltage must be equal to or exceed VPA + 275 mV.

Warning: During fuse programing, the Vout sys must be set to 2.5V. → Do not connect the pin VDD\_SYS (internal connection)

### **KW45 - DCDC Bypass Schematic**

HVQFN40 – 6x6

DCDC bypass mode with the possibility of Bluetooth LE Low Power mode active.

### KW45 - DCDC Bypass BOM

HVQFN40 – 6x6

Bluetooth LE Low Power mode option available (32kHz populated)

| Reference               | Value          |

|-------------------------|----------------|

| C40,C44                 | 1uF            |

| C11,C14,C34,C39,C41,C43 | 0.1uF          |

| C12                     | 4.7uF          |

| C15,C42                 | 0.22uF         |

| C48                     | 12pF           |

| C12,C44                 | 4.7uF          |

| C47                     | 1.5uF (or 1uF) |

| C38,C49                 | 10uF           |

| Printed IFA antenna     | 2.4GHZ         |

| U1                      | KW45B41Z<br>Or |

|                         | K32W148        |

| Y3                      | 32MHz          |

| Y4                      | 32.768 kHz     |

|                         |                |

| RF matching (whatever the RF output power) |        |  |  |  |

|--------------------------------------------|--------|--|--|--|

| C9                                         | 1 uF   |  |  |  |

| C10                                        | 12 pF  |  |  |  |

| L2 (LQG15HZ15NJ02D)                        | 15 nH  |  |  |  |

| L3 (resistor shunt)                        | 0 ohm  |  |  |  |

| C1 (GCM1555C1H1R1BA16)                     | 1.1 pF |  |  |  |

| L15 (LQG15WH1N5B02)                        | 1.5nH  |  |  |  |

| C2 (GCM1555C1H2R5BA16)                     | 2.5 pF |  |  |  |

Note: C38,C40, C42, and C46 have different values from the schematic. This is due to the LPC current probe which need bigger decoupling capacitors.

### **DCDC Buck Pin configuration**

### HVQFN48 – 7x7

| Pin Number | Pin Name         | Bypass connection                              |

|------------|------------------|------------------------------------------------|

| 4          | VDD_IO_ABC       | 1.71-3.6V                                      |

| 6          | VDD_SWITCH       | 1.71-3.6V                                      |

| 7          | VOUT_SWITCH      | Floating (when not used)                       |

| 15         | VDD_LDO_CORE     | 1.15-3.6V                                      |

|            |                  | 0.95-1.1V (Mid drive) or                       |

| 16         | VDD_CORE1        | 1.04-1.21V (Normal drive or safe mode voltage) |

| 20         | DCDC_LX          | 1.71-3.6V                                      |

| 21         | VDD_DCDC         | 1.8-3.6V                                       |

| 22         | VOUT_SYS/VDD_SYS | Floating (except the decoupling capacitor)     |

| 29         | VDD_ANA          | 1.71-3.6V                                      |

| 30         | VREF_OUT         | Floating (except the decoupling capacitor)     |

| 34         | VDD_RF           | 1.175-2.5V                                     |

| 36         | VPA_2P4GHZ       | 0.9-2.4V                                       |

|            |                  | 0.95-1.1V (Mid drive) or                       |

| 41         | VDD_CORE2        | 1.04-1.21V (Normal drive or safe mode voltage) |

| 49         | VSS              | GND                                            |

| 19         | VSS_DCDC         | GND                                            |

Warning: → Do not connect the pin VDD\_SYS (internal connection)

Bluetooth LE Low Power mode option available (32kHz populated)

### KW45 - DCDC Bypass Pin configuration HVQFN40 – 6x6

| Pin Number | Pin Name         | Bypass connection                                                 |

|------------|------------------|-------------------------------------------------------------------|

| 3          | VDD_IO_ABC       | 1.71-3.6V                                                         |

| 5          | VDD_SWITCH       | 1.71-3.6V                                                         |

| 6          | VOUT_SWITCH      | Floating (when not used)                                          |

| 13         | VDD_LDO_CORE     | 1.15-3.6V                                                         |

|            |                  | 0.95-1.1V (Mid drive) or<br>1.04-1.21V (Normal drive or safe mode |

| 14         | VDD_CORE1        | voltage)                                                          |

| 18         | DCDC_LX          | floating                                                          |

| 19         | VDD_DCDC         | 1.8-3.6V                                                          |

| 20         | VOUT_SYS/VDD_SYS | Floating (except the decoupling capacitor)                        |

| 24         | VDD_ANA          | 1.71-3.6V                                                         |

| 25         | VREF_OUT         | Floating (except the decoupling capacitor)                        |

| 28         | VDD_RF           | 1.175-2.5V                                                        |

| 30         | VPA_2P4GHZ       | 0.9-2.4V                                                          |

|            |                  | 0.95-1.1V (Mid drive) or<br>1.04-1.21V (Normal drive or safe mode |

| 33         | VDD_CORE2        | voltage)                                                          |

| 41         | VSS              | GND                                                               |

| 17         | VSS_DCDC         | GND                                                               |

Warning: Do not connect the pin VDD\_SYS (internal connection)

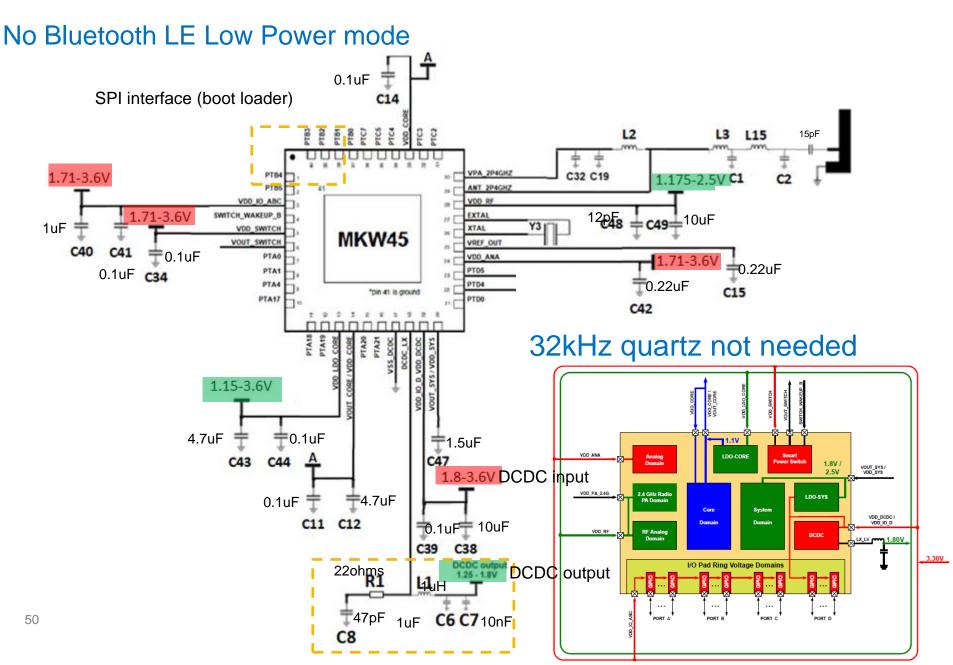

# BYPASS MODE NO BLUETOOTH LE LOW POWER MODE

#### **KW45 - DCDC Bypass Schematic HVQFN40 – 6x6** No Bluetooth LE Low Power mode 0.1uF = C14 L2 L3 L15 15pF 1.71-3.6V C32 C19 VPA 2P4GH2 1.175-2.5V C2 PTB4 C1 PTB INT 2P4GHZ VOD RF VDD IO AB 1.71-3.6V SWITCH\_WAKEUP\_B EXTAL **C48 = C49 =** 10uF 1uF Y31 XTAL VDD\_SWITCH **MKW45** VOUT SWITCH VREF\_OUT 15 C40 0.1uF Ŧ 0.1uF PTA0 VDD ANA 24 1.71-3.6\ =0.22uF PTA1 PTD5 C34 28 = 0.22uF PTA4 PTD4 C15 22 "pin 41 is ground PTA17 PTDO 21 32kHz quartz not needed ۵. 2 2 PTA18 1.5uF PTA21 PTAS PTA2 8 1.15-3.6V 1.1V DO-CORI 1.8V / 2.5V VOUT\_SYS / VDD\_SYS 0.1uF 1uF 荢 1.5uF VDD PA 2.40 C47 VDD\_DCDC / VDD\_IO\_D C43 C44 VDD\_R 1.8-3.6V DCDC 2.5V I/O Pad Ring Voltage Domains C11 C12 ... 0.1uF 4.7uF C39 C38 0.1uF 10uF

# KW45 - DCDC Bypass BOMNoNoBluetooth LE Low Power mode

#### Reference Value 1uF C40 10uF C38 0.1uF C11,C14,C34,C39,C41,C43,C44 0.22uF C15,C42 12pF C48 4.7uF C12 1.5uF (or 1uF) C47 22uF C49 2.4GHZ Printed IFA antenna KW45B41Z U1 32MHz Y3

| RF matching (whatever the RF output power) |        |  |  |

|--------------------------------------------|--------|--|--|

| С9                                         | 1 uF   |  |  |

| C10                                        | 12 pF  |  |  |

| L2 (LQG15HZ15NJ02D)                        | 15 nH  |  |  |

| L3 (resistor shunt)                        | 0 ohm  |  |  |

| C1 (GCM1555C1H1R1BA16)                     | 1.1 pF |  |  |

| L15 (LQG15WH1N5B02)                        | 1.5nH  |  |  |

| C2 (GCM1555C1H2R5BA16)                     | 2.5 pF |  |  |

HVQFN40 – 6x6

Note: C38,C40, C42, and C46 have different values from the schematic. This is due to the LPC current probe which need bigger decoupling capacitors.

### **KW45 - DCDC Buck Schematic**

### HVQFN40 - 6x6

#### Possibility of Bluetooth LE Low Power mode active.

### **KW45 - DCDC Buck Schematic**

### HVQFN40 - 6x6

#### Possibility of Bluetooth LE Low Power mode active.

#### FLEXIBLE POWER ARCHITECTURE – DCDC CONFIGURATION RECOMMENDED SOLUTION FOR TRADEOFF BETWEEN COST AND POWER EFFICIENCY Configuration

- External 3.3V for DCDC , VDD\_IO, LDO-SYS

- LDO-CORE, VDD\_RF come from DCDC output

- Generate VPA\_2PGHZ internally from VDD\_RF

| Regulator | Output |                                        | Input voltage range  |                        |                      |

|-----------|--------|----------------------------------------|----------------------|------------------------|----------------------|

| DCDC      | 1.25   | 25/1.35/1.8/2.5 V                      |                      | 1.71~3.6V; >= 0        | output + 500 mV      |

| LDO-SYS   |        | 1.8 / 2.5 V                            |                      | 1.8~3                  | 3.6 V                |

| LDO-CORE  | 1      | 1.05 / 1.1 / 1.15 V 1.71~3.6 V (Enable |                      | 1.71~3.6 V (Enable); ( | 0.84~1.21 V (Bypass) |

| VPA_2P4GH | z      | Tx Output<br>Power                     |                      | VPA source             | VDD_RF               |

| 0.9 V     |        | +1.8 dBm                               |                      |                        | 1.175 ~3.6 V         |

| 1.525 V   |        | +7 dBm                                 | External or internal |                        | 1.8 ~ 3.6 V          |

| 2.2.V     |        | +10 dBm                                |                      |                        | 2.475~3.6 V          |

VPA\_2P4GHZ voltage depends on Tx power level. It can be powered externally or internally. For internal generation, VDD\_RF voltage must be equal to or exceed VPA + 275 mV.

### KW45 - DCDC Buck BOM

### HVQFN40 – 6x6

### Bluetooth LE Low Power mode possible.

| Reference               | Value          |

|-------------------------|----------------|

| C38,C49                 | 10uF           |

| C6,C40,C44              | 1uF            |

| C11,C14,C34,C39,C41,C43 | 0.1uF          |

| C12                     | 4.7uF          |

| C15,C42                 | 0.22uF         |

| C7                      | 10nF           |

| C8                      | 47pF           |

| C48                     | 12pF           |

| C47                     | 1.5uF (or 1uF) |

| Printed IFA antenna     | 2.4GHZ         |

| R1                      | 22 ohms        |

| L1 (MLZ2012A1R0WTD25)   | 1uH            |

| U1                      | KW45B41Z       |

| Y3                      | 32MHz          |

| Y4                      | 32.768 kHz     |

| <b>RF matching</b> (whatever the RF output power) |        |  |  |  |

|---------------------------------------------------|--------|--|--|--|

| C9                                                | 1 uF   |  |  |  |

| C10                                               | 12 pF  |  |  |  |

| L2 (LQG15HZ15NJ02D)                               | 15 nH  |  |  |  |

| L3 (resistor shunt)                               | 0 ohm  |  |  |  |

| C1 (GCM1555C1H1R1BA16)                            | 1.1 pF |  |  |  |

| L15 ( <i>LQG15WH1N5B02</i> )                      | 1.5nH  |  |  |  |

| C2 (GCM1555C1H2R5BA16)                            | 2.5 pF |  |  |  |

Note: C38,C40, C42, and C46 have different values from the schematic. This is due to the LPC current probe which need bigger decoupling capacitors.

### **KW45 - DCDC Buck Pin configuration**

### HVQFN40 - 6x6

| Pin Number | Pin Name         | Bypass connection                                                 |

|------------|------------------|-------------------------------------------------------------------|

| 3          | VDD_IO_ABC       | 1.71-3.6V                                                         |

| 5          | VDD_SWITCH       | 1.71-3.6V                                                         |

| 6          | VOUT_SWITCH      | Floating (when not used)                                          |

| 13         | VDD_LDO_CORE     | 1.15-3.6V                                                         |

|            |                  | 0.95-1.1V (Mid drive) or<br>1.04-1.21V (Normal drive or safe mode |

| 14         | VDD_CORE1        | voltage)                                                          |

| 18         | DCDC_LX          | 1.71-3.6V                                                         |

| 19         | VDD_DCDC         | 1.8-3.6V                                                          |

| 20         | VOUT_SYS/VDD_SYS | Floating (except the decoupling capacitor)                        |

| 24         | VDD_ANA          | 1.71-3.6V                                                         |

| 25         | VREF_OUT         | Floating (except the decoupling capacitor)                        |

| 28         | VDD_RF           | 1.175-2.5V                                                        |

| 30         | VPA_2P4GHZ       | 0.9-2.4V                                                          |

|            |                  | 0.95-1.1V (Mid drive) or<br>1.04-1.21V (Normal drive or safe mode |

| 33         | VDD_CORE2        | voltage)                                                          |

| 41         | VSS              | GND                                                               |

| 17         | VSS_DCDC         | GND                                                               |

Warning: Do not connect the pin VDD\_SYS (internal connection)

# BUCK MODE NO BLUETOOTH LE LOW POWER MODE

### **KW45 - DCDC Buck Schematic**

### HVQFN40 – 6x6

### **KW45 - DCDC Buck BOM**

### HVQFN40 – 6x6

### No Bluetooth LE Low Power mode.

| Reference               | Value          |

|-------------------------|----------------|

| C38,C49                 | 10uF           |

| C6,C40,C44              | 1uF            |

| C11,C14,C34,C39,C41,C43 | 0.1uF          |

| C12                     | 4.7uF          |

| C15                     | 0.22uF         |

| C7                      | 10nF           |

| C8                      | 47pF           |

| C48                     | 12pF           |

| C47                     | 1.5uF (or 1uF) |

| Printed IFA antenna     | 2.4GHZ         |

| R1                      | 22 ohms        |

| L1 (MLZ2012A1R0WTD25)   | 1uH            |

|                         | KW45B41Z       |

| U1                      | Or             |

|                         | K32W148        |

| Y3                      | 32MHz          |

|                         |                |

| <b>RF matching</b> (whatever the RF output power) |        |

|---------------------------------------------------|--------|

| С9                                                | 1 uF   |

| C10                                               | 12 pF  |

| L2 (LQG15HZ15NJ02D)                               | 15 nH  |

| L3 (resistor shunt)                               | 0 ohm  |

| C1 (GCM1555C1H1R1BA16)                            | 1.1 pF |

| L15 (LQG15WH1N5B02)                               | 1.5nH  |

| C2 (GCM1555C1H2R5BA16)                            | 2.5 pF |

Note: C38,C40, C42, and C46 have different values from the schematic. This is due to the LPC current probe which need bigger decoupling capacitors.

**PMIC SUPPLY**

### KW45 – PMIC supply

### HVQFN40 – 6x6

#### Possibility of Bluetooth LE Low Power mode active.

## **POWER SWITCH**

## KW45 EVK – Power config diagram – Power Switch

#### <100 NA TOTAL LEAKAGE CURRENT</pre>

#### Configuration

- · External 3.3 V supply to Smart Power Switch

- Power switch output connected to

- DCDC, LDO-SYS, VDD\_ANA and VDD\_IO

- DCDC output connected to

- LDO-CORE, VDD\_RF

#### Usage

- Software can disable smart power switch in Deep Power Down modes

- Reenable Switch from:

- External wakeup pin

- Internal timer with FRO16K

- Standby RAM regulator support 8KB RAM retention

- Can configure to disable during manufacturing process that disconnects battery from device in order to maximize battery life

Warning: During fuse programing, the Vout sys must be set to 2.5V. → Do not connect the pin VDD\_SYS (pin) jumper on A

#### SMART POWER SWITCH ULTRA LOW POWER & FLEXIBLE

#### Performance

- <100 nA (typ) leakage current when OFF (no RAM retention, timer disabled)</li>

- <700 nA (typ) leakage current when OFF (8KB RAM retention + timer )

- 40 mA active output current capability

#### Flexible

- Can be used to power partial or entire chip supply

- Can be used to power external circuits saving BOM costs

#### Configurable power control

- One external wakeup pin (SWITCH\_WAKEUP\_B) to enable power switch

- Internal Timer timeout (from 7.8125ms to 1s) to enable power switch

- Dedicated register bits to control power switch in Low Power mode / Active mode

#### Data storage

Support up to 8KB RAM retention

### **KW45 - Power switch Schematic**

### HVQFN40 - 6x6

#### Possibility of Bluetooth LE Low Power mode active.

### **KW45 - DCDC Buck BOM**

### HVQFN40 – 6x6

| Reference                   | Value          |

|-----------------------------|----------------|

| C38,C49                     | 10uF           |

| C6,C40,C44                  | 1uF            |

| C11,C14,C34,C36,C39,C41,C43 | 0.1uF          |

| C12                         | 4.7uF          |

| C15,C42                     | 0.22uF         |

| C7                          | 10nF           |

| C8                          | 47pF           |

| C48                         | 12pF           |

| C47                         | 1.5uF (or 1uF) |

| Printed IFA antenna         | 2.4GHZ         |

| R1                          | 22 ohms        |

| L1 (MLZ2012A1R0WTD25)       | 1uH            |

| U1                          | KW45B41Z       |

| Y3                          | 32MHz          |

| Y4                          | 32.768 kHz     |

| <b>RF matching</b> (whatever the RF output power) |        |

|---------------------------------------------------|--------|

| C9                                                | 1 uF   |

| C10                                               | 12 pF  |

| L2 (LQG15HZ15NJ02D)                               | 15 nH  |

| L3 (resistor shunt)                               | 0 ohm  |

| C1 (GCM1555C1H1R1BA16)                            | 1.1 pF |

| L15 ( <i>LQG15WH1N5B02</i> )                      | 1.5nH  |

| C2 (GCM1555C1H2R5BA16)                            | 2.5 pF |

Note: C38,C40, C42, and C46 have different values from the schematic. This is due to the LPC current probe which need bigger decoupling capacitors.

### KW45 – Power Switch Pin configuration HVQFN40 – 6x6

| Pin Number | Pin Name         | Bypass connection                                     |  |

|------------|------------------|-------------------------------------------------------|--|

| 3          | VDD_IO_ABC       | 1.71-3.6V                                             |  |

| 5          | VDD_SWITCH       | 1.71-3.6V,<br>Connected to decoupling capacitor 0.1uF |  |

| 6          | VOUT_SWITCH      | 1.71-3.6V,<br>Connected to decoupling capacitor 0.1uF |  |

| 13         | VDD_LDO_CORE     | 1.15-3.6V                                             |  |

|            |                  | 0.95-1.1V (Mid drive) or                              |  |

| 14         | VDD_CORE1        | 1.04-1.21V (Normal drive or safe mode voltage)        |  |

| 18         | DCDC_LX          | 1.71-3.6V                                             |  |

| 19         | VDD_DCDC         | 1.8-3.6V                                              |  |

| 20         | VOUT_SYS/VDD_SYS | Floating (except the decoupling capacitor)            |  |

| 24         | VDD_ANA          | 1.71-3.6V                                             |  |

| 25         | VREF_OUT         | Floating (except the decoupling capacitor)            |  |

| 28         | VDD_RF           | 1.175-2.5V                                            |  |

| 30         | VPA_2P4GHZ       | 0.9-2.4V                                              |  |

|            |                  | 0.95-1.1V (Mid drive) or                              |  |

| 33         | VDD_CORE2        | 1.04-1.21V (Normal drive or safe mode voltage)        |  |

| 41         | VSS              | GND                                                   |  |

| 17         | VSS_DCDC         | GND                                                   |  |

Warning: Do not connect the pin VDD\_SYS (internal connection)

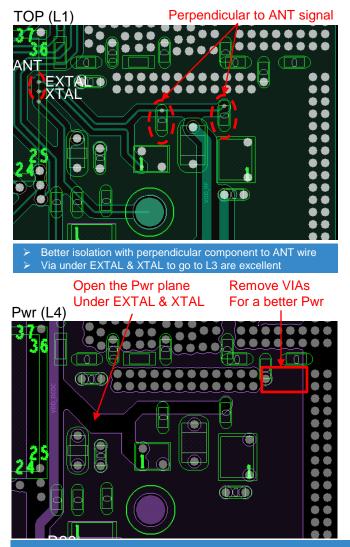

## LAYOUT RECOMMENDATION

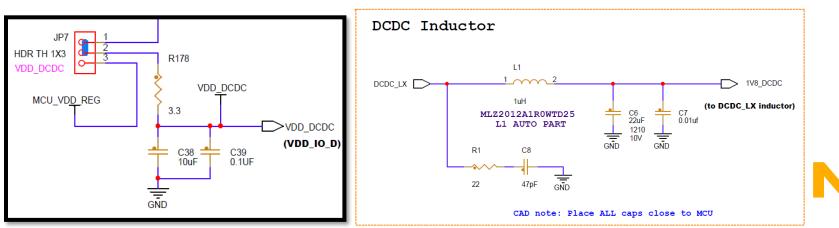

### **Evaluation board – HW Recommendation - DCDC**

- 1. C38 & C39 must be as close as possible to the DCDC Vdd but not so much for the DCDC vss. Recommend is to place them with the LX connection to the inductor passing between their terminals. It is really critical to reduce the loop formed by the DCDC VDD/VSS pins and those capacitors. Please add more vias to the ground plane.

- 2. In a similar fashion place **C7** in a way that it's connection to the inductor **L1** is where it is now and VSS connection gets close to the chip. Adding vias to better connect vss to the ground plane will help.

- 3. It is interesting to move **C6** closer to the IC and add vias as on this example.

- 4. **C8** in a similar fashion as **C7** may be helpful for emissions >300MHz.

- L1 is 1uH for the KW45/K32W148 (iso 10uH on KW35/36/37/38/39 reference design)

#### Note:

Having short connection and small area loops is the most important thing to contain any emissions. Bringing those caps closer to the chip will be helpful. And having the ground plane well preserved underneath those components (as it is on the current layout) will greatly help reduce the effect of the inductor not being really close to the chip.

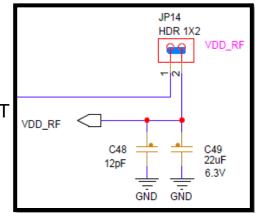

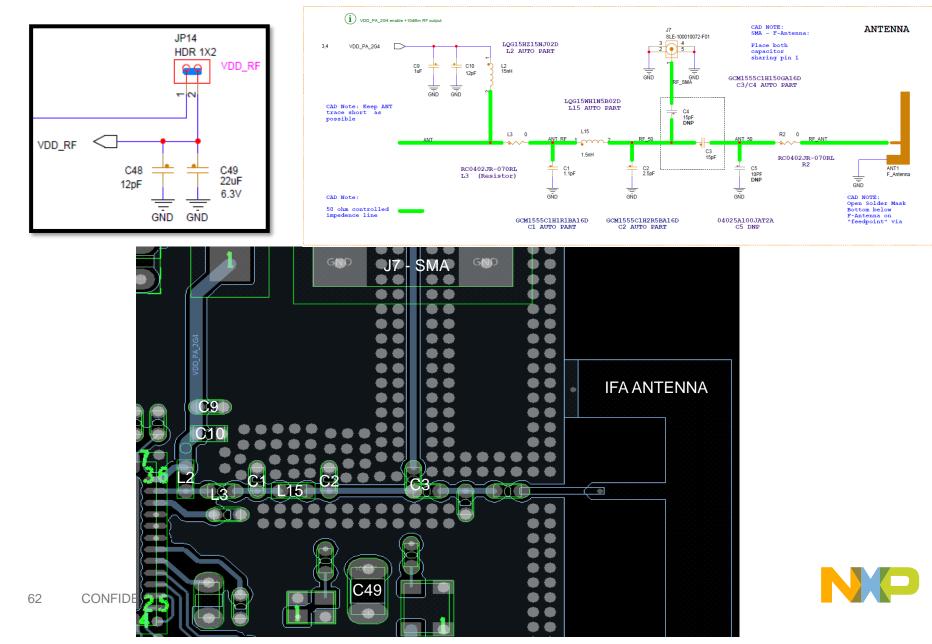

### **Evaluation board – HW Recommendation - Radio**

- The value capacitor C48 used for an RF short are 12pF

- C10 must be as close to L2 as possible

- C49=22uF on VDD\_RF could be placed as DNP

- The pull up inductor L2 placement must follow the layout example

- The **antenna matching** components must be at minimum spacing to the DUT and each other, as on the current layout.

- **C48** needs to be placed in order to have the best isolation with ANT\_RF line. VDDRF line needs to be isolated with VDDRF\_line. Please copy the current

layout

- Need isolation between VDDRF and UART signals.

- VDD\_PA\_2g4 needs to be isolated vs PTC0

- General comment: The power planes which create huge fat nets are for the VDD\_ANA and VDD\_SYS. No benefit to reduce the power plane.

### **Evaluation board – HW Recommendation - Radio**

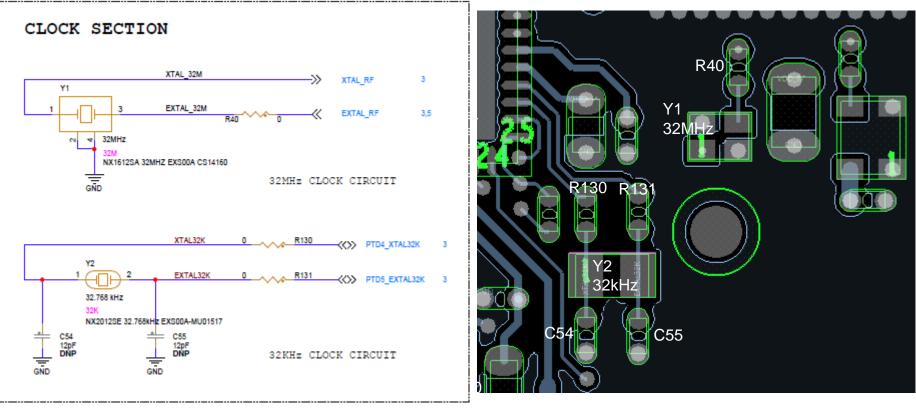

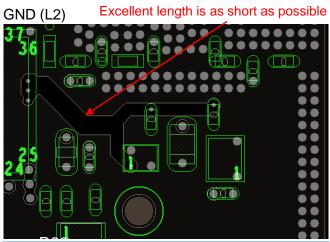

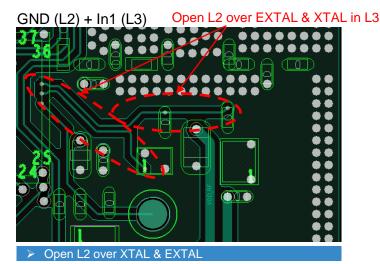

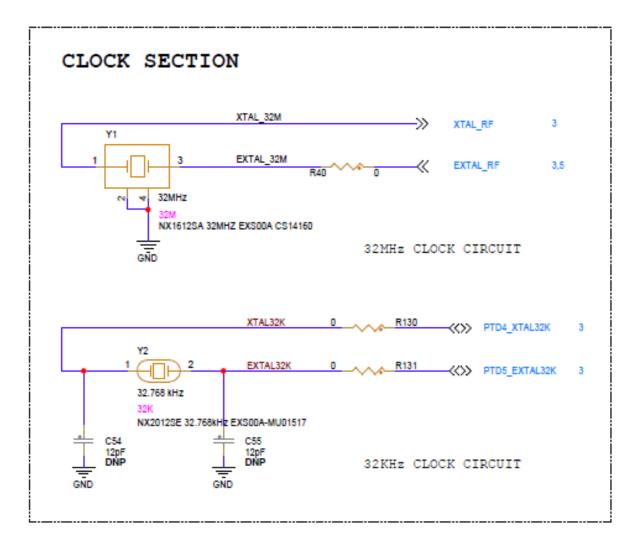

### **Evaluation board – HW Recommendation - Clocks**

- 32MHz & 32kHz wire length must be as symetric as possible

- 32kHz quartz is not necessary to be as closed as possible from the DUT (KW45/K32W148)

### **Evaluation board – HW Recommendation - Clocks**

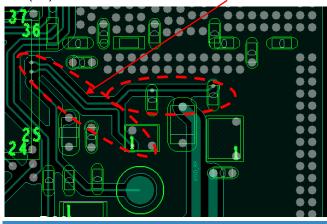

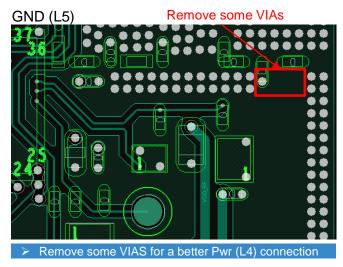

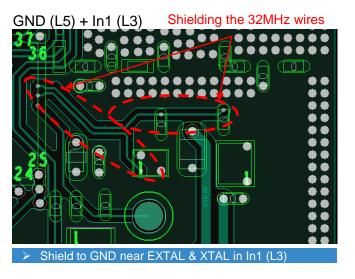

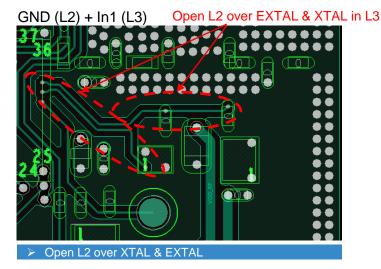

Special focus on 32MHz wires to help on a very good layout.

Under EXTAL & XTAL Pwr net need to be open to reduce coupling capacitance to PWR

Some GND vias can be removed to have a better connection of PWR signal

- To reduce capacitance on EXTAL & XTAL GND plane can be opened over XTAL & EXTAL wires

- The shielding is already present on TOP (L1) being GND in these area

#### In1 (L3)

#### Shielding area

To avoid coupling XTAL with XTAL\_OUT a shield is applied

To avoid any coupling on XTAL a shield on TOP is applied

### **Evaluation board – HW Recommendation - Clocks**

- Special focus on 32MHz wires to help on a very good layout.

# COMPLEMENTARY INFORMATION

### Recommendation

KW45/K32W1 requires signed firmware to be loaded into the NBU. This happens through the Bootloader. **PTC2 and PTC3 are the UART connection to the Bootloader**. We recommend to have an option to connect them to a UART to USB converter (for PC connection).

NXP recommend to have a way to **pull PTA4 to logic high** in order to enter the device in **bootloader mode**.

Make sure that everything connected to PORTD is at the same voltage as VDD\_IO\_D. Same for PORTA, B and C and VDD\_IO\_ABC.

### Recommendation connection for unused IOs HVQFN48WF – 7x7

#### Table 54. Recommended connection for unused interfaces

| Pin Type                    | Pin Function  | Recommendation                        | Comments                                                                                                                                                                                                                                                                          |

|-----------------------------|---------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power                       | VDD_LDO_CORE  | Connect to<br>VOUT_CORE and VSS       | When the LDO is not used, the input and output should be connected together and tied to ground through a 10 k $\Omega$ resistor. The regulator should also be disabled in software.                                                                                               |

| Power                       | VOUT_CORE     | Connect to<br>VDD_LDO_CORE and<br>VSS | When the LDO is not used, the input and output should be connected together and tied to ground through a 10 k $\Omega$ resistor. The regulator should also be disabled in software.                                                                                               |

| Power                       | VOUT_SYS      | Connect to VDD_IO_D                   | When the LDO is bypassed, the input and<br>output should be connected together and tied to<br>an external supply. The regulator should also be<br>disabled in software.                                                                                                           |

| Power                       | VDD_DCDC      | Ground                                | When the DCDC is not used, the input should be tied to VSS through a 10 k $\Omega$ resistor.                                                                                                                                                                                      |

| Power                       | DCDC_LX       | Float                                 | The input VDD_DCDC should be tied to VSS with 10 Kohm                                                                                                                                                                                                                             |

| Power                       | VDD_IO_D      | Must be powered                       | VDD_IO_D is used to power parts of the system<br>power controller (SPC) and must be powered to<br>use the chip. If LDO_SYS is not being used,<br>then tie VDD_IO_D to VOUT_SYS and supply<br>power from an external source. The regulator<br>should also be disabled in software. |

| Power<br>NFIDENTIAL AND PRO | VDD_PA_2.4GHz | Float                                 | VDD_PA_2.4GHz is always driven, either<br>from internal LDO sourced by VDD_RF, or<br>from external supply.                                                                                                                                                                        |

### Recommendation connection for unused IOs HVQFN48WF – 7x7

|          | Power           | VDD_SWITCH    | Must be powered                         | Powers FRO16 and a portion of RAM.                                                                                                                                                                                                                              |

|----------|-----------------|---------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Power           | VOUT_SWITCH   | Float                                   |                                                                                                                                                                                                                                                                 |

|          | Power           | VDD_IO_ABC    | Must be powered                         | VDD_IO_ABC powers the mux logic for PORTA,<br>PORTB and PORTC. It must be powered during<br>POR. The recommendation is to keep it<br>powered, but it can be connected to the output<br>of the Smart Power Switch and be left floating in<br>shelf storage mode. |

|          | Power           | VDD_ANA       | Float                                   |                                                                                                                                                                                                                                                                 |

|          | Power           | VREFH         | Always connect to VDD_ANA potential     | Always connect to VDD_ANA potential                                                                                                                                                                                                                             |

|          | Power           | VREFL         | Always connect to VSS potential         | Always connect to VSS potential                                                                                                                                                                                                                                 |

|          | Power           | VSS_ANA       | Always connect to VSS potential         | Always connect to VSS potential                                                                                                                                                                                                                                 |

|          | Power           | VSS_DCDC      | Always connect to VSS potential         | Always connect to VSS potential                                                                                                                                                                                                                                 |

|          | Power           | VSS_RF        | Always connect to VSS potential         | Always connect to VSS potential                                                                                                                                                                                                                                 |

|          | Analog/non-GPIO | ADCn_x        | Float                                   |                                                                                                                                                                                                                                                                 |

|          | Analog/non-GPIO | VREF_OUT      | Float                                   | Analog output - Float                                                                                                                                                                                                                                           |

|          | Analog/non-GPIO | TAMPERx       | Float                                   |                                                                                                                                                                                                                                                                 |

|          | Analog/non-GPIO | RTC_WAKEUP_B  | Float                                   |                                                                                                                                                                                                                                                                 |

|          | Analog/non-GPIO | RTC_RTCCLKOUT | Float                                   |                                                                                                                                                                                                                                                                 |

|          | Analog/non-GPIO | EXTAL32K      | Float                                   |                                                                                                                                                                                                                                                                 |

|          | Analog/non-GPIO | XTAL32K       | Float                                   | Analog output - Float                                                                                                                                                                                                                                           |

|          | Analog/non-GPIO | EXTAL_32M     | Float                                   |                                                                                                                                                                                                                                                                 |

|          | Analog/non-GPIO | XTAL_32M      | Float                                   | Analog output - Float                                                                                                                                                                                                                                           |

|          | GPIO/Analog     | PTx/CMPn_INx  | Float                                   | Float (default is analog input)                                                                                                                                                                                                                                 |

|          | GPIO/Digital    | PTD1/NMI_b    | $10k\Omega$ pullup or disable and float | Pull high or disable in PCR & FOPT and float                                                                                                                                                                                                                    |

| CONFIDEN | GPIO/Digital    | PTx           | Float                                   | Float (default is disabled)                                                                                                                                                                                                                                     |

### **Additional information – both packages**

The DTM pins are available for both 48 pins and 40 pins packages. The options are:

48-pin only:

PTA16 - RF\_UART\_SIN PTA17 - RF\_UART\_SOUT PTD1 - RF\_UART\_SIN PTD2 - RF\_UART\_SOUT

Both 40-pin & 48-pin PTA18 – RF\_UART\_SIN PTA19 – RF\_UART\_SOUT PTB2 – RF\_UART\_SIN PTB3 – RF\_UART\_SOUT PTC2 – RF\_UART\_SIN PTC3 – RF\_UART\_SOUT

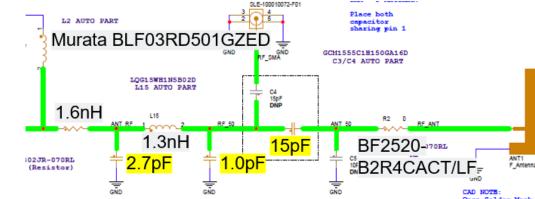

### **RF Matching – Automotive compliant**

#### **RF Matching Goals:**

- Only certified automotive component have been used.

- Ensure sensitivity performance was the focus of this RF Matching

- PASS internal specification regarding 2<sup>nd</sup> and 3<sup>rd</sup> harmonics with 10dBm output power.

- Same Matching for 0dBm, 4dBm, 7dBm and 10dBm output power.

Based on previous 10dBm RF Matching done with LQW inductance we got a good staring point to found the best compromise with those automotive components.

## **Evaluation board – Recommendation**

#### **Evaluation board – Recommendation – Clocks**

## Alternate Y1

For Bluetooth LE and GFSK 32MHz and 26MHz quartz references

| Manufacturer | Series   | Part Number    | Frequency |

|--------------|----------|----------------|-----------|

| NDK          | NX1612SA | EXS00A-CS14160 | 32MHz     |

| NDK          | NX2016SA | EXS00A-CS13636 | 26MHz     |

| Manufacturer | Series   | Part Number    | Frequency |  |

|--------------|----------|----------------|-----------|--|

| NDK          | NX2016SA | EXS00A-CS14161 | 32MHz     |  |

|              |          |                |           |  |

### Alternate Y2

#### For Bluetooth LE and GFSK 32kHz quartz reference

| Manufacturer | Manufacturer Series |                | Frequency |  |

|--------------|---------------------|----------------|-----------|--|

| NDK          | NX2016SA            | EXS00A-MU01517 | 32,768kHz |  |

| NDK          | NX2012SA            | EXS00A-MU00801 | 32,768kHz |  |

## **IO current drive @12mA**

First the list of the specific pins which could handle 12ma current drive instead of 6mA on other IO pins:

- PTA18-19

- PTB4-5

- PTC0-1

- PTC4-5

Note that both the DSEO and DSE1 bits in the control register for that pin must be set in order to get the highest drive strength.

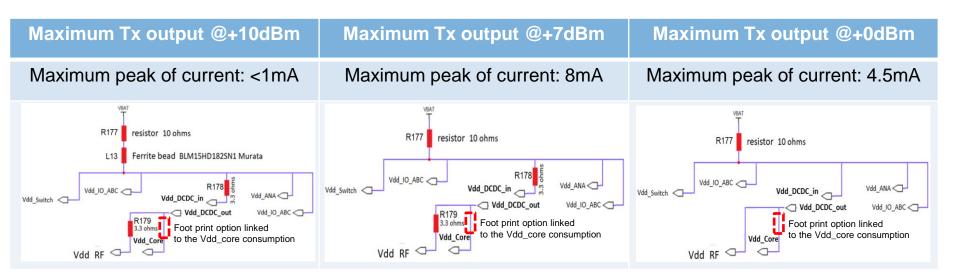

Schematic – Recommandation for coincell only (peak of current below 10mA) Reduced current peak

# DCDC Buck Mode – Coincell – Summary

#### Suitable for battery (coincell) applications only

Solution to reduce the DCDC current peaks and current peaks on Tx signals (+10/+7/+0dBm) during Bluetooth LE events (Advertising, Connect & Scan) is to add serial resistor(s) on different supplies.

It will limit the peaks of current below 10mA and avoid voltage drop on the battery. Voltage drop occurs due to the serial resistor(s) but it never goes down to POR threshold (up to 105°C).

In addition, change the Vbat decoupling capacitor C18 from 10uF to 47uF.

#### **Buck Mode using coincell**

HVQFN48 - 7x7

DCDC LP filter

## **CISPR25** Automotive Chinese certification

#### The KW45-EVK and K32W1-EVK could withstand the CISPR25 certification.

To pass this certification for +10dBm Tx output power, the EVK board needs to be modified as follow:

- Replace the RF matching component values

| RF Service<br>[User band in MHz] | Frequency [MHz] | RBW<br>(kHz) | Limits [dBuV/m] |         |             |

|----------------------------------|-----------------|--------------|-----------------|---------|-------------|

|                                  |                 |              | Peak            | Average | Quasi- Peak |

| Bluetooth                        | 2400 - 2690     | 120          | 44              | 24      | N/A         |

| SIG                              | 3000 - 5000     | ≥1000        | 64              | 44      | N/A         |

| GNSS                             | 5010 - 5030     | 9/10         | N/A             | 16      | N/A         |

| WLAN                             | 5000 - 6000     | ≥1000        | 68              | 48      | N/A         |

| nH             | nH  | рF  | nH  | рF  | рF |

|----------------|-----|-----|-----|-----|----|

| L2             | L3  | C1  | L15 | C2  | C3 |

| BLF03RD501GZED | 1.6 | 2.7 | 1.3 | 1.1 | 15 |

- Replace R2 by a Band Pass Filter at R2. Reference BF2520-B2R4CACT/LF

Note: The default EVK board pass the certification with Tx output power at -15dBm.

## **CISPR25** Automotive Chinese certification

The KW45-EVK and K32W1-EVK could withstand the CISPR25 certification.

EMC HW modification has an impact on the radio performances:

- **Maximum output power** is impacted by **3dB**: +7dBm maximum.

- The **sensitivity** is also impacted by **2dB** whatever the datarate.

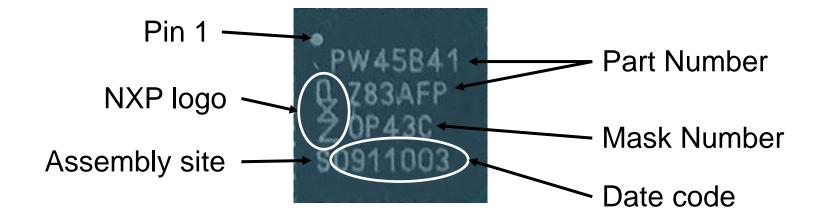

## Annex 1: KW45 marking

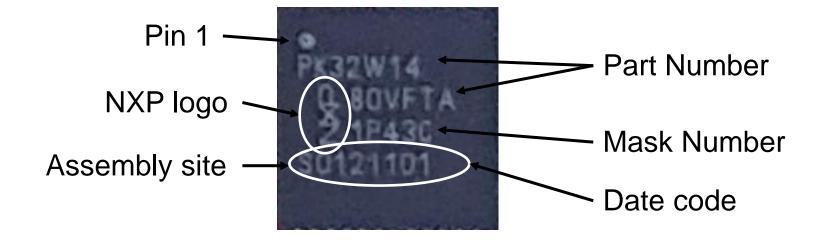

## Annex 2: K32W148 marking

### SECURE CONNECTIONS FOR A SMARTER WORLD