# KW45/K32W1 HARDWARE DESIGN RECOMMENDATION

Christophe MENARD SE team - Caen NOVEMBER 2023

PUBLIC

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2022 NXP B.V.

## RECOMMENDATION FOR A SUCCESSFUL PLATFORM DESIGN: ENTRY POINT

# IC Datasheet & Reference Manual

- Pinout

- Unused pins

- Package (48/40 pins)

5 Pinout

#### 5.1 Pinout Table

| 48HV<br>QFN | 40HV<br>QFN | Pin<br>Name | ALT0 | ALT1 | ALT2                | ALT3 | ALT4               | ALT5         | ALT6                     | ALT7 | ALT8 | ALT9                | ALT1<br>0 | ALT1<br>1 | Wake<br>up       |

|-------------|-------------|-------------|------|------|---------------------|------|--------------------|--------------|--------------------------|------|------|---------------------|-----------|-----------|------------------|

| 2           | 1           | PTB4        |      | PTB4 | LPSP<br>I1_PC<br>S3 |      | LPI2<br>C1_S<br>DA | I3C0_<br>SDA | TRG<br>MUX<br>0_IN0      |      |      | FLEX<br>IO0_<br>D30 |           |           | WUU<br>0_P1<br>5 |

| 3           | 2           | PTB5        |      | PTB5 | LPSP<br>I1_PC<br>S2 | RT1_ | LPI2<br>C1_S<br>CL | I3C0_<br>SCL | TRG<br>MUX<br>0_OU<br>T0 |      |      | FLEX<br>IO0_<br>D31 |           |           |                  |

#### 5.2 Recommended connection for unused analog and digital pins

Table 59 shows the recommended connections for pins if those pins are not used in the customer's application

#### Table 59. Recommended connection for unused interfaces

| Pin Type | Pin Function | Recommendation                  | Comments                                                                                                                                                                            |

|----------|--------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power    | VDD_LDO_CORE | Connect to<br>VOUT_CORE and VSS | When the LDO is not used, the input and output should be connected together and tied to ground through a 10 k $\Omega$ resistor. The regulator should also be disabled in software. |

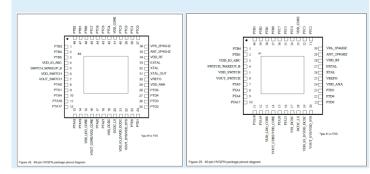

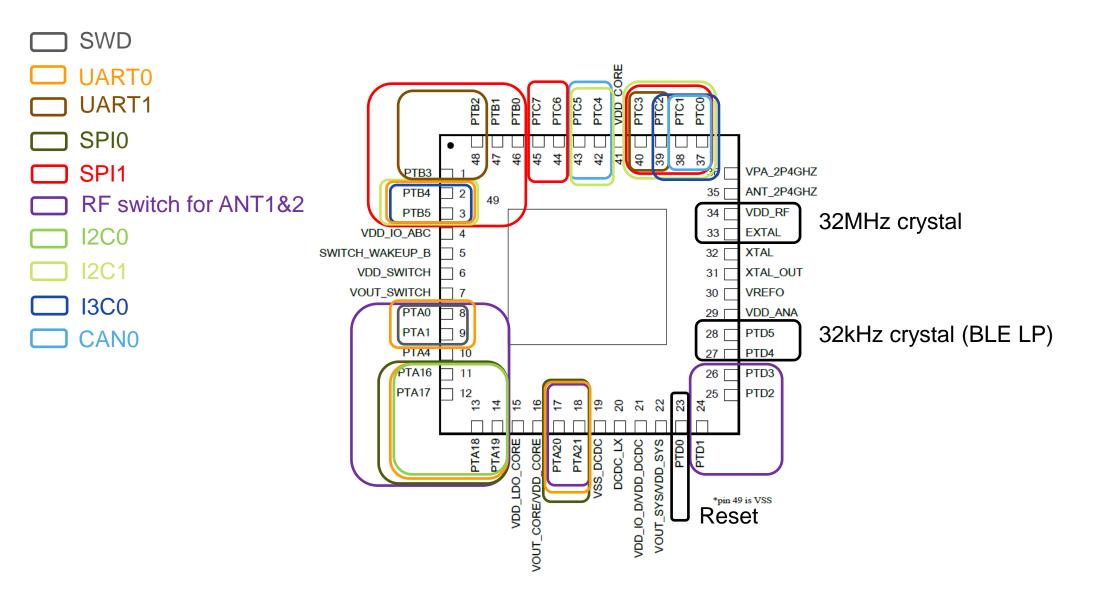

#### 5.3 Pinouts diagram

The below figure shows the pinout diagram for the devices supported by this document. Many signals may be multiplexed onto a single pin. To determine what signals can be used on which pin, see the previous section.

## Design In Check List (schematic & layout part) Hardware Guideline

SCHEMATICS

| Check  | D                                             | SCHEMATICS<br>DESIGN-IN REVIEW CHECK-LIST                                        |                                                                         |                        |       |                     |                    |

|--------|-----------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------|-------|---------------------|--------------------|

| number |                                               |                                                                                  |                                                                         |                        | VININ |                     |                    |

| 10     |                                               | Programming and Debug                                                            |                                                                         |                        |       |                     |                    |

| 10.1   | microcontroler?                               | as the debug connector been connected to the correct I/O on the<br>crocontroler? |                                                                         |                        |       |                     |                    |

| 10.2   | Has a connector bee<br>programming mode?      |                                                                                  | allows the microcontroller to be pu                                     | t into                 |       |                     |                    |

| 10.3   | Is RESET_b proper                             |                                                                                  |                                                                         |                        |       |                     |                    |

| 10.5   | Does the design allo<br>tests?                | w for the poss                                                                   | ibility to perform conducted and ra                                     |                        |       |                     |                    |

| 10.7   | If using Kinetis Boot<br>chosen interface(s)? |                                                                                  | DESIGN-IN                                                               | LAYOU<br>REVIEW        |       | HECK-LIST           |                    |

| 11     |                                               |                                                                                  |                                                                         |                        |       |                     |                    |

| 11.1   | Has the correct type                          |                                                                                  |                                                                         | GENER/                 |       |                     |                    |

|        | to the microcontrolle                         |                                                                                  | Has the number of layers been clea                                      |                        |       |                     |                    |

| 11.2   | Has the flash memo                            | rys 1.2                                                                          | Has the layout been checked versus                                      | s NXP refe             | renc  | e board (KW45-E     | VK or K32W1-       |

| 12     |                                               |                                                                                  | EVK)?                                                                   | 15 10                  |       |                     |                    |

|        | Is the reset pin being                        |                                                                                  | Has the correct PCB material been                                       |                        | -42   |                     |                    |

| 12.1   | pushbutton or some                            | 011                                                                              | Has the correct PCB thicknesses b                                       | een specini<br>RF line |       |                     |                    |

|        | customer read the C                           | 20m                                                                              | Is the RF line well sized for 50 ohm                                    |                        |       | must be calculate   | d according to     |

|        | reset pin as a reset                          |                                                                                  | the transmission line technology ( m                                    |                        |       |                     |                    |

| 12.1   | If the NMI pin is beir                        |                                                                                  | thickness and the PCB material.                                         |                        |       |                     |                    |

|        | immediately on pow                            | er-u                                                                             | If microstrip is used has the trace be                                  | een well iso           | late  | d from the GND pla  | ane?               |

|        |                                               | 2.2                                                                              | If coplanar waveguide is used have                                      | the GND c              | ondu  | ictors been well co | onnected with vias |

|        |                                               |                                                                                  | to the reference GND plane layer ?                                      |                        |       |                     |                    |

|        |                                               | 2.3                                                                              | Is the RF trace as short as possible                                    |                        |       |                     |                    |

|        |                                               | 2.4                                                                              | Have vias been avoided in the RF lin                                    |                        |       |                     |                    |

|        |                                               | 2.5                                                                              | Have the matching components bee<br>("ANT" pin) and oriented the same v |                        |       |                     | W1 RF port         |

|        |                                               |                                                                                  |                                                                         |                        |       |                     |                    |

|        |                                               |                                                                                  |                                                                         |                        |       |                     |                    |

|        |                                               | NXP Semico                                                                       |                                                                         | Document               |       | ber: AN13227        |                    |

|        |                                               | Application N                                                                    | ote                                                                     |                        | Re    | ev. 3, 08/2022      |                    |

|        |                                               |                                                                                  |                                                                         |                        |       |                     |                    |

|        |                                               |                                                                                  |                                                                         |                        |       |                     |                    |

|        |                                               |                                                                                  |                                                                         |                        |       |                     |                    |

|        |                                               |                                                                                  |                                                                         |                        |       |                     |                    |

|        |                                               | Hardwar                                                                          | e Design Considera                                                      | tions f                | or    |                     |                    |

|        |                                               |                                                                                  |                                                                         |                        |       |                     |                    |

|        |                                               | KW45B4                                                                           | 1Z & K32W148 Blue                                                       | tooth l                | LE    |                     |                    |

|        |                                               | Devices                                                                          |                                                                         |                        |       |                     |                    |

|        |                                               | Devices                                                                          |                                                                         |                        |       |                     |                    |

|        |                                               |                                                                                  |                                                                         |                        |       |                     |                    |

|        |                                               |                                                                                  |                                                                         |                        |       |                     |                    |

|        |                                               | 1. Introduct                                                                     | ion                                                                     |                        | nter  | Its                 |                    |

|        |                                               | This application note                                                            | describes Printed Circuit Board 1. Introduc                             |                        |       | 1                   |                    |

|        | (                                             | PCB) design consid                                                               |                                                                         | ents<br>component co   | pper  | laver               |                    |

|        | (                                             | HVQFN-7x7 Pitch (                                                                | .5mm) wettable flank package and 2.1. 4                                 | 8-pin HVQFN            | í     |                     |                    |

|        | 1                                             | KW45B41Z83AFPA                                                                   | and KW45B41Z82AFPA 40-pin 2.2.1                                         | 48-pin HV<br>48-pin HV | OFN   | solder mask         |                    |

|        | 9                                             | QFN (HVQFN-6x6                                                                   |                                                                         | 0-pin HVOFN            |       |                     |                    |

Included are layouts of the component copper layer,

used and the other components on the board

solder mask, and solder paste stencil. These recommendations are guidelines only and may need to be modified depending on the assembly house

OFN package dimensions

details 13

Revision histor

QFN soldering profile.... Design and board layout considerations 2. RF circuit topology and matching...

48-pin HVQFN packag 1.1. 48-pin HVQFN de tails 40-pin HVQFN packag

40-pin HVQFN solder mask 40-pin HVQFN solder paste stenci

QFN problems with excess solder

48-pin HVQFN device marl

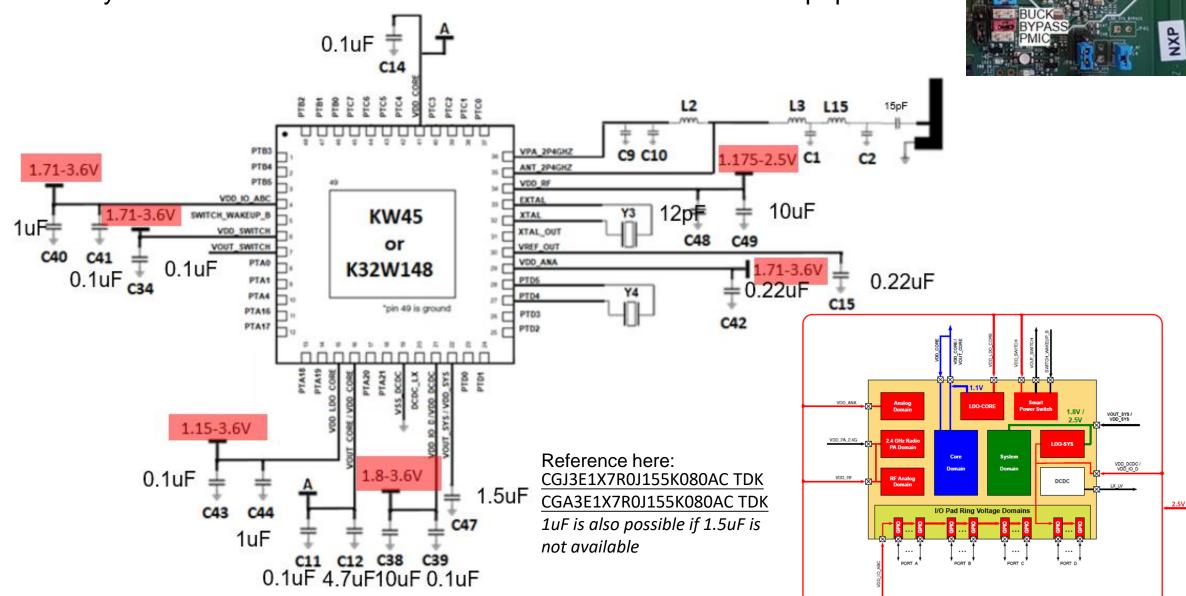

## Minimum BoM

- HVQFN48 7x7

- HVQFN40 6x6

- DCDC modes:

- Buck

- Bypass

- Power Switch

- Low Power or not NXP boards:

- KW45-EVK (sch-50555)

- K32W1-EVK (sch-50701)

#### KW45 & K32W1 MINIMUM BOM

## APPLICATION NOTES AND COLLATERALS

All needed documents are available in the NXP Community <u>The best way to build a PCB using a KW45 or K32W1 first time right</u> <u>- NXP Community</u>

Content: Find the important link to build a PCB using a KW45 and all concerning the radio performances, low power and radio certification (CE/FCC/IC).

Different chapters are available. Focus is done in Hardware part in this document

Hardware:

KW45/K32W1-EVK schematic, layout and gerber files KW45/K32W1-EVK User Manual **AN13227** Hardware Guideline Minimum BoM Design-In check list RF matching Crystal (Trimming) DCDC management guide

# HARDWARE DESIGN RECOMMENDATION

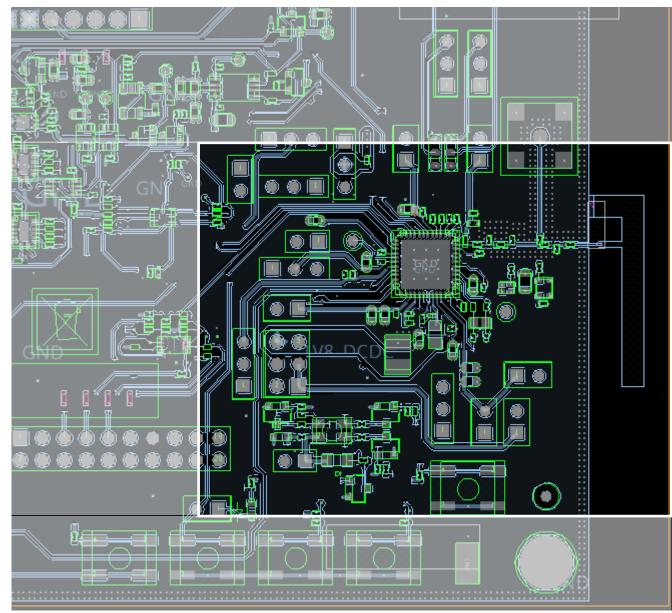

- Layout overview

- DCDC modes

- DCDC inductor

- Radio

- Supplies

- Clocks & Crystals

- Bootloader pins

- Wake Up pins

- Level shifter

- IO current drive

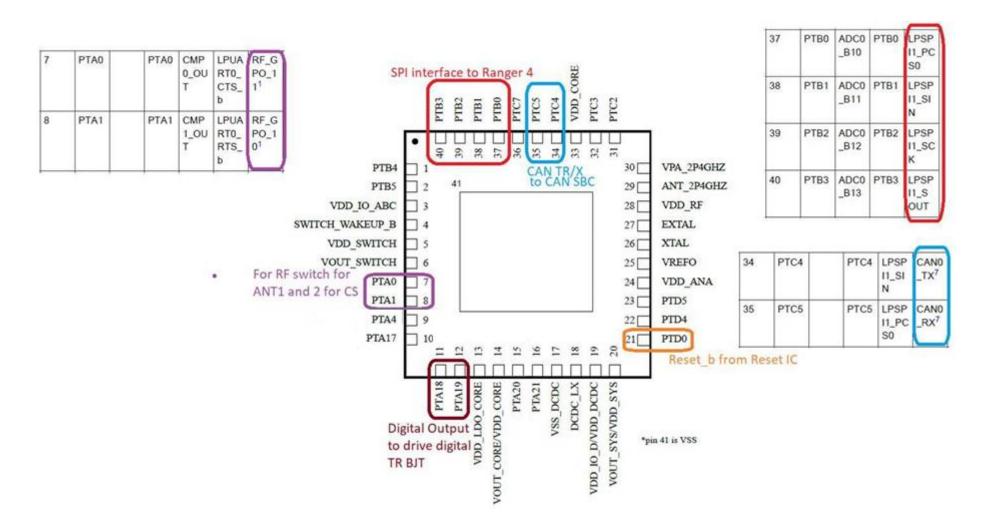

- Peripherals

- DTEST pins

- Battery: Coin Cell

- Unused los

- Layout general rules

- EMC immunity option

- CISPR25

- Jumper configuration on KW45/K32W1-EVK

3

# Layout overview

#### PUBLIC

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2022 NXP B.V.

## **Product Enablement HW**

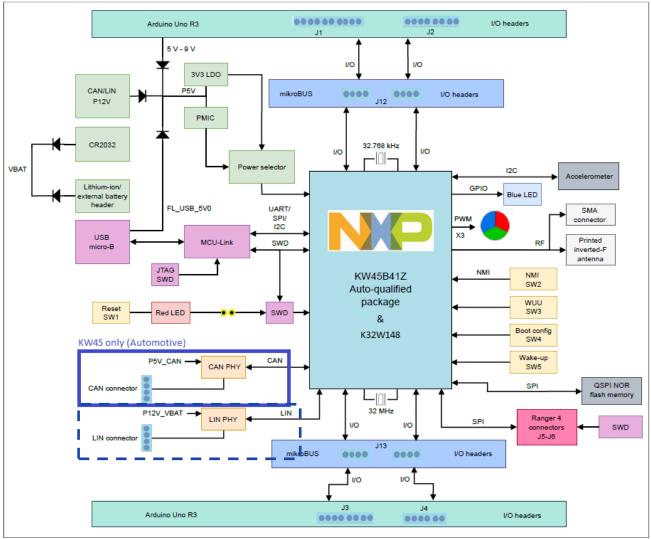

## X-КW45B41Z-EVK (SPF-50555) <u>Schematic & Layout</u> X-К32W148-EVK (SPF-50701)

### KW45 for Automotive

#### KW45B41Z82AFTAx KW45B41Z83AFTAx KW45B41Z82AFPAx KW45B41Z83AFPAx

40HVQFN 48HVQFN 6 x 6 x 0.85 mm; Pitch 7 x 7 x 0.85 mm; Pitch 0.5 mm; Wettable Flanks Flanks

| N32001400011A1 |  |

|----------------|--|

|                |  |

|                |  |

| NP             |  |

K32\//1/80\/FTAT

48HVQFN 7 x 7 x 0.85 mm; Pitch 0.5 mm

## HW RECOMMENDATION – LAYOUT OVERVIEW

Extract from HW guideline:

# DCDC modes

#### PUBLIC

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2022 NXP B.V.

## HW RECOMMENDATION – DCDC BYPASS MODE

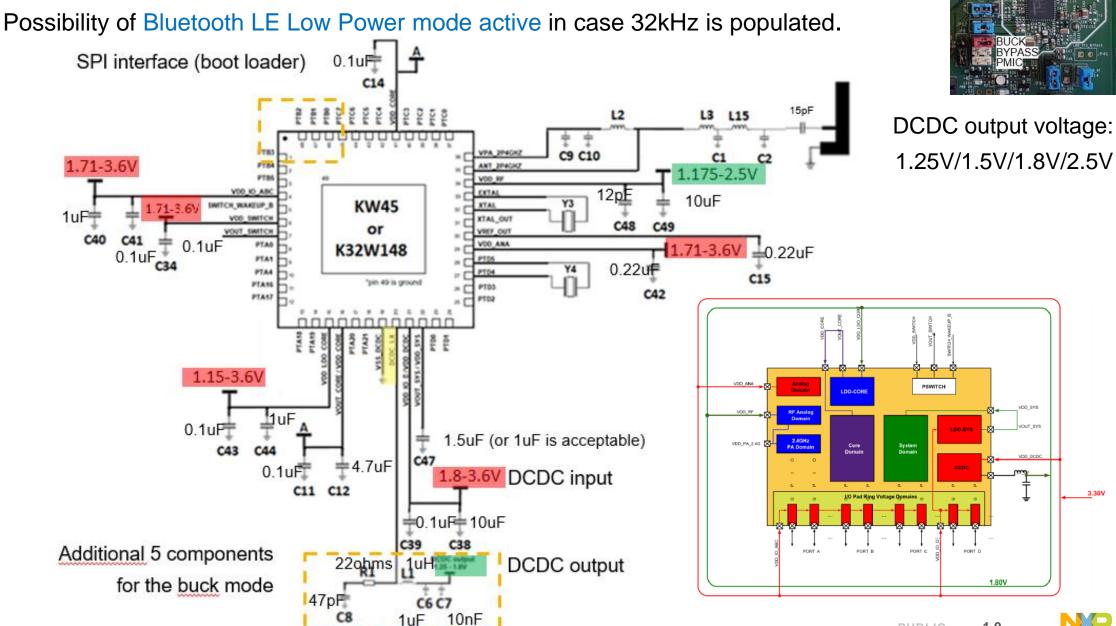

Possibility of Bluetooth LE Low Power mode active in case 32kHz is populated.

## **DCDC BYPASS PIN CONFIGURATION**

| Pin Number | Pin Name         | Bypass connection                              |

|------------|------------------|------------------------------------------------|

| 4          | VDD_IO_ABC       | 1.71-3.6V                                      |

| 6          | VDD_SWITCH       | 1.71-3.6V                                      |

| 7          | VOUT_SWITCH      | Floating (when not used)                       |

| 15         | VDD_LDO_CORE     | 1.15-3.6V                                      |

|            |                  | 0.95-1.1V (Mid drive) or                       |

| 16         | VDD_CORE1        | 1.04-1.21V (Normal drive or safe mode voltage) |

| 20         | DCDC_LX          | Floating (not used)                            |

| 21         | VDD_DCDC         | 1.8-3.6V                                       |

| 22         | VOUT_SYS/VDD_SYS | Floating (except the decoupling capacitor)     |

| 29         | VDD_ANA          | 1.71-3.6V                                      |

| 30         | VREF_OUT         | Floating (except the decoupling capacitor)     |

| 34         | VDD_RF           | 1.175-2.5V                                     |

| 36         | VPA_2P4GHZ       | 0.9-2.4V                                       |

|            |                  | 0.95-1.1V (Mid drive) or                       |

| 41         | VDD_CORE2        | 1.04-1.21V (Normal drive or safe mode voltage) |

| 49         | VSS              | GND                                            |

| 19         | VSS_DCDC         | GND                                            |

Warning: → Do not connect the pin VDD\_SYS (pin) This pin is set to internal 2.5V for fuse programming.

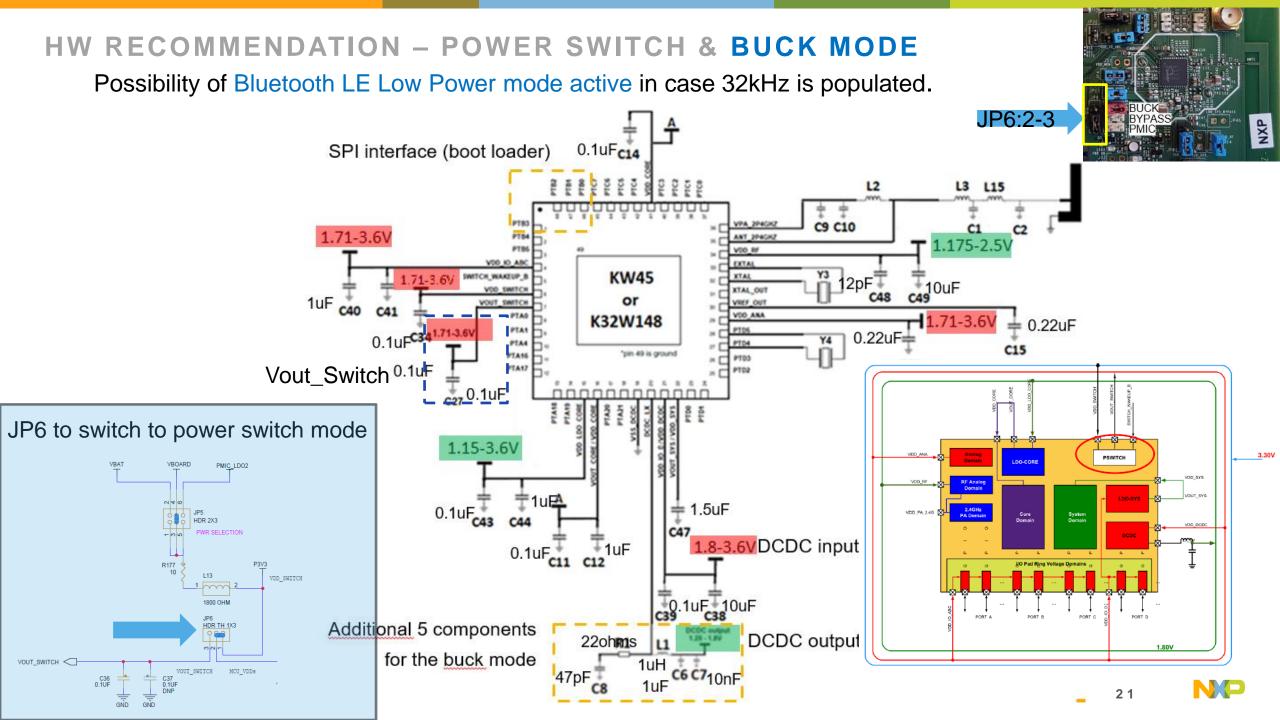

## HW RECOMMENDATION – DCDC BUCK MODE

NXP

10 PUBLIC

NP

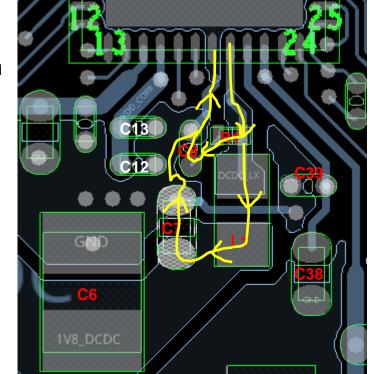

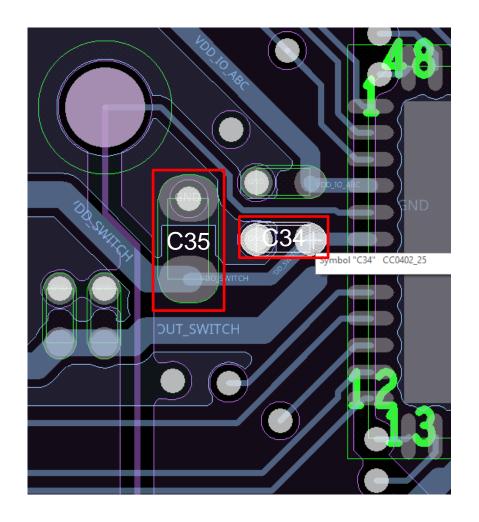

## HW RECOMMENDATION – DCDC LAYOUT

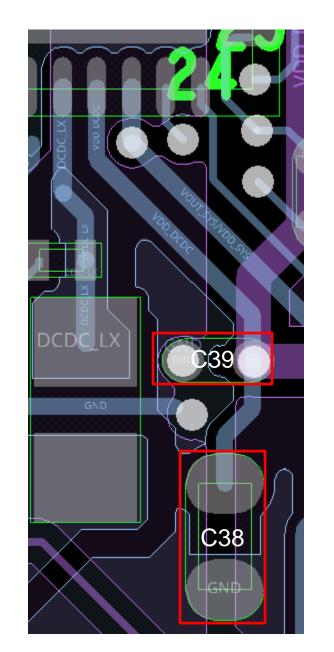

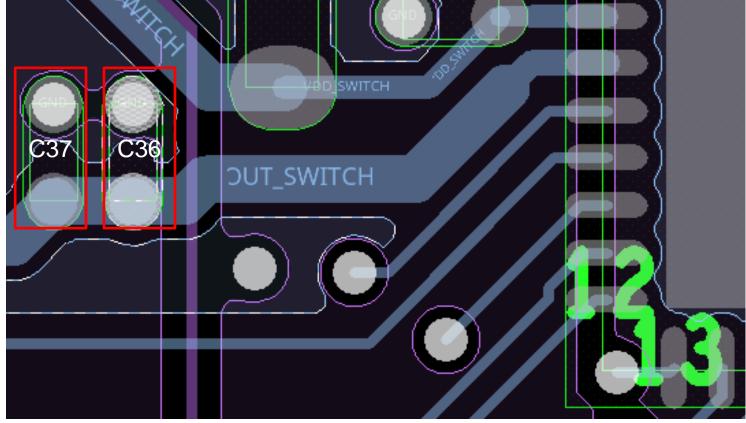

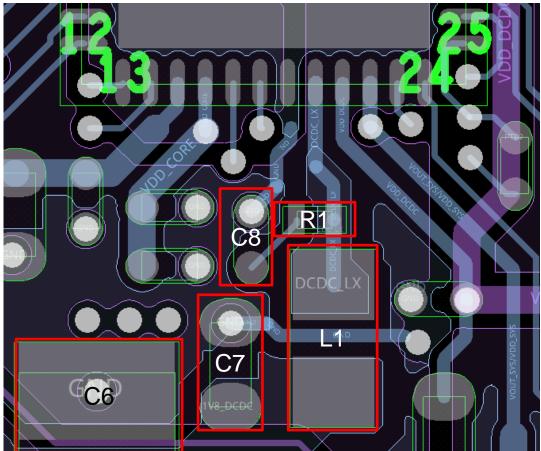

- C38 & C39 must be as close as possible to the DCDC Vdd but not so much for the 1. DCDC vss. Recommend is to place them with the LX connection to the inductor passing between their terminals. It is really critical to reduce the loop formed by the DCDC VDD/VSS pins and those capacitors. Please add more vias to the ground plane.

- 2. In a similar fashion place **C7** in a way that it's connection to the inductor **L1** is where it is now and VSS connection gets close to the chip. Adding vias to better connect vss to the ground plane will help.

- It is interesting to move **C6** closer to the IC and add vias as on this example. 3.

- **C8** in a similar fashion as **C7** may be helpful for emissions >300MHz. 4.

- L1 is 1uH for the KW45/K32W148 (iso 10uH on KW35/36/37/38/39 reference 5. design)

#### Note:

Having short connection and small area loops is the most important thing to contain any emissions. Bringing those caps closer to the chip will be helpful. And having the ground plane well preserved underneath those components (as it is on the current layout) will greatly help reduce the effect of the inductor not being really close to the chip.

> 1V8 DCDC

(to DCDC LX inductor)

C7 0.01uf

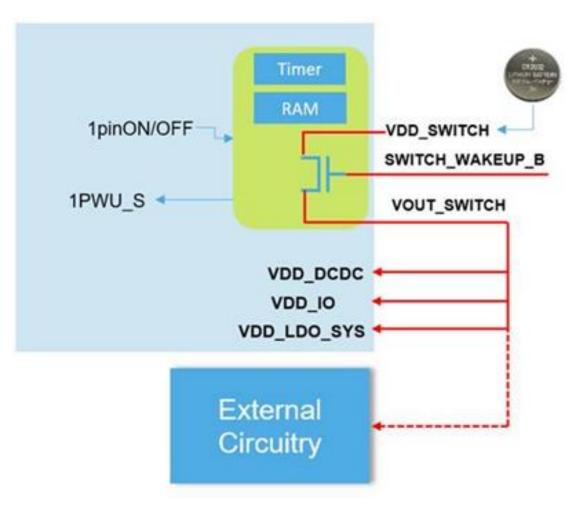

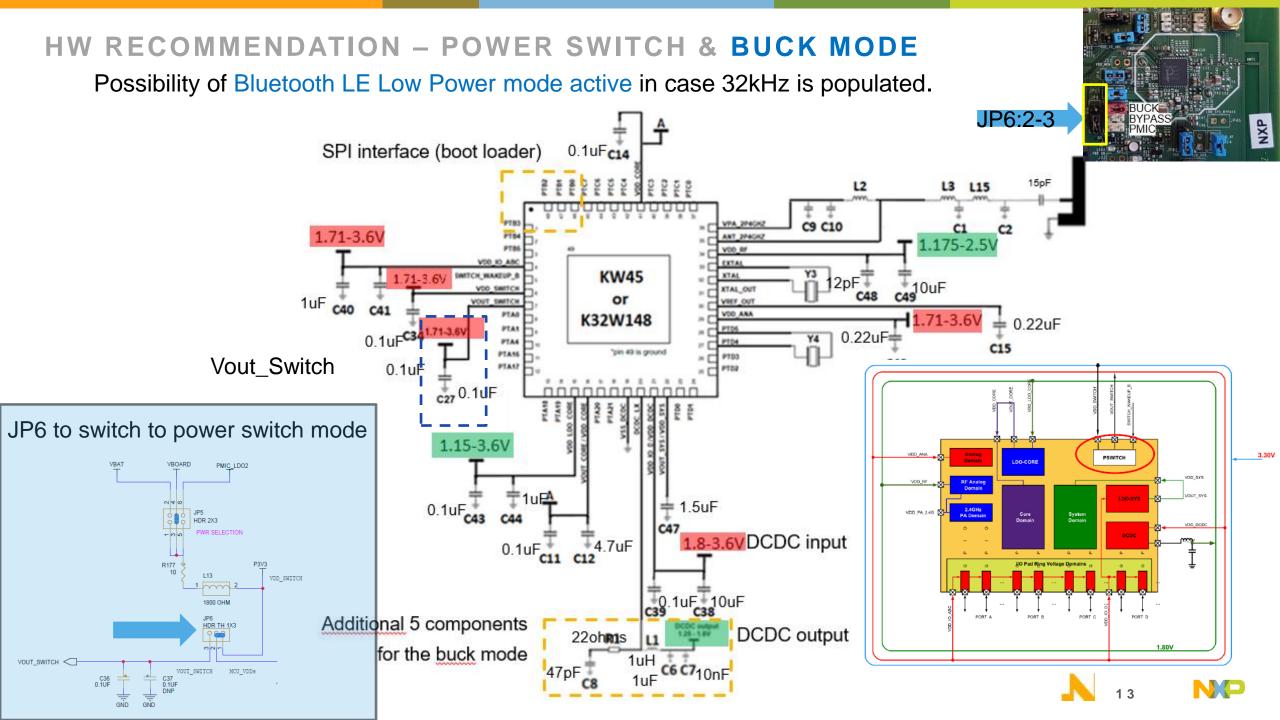

## HW RECOMMENDATION – POWER SWITCH & BUCK MODE

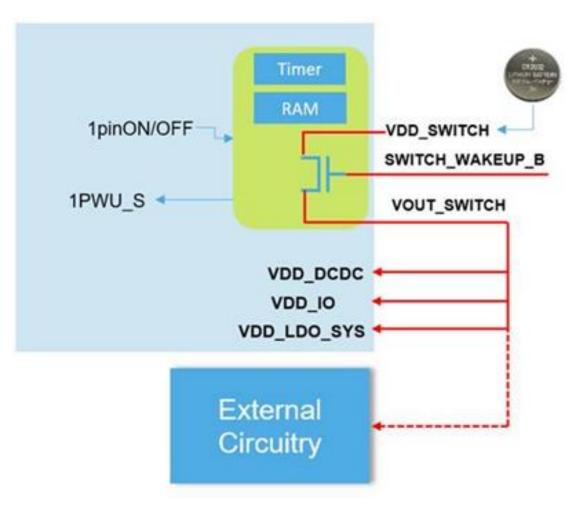

## SMART POWER SWITCH ULTRA LOW POWER & FLEXIBLE

#### Performance

- <100 nA (typ) leakage current when OFF (no RAM retention, timer disabled)</li>

- <700 nA (typ) leakage current when OFF (8KB RAM retention + timer )</li>

- 40 mA active output current capability

#### Flexible

- · Can be used to power partial or entire chip supply

- · Can be used to power external circuits saving BOM costs

### Configurable power control

- · One external wakeup pin (SWITCH\_WAKEUP\_B) to enable power switch

- Internal Timer timeout (from 7.8125ms to 1s) to enable power switch

- Dedicated register bits to control power switch in Low Power mode / Active mode

### Data storage

Support up to 8KB RAM retention

switch

NXP

# **DCDC** inductor

#### PUBLIC

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2022 NXP B.V.

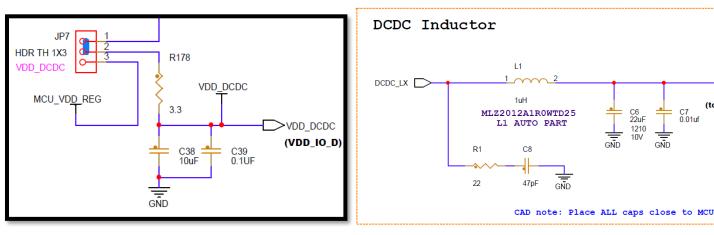

## **DCDC** inductor

### х-кw45b41z-evk – HW UM extract

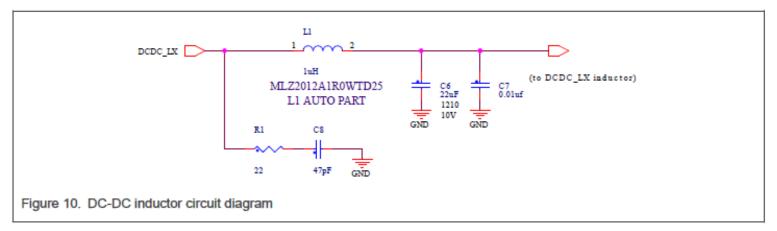

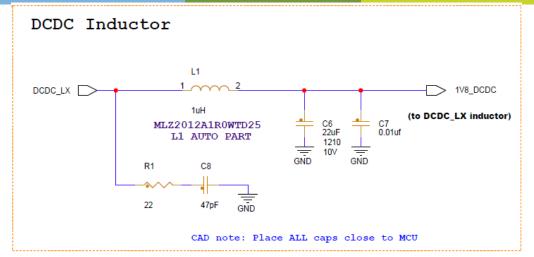

2.1.2 DC-DC inductor

The KW45B41Z-EVK board uses a 1 µH DC-DC inductor L1 (TDK MLZ2012A1R0WTD25). The inductor is enabled when the board is configured in DC-DC Buck mode. The figure below shows the DC-DC inductor circuit diagram of the KW45B41Z-EVK board.

Choosing right DC-DC inductor for your target board is very important. While selecting a DC-DC inductor, look for the following specifications:

- Inductor value: 1 µH or 1.5 µH

- ESR: < 0.3 Ω</li>

- Saturation current (Isat): > 300 mA

- · Self-resonant frequency: > 50 MHz

The DC-DC inductor used in the KW45B41Z-EVK board is a good choice for general automotive applications (for example, car access) as it delivers good performance (low ESR, high saturation current). It is also a good choice for keyfob application based on LF technology. It prevents spurious from 100 kHz to 200 kHz that can interact with another reception device (that is, NXP LF device at 125 kHz) on the same board. Other recommended inductors are LQM18PH1R0MFRL from Murata and 78438336010 from Wurth.

The figure below shows other possible inductor options.

## **DCDC** inductor

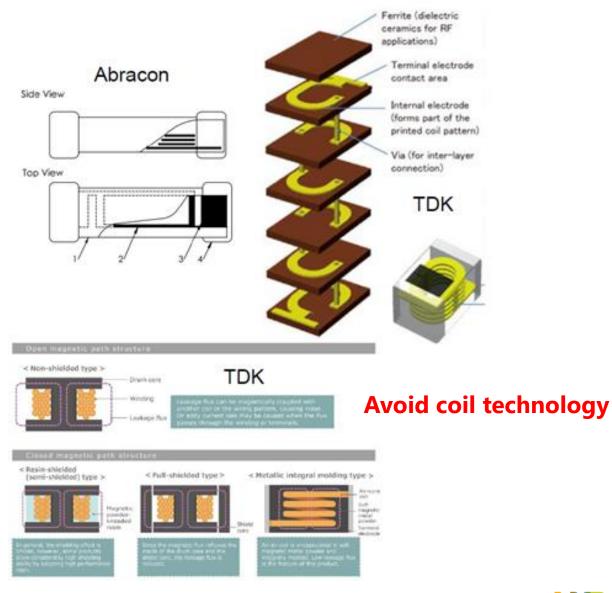

# Inductor and Shielding

- Normally for chip inductors the coils are in the same plane of the PCB. Any other coil in the same plane, with the same axis, will couple maximally.

- Rotating inductor does not help unless the plane of the coils are perpendicular to the PCB

- Coupling is minimal at the axis

- There are different types of shielding applied to inductors with different levels of effectiveness:

- Electrostatic shielding will probably not help at LF.

- Magnetic shielding ranges from a simple coating to complete encapsulation. The later is substantially more effective

- Must make sure inductor is not getting close to saturation! >>300mA.

1uH inductor: ESR must be closed to 0.2 ohms

# PMIC supply

#### PUBLIC

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2022 NXP B.V.

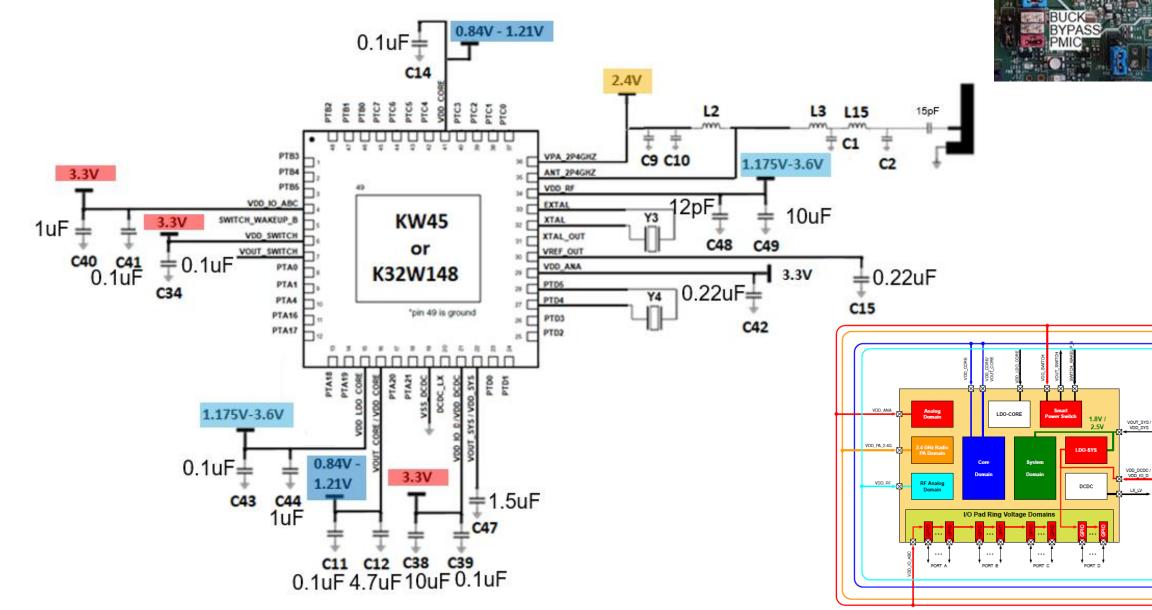

## **HVQFN48 – 7x7**

1

NXP

3.30V

2.40V

0.84-1.21V

175-3.6

## **KW45 – PMIC SUPPLY**

# **Smart Power Switch**

#### PUBLIC

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2022 NXP B.V.

## HW RECOMMENDATION – POWER SWITCH & BUCK MODE

## SMART POWER SWITCH ULTRA LOW POWER & FLEXIBLE

#### Performance

- <100 nA (typ) leakage current when OFF (no RAM retention, timer disabled)</li>

- <700 nA (typ) leakage current when OFF (8KB RAM retention + timer )</li>

- 40 mA active output current capability

#### Flexible

- · Can be used to power partial or entire chip supply

- · Can be used to power external circuits saving BOM costs

#### Configurable power control

- · One external wakeup pin (SWITCH\_WAKEUP\_B) to enable power switch

- Internal Timer timeout (from 7.8125ms to 1s) to enable power switch

- Dedicated register bits to control power switch in Low Power mode / Active mode

### Data storage

Support up to 8KB RAM retention

switch

NXP

# Radio

#### PUBLIC

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2022 NXP B.V.

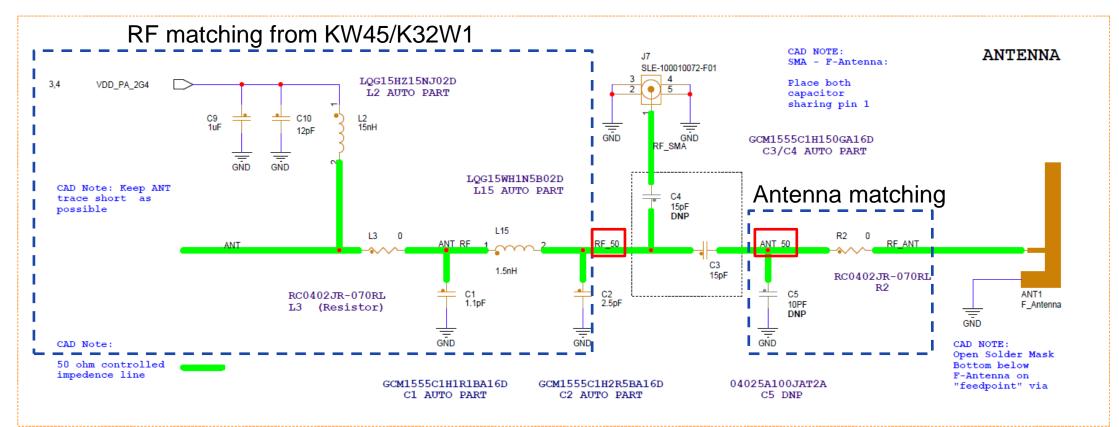

## HW RECOMMENDATION: RADIO AUTOMOTIVE COMPLIANT

## **RF Matching Goals:**

- Only certified automotive component have been used.

- Ensure sensitivity performance was the focus of this RF Matching

- PASS internal specification regarding 2<sup>nd</sup> and 3<sup>rd</sup> harmonics with 10dBm output power.

- Same Matching for 0dBm, 4dBm, 7dBm and 10dBm output power.

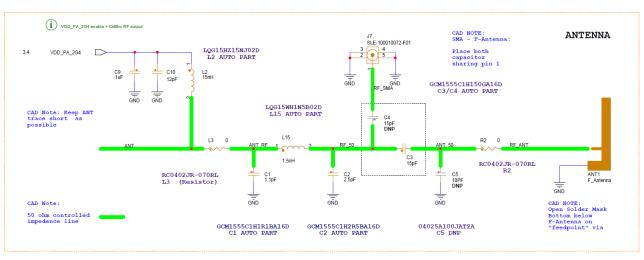

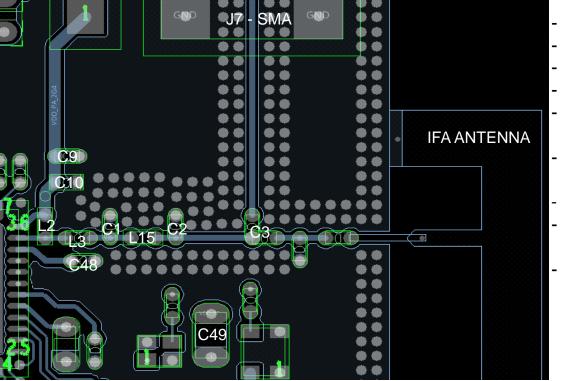

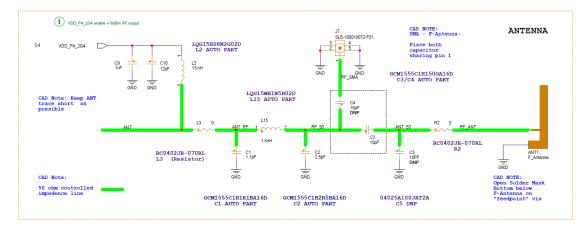

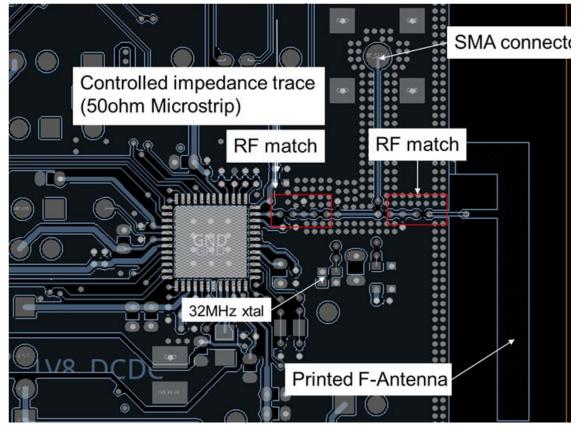

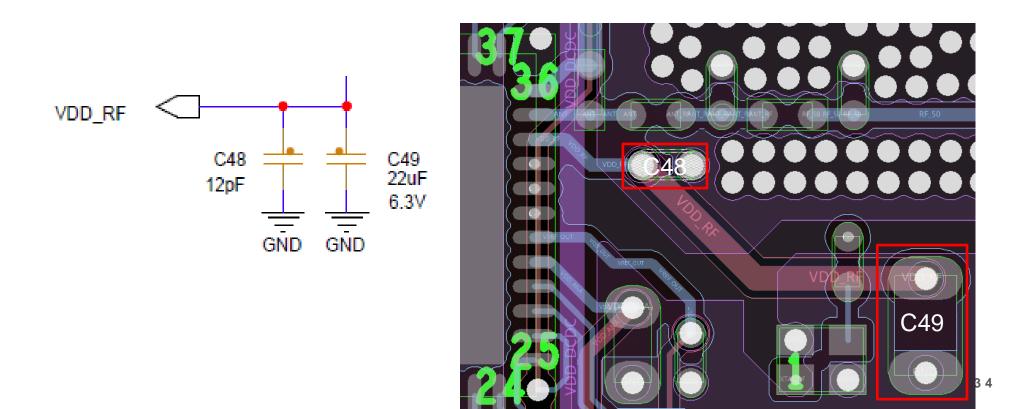

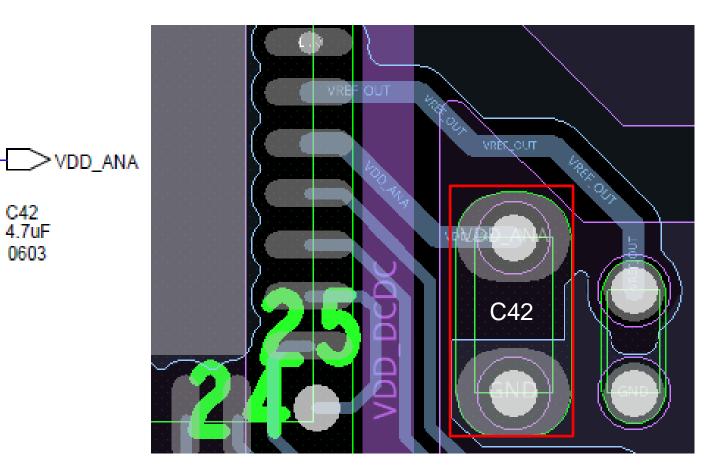

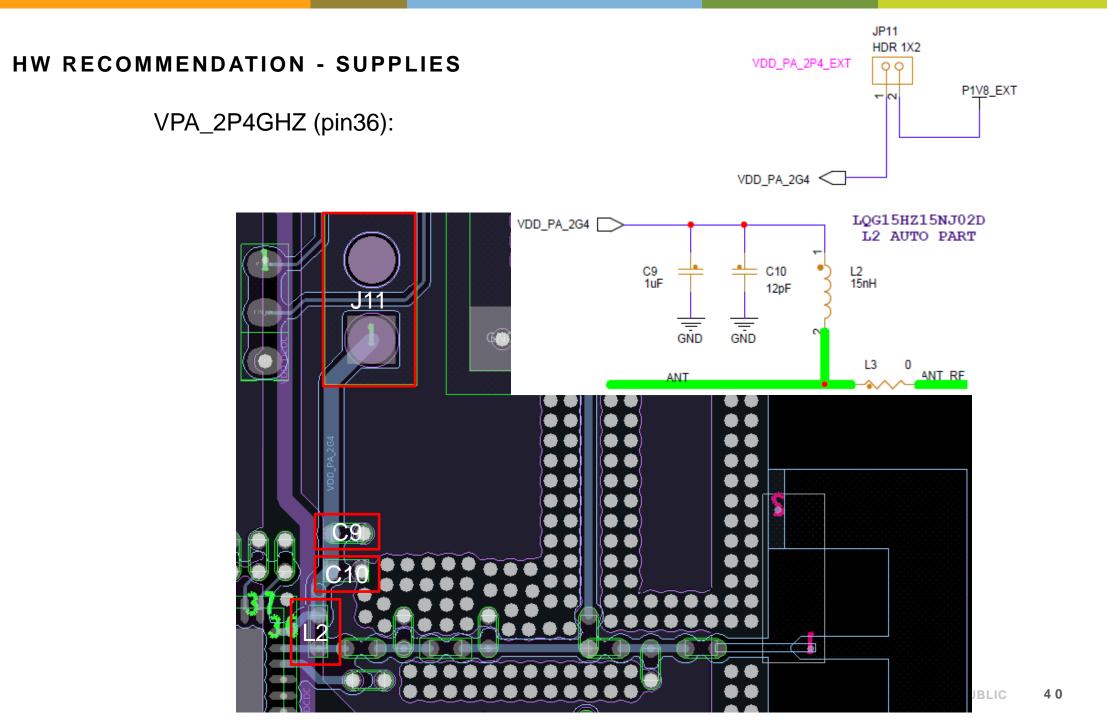

## HW RECOMMENDATION - RADIO

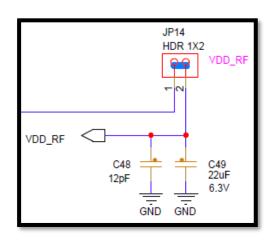

- The value capacitor C48 used for an RF short are 12pF

- C10 must be as close to L2 as possible

- C49=22uF on VDD\_RF could be placed as DNP

- The pull up inductor L2 placement must follow the layout example

- The **antenna matching** components must be at minimum spacing to the DUT and each other, as on the current layout.

- C48 needs to be placed in order to have the best isolation with ANT\_RF line.

VDDRF line needs to be isolated with VDDRF\_line. Please copy the current layout

- Need isolation between VDDRF and UART signals.

- VDD\_PA\_2g4 needs to be isolated vs PTC0

- General comment: The power planes which create huge fat nets are for the VDD\_ANA and VDD\_SYS. No benefit to reduce the power plane.

NP

## **Product Enablement HW**

X-KW45B41Z-EVK and X-K32W148-EVK Design and board layout considerations (HW guideline extract) – RF matching wave guide 50ohms for RF power output.

Matching components are:

٠

Inductors

## Automotive qualified

| R  | Reference | Value  | Description                                    | Mfr. name | Mfr. part number |

|----|-----------|--------|------------------------------------------------|-----------|------------------|

| L2 | 2         | 15 nH  | IND 0.015 µH @ 100 MHz 450 mA +/-5% 0402       | MURATA    | LQG15HZ15NJ02D   |

| L3 | 3         | 0ohm   | shunt                                          |           |                  |

| L1 | 15        | 1.5 nH | IND 0.0015 µH @ 100 MHz 1000 mA +/-0.1 nH 0402 | MURATA    | LQG15WH1N5B02    |

Capacitors

| Reference | Value  | Description                           | Mfr. name | Mfr. part number   |

|-----------|--------|---------------------------------------|-----------|--------------------|

| C2        | 2.5 pF | CAP CER 2.5 pF 50 V 0.1 pF C0G 0402   | MURATA    | GCM1555C1H2R5BA16  |

| C1        | 1.1 pF | CAP CER 1.1 pF 50 V 0.1 pF C0G 0402   | MURATA    | GCM1555C1H1R1BA16  |

| C10       | 12 pF  | CAP CER 12pF 50V 5% C0G AEC-Q200 0402 | MURATA    | GCM1555C1H120JA16D |

| C1        | 1 uF   | CAP CER 1uF 10V 10% X7S AEC-Q200 0402 | MURATA    | GCM155C71A105KE38D |

NP

## **Product Enablement HW**

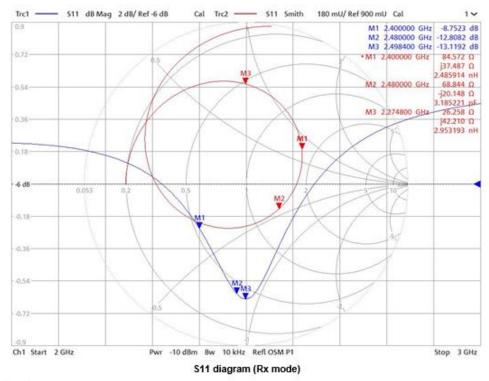

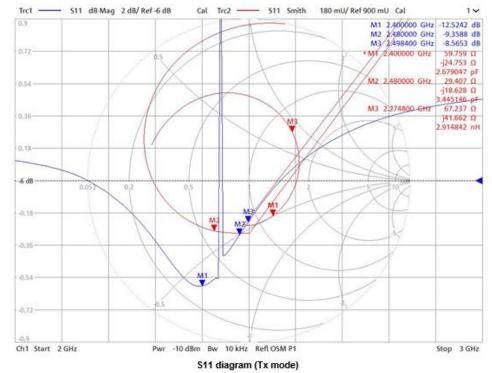

# S11 (return loss) results (AN13228 RF report extract) – RF matching 50ohms

## How to measure S11 on FRDM-KW3x & KW45

#### 4.2 RX

In the Rx mode, the return loss measurement is performed by setting the LNA gain of K32W148 to the maximum.

#### Hardware: X-K32W148-EVK

#### 4.3 TX

In the Tx mode, the return loss measurement is performed by setting the K32W148 RF output power to the minimum.

#### Hardware: K32W148 EVK

#### Results:

Return loss: -12.8 dB (2.48 GHz) < \$11 < -8.7 dB (2.4 GHz)</li>

#### There is no specification for the return loss.

#### Conclusion

• The return loss (S11) is lower than -8 dB

There is no specification for the return loss.

#### Conclusion:

Results:

• The return loss (S11) is lower than -9 dB.

Return loss: -12.5 dBm (2.4 GHz) < \$11 < -9.3dB (2.48 GHz)</li>

NO

# Supplies

#### PUBLIC

NXP, THE NXP LOGO AND NXP SECURE CONNECTIONS FOR A SMARTER WORLD ARE TRADEMARKS OF NXP B.V. ALL OTHER PRODUCT OR SERVICE NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS. © 2022 NXP B.V.

## Power modes: Buck, Bypass or PMIC Switch.

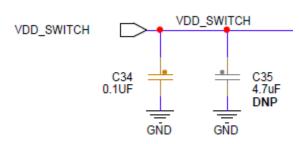

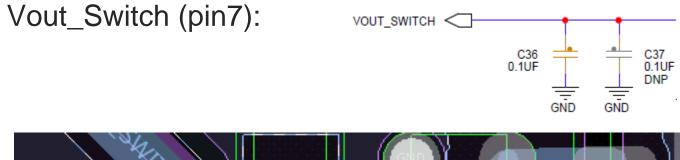

## Vdd\_Switch (pin6)

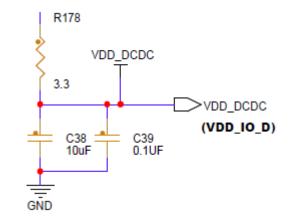

Vdd\_DCDC (& VDD\_IO\_D) (pin21)

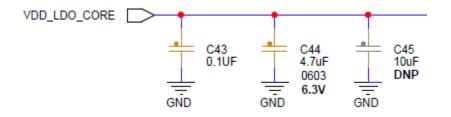

# Vdd\_LDO\_Core (pin15)

## Vdd\_Core1 (pin16):

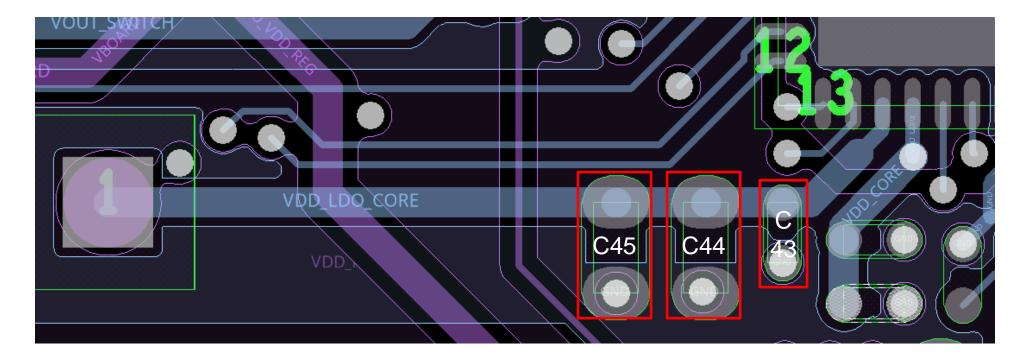

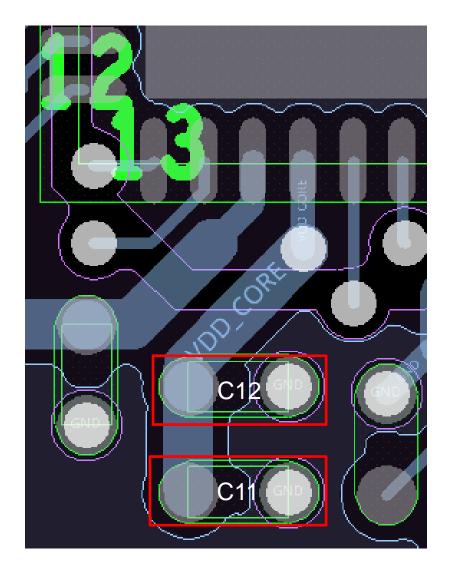

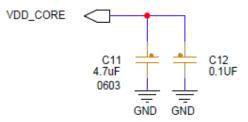

CAD note: Place C11 & C12 caps close to pin16

## Vdd\_Core2 (pin41):

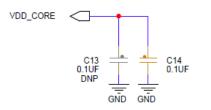

CAD note: Place C13 & C14 caps close to pin41

Vdd\_RF (pin34):

- decoupling near the IC (some mm, not more)

- Decoupling capacitor of 12pF (near the pin 34) between 32MHz crystal RF path

- Decoupling capacitor of 22uF not so closed to the IC due to component size

- Vdd\_RF line not superposed to another supply (digital supply is strongly forbidden)

- Vdd\_RF line not crossing the expose die pad of the IC

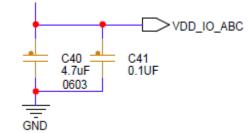

Vdd\_IO\_ABC (pin4):

GND

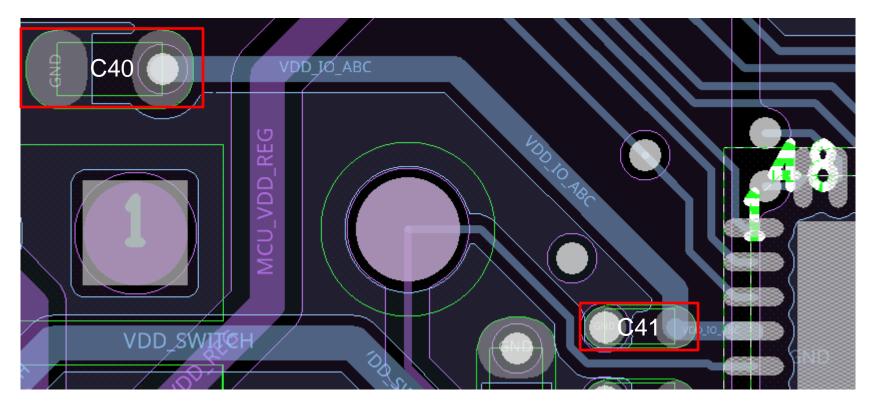

### Vdd\_Ana (pin29)

PUBLIC 37

Notes DCDC\_LX (pin20):

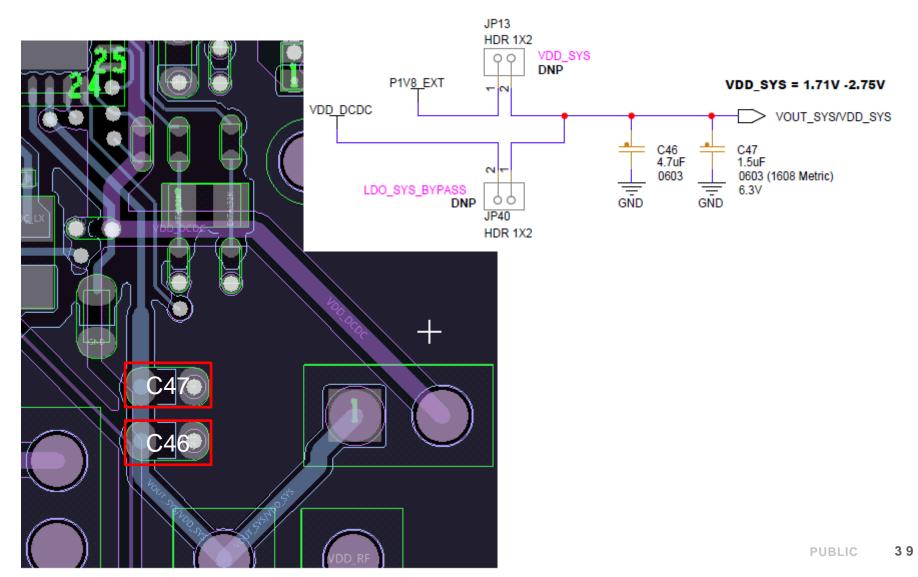

VOUT\_SYS/VDD\_SYS (pin22):

NP

NP

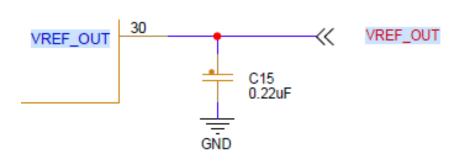

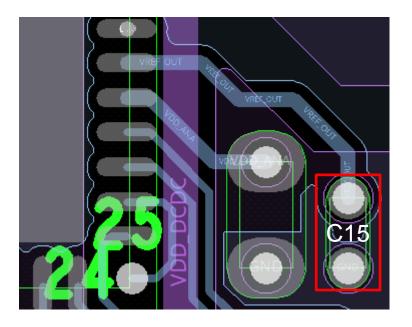

#### VREF\_OUT (pin30):

- Reduce the line width (voltage output with low current)

- Decoupling capacitor C15 is not needed to be near the IC (compromize to gain space)

- Vref\_out line not superposed to Vdd\_RF line

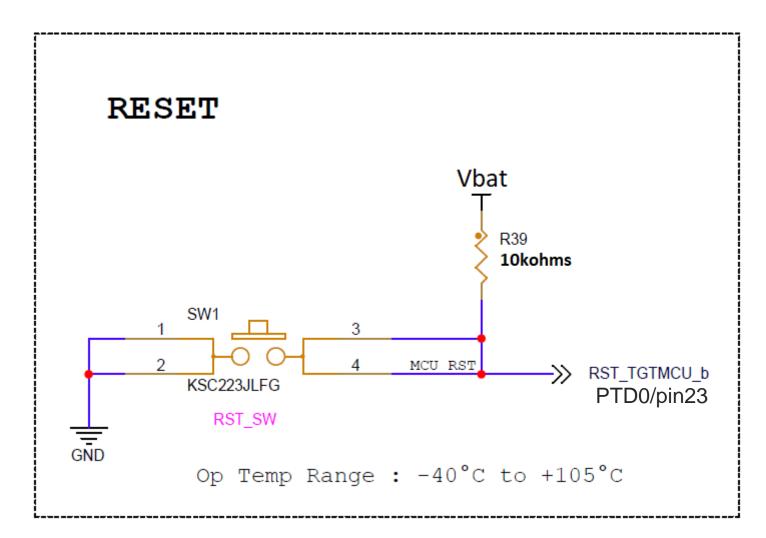

# RESET

#### PUBLIC

RESET

Be careful to connect the 10kohms pullup to Vbat, not Vdd\_1p8 in buck mode.

# **Clocks and Crystals**

#### PUBLIC

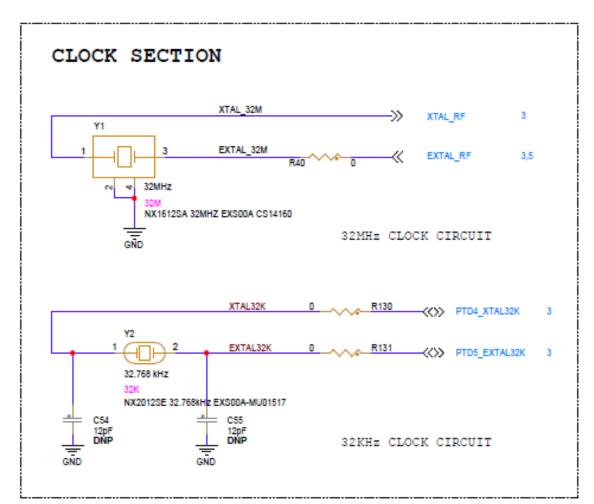

#### CRYSTAL REFERENCES

### For Bluetooth LE, GFSK & 802.15.4 **32MHz** and **26MHz** quartz references

| Manufacturer        | Series             | Part Number                   | Frequency          |

|---------------------|--------------------|-------------------------------|--------------------|

| NDK                 | NX1612SA           | EXS00A-CS14160                | 32MHz              |

| NDK                 | NX2016SA           | EXS00A-CS13636                | 26MHz              |

|                     |                    |                               |                    |

| Manufacturer        | Series             | Part Number                   | Frequency          |

| Manufacturer<br>NDK | Series<br>NX2016SA | Part Number<br>EXS00A-CS14161 | Frequency<br>32MHz |

### For Bluetooth LE and GFSK 32kHz quartz reference

| Manufacturer | Series   | Part Number    | Frequency |

|--------------|----------|----------------|-----------|

| NDK          | NX2016SA | EXS00A-MU01517 | 32,768kHz |

| NDK          | NX1612SA | EXS00A-MU00801 | 32,768kHz |

### TECHNICAL CRYSTAL PARAMETERS

#### **BLE recommendation: +/-50ppm**

- KWxx internal oscillator tolerance is -17/+20pm

- XTal:

- Initial tolerance is +/-10ppm

- Tolerance for external Xtal is -33/+30ppm

- Frequency aging (10years) is -6/+1ppm

- Frequency vs temperature (-40/+105°C) is +/-18ppm

- Frequency tolerance (reference) is -9/+11ppm

It is OK for BLE with the NDK Xtals (+105°C max Ta temperature)  $\rightarrow$

#### 15.4 recommendation: +/-40ppm

The same unique NDK Xtal reference so far !! And it doesn't fit with the +/-40ppm

For 15.4, KWxx internal oscillator tolerance is the same : -17/+20pm Then Xtal tolerance over Temperature and aging has to be -23/+20ppm! Is there any existing Xtal with such performance with :

Same Cload at 8pF

for a temperature range of -40+125°

In 1612 package

ESR 50 typical >> 60 max (120 may be acceptable)

Level of drive 200 $\mu$ W max

| <ol> <li>Customer Specifications Number</li> </ol> |  |

|----------------------------------------------------|--|

|----------------------------------------------------|--|

2. NDK Specification Number : EXS00A-CS14160

3. Type

: NX1612SA

#### 4. Electrical Specifications

|   | Parameters                                                 | SYM. | 1    | Electrical Spec. |      |                   | Notes                                                      |  |

|---|------------------------------------------------------------|------|------|------------------|------|-------------------|------------------------------------------------------------|--|

|   | Parameters                                                 | STM. | min  | typ              | max  | Units             | Notes                                                      |  |

| 1 | Nominal frequency                                          | fnom |      | 32.000           |      | MHz               |                                                            |  |

| 2 | Overtone order                                             | -    | Fu   | ndame            | ntal | -                 |                                                            |  |

|   |                                                            |      | -33  | -                | +30  | ×10 <sup>-6</sup> | at -40~+105°C<br>Include 4,5 and 6                         |  |

| 3 | Frequency tolerance(Overall)                               | -    | -33  | -                | +62  | ×10 <sup>-6</sup> | at +105~+120°C<br>Include 4,5 and 6                        |  |

|   |                                                            |      | -33  | -                | +72  | ×10 <sup>-6</sup> | at +120~+125°C<br>Include 4,5 and 6                        |  |

| 4 | Frequency tolerance(Reference)                             |      | -9   | -                | +11  | ×10 <sup>-6</sup> | at +25°C                                                   |  |

|   |                                                            |      | 18   | -                | +18  | ×10 <sup>-6</sup> | at -40~+105°C<br>The reference temperature shall be +25°C  |  |

| 5 | Frequency versus temperature<br>characteristics(Reference) | 1    | -18  | -                | +50  | ×10 <sup>-6</sup> | at +105~+120°C<br>The reference temperature shall be +25°C |  |

|   |                                                            |      | -18  | -                | +60  | ×10 <sup>-6</sup> | at +120~+125°C<br>The reference temperature shall be +25°C |  |

|   |                                                            |      | -2   | -                | +1   | ×10 <sup>-6</sup> | 1year                                                      |  |

| 6 | Frequency Aging(at +25°C)<br>(Reference)                   | -    | -4   | -                | +1   | ×10 <sup>-6</sup> | 5years                                                     |  |

|   |                                                            | 4    | -6   | -                | +1   | ×10 <sup>-6</sup> | 10years                                                    |  |

| 7 | Equivalent resistance                                      | -    | -    | 40               | 60   | Ω                 | IEC PI-network/Series                                      |  |

| 8 | Shunt capacitance                                          | Cn   | -30% | 0.54             | +30% | рF                | Not grounded                                               |  |

KW45 DS 32MHz:

Target: +/-50ppm (BLE)

Ta: max at 105°C

| Symbol         | Description                                                                 | F0 = 32.0 MHz |     | F0 = 26.0 MHz |     |     | Unit | Notes |     |

|----------------|-----------------------------------------------------------------------------|---------------|-----|---------------|-----|-----|------|-------|-----|

|                |                                                                             | Min           | Тур | Max           | Min | Тур | Max  | 1     |     |

| T <sub>A</sub> | Operating<br>Temperature                                                    | -40           | _   | 120           | -40 | _   | 120  | °C    | 1   |

|                | Crystal initial<br>frequency<br>tolerance                                   | -10           | _   | 10            | -10 | _   | 10   | ppm   | 2,3 |

|                | Crystal frequency stability and aging                                       | -25           | _   | 25            | -25 | _   | 24   | ppm   | 2,4 |

|                | Oscillator variation                                                        | -12           | _   | 15            | -12 | _   | 16   | ppm   | 5   |

|                | Total reference<br>oscillator tolerance<br>for Bluetooth LE<br>applications | -50           | _   | 50            | -50 | _   | 50   | ppm   | 6   |

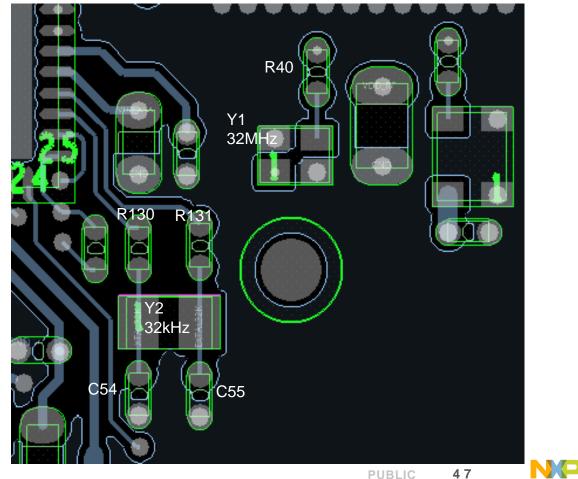

### **HW RECOMMENDATION - CLOCKS**

- 32MHz & 32kHz wire length must be as symetric as possible

- 32kHz quartz is not necessary to be as closed as possible from the DUT (KW45/K32W148)

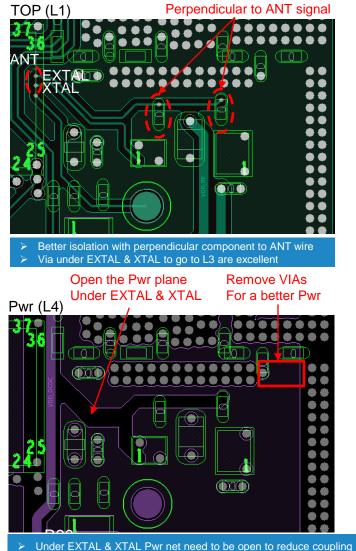

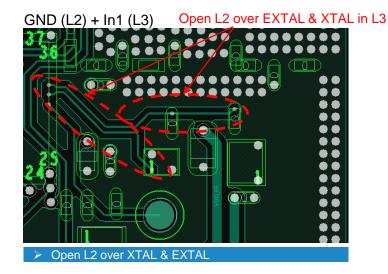

### HW RECOMMENDATION - CLOCKS

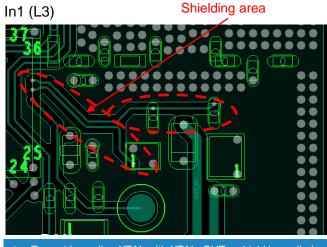

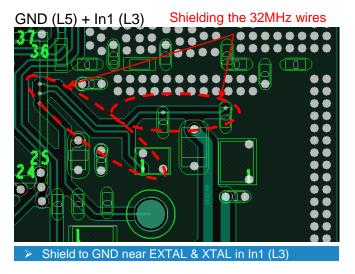

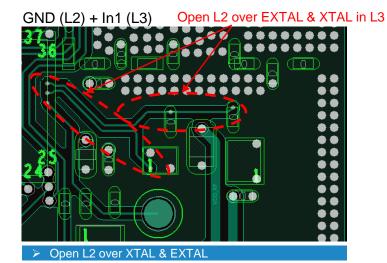

Special focus on 32MHz wires to help on a very good layout.

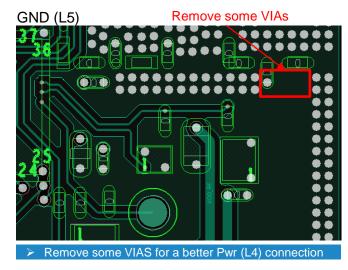

- Under EXTAL & XTAL Pwr net need to be open to reduce coupling capacitance to PWR

- > Some GND vias can be removed to have a better connection of PWR signal

- Excellent length is as short as possible GND (L2) 0 . •• . . . . . . . . ...  $\bullet \bullet$ . > To reduce capacitance on EXTAL & XTAL GND plane can be opened over XTAL & EXTAL wires

- The shielding is already present on TOP (L1) being GND in these area

To avoid coupling XTAL with XTAL\_OUT a shield is applied

To avoid any coupling on XTAL a shield on TOP is applied

### HW RECOMMENDATION - CLOCKS

- Special focus on 32MHz wires to help on a very good layout.

# **Bootloader pins**

#### PUBLIC

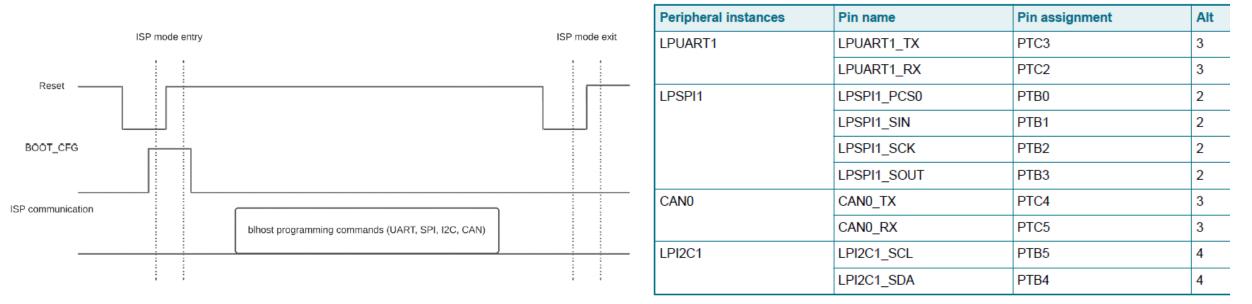

### **RECOMMENDATION - BOOTLOADER**

KW45/K32W1 requires signed firmware to be loaded into the NBU. This happens through the Bootloader. PTC2 and PTC3 are the UART connection to the Bootloader (refer to the table below for other peripherals to enter in ISP mode).

NXP recommend to have an option to connect them to a UART to USB converter (for PC connection).

NXP recommend to have a way to **pull PTA4 to logic high** in order to enter the device in bootloader mode.

Make sure that everything connected to PORTD is at the same voltage as VDD\_IO\_D. Same for PORTA, B and C and VDD IO ABC.

#### Table 83. Peripheral instances and pin assignments used by ISP

# Wake up pins

#### PUBLIC

### **RECOMMENDATION – WAKE UP PINS**

Some pins could wake up the KW45/K32W1:

48 pins package: PTB4, PTA0, PTA4, PTA17, PTA19, PTA21, PTC0, PTC1, PTC2, PTC4, PTC6, PTC7, PTB0, PTB3

40 pins package: PTB4, PTA0, PTA4, PTA17, PTA19, PTA21, PTC4, PTC7, PTB0, TPB3

# Level shifters

#### PUBLIC

### **RECOMMENDATION – LEVEL SHIFTER**

Make sure that everything connected to PORTD is at the same voltage as VDD\_IO\_D.

Same for PORTA, B and C and VDD\_IO\_ABC.

Other peripheral ICs connected to the KW45/K32W1 MUST be at the same voltage level. KW45/K32W1 device is capable to set the IO\_ABC voltage independently to the other Vdd voltages.

# IO current drive

#### PUBLIC

### **RECOMMENDATION – IO CURRENT DRIVE**

It's important to know some pins could handle higher current than others.

This specific pin list could handle 12mA current drive instead of 6mA on other IO pins:

• PTA18-19; PTB4-5; PTC0-1; PTC4-5

Note that both the DSEO and DSE1 bits in the control register for that pin must be set in order to get the highest drive strength.

#### 20.2 Module Configuration (INTERNAL REVIEW ONLY)

Resolved for module instance: PORTA

Chapter merged also from module instances: PORTB, PORTC, PORTD

| Parameter   | Instantiated Value<br>(PORTA) | Differences                     | Range                 | Origin | Description              |

|-------------|-------------------------------|---------------------------------|-----------------------|--------|--------------------------|

| PINDSE0_DIS | 0x00 (0)                      | PORTD: 4294967295               | [0-<br>unbounde<br>d] | RTL    | Disable DSE0 Config Bits |

| PINDSE0_RST | 0x04 (4)                      | PORTB: 0, PORTC: 0,<br>PORTD: 0 | [0-<br>unbounde<br>d] | RTL    | Pin DSE0 Reset value     |

PUBLIC 57

# Peripherals

#### PUBLIC

### **INFORMATION – PERIPHERAL PINS ON <u>48PINS</u> DEVICE**

### **INFORMATION – PERIPHERAL PINS ON <u>40PINS</u> DEVICE**

# **DTEST** pins

#### PUBLIC

#### **INFORMATION – DTEST PINS**

The DTM (Direct Test Mode) pins are available for both 48 pins and 40 pins packages.

The options are:

| PTD1 ALT8 – RF_UART_SIN  | (48-pin only)     |

|--------------------------|-------------------|

| PTD2 ALT8 – RF_UART_SOUT | (48-pin only)     |

| PTC2 ALT6 – RF_UART_SIN  | (48-pin & 40-pin) |

| PTC3 ALT6 – RF_UART_SOUT | (48-pin & 40-pin) |

# Battery: CoinCells

#### PUBLIC

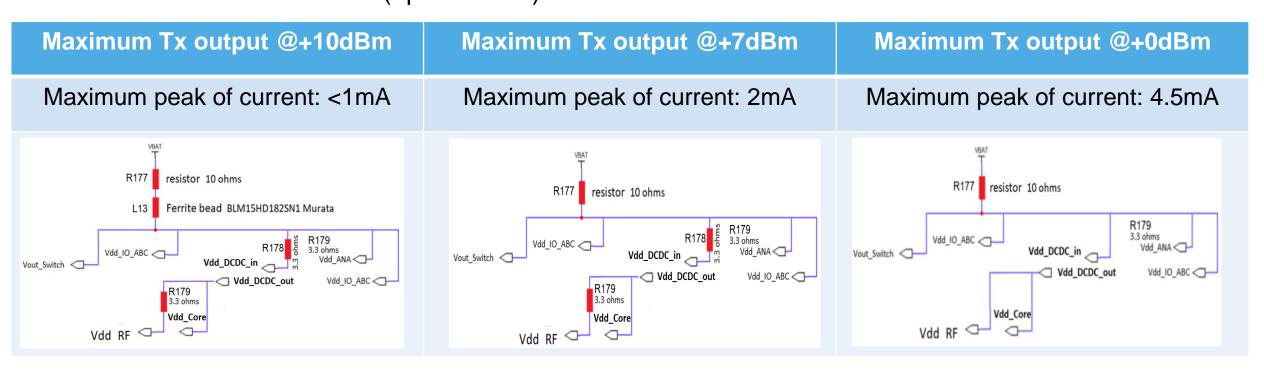

Schematic – Recommandation for coincell only (peak of current below 10mA) Reduced current peak

#### DCDC BUCK MODE - COINCELL - SUMMARY

Suitable for battery (coincell) applications only

Solution to reduce the DCDC current peaks and current peaks on Tx signals (+10/+7/+0dBm) during Bluetooth LE events (Advertising, Connect & Scan) is to add serial resistor(s) on different supplies. It will limit the peaks of current below 10mA.

Voltage drop occurs due to the serial resistor(s) but it never goes down to POR threshold (up to 105°C).

# Unused IOs

#### PUBLIC

#### **RECOMMENDATION CONNECTION FOR UNUSED IOS**

#### Datasheet extract

### HVQFN48WF - 7x7

#### Table 54. Recommended connection for unused interfaces

| Pin Type | Pin Function  | Recommendation                        | Comments                                                                                                                                                                                                                                                                          |

|----------|---------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power    | VDD_LDO_CORE  | Connect to<br>VOUT_CORE and VSS       | When the LDO is not used, the input and output should be connected together and tied to ground through a 10 k $\Omega$ resistor. The regulator should also be disabled in software.                                                                                               |

| Power    | VOUT_CORE     | Connect to<br>VDD_LDO_CORE and<br>VSS | When the LDO is not used, the input and output should be connected together and tied to ground through a 10 k $\Omega$ resistor. The regulator should also be disabled in software.                                                                                               |

| Power    | VOUT_SYS      | Connect to VDD_IO_D                   | When the LDO is bypassed, the input and<br>output should be connected together and tied to<br>an external supply. The regulator should also be<br>disabled in software.                                                                                                           |

| Power    | VDD_DCDC      | Ground                                | When the DCDC is not used, the input should be tied to VSS through a 10 k $\Omega$ resistor.                                                                                                                                                                                      |

| Power    | DCDC_LX       | Float                                 | The input VDD_DCDC should be tied to VSS with 10 Kohm                                                                                                                                                                                                                             |

| Power    | VDD_IO_D      | Must be powered                       | VDD_IO_D is used to power parts of the system<br>power controller (SPC) and must be powered to<br>use the chip. If LDO_SYS is not being used,<br>then tie VDD_IO_D to VOUT_SYS and supply<br>power from an external source. The regulator<br>should also be disabled in software. |

| Power    | VDD_PA_2.4GHz | Float                                 | VDD_PA_2.4GHz is always driven, either<br>from internal LDO sourced by VDD_RF, or<br>from external supply.                                                                                                                                                                        |

#### **RECOMMENDATION CONNECTION FOR UNUSED IOS**

### Datasheet extract

## HVQFN48WF - 7x7

| Power           | VDD_SWITCH    | Must be powered                          | Powers FRO16 and a portion of RAM.                                                                                                                                                                                                                              |

|-----------------|---------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power           | VOUT_SWITCH   | Float                                    |                                                                                                                                                                                                                                                                 |

| Power           | VDD_IO_ABC    | Must be powered                          | VDD_IO_ABC powers the mux logic for PORTA,<br>PORTB and PORTC. It must be powered during<br>POR. The recommendation is to keep it<br>powered, but it can be connected to the output<br>of the Smart Power Switch and be left floating in<br>shelf storage mode. |

| Power           | VDD_ANA       | Float                                    |                                                                                                                                                                                                                                                                 |

| Power           | VREFH         | Always connect to VDD_ANA potential      | Always connect to VDD_ANA potential                                                                                                                                                                                                                             |

| Power           | VREFL         | Always connect to VSS potential          | Always connect to VSS potential                                                                                                                                                                                                                                 |

| Power           | VSS_ANA       | Always connect to VSS potential          | Always connect to VSS potential                                                                                                                                                                                                                                 |

| Power           | VSS_DCDC      | Always connect to VSS potential          | Always connect to VSS potential                                                                                                                                                                                                                                 |

| Power           | VSS_RF        | Always connect to VSS potential          | Always connect to VSS potential                                                                                                                                                                                                                                 |

| Analog/non-GPIO | ADCn_x        | Float                                    |                                                                                                                                                                                                                                                                 |

| Analog/non-GPIO | VREF_OUT      | Float                                    | Analog output - Float                                                                                                                                                                                                                                           |

| Analog/non-GPIO | TAMPERx       | Float                                    |                                                                                                                                                                                                                                                                 |

| Analog/non-GPIO | RTC_WAKEUP_B  | Float                                    |                                                                                                                                                                                                                                                                 |

| Analog/non-GPIO | RTC_RTCCLKOUT | Float                                    |                                                                                                                                                                                                                                                                 |

| Analog/non-GPIO | EXTAL32K      | Float                                    |                                                                                                                                                                                                                                                                 |

| Analog/non-GPIO | XTAL32K       | Float                                    | Analog output - Float                                                                                                                                                                                                                                           |

| Analog/non-GPIO | EXTAL_32M     | Float                                    |                                                                                                                                                                                                                                                                 |

| Analog/non-GPIO | XTAL_32M      | Float                                    | Analog output - Float                                                                                                                                                                                                                                           |

| GPIO/Analog     | PTx/CMPn_INx  | Float                                    | Float (default is analog input)                                                                                                                                                                                                                                 |

| GPIO/Digital    | PTD1/NMI_b    | 10k $\Omega$ pullup or disable and float | Pull high or disable in PCR & FOPT and float                                                                                                                                                                                                                    |

| GPIO/Digital    | РТх           | Float                                    | Float (default is disabled)                                                                                                                                                                                                                                     |

PUBLIC 67

# Layout general rules

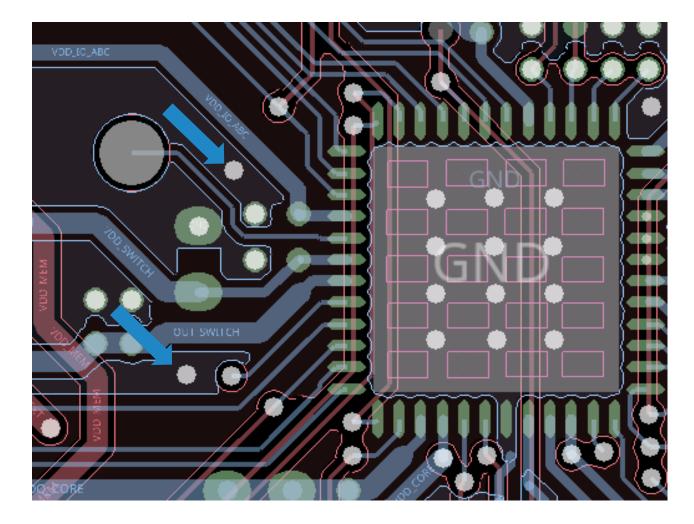

#### HW RECOMMENDATION - LAYOUT GENERAL RULES: FINGERPRINT

Avoid fingerprint like below example:

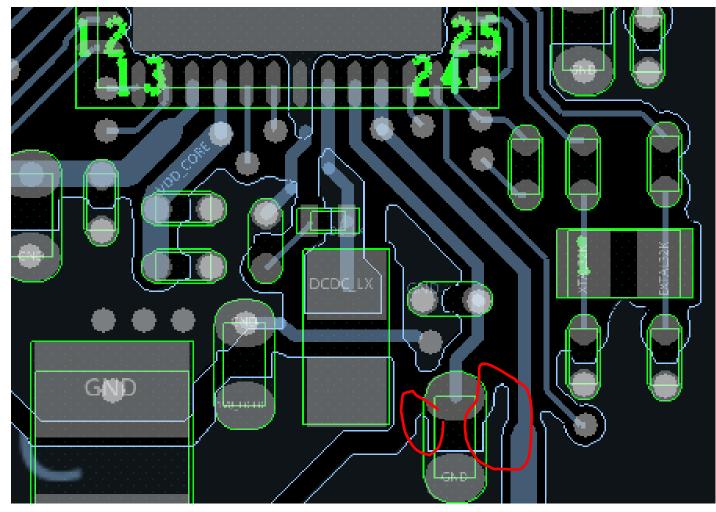

#### HW RECOMMENDATION - LAYOUT GENERAL RULES: VIAS

Add vias at the end of the ground area: 2 examples below:

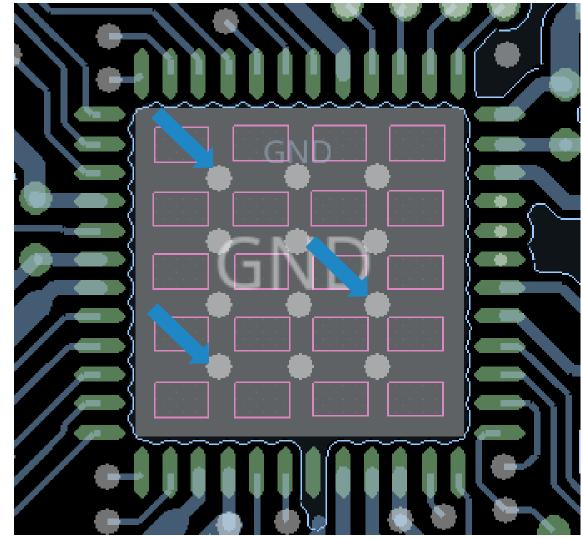

#### HW RECOMMENDATION - LAYOUT GENERAL RULES: DIEPAD

Diepad & Vias connected to GND: Matrix of 4x5

# EMC immunity option

#### PUBLIC

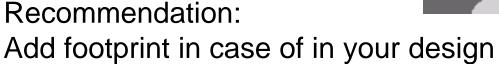

#### ONE WAY TO REDUCE VCO IMPACT (4.8GHZ) ON EMC

Possible way to avoid VCO noise on the PCB is to place a 3pF decoupling capacitor with resonance @4.8GHz on pins PTC0, PTC1, PTC2 & PTC3.

- Decoupling capacitor must be very closer to the pin.

- Wire must be as short as possible.

- No vias allowed

# CISPR25

#### PUBLIC

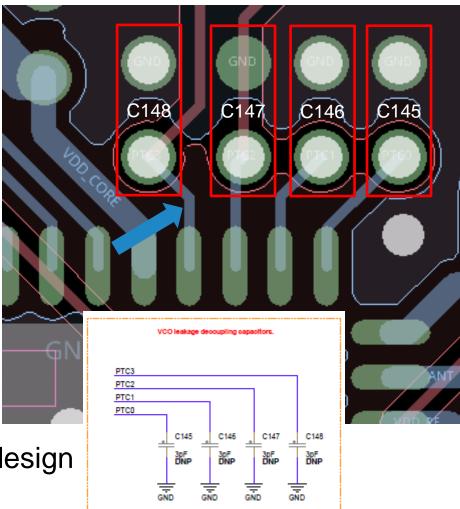

#### **CISPR25 AUTOMOTIVE CHINESE CERTIFICATION**

#### The KW45-EVK and K32W1-EVK could withstand the CISPR25 certification.

To pass this certification for +10dBm Tx output power, the EVK board needs to be modified as follow:

- Replace the RF matching component values

| RF Service         | E               | RBW   | Limits [dBuV/m] |         |             |  |

|--------------------|-----------------|-------|-----------------|---------|-------------|--|

| [User band in MHz] | Frequency [MHz] | (kHz) | Peak            | Average | Quasi- Peak |  |

| Bluetooth          | 2400 - 2690     | 120   | 44              | 24      | N/A         |  |

| G                  | 3000 - 5000     | ≥1000 | 64              | 44      | N/A         |  |

| GGG                | 5010 - 5030     | 9/10  | N/A             | 16      | N/A         |  |

| WLAN               | 5000 - 6000     | ≥1000 | 68              | 48      | N/A         |  |

| nH             | nH  | рF  | nH  | рF  | рF |

|----------------|-----|-----|-----|-----|----|

| L2             | L3  | C1  | L15 | C2  | C3 |

| BLF03RD501GZED | 1.6 | 2.7 | 1.3 | 1.1 | 15 |

- Replace R2 by a Band Pass Filter at R2. Reference BF2520-B2R4CACT/LF

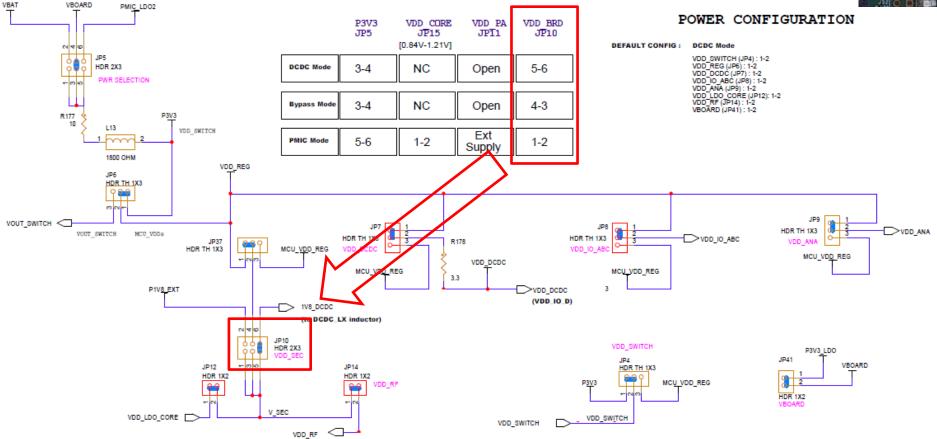

# Jumper configuration on KW45/K32W1-EVK

PUBLIC

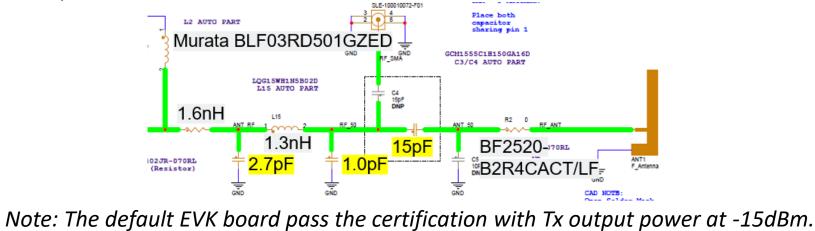

#### **GENERAL INFORMATION - JUMPER CONFIGURATION**

- DCDC modes (red jumper)

- Current consumption header (blue jumpers)

PUBLIC 77

# SECURE CONNECTIONS FOR A SMARTER WORLD