# **LPTMR**

**Low-Power Timer**

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, the Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorlQ, StarCore and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKitt, BeeSlack, ColdFire+, CoreNet, Flexis, Kinetis, MXC, Platform in a Package, Processor Expert, QorlQ Qonverge, Qorivva, QUICC Engine, SMARTMOS, TurboLink, VortiQa and Xtinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. @ 2011 Freescale Semiconductor, Inc.

#### **Feature List**

#### The features of the LPTMR module include:

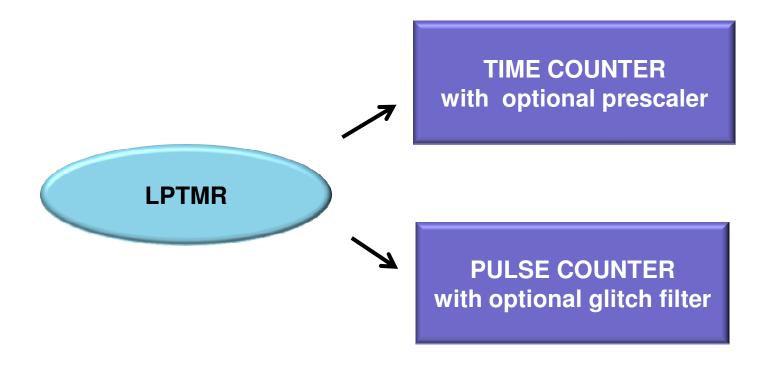

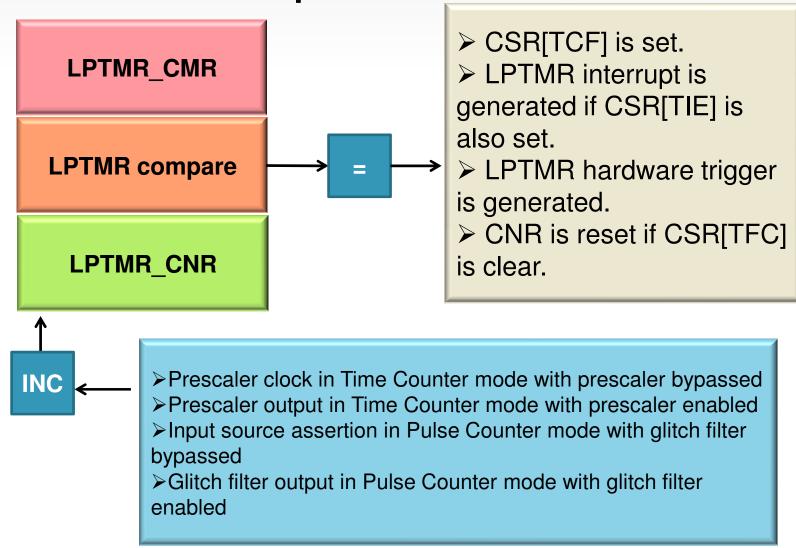

- > 16-bit time counter or pulse counter with compare

- > Optional interrupt can generate asynchronous wakeup from any lowpower mode

- > Hardware trigger output

- > Counter supports free-running mode or reset on compare

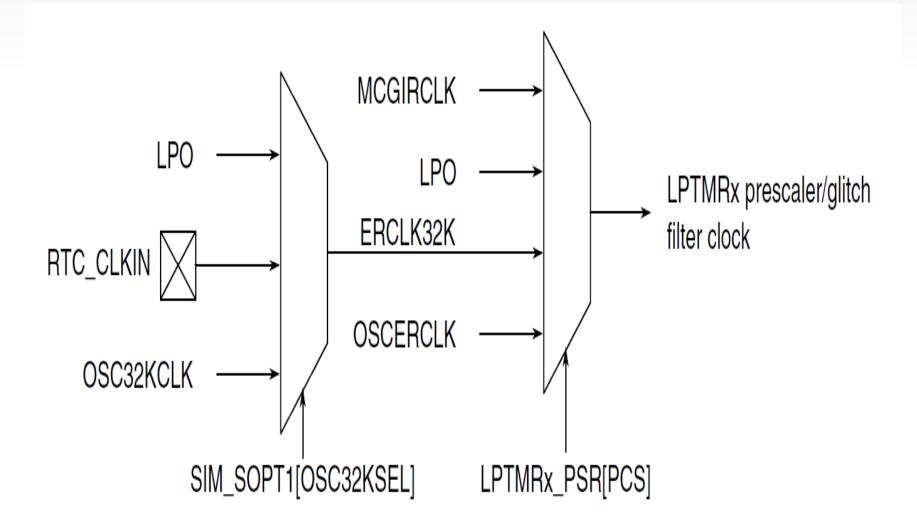

- > Configurable clock source for prescaler/glitch filter

- > Configurable input source for pulse counter

- > Rising-edge or falling-edge

### **Clocks sources**

## **Functional description**

## **Functional description**

## **LPTMR Register**

| Register name                                        | Width<br>(in bits) | Access | Reset value |

|------------------------------------------------------|--------------------|--------|-------------|

| Low Power Timer Control Status Register (LPTMR0_CSR) | 32                 | R/W    | 0000_0000h  |

| Low Power Timer Prescale Register (LPTMR0_PSR)       | 32                 | R/W    | 0000_0000h  |

| Low Power Timer Compare Register (LPTMR0_CMR)        | 32                 | R/W    | 0000_0000h  |

| Low Power Timer Counter Register (LPTMR0_CNR)        | 32                 | R      | 0000_0000h  |

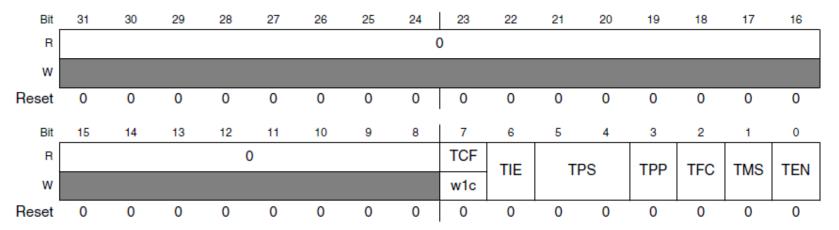

#### Low Power Timer Control Status Register (LPTMRx\_CSR)

Address: 4004\_0000h base + 0h offset = 4004\_0000h

## Low Power Timer Control Status Register (LPTMRx\_CSR)

| 0 | TEN |     | 0 |

|---|-----|-----|---|

| - | TMS | 2   | 0 |

| 2 | TEC | -   | 0 |

| 3 | ТРР |     | 0 |

| 1 | S   | 0   |   |

| 9 | SdT |     | 0 |

| 9 | TIE | 0   |   |

| 7 | TCF | w1c | 0 |

| 8 |     |     | 0 |

| Field      | Description                                                                                                                                                                                                                                                                     |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TCF   | Timer Compare Flag 0 The value of CNR is not equal to CMR and increments. 1 The value of CNR is equal to CMR and increments.                                                                                                                                                    |

| 6<br>TIE   | Timer Interrupt Enable 0 Timer interrupt disabled. 1 Timer interrupt enabled.                                                                                                                                                                                                   |

| 5–4<br>TPS | Timer Pin Select Configures the input source to be used in Pulse Counter mode. 00 Pulse counter input 0 is selected. 01 Pulse counter input 1 is selected. 10 Pulse counter input 2 is selected. 11 Pulse counter input 3 is selected.                                          |

| 3<br>TPP   | Timer Pin Polarity Configures the polarity of the input source in Pulse Counter mode.  0 Pulse Counter input source is active-high, and the CNR will increment on the rising-edge.  1 Pulse Counter input source is active-low, and the CNR will increment on the falling-edge. |

| 2<br>TFC   | Timer Free-Running Counter 0 CNR is reset whenever TCF is set. 1 CNR is reset on overflow.                                                                                                                                                                                      |

| 1<br>TMS   | Timer Mode Select 0 Time Counter mode. 1 Pulse Counter mode.                                                                                                                                                                                                                    |

| 0<br>TEN   | Timer Enable 0 LPTMR is disabled and internal logic is reset. 1 LPTMR is enabled.                                                                                                                                                                                               |

### Low Power Timer Prescale Register (LPTMRx\_PSR)

Address: 4004\_0000h base + 4h offset = 4004\_0004h

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21   | 20   | 19 | 18     | 17 | 16  |

|-------|----|----|----|----|----|----|----|----|----|----|------|------|----|--------|----|-----|

| R     |    |    |    |    |    |    |    | (  | )  |    |      |      |    |        |    |     |

| w     |    |    |    |    |    |    |    |    |    |    |      |      |    |        |    |     |

| Reset | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0    | 0  | 0      | 0  | 0   |

|       |    |    |    |    |    |    |    |    |    |    |      |      |    |        |    |     |

| Bit   | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5    | 4    | 3  | 2      | 1  | 0   |

| R     |    |    |    |    | 0  |    |    |    |    |    | PRES | CALE |    | PBYP   | P  | CS. |

| w     |    |    |    |    |    |    |    |    |    |    | THEO | OALL |    | 1 0 11 |    |     |

| Reset | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0    | 0  | 0      | 0  | 0   |

## Low Power Timer Prescale Register (LPTMRx\_PSR)

| Field           | Description                                                                                                                                                                                                |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6–3<br>PRESCALE | Prescale Value Configures the size of the Prescaler in Time Counter mode or width of the glitch filter in Pulse Counter mode.                                                                              |

| 2<br>PBYP       | Prescaler Bypass  0 Prescaler/glitch filter is enabled.  1 Prescaler/glitch filter is bypassed.                                                                                                            |

| 1–0<br>PCS      | Prescaler Clock Select 00 Prescaler/glitch filter clock 0 selected. 01 Prescaler/glitch filter clock 1 selected. 10 Prescaler/glitch filter clock 2 selected. 11 Prescaler/glitch filter clock 3 selected. |

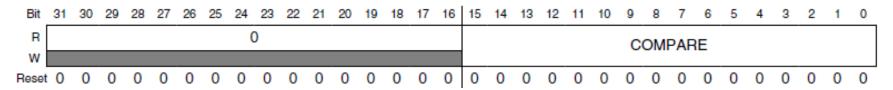

#### Low Power Timer Compare Register (LPTMRx\_CMR)

Address: 4004\_0000h base + 8h offset = 4004\_0008h

| Field           | Description                                                                                                                                                                                                                                                                                                                                        |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–0<br>COMPARE | Compare Value When the LPTMR is enabled and the CNR equals the value in the CMR and increments, TCF is set and the hardware trigger asserts until the next time the CNR increments. If the CMR is 0, the hardware trigger will remain asserted until the LPTMR is disabled. If the LPTMR is enabled, the CMR must be altered only when TCF is set. |

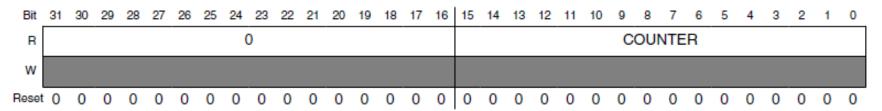

#### Low Power Timer Counter Register (LPTMRx\_CNR)

Address: 4004\_0000h base + Ch offset = 4004\_000Ch

| Field           | Description   |

|-----------------|---------------|

| 15–0<br>COUNTER | Counter Value |

#### Hands-On

- Configure the LPTMR toggle a LED every X time using a compare value.

- The steps to configure the LPTMR for this module are:

- 1. Set the clock for the LPTMR (SIM SCGC5)

- 2. Reset the module to clear any flag/ value (LPTMR0\_CSR)

- 3. Set the compare value (LPTMR0\_CMR)

- Set the clock use it and the prescaler (LPTMR0\_PSR)

- 5. Enable the LPTMR (LPTMR0\_CSR

- 6. Wait for counter to reach compare value

- Clear the flag