ULTRA SCALABLE: I.MX

APPLICATION PROCESSORS

### **SINGAPORE**

WOON SOCK KENG JULY 2016

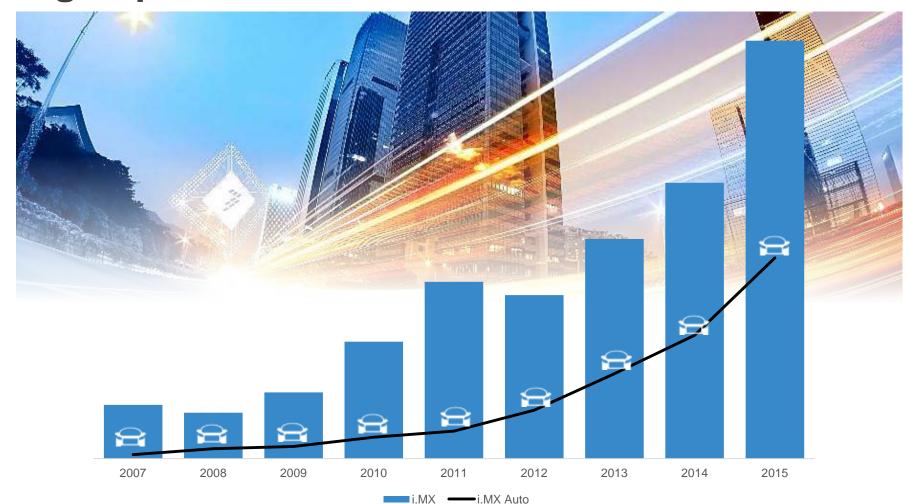

# i.MX Driving Explosive Growth in Automotive and Smart Devices

Over 250M i.MX SOC's shipped to date Over 65M vehicles enabled with i.MX since 2007

#1 in eReaders, #1 in Auto Infotainment MPU

# i.MX Applications Processors Core Values

### Scalability

- CPU (single/dual/quad, asymmetric), GPU, IO

- Software: Linux, Android, QNX, Windows-embedded, RTOS

- Industry leading ecosystem and partnerships

- Pin compatibility and software portability

### Integration

- Automotive/Industrial/Consumer peripheral sets

- Qualifications: AEC-Q100, JEDEC Industrial and Consumer

### Trust

- Market knowledge/expertise in industrial, consumer and automotive

- Longevity: minimum of 10-15 years in all markets

- Consistency of supply, product availability

- Quality, robustness, zero-defect methodology

- Security and Safety

### Ease of Adoption

- Communities, innovation, support

- Design collateral, distribution

- System solutions: SoC, sensors, PMIC, IoT comms, SBC

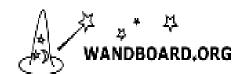

### **Product Longevity**

# i.MX Product Longevity and Energy Efficiency Programs

For terms and conditions and to obtain a list of available products, visit <a href="www.nxp.com/productlongevity">www.nxp.com/productlongevity</a>

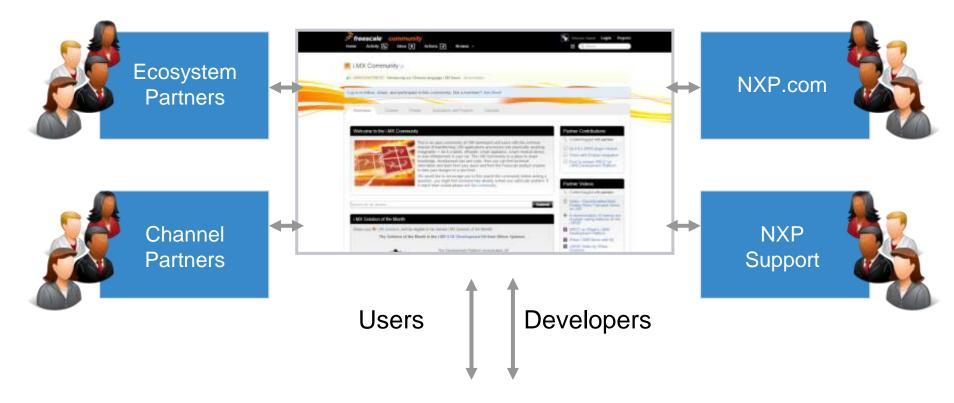

# iMXCommunity.org – Connect, Collaborate, Share

Greater than **4,000 members** 3500 new content added every year

Support and enablement for i.MX processors and software – share tips, ask questions, spark ideas

Federated search capability integrated with our website

Forums – Discussions – Groups – Blogs Posts – News – Multimedia Gallery – Training

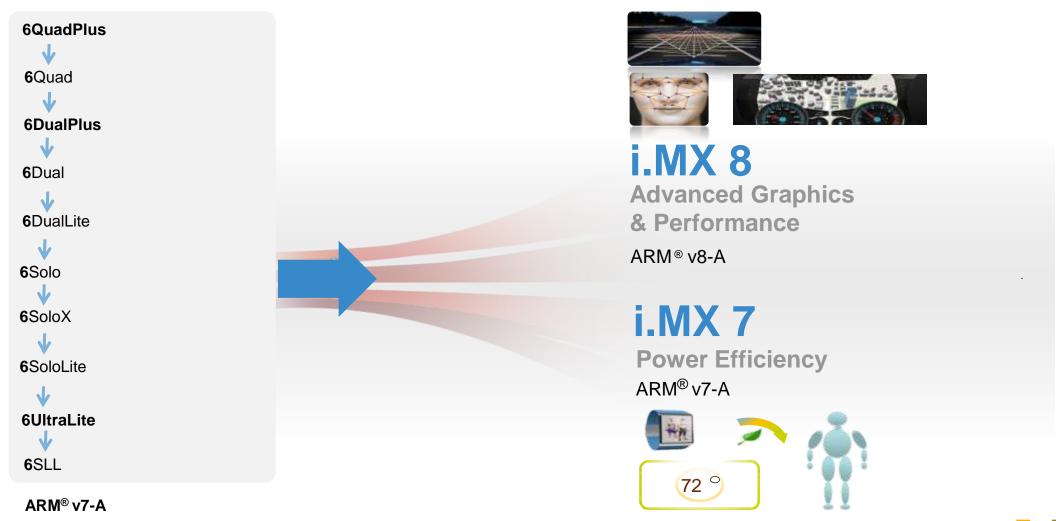

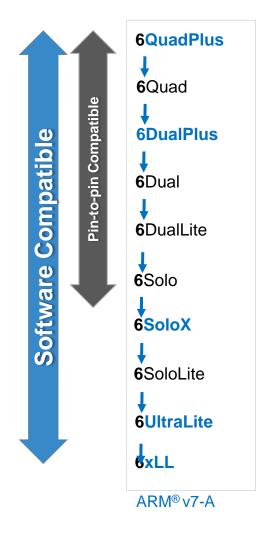

# i.MX 6 Series: Supreme Scalability and Flexibility

### Scalable series of **NINE** ARM-based SoC Families

Software Compatible

Expanded series for performance, power efficiency and lower BOM

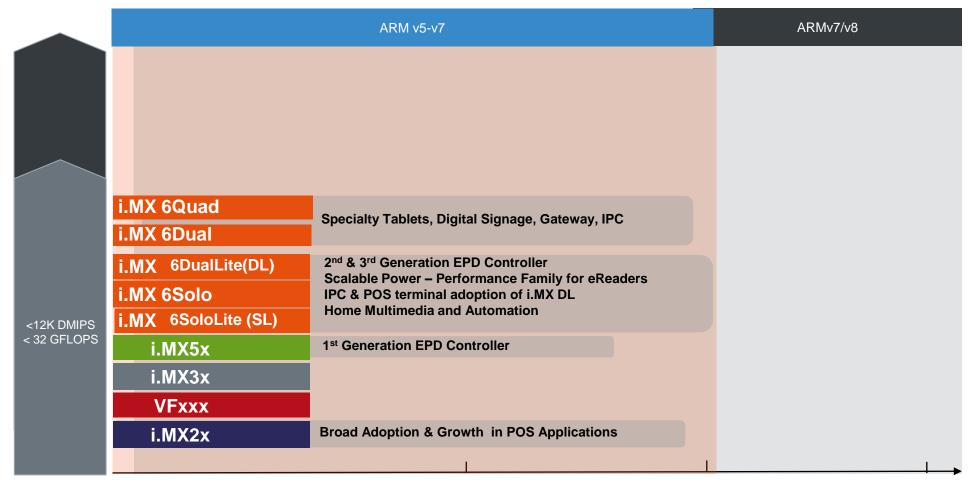

# **Applications Processor Family: Consumer and Industrial**

i.MX and VF-Series Products Available Prior to 2015

# i.MX Processor Roadmap:

Two New i.MX Platforms Based on 28nm Technology

# i.MX 8 Platform: 3 Series of Parts With Targeted Features

### i.MX 8 series

**Advanced Graphics and Performance**

ARM® v8-A (32-Bit / 64-Bit)

### i.MX 8M series

Advanced Audio and Video

ARM® v8-A (32-Bit / 64-Bit)

### i.MX 8X series

**BOM** and Energy Efficiency

ARM® v8-A (32-Bit / 64-Bit)

### **i.MX** 7

Power Efficiency & BOM Cost Optimizations

ARM® v7-A

# Software, Professional Support & Services

### **Complimentary Software & Tools**

### **Complimentary Support**

Freescale Boards

Communities

**Technical Information Center**

Distributor Apps Engineers

Field Application Engineers

### **Software Products**

**Graphic Tools**

Connected Audio Solution

CarPlay, AVB, Miracast, TRLE,

TEE, Home Kit, MICROEJ,

Sensor Fusion

1st Time Boot

Schematics & Layout Review

### **Professional Support**

Risk Reduction

Fast Answers

Hot Fixes

# **Enablement Through Reference Designs**

### **SABRE Platform for Smart Devices**

ambient light sensor and digital microphones

Builds on SABRE Board design with additional features including 10.1" capacitive multi-touch display, 2x MIPI camera sensors, SPI Nor Flash, GPS,

| Supported             | Description                       |  |

|-----------------------|-----------------------------------|--|

| i.MX 6Quad            | Quad-core 1-1.2 GHz ARM Cortex-A9 |  |

| i.MX 6Dual (emulated) | Dual-core 1-1.2 GHz ARM Cortex-A9 |  |

| i.MX 6DualLite        | Dual-core 1GHz ARM Cortex-A9      |  |

| i.MX 6Solo (emulated) | Single-core 1GHz ARM Cortex-A9    |  |

### **SABRE for Auto Infotainment**

Support for terrestrial and satellite radio tuners, Wi-Fi, Bluetooth, GPS, cellular modem, iAP authentication modules, MOST vehicle networking, cameras and displays

| Supported             | Description                                  |  |  |

|-----------------------|----------------------------------------------|--|--|

| i.MX 6Quad            | Quad-core 800MHz-1GHz ARM Cortex-A9          |  |  |

| i.MX 6Dual (emulated) | Dual-core 800MHz-1GHz ARM Cortex-A9          |  |  |

| i.MX 6DualLite        | Dual-core 800MHz ARM Cortex-A9               |  |  |

| i.MX 6Solo (emulated) | Single-core 800MHz ARM Cortex-A9             |  |  |

| i.MX 6SoloX (Q3'15)   | 800MHz ARM Cortex-A9<br>200MHz ARM Cortex-M4 |  |  |

### **SABRE Board for Smart Devices**

Multiple connectivity options: Wi-Fi®, Bluetooth®, GPS, Ethernet, SD, parallel/serial interfaces, SATA (i.MX 6Quad only), and PCIe

| Supported                           | Description                                                            |

|-------------------------------------|------------------------------------------------------------------------|

| i.MX 6Quad<br>i.MX 6Dual (emulated) | Quad-core 1-1.2 GHz ARM Cortex-A9<br>Dual-core 1-1.2 GHz ARM Cortex-A9 |

| i.MX 6SoloX                         | 1GHz ARM Cortex-A9<br>200MHz ARM Cortex-M4                             |

### i.MX 6SoloLite Evaluation Kit

- Enables EPD and/or LCD or HDMI display, touch control and audio playback, and the ability to add WLAN, a 3G modem or Bluetooth technology

- E-Ink display available separately

| Supported      | Description                    |

|----------------|--------------------------------|

| i.MX 6SoloLite | Single-core 1GHz ARM Cortex-A9 |

# I.MX 6DUALPLUS & 6QUADPLUS

# i.MX 6QuadPlus / i.MX 6DualPlus Applications Processor

NXP identified multiple fabric and IP changes to improve the overall memory and graphics performance of the existing i.MX 6Dual/6Quad processors while minimizing software changes, resulting in the i.MX 6DualPlus/6QuadPlus family of processors

### • i.MX 6DualPlus/6QuadPlus key features:

- Updated 3D, 2D and OpenVG GPUs

- New pre-fetch and resolve modules to improve efficiency (effective for improving performance and memory bandwidth utilization and decreasing bus load)

- Fabric modifications to improve memory bandwidth

- Pin compatible with existing i.MX 6Dual/6Quad processors

- Multiple i.MX 6Dual/6Quad errata fixes

# i.MX 6DualPlus/i.MX 6QuadPlus Target Applications

### **Automotive**

- Infotainment

- Instrument Clusters

### **Smart Devices**

- Aerospace / Defense

- Digital Signage

- Health Care patient monitoring, fitness equipment

- Factory, process and building automation (gateways, surveillance, HMI)

- Home entertainment, appliances

- Media Streaming

- Transportation industrial vehicle with control & HMI, e.g. tractor, train, ship, heavy equipment

# i.MX 6QuadPlus/DualPlus Block Diagram

### **Specifications**

- · CPU:

- i.MX 6QuadPlus: 4x Cortex-A9 @ 800MHz/852MHz/1GHz/1.2 GHz\*

- i.MX 6DualPlus: 2x Cortex-A9 @ 800MHz/852MHz/1GHz/1.2 GHz\*

- **GPU**: GC2000+, 21.78 GFLOPS

- Process: 40nm

- Package: 21x21 0.8mm Flip-chip BGA

- Temp Range (Tj):

- Auto -40 to 125C

- Industrial -40 to 105C

- Extended Commercial -20 to 105C

- · Pin compatible with i.MX 6Quad/6Dual

- Up to 11,520 DMIPS

System Control Connectivity **CPU Platform** Secure JTAG MMC 4.4/ USB2 HSIC Quad ARM® Cortex™-A9 Core SD 3.0 x3 Host x2 PLL, Osc. 32 KB I-Cache 32 KB D-Cache per Core per Core MMC 4.4/ MIPI HSI Clock and Reset SDXC **NEON** per Core PTM per Core S/PDIF Smart DMA UART x5, Tx/Rx 1 MB L2-Cache + VFPv3 5 Mbps IOMUX PCIe 2.0 Multimedia Timer x3 (1-Lane) PC x3. Hardware Graphics Accelerators SPI x5 PWM x4 Enhanced 3D Vector Graphics FlexCAN x2 Enhanced 2D MLB150 + Watch Dog x2 ESAI, ISS/SSI DTCP Prefetch and Resolve **Power Management** 3.3V GPIO Video Codecs Audio 1 Gb Ethernet Temperature Power. 1080p30 Enc/Dec ASRC + IEEE® 1588 Monitor Supplies Keypad Imaging Processing Unit Internal Memory NAND Cntrl. Image Enhancement Resizing and Blending ROM RAM S-ATA and (BCH40) Inversion/Rotation PHY 3 Gbps Security LP-DDR2. Display and Camera Interface RNG Security Critit DDR3/ USB2 OTG 24-bit RGB, LVDS (x2) HDMI and PHY LV-DDR3 and PHY TrustZone Secure RTC **USB2 Host** x32/64. MIPI DSI 20-bit CSI 533 MHz and PHY Ciphers eFuses MIPI CSI2

<sup>\* 1.0</sup> GHz available now. For 1.2 GHz, contact NXP for availability

# SABRE Board for Smart Devices (SDB) – i.MX 6QuadPlus

Website: www.nxp.com/sabresdb

Part Numbers: MCIMX6QP-SDB (Feb 23, 2016)

Display (10.1"): MCIMX-LVDS1 Display (4.3"): MCIMX28LCD

### Overview

- NXP i.MX 6QuadPlus

–i.MX 6DualPlus emulation on 6QuadPlus

- •NXP MMPF0100 vF9 PMIC

- •1 GB DDR3 memory (non terminated)

- •3" x 7" 8-layer PCB

### **Display Connectors**

- •2x LVDS connectors

- Connector for 24 bit 4.3" 800x480 WVGA with 4-wire touch screen

- HDMI Connector

### **Audio**

- Audio Codec

- Microphone and headphone jacks

### Connectivity

- •2x full-size SD/MMC card slot

- •22-pin SATA connector

- •10/100/1000 Ethernet port

- •1x high-speed USB OTG port

- mPCI-e connector

### **Debug**

- JTAG connector

- Serial to USB connector

### **Expansion Connector**

- Enables parallel LCD or HDMI output

- Camera CSI port signals

- I2C, SSI, SPI signals

### **Additional Features**

- 3-axis NXP accelerometer

- eCompass

- Power supply

- No battery charger

### **OS Support**

- ·Linux and Android BSPs from NXP

- •Others: 3rd parties

### **Tools Support**

- Lauterbach

- •ARM (DS-5)

- Macraigor

### WiFi: (not included with kit)

- Silex WiFi module

- Murata WiFi module

### **Power**

- Because of the changes to GPU, bus fabric and other modules in the VDD\_SOC domain, the maximum power consumption will increase compared to i.MX 6Dual/6Quad

- Customer applications that are DDR intensive may consume more power, including NVCC\_DRAM supply rail due to the increased throughput in the Plus' DRAM subsystem

- Datasheet provides max power numbers to help board/system designers budget for the power supply. Typical power numbers are lower.

- Power consumption is use case dependent and also varies with temperature of operation

- Various SW power management techniques are available in the BSP to help with power management in the customer application

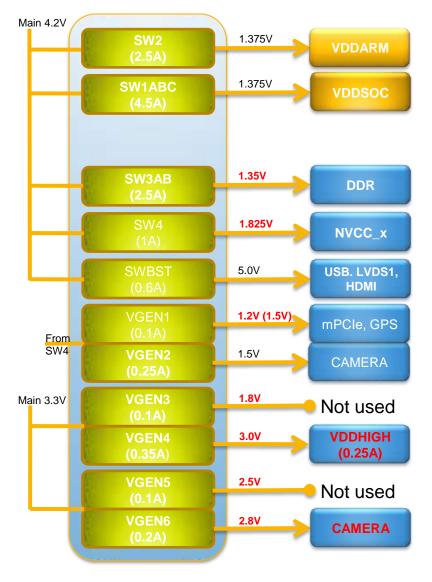

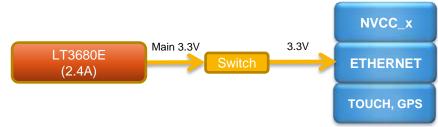

# i.MX 6DualPlus/6QuadPlus SABRE SDB PF0100 Configuration

| Power Sequence |                  |  |  |  |  |

|----------------|------------------|--|--|--|--|

| 0              | SNVS (not shown) |  |  |  |  |

| 1              | VGEN4            |  |  |  |  |

| 2              | SW1ABC, SW2      |  |  |  |  |

| 3              | SW3AB, VREFDDR   |  |  |  |  |

| 4              | SW4, VGEN6       |  |  |  |  |

| 5              | VGEN2, 3 & 5     |  |  |  |  |

PF0100 Part Number: MMPF0100F9ANES

(Recommended for Consumer and Industrial Applications)

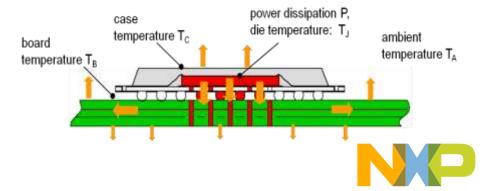

# Package & Thermals

- Plus uses the same package and ball map as i.MX 6Dual/6Quad

- VDD\_HIGH and VDD\_SNVS are specified to a maximum 3.3V in i.MX 6Dual/6Quad, in Plus the specified maximum is increased to 3.6V

- Improved thermal management may be required, compared to i.MX 6Dual/6Quad, due to the increased power consumption

- Software should take advantage of i.MX6 hardware features that allow power optimization

- Factor thermals in early in the Board Design process

- Run thermal simulations to get a holistic system thermal design & identify possible thermal bottlenecks

- NXP can provide Flotherm thermal models on request

### Same package and ball map

### Heat flow through the board

### Conclusion

- Major changes between the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus processors

- Updated 3D, 2D and OpenVG GPUs

- New pre-fetch and resolve modules to improve efficiency

- Fabric modifications to improve memory bandwidth

- Increased On Chip RAM (OCRAM)

- Multiple i.MX 6Dual/6Quad errata fixes

- Pin compatible with existing i.MX 6Dual/6Quad processors

- Design changes required to migrate to the Plus processors

- Increased power supply requirements for VDD\_SOC domain and DRAM sub-system

- SW changes minimized to new IP modules and issue fixes

- PF0100 PMIC for use with Plus designs

- F9 PF0100 derivative, as used on the SABRE AI CPU3 and SABRE SDB Plus platforms

- Performance benchmarks between the i.MX 6Dual/6Quad and i.MX 6DualPlus/6QuadPlus processors

- Improved ARM performance

- Improved graphics and DRAM performance

# Q & A

- i.MX 6QuadPlus Product Summary Page:

- <a href="http://www.nxp.com/products/microcontrollers-and-processors/arm-processors/i.mx-applications-processors-based-on-arm-cores/i.mx-6-processors/i.mx6qp/i.mx-6quadplus-processor-quad-core-high-performance-advanced-3d-graphics-hd-video-advanced-multimedia-arm-cortex-a9-core:i.MX6QP">http://www.nxp.com/products/microcontrollers-and-processors/arm-processors/i.mx-applications-processors-based-on-arm-cores/i.mx-6-processors/i.mx6qp/i.mx-6quadplus-processor-quad-core-high-performance-advanced-3d-graphics-hd-video-advanced-multimedia-arm-cortex-a9-core:i.MX6QP</a>

- i.MX 6DualPlus Product Summary Page:

- <a href="http://www.nxp.com/products/microcontrollers-and-processors/arm-processors/i.mx-applications-processors-based-on-arm-cores/i.mx-6-processors/i.mx6qp/i.mx-6dualplus-processor-dual-core-high-performance-advanced-3d-graphics-hd-video-advanced-multimedia-arm-cortex-a9-core:i.MX6DP">http://www.nxp.com/products/microcontrollers-and-processors/arm-processors/i.mx-applications-processors-based-on-arm-cores/i.mx-6-processors/i.mx6qp/i.mx-6dualplus-processor-dual-core-high-performance-advanced-3d-graphics-hd-video-advanced-multimedia-arm-cortex-a9-core:i.MX6DP</a>

- i.MX 6 Sabre Tool Summary Page:

- <u>www.nxp.com/imx6tools</u>

Contact your local NXP representative

## **FAQ**

Q: Was the VPU enhanced and did the VPU performance change on Plus?

A: Same IP for the VPU on Plus, however users can expect improved performance in multimaster use cases using the VPU due to fabric enhancements discussed.

Q: Is the PMIC configuration proposed for Plus backward compatible to 6Dual/6Quad?

A: Yes, we recommend all new 6Dual/6Quad to use this new configuration to allow for future upgrades to the Plus

Q: What guidelines should I follow if I am starting a new design with the i.MX 6Dual/6Quad and i.MX 6DualPlus/QuadPlus?

A: For new designs it is recommended to use F9, FA or similar custom OTP flavor of the PF0100 for powering the system. This provides a single power solution for i.MX 6Dual/6Quad and i.MX 6DualPlus/QuadPlus while also providing sufficient margin for the worst case load currents.

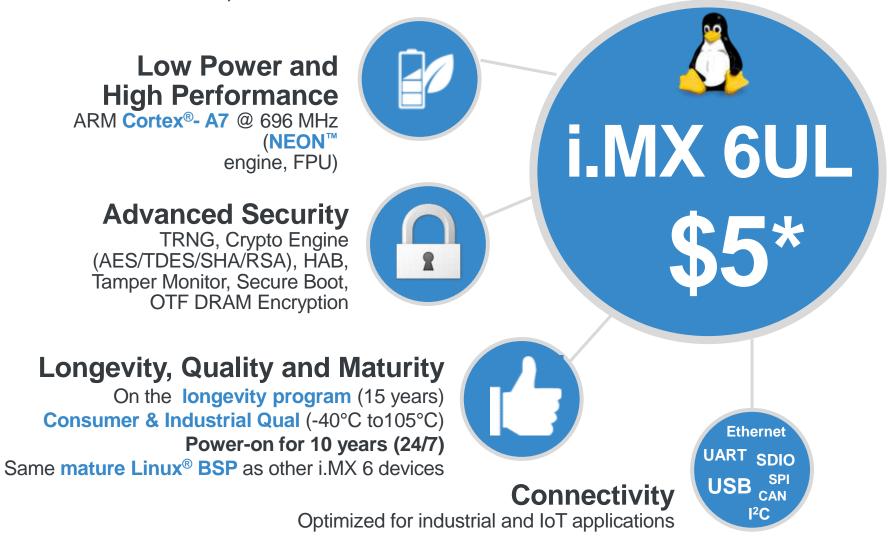

# I.MX 6ULTRALITE

### i.MX 6UltraLite

The Most Power-efficient, Lowest Cost and Smallest i.MX 6 Member

# i.MX 6UltraLite Target Applications

### **Industrial HMI**

- XGA industrial HMI with basic UI

- Large or highquality small appliance

- Industrial scanner or printer

- Vending machine with display and basic UI

# **Building Control**

- Access control (security) panel

- Surveillance monitoring

- Building control, e.g. elevator or automated door

### **Medical**

- Mobile patient care, e.g. infusion pump or respirator

- Blood pressure monitor

- Activity and wellness monitor

- Exercise equipment with display

# Integrated Connectivity

- Wired and wireless audio streaming

- Energy management hub

- Industrial gateway

- VoIP

# Financial Payment

- Point of Sale

- Financial payment system

# i.MX 6UltraLite Evaluation Kit Key Features

Part Numbers: MCIMX6UL-EVKB (\$149) Display (4.3"): LCD8000-43T (\$100)

### **Processor**

• NXP Semiconductors i.MX 6UltraLite 528MHz ARM®

Cortex™-A7 CPU

### **Memory**

- 4Gb DDR3L DRAM memory

- 256Mb Quad SPI Flash

- Footprint for NAND

- Footprint for eMMC

- TF socket for boot

### Display

- Parallel WVGA LCD add-on card via expansion connector

- Camera Connector

### **Audio**

- Audio Codec

- 4-pole Audio Headphone Jack

- External speaker connection

- Microphone

### Connectivity

- USB Host connector

- Micro USB OTG connector

- Two Ethernet (10/100T) connector

- SD/SDIO Connector

- Two CAN Transceivers

- EMV Smart Card connector

### Debug

- JTAG connector

- Serial to USB connector

### Sensors

- Footprint for FXAS21000CQR1 Gyro

- FXLS8471Q three-axis digital accelerometer

- MAG3110 Digital eCompass

### **Tools & OS Support**

Linux® BSPs from NXP Semiconductors

### **Others**

CPU Module: 1.67x2.66 inch

Base Board: 4.25x5.12 inch

4 layer through hole PCB

# BOARD BRING-UP: WHERE DDR BRING-UP FITS IN

### i.MX 6UL MMDC Overview

### **DDR** Initialization

- i.MX 6UL MMDC is used to program DDR device for proper operation

- Achieved by initialization sequence of specific register writes prior to accessing external DDR device

- DDR initialization is dependent on various factors such as:

- DDR type (DDR3 or LPDDR2)

- DDR memory timing and speed grade

- Bus width (x16 only)

- Drive Strength and Board/Memory layout (Fly-by, T topology)

- Common programming recommendations cannot be provided as they will be unique for each customer design based on the above factors

- NXP provides a DDR Register Programming Aid to help in configuring these specific parameters as well as DDR stress test that optimizes and tests the DDR interface

# **Board Bring-Up and Debug Checklist**

| Chec  | 1, | liat | Itam |

|-------|----|------|------|

| t nec | ĸ  | 1181 | Hem  |

The following items need to be completed serially

Visual Inspection

Verify all SoC voltage rails

Verify power up sequence

Measure/probe input clocks (32kHz, 24MHz, others)

JTAG connectivity (DS-5, RV-ICE, Lauterbach, Macraigor, etc)

Access internal RAM

### Run basic DDR initialization and test memory

### Run DDR Stress test

The following items may be worked on in parallel with other bring up tasks

Verify CLKO outputs (measure and verify default clock frequencies for desired clock output options); this assumes that the board design supports probing of the CLKO pin.

Measure boot mode frequencies (set the boot mode switch for each boot mode and measure the following, depending on what is available in the system):

- NAND (probe CE to verify boot, measure RE frequency)

- SPI-NOR (probe slave select and measure clock freq)

- MMC/SD (measure clock freq)

Run other unit tests

# Tools for DDR Bring-up and debug

# Run basic DDR initialization and test

memory

**Run DDR Stress test**

### **DDR Register Programming Aid**

Use a JTAG debugger, run the **DDR initialization** and open a debugger memory window pointing to the DDR memory map starting address, or use the DDR stress test connected via USB. Try writing a few words and verify if they can be read correctly. If not, re-check the **DDR initialization** sequence and if the DDR has been correctly soldered onto the board. It is also recommended to re-check the schematic to ensure the DDR memory has been connected to the SoC correctly. In some cases, a DDR calibration routine may need to be executed, see next row.

A non-OS based, bare-metal unit test that focuses on the robustness of the DDR interface. Downloaded through JTAG debugger or USB into internal RAM. MX6UL includes option to run DDR calibration.

### **DDR Stress Test**

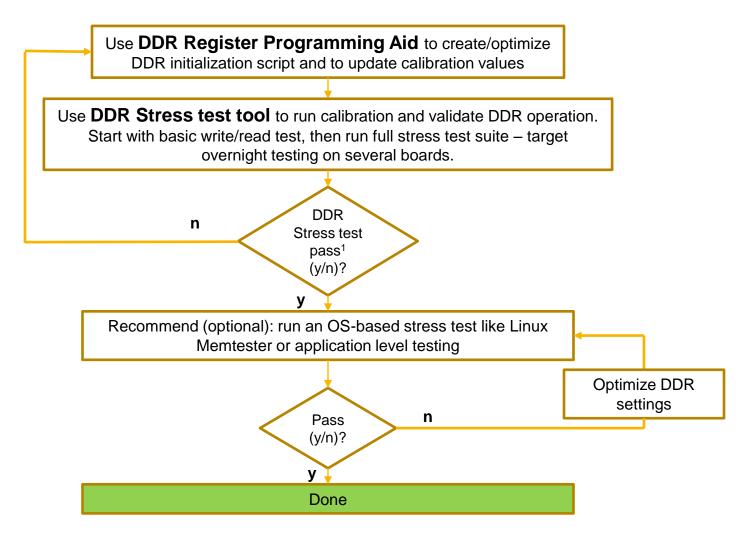

# Recommended Flow and Tools for Optimal DDR Initialization

**Create initial DDR initialization script**

- Use the DDR Register Programming Aid

- Input values from Memory vendor datasheet

Perform calibration to optimize script

- Use the **DDR Stress Test**:

Calibration Routine

- Generates optimal calibration values

Validate DDR interface with optimized script

- Use DDR Stress

Test: Memory Sub routines

- Using updated calibration values

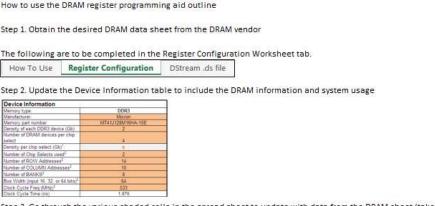

# DDR REGISTER PROGRAMMING AID

### Intro

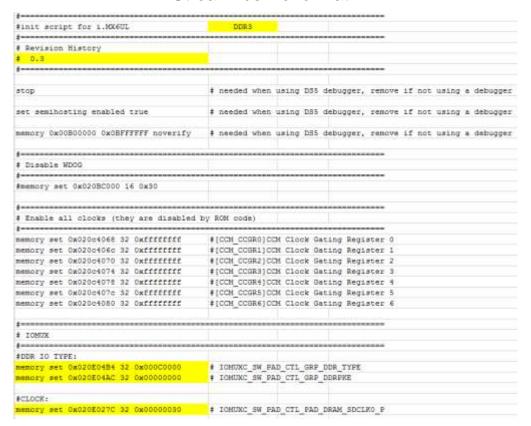

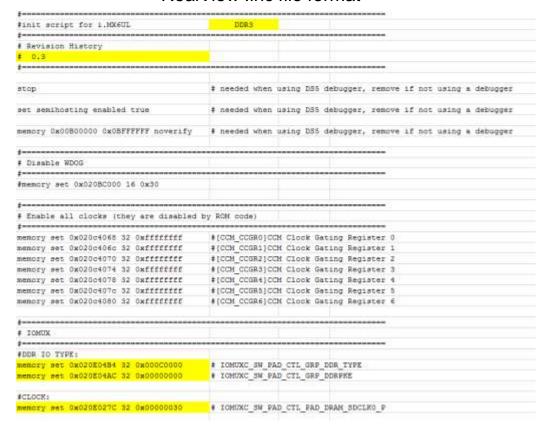

- DDR Register Programming Aid creates JEDEC compliant sequence to initialize DDR memory and interface

- IOMUX register writes to set i.MX 6UL DDR IO drive strength

- MMDC register writes and DDR mode register writes

- Mainly used to program JEDEC timing and DDR parameters

- Timings: tRCD, tRC, tRFC, etc; Parameters: rows, cols, bank address, and chip selects

- Memory timing information obtained from DDR vendor datasheet for respective speed grade and density

- Automatically generates DDR initialization scripts

- For specific memory types (DDR3 or LPDDR2)

- For ARM RVD (.inc file) and ARM DS5 (.ds file) debugger formats

- Scripts can be converted by user to DCD format for inclusion in SW OS Bootloader

- Developed based on NXP development boards; can be customized by user for their board design

### Intro

- Each Programming Aid tool based on DDR technology: DDR3 or LPDDR2

- Useful for quickly changing parameters:

- Drive strength, user selects via pull down menu

- DDR Mode register settings configures mode register "word" to send to the DDR

- Calibration fields highlighted for user update

- Applies correct order of programming MMDC registers

- Detailed instructions on how to generate custom scripts

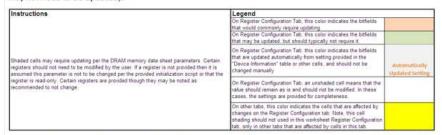

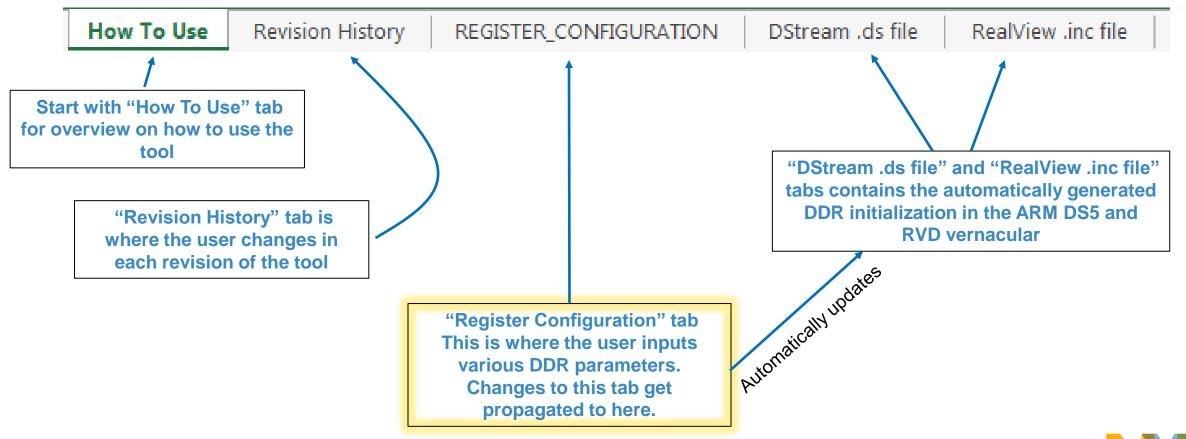

Step 3. Go through the various shaded cells in the spread sheet to update with data from the DRAM sheet (take special note of the "Legend" table to ascertain the meaning of different shaded cells; in many cases, the cells may not need to be updated).

The following refers to the "DStream .ds file" Worksheet tab. In this tab, the entire DRAM initialization can be obtained. This initialization can be used as a DStream .ds file (see below) or as reference for the bootloader DRAM initialization.

How To Use Register Configuration DStream .ds file

Step 4. Go to the "DStream .ds file" file worksheet tab and copy and paste this into a text document (make sure to rename the document with a ".ds" file ending); this is ready to use with the ARM DStream development

Step 5. This .ds file can also be used as a reference for other debugger tools and bootloaders.

Note, there are some commands that are specific for the DS5 debugger and are noted in the "Dstream .ds file" work sheet. These commands should be commented out or removed for use in bootloaders or non-debugger based DDR stress tests (for example, when using a USB loadable DDR stress test)

Walkthrough

There are several tabs (worksheets), described below

### Walkthrough

Debugger scripts automatically generated

### DStream .ds file format

### How To Use Revision History REGISTER\_CONFIGURATION DStream .ds file RealView .inc file

### RealView .inc file format

Copy and paste these commands into a text file and re-name file as <file\_name>.ds or <file\_name>.inc

# DDR STRESS TEST

#### **Overview**

- Non-OS test to exercise DDR interface

- Non-OS (bare-metal): easier than OS to catch/debug DDR failures

- Helps diagnose but doesn't fix DDR problems

- Primarily uses sequential bursts of back-to-back data looking for simultaneous switching noise (SSN)

- Validation vehicle that reports how robust DDR interface is given current set of parameters (i.e. drive strength settings, timing parameters, board layout, etc)

- Runs from internal RAM

- Device under test is DDR itself, doesn't execute from same memory being tested

- DDR region tagged as cacheable to take advantage of cache line flush/fill resulting in long burst accesses

- Increment DDR frequency

- Method to stress interface accounting for variations in PVT

#### **Overview**

- Supports Calibration

- MMDC has built-in support for various calibrations

- All controllers support run-time ZQ calibration: ZQ calibration is something simply enabled, no user interaction

- New GUI version developed to make it easier to run

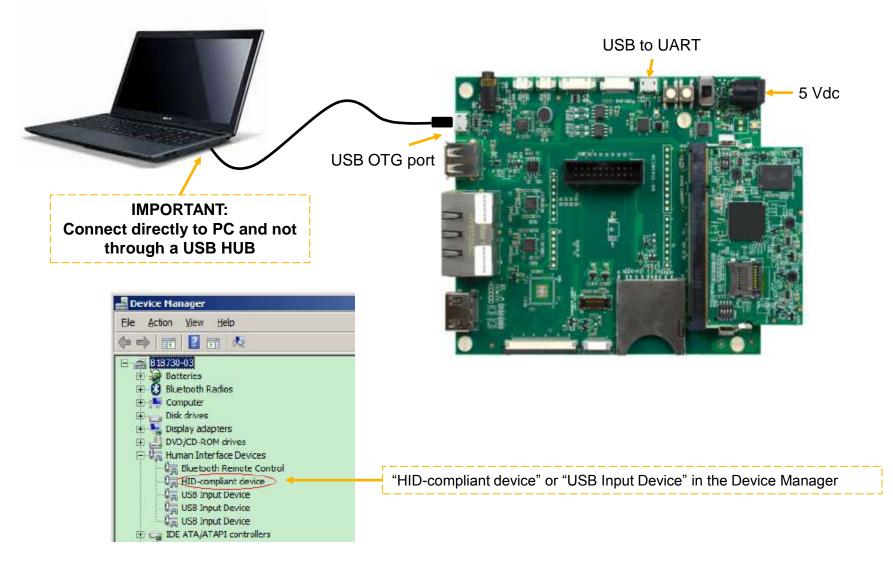

- GUI-based tool uses USB connected from Host PC to i.MX 6 board USB

OTG port

- JTAG version (elf) allows use with debugger and serial terminal

- Binary version (bin) allows user to run under u-boot

- Available on i.MX Community: <a href="https://community.freescale.com/docs/DOC-105652">https://community.freescale.com/docs/DOC-105652</a>

#### Overview

Once DDR stress test passes with ample margin, are we guaranteed the OS will never fail due to DDR issues?

- High degree of confidence DDR robust enough, but...

- OS is still the most stressful, particularly an OS stress test like memtester or u-boot decompressing the Linux kernel

- Recommend to run any OS stress tests to double check

#### Differences between non-OS DDR stress test and OS based stress

| DDR Stress Test                                               | OS stress test (like memtester)                                       |

|---------------------------------------------------------------|-----------------------------------------------------------------------|

| increments DDR frequency above max                            | runs at fixed frequency                                               |

| single-task, lightweight (nothing else runs)                  | runs under OS, lots of stuff running, more system stress              |

| runs from OCRAM, easier to catch DDR failures (data failures) | harder since it runs from DDR (could see data failure or code lockup) |

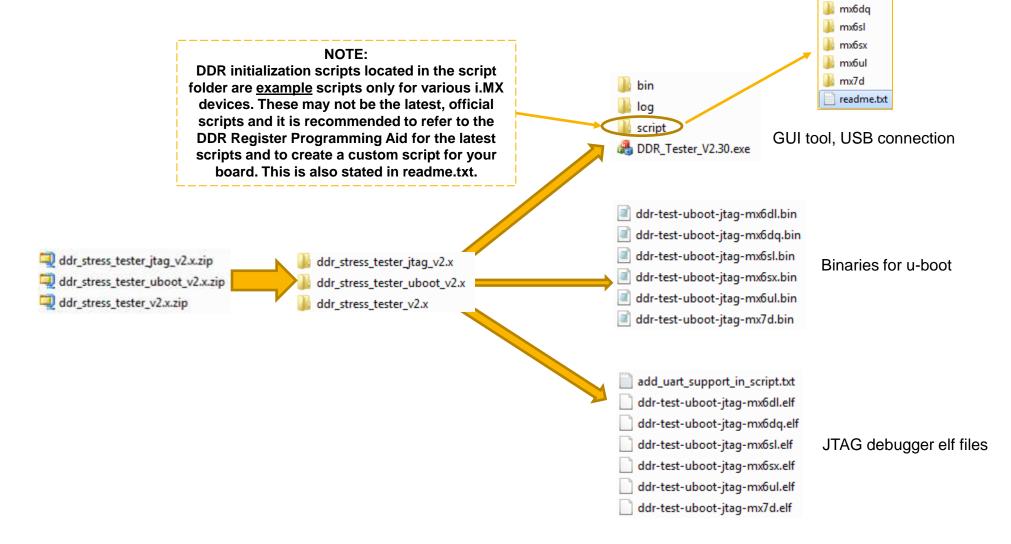

#### **Zip contents**

iii mx6dl

# **Connecting to the EVK**

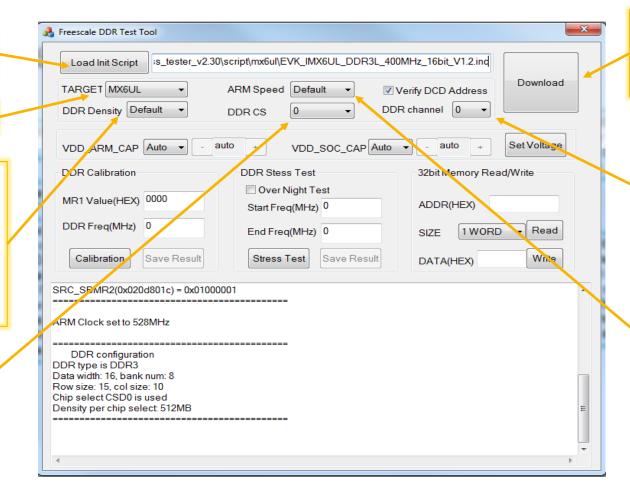

#### **GUI** walk through: downloading to EVK

Select the desired DDR init script

2 Select MX6UL as target

It is recommended to leave the DDR density option as Default.

The Density information is obtained from the init script.

Future improvements will allow user to select a lower density allowing them to run a quicker test.

EVK uses CSD0 only, so this should be 0.

When the MX6UL option is selected for TARGET and the desired DDR init script is selected, hit Download

For use with LPDDR2 memories, MX6UL only supports single channel, leave as default

For MX6UL, it is recommended to leave the ARM Speed as default as the current max speed is 528MHz. The other ARM speed options are not applicable to i.MX 6UL.

6

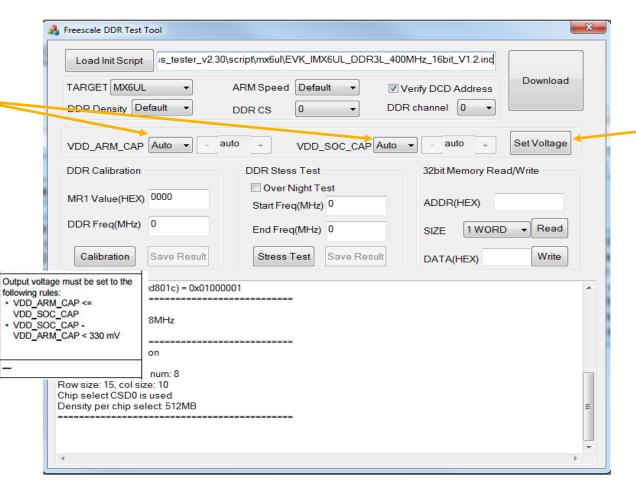

#### **GUI** walk through: voltage select option

Pull down option selects between Auto and Manual. "Manual" allows user to adjust voltages, but user must abide by data sheet (see below).

A7 core at 528

A7 core at 396

MHz

A7 core at 198

MHz

1.15

1.00

0.925

1.15

1.3

1.3

1.3

1.3

V

When manually setting the voltage, hit Set Voltage to engage.

VDD\_ARM\_CAP

VDD\_SOC\_CAP

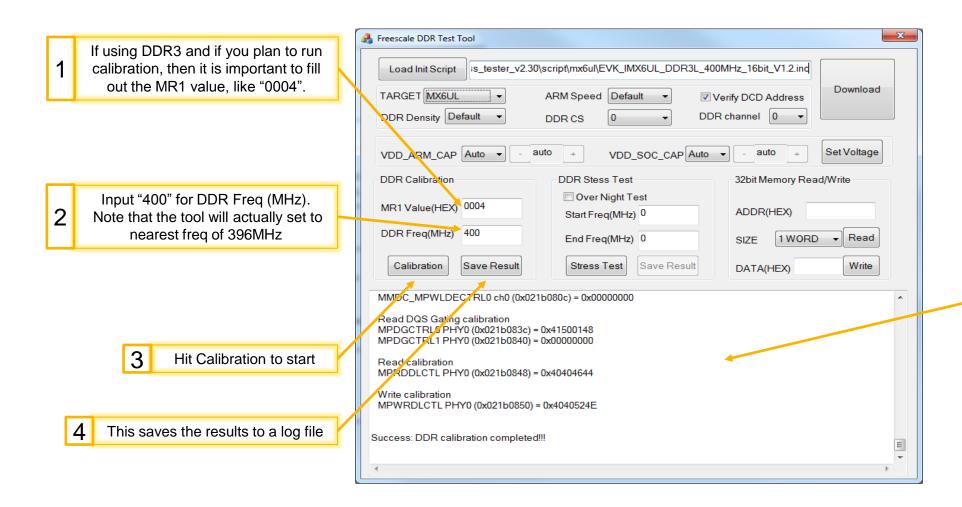

#### **GUI** walk through: calibration

Copy Calibration values and put into your init script

5

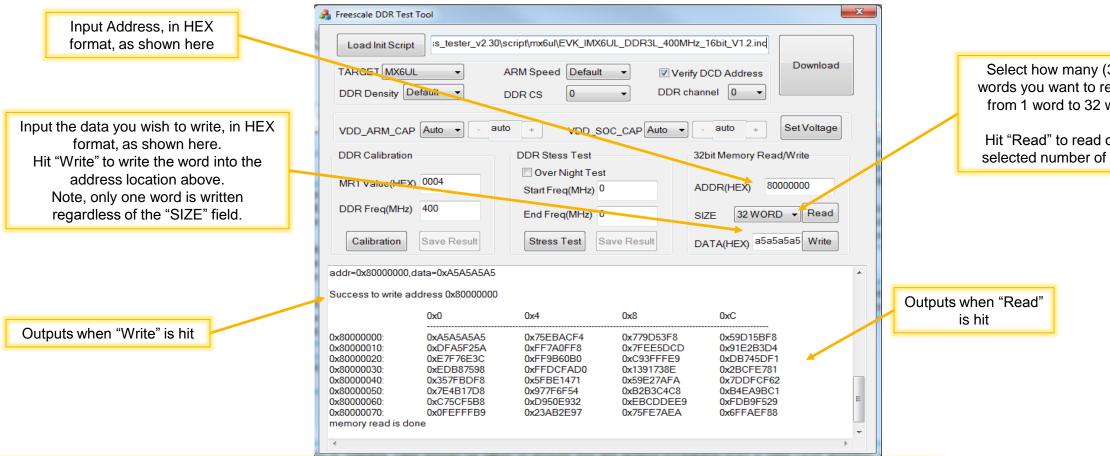

#### GUI walk through: simple memory write/read test

Select how many (32-bit) words you want to read out, from 1 word to 32 words.

Hit "Read" to read out the selected number of words.

Note: when writing or reading, care should be taken to ensure you are writing-to/reading-from a valid DDR address, else you could hang the tool (at which point you'll have to re-start the tool).

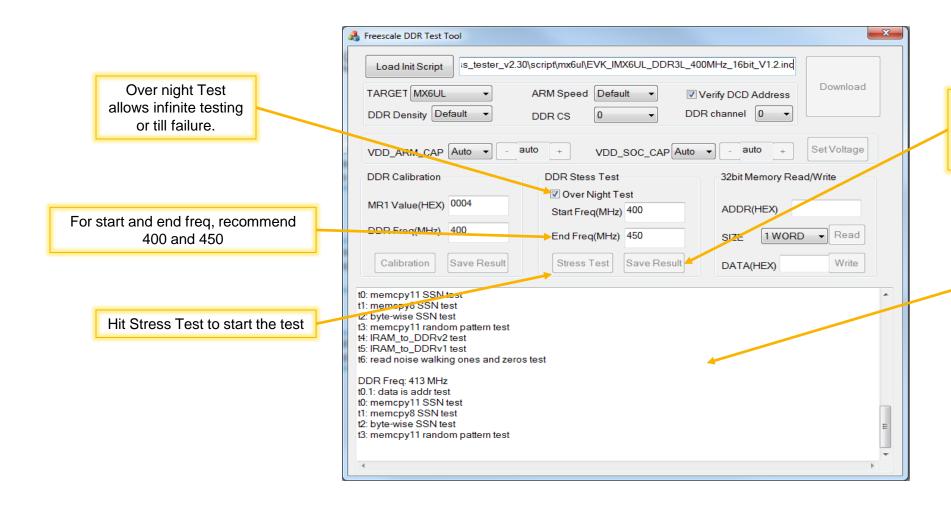

#### **GUI** walk through: running the stress test

When testing completes (either when select finite testing or failure occurs), you can save output to log file

Stress test output, shows current test frequency and subtests, along with the iteration if running with Over Night Test selected.

# i.MX 6UL MMDC Tool Usage Flow Chart

1. When running stress test with incrementing frequency, usually target ~%10 above maximum freq. For 400MHz, target at least 440MHz

# I.MX 7SOLO & I.MX 7DUAL

# Growing Number of Embedded Use Cases Require Concurrent Execution of Isolated and Secure Software Environments

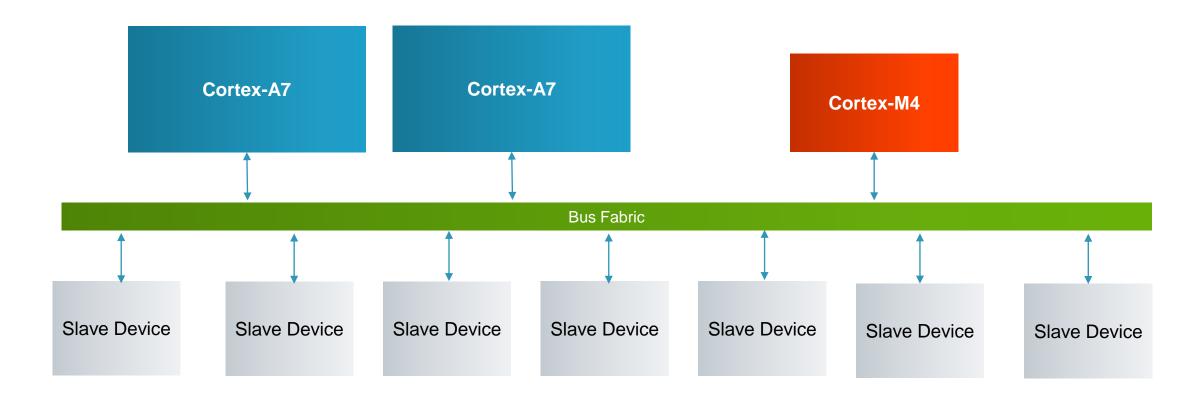

# **Heterogeneous Multicore Processing (HMP)**

# **Shared Topology**

# i.MX 7Dual/Solo Family Target Applications

#### **MOBILE DEVICES**

# LPDDR2/3 Small Package

- Healthcare / Patient Monitoring

- HMI Control / Security

- Point of Sale

- Printing

- Home Control

- Wearables

- eReaders

- General Embedded Control

- Embedded Board Solutions

- IoT

#### **CONNECTED DEVICES**

# Low Cost DDR3 Larger Pitch Package

# i.MX 7Solo and i.MX 7Dual

#### i.MX 7Solo

- Single ARM® Cortex®-A7 up to 800 MHz

- Cortex-M4 up to 200 MHz

- 512KB L2 cache

- 16/32-bit DDR3/DDR3L and LPDDR2/3 at 533 MHz

- Single Gigabit Ethernet (AVB)

- Full security with tamper resist

#### i.MX 7Dual

- Dual ARM® Cortex®-A7 up to 1.0 GHz

- Cortex-M4 up to 200 MHz

- 512 KB L2 cache

- 16/32-bit DDR3/DDR3L and LPDDR2/3 at 533 MHz

- Dual Gigabit Ethernet (AVB)

- Full security with tamper resist

- EPD controller

- PCle (x1 lane)

Red indicates change from column to the left

Pin-to-pin and power compatible

Software compatible

Consumer

Extended Consumer

# **Q & A**

- i.MX Product Summary Page:

- <a href="http://www.nxp.com/products/microcontrollers-and-processors/arm-processors/i.mx-applications-processors:IMX\_HOME">http://www.nxp.com/products/microcontrollers-and-processors/arm-processors/i.mx-applications-processors:IMX\_HOME</a>

- i.MX 6 Series Software and Development Tool Resources

- <a href="http://www.nxp.com/products/microcontrollers-and-processors/arm-processors/i.mx-applications-processors/i.mx-6-processors/i.mx6qp/i.mx-6-series-software-and-development-tool-resources:IMX6\_SW?tid=vanIMX6TOOLS#bsp

- i.MX 6 Sabre Tool Summary Page:

- www.nxp.com/imx6tools

Targeted i.MX7 Global Full Market Launch (which means mass market launch) date is July 18, 2016 (US time)

# SECURE CONNECTIONS FOR A SMARTER WORLD

#### ATTRIBUTION STATEMENT

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, CoolFlux, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE, MIFARE Classic, MIFARE DESFire, MIFARE Plus, MIFARE Plus, MIFARE Flex, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TrenchMOS, UCODE, Freescale, the Freescale logo, AltiVec, C 5, CodeTEST, CodeWarrior, ColdFire+, C Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorlQ, QorlQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. ARM, AMBA, ARM Powered, Artisan, Cortex, Jazelle, Keil, SecurCore, Thumb, TrustZone, and µVision are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. ARM7, ARM9, ARM11, big.LITTLE, CoreLink, CoreSight, DesignStart, Mali, mbed, NEON, POP, Sensinode, Socrates, ULINK and Versatile are trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2015–2016 NXP B.V.