# Low-Power Modes for MPC5xxx and Beyond

**Steve Mihalik**

Senior Field Application Engineer

October 2018 | AMF-AUT-T3381

Ĥ

Company Public – NXP, the NXP logo, and NXP secure connections for a smarter world are trademarks of NXP B.V. All other product or service names are the property of their respective owners. © 2018 NXP B.V.

# Agenda

- Mode Entry Module Introduction

- Use Case

- Low Power Modes

- HW Implications:

- Terminations

- Pad Keeping

- SW Implications:

- Configuration

- Entering low power

- Exiting low power

- MCAL

Debugging and When Things Go Wrong

#### Abstract

Achieving the lowest MCU power during sleep presents challenges to HW and SW designers from switching off clocks and power to modules.

Low power use cases and concepts for NXP's Mode Entry module are presented along with implications to hardware design, software design and debugging.

# Use Case: Conserving Power While Software Runs (1 of 2)

• Software *runs* one of the three following tasks:

#### - Analog Monitor

- Uses ADC to look for particular voltages on inputs

- Only requires 16 MHz FIRC, which is also sysclk

- If analog input measurements meet a criteria, software transitions to the communication task

#### - Communication

- Uses FlexCAN\_0, FlexCAN\_1 to transmit analog data and receive response

- Only requires FXOSC, which is also sysclk

- If response is positive, software transitions to the whole chip task

#### -Whole Chip

- Requires all peripherals active

- Sysclk = maximum frequency FMPLL, which also requires FXOSC

#### Use Case: Conserving Power While Software Runs (2 of 2)

| Mode            | sysclk | syscik Clock Sour |            | s Req'd            | Peripherals Requiring                               |

|-----------------|--------|-------------------|------------|--------------------|-----------------------------------------------------|

|                 |        | FIRC              | XOSC       | FMPLL              | Enabled Clock                                       |

|                 | ← M    | ode Co            | nfiguratio | on <del>&gt;</del> | $\leftarrow$ Peripheral Configuration $\rightarrow$ |

| RUNO: AnalogMon | FIRC   | Х                 |            |                    | ADC, SIU                                            |

| RUN1: Comm      | XOSC   |                   | Х          |                    | FlexCAN_0, FlexCAN_1, SIU                           |

| RUN2: WholeChip | FMPLL  |                   | Х          | Х                  | All                                                 |

| Peripherals  | Mode | s with E | nabled | Clock | Peripheral                        | Peripheral's                                                |

|--------------|------|----------|--------|-------|-----------------------------------|-------------------------------------------------------------|

|              | RUN0 | RUN1     | RUN2   | RUN3  | Configuration<br>for RUN<br>modes | Control Register<br>(Specifies Peri.<br>Config. to be used) |

| ADC          | Х    |          | Х      |       | Run PC0                           | PCTL[32]                                                    |

| FlexCAN_0, 1 |      | Х        | Х      |       | Run PC1                           | PCTL[16], PCTL[17]                                          |

| SIU          | Х    | Х        | Х      |       | Run PC2                           | PCTL[68]                                                    |

| All others   |      |          | Х      |       | Run PC3                           | Other PCTL's                                                |

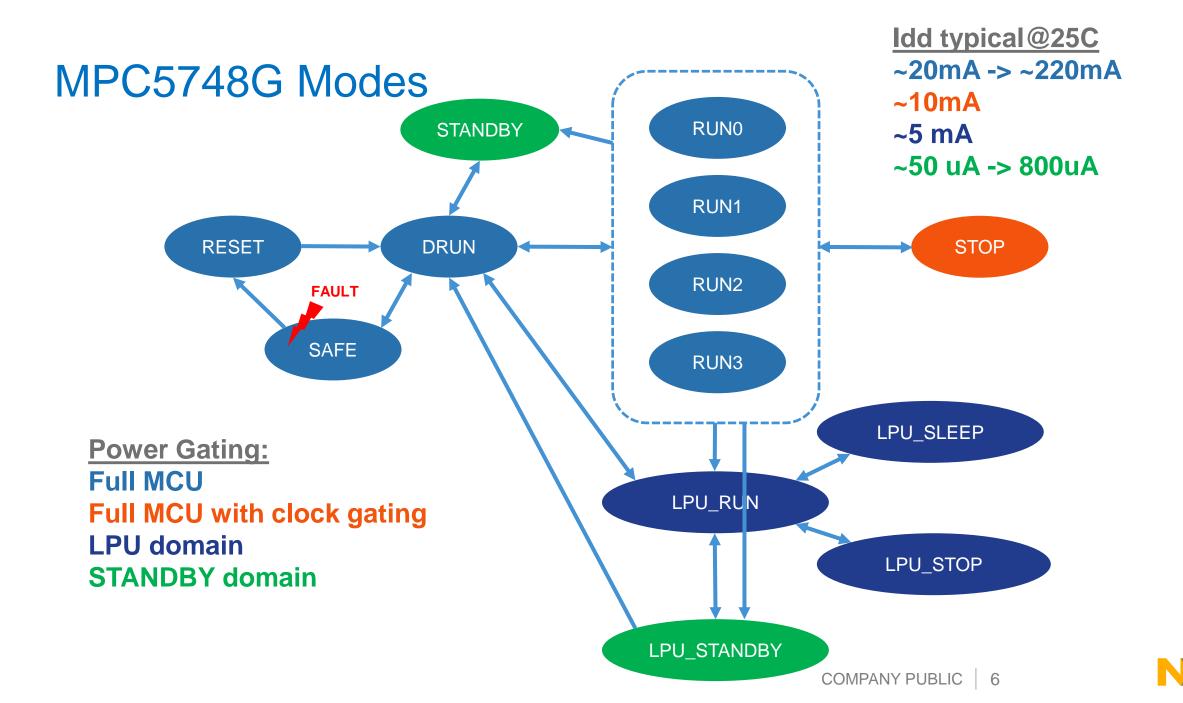

# Low Power Modes Summary (MPC5748G)

- **STOP** (11mA)

- In STOP mode the MCU remains completely powered

- Exit STOP mode on interrupt or wake-up

- Exiting STOP mode the MCU context is retained so no need to reconfigure core or peripherals

#### • STANDBY & LPU\_STANDBY (71uA)

- In STANDBY mode 99% of the MCU is powered-down

- Upon wake-up the MCU context is lost (except STANDBY peripherals)

#### • Wake-up source options for STOP and STANDBY modes

- 30x input pins

- Analog comparator

- Timers

- Non-Maskable Interrupt

- Interrupts (STOP mode only!)

#### Power block diagram

#### MPC574XG 6MB and 3MB STANDBY Current

Table 12. STANDBY Current consumption characteristics

#### MPC5746C Data Sheet, Rev 5.1, 05/2017

| Symbol   | Parameter    | Conditions <sup>1</sup> | Min | Тур | Max  | Unit        | M   | in | Тур | Max  | Unit |

|----------|--------------|-------------------------|-----|-----|------|-------------|-----|----|-----|------|------|

| STANDBY0 | STANDBY with | $T_a = 25 \text{ °C}$   | _   | 71  | _    | μA          | - 1 | -  | 71  | _    | μA   |

|          | 8K RAM       | T <sub>a</sub> = 85 °C  | _   | 175 | 800  | ]           | —   | 1  | 125 | 700  | ]    |

|          |              | T <sub>a</sub> = 105 °C | _   | 338 | 1725 |             | —   | 1  | 195 | 1225 | ]    |

|          |              | T <sub>a</sub> = 125 °C | _   | 750 | 2775 |             | —   | 3  | 314 | 2100 |      |

| STANDBY1 | STANDBY with | T <sub>a</sub> = 25 ℃   | _   | 72  | _    | μA          | -   | -  | 72  | _    | μA   |

|          | 64K RAM      | T <sub>a</sub> = 85 ℃   | _   | 176 | 815  | 815<br>1775 | —   | 1  | 140 | 715  |      |

|          |              | T <sub>a</sub> = 105 °C | _   | 350 | 1775 |             | —   | 2  | 225 | 1275 | ]    |

|          |              | T <sub>a</sub> = 125 °C | _   | 825 | 3000 |             | —   | 3  | 358 | 2250 | ]    |

| STANDBY2 | STANDBY with | T <sub>a</sub> = 25 °C  | -   | 75  | _    | μA          | -   | -  | 75  | _    | μA   |

|          | 128K RAM     | T <sub>a</sub> = 85 ℃   | _   | 182 | 830  |             | —   | 1  | 155 | 730  | 1    |

|          |              | T <sub>a</sub> = 105 °C | _   | 366 | 1825 | 1825        | —   | 2  | 255 | 1350 |      |

|          |              | T <sub>a</sub> = 150 °C | _   | 900 | 3250 |             | —   | 3  | 396 | 2600 |      |

| STANDBY3 | STANDBY with | T <sub>a</sub> = 25 °C  | -   | 80  | _    | μA          | -   | -  | 80  | _    | μA   |

|          | 256K RAM     | T <sub>a</sub> = 85 °C  | _   | 197 | 860  |             | —   | 1  | 180 | 800  |      |

|          |              | T <sub>a</sub> = 105 °C | _   | 400 | 1875 |             | —   | 2  | 290 | 1425 | 1    |

|          |              | T <sub>a</sub> = 125 °C | _   | 975 | 3500 |             | —   | 4  | 465 | 2900 | 1    |

| STANDBY3 | FIRC ON      | T <sub>a</sub> = 25 °C  | —   | 500 | _    | μA          | -   | -  | 500 | _    | μA   |

COMPANY PUBLIC 9

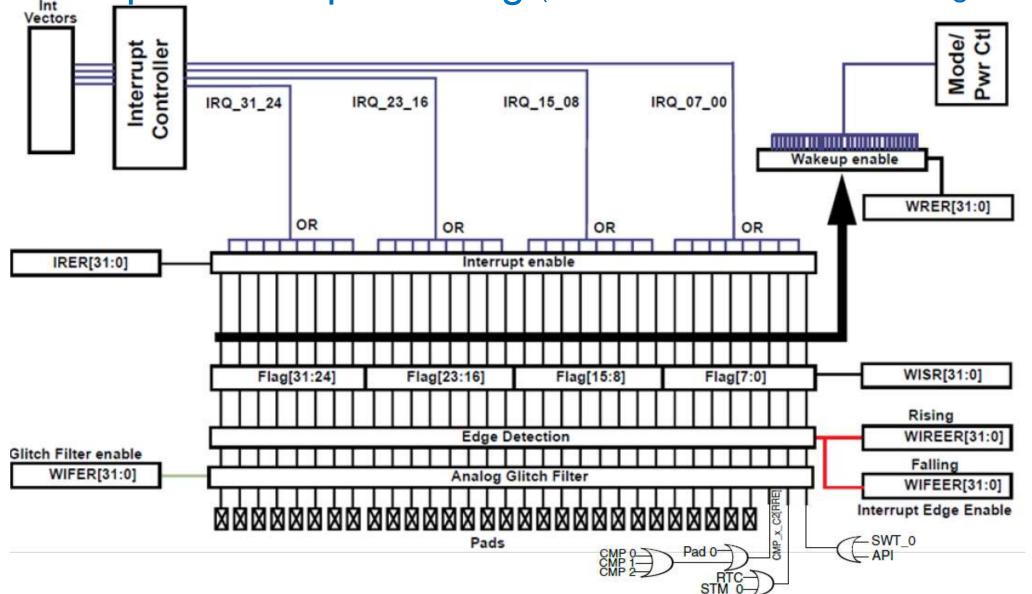

## Interrupt / wakeup – Signal identification

- See IO Signal Table in spreadsheet attached to MPC5748G Reference Manual

- WKPU[x] corresponds to wakeup / interrupt source (also called channel) in WKPU registers:

- Status (WISR)

- Interrupt Req. Enable (IRER)

- Wakeup Req. Enable (WRER)

- Rising Edge Enable (WIREER)

- Falling Edge Enable (WIFEER)

- Filter Enable (WIFER)

- Pull Enable (WIPER)

|                  |        | LVDS Pair |              |            |            |           |   |

|------------------|--------|-----------|--------------|------------|------------|-----------|---|

| 6                | Port 👻 | Port 👻    | SIUL MESR# 🚽 | MSCR SSS 👻 | Function 👻 | Modul 🚽   | D |

| 7                | PA[0]  |           | 0            | 0000_0000  | GPIO[0]    | SIUL2     |   |

| 8                | PA[0]  |           |              | 0000_0001  | E0UC_0_X   | EMIOS0    |   |

| 9                | PA[0]  |           |              | 0000_0010  | CLKOUT0    | CGM       |   |

| L <b>O</b>       | PA[0]  |           |              | 0000_0011  | E0UC_13_H  | EMIOS0    |   |

| 1                | PA[0]  |           |              | -          | WKPU[19]   | WKPU      |   |

| 12               | PA[0]  |           | 512          | 0000_0010  | E0UC_0_X   | EMIOS0    |   |

| 13               | PA[0]  |           | 525          | 0000_0010  | E0UC_13_H  | EMIOS0    |   |

| L <b>4</b>       | PA[0]  |           | 701          | 0000_0001  | CAN1RX     | FlexCAN_1 |   |

| 15               | PA[1]  |           | 1            | 0000_0000  | GPIO[1]    | SIUL2     |   |

| l <b>6</b>       | PA[1]  |           |              | 0000_0001  | E0UC_1_G   | EMIOS0    |   |

| 17               | PA[1]  |           |              | -          | WKPU[2]    | WKPU      |   |

| L <mark>8</mark> | PA[1]  |           |              | -          | NMI[0]     | WKPU      |   |

| L <b>9</b>       | PA[1]  |           | 513          | 0000_0010  | E0UC_1_G   | EMIOS0    |   |

| 20               | PA[1]  |           | 703          | 0000_0001  | CAN3RX     | FlexCAN_3 |   |

| 21               | PA[2]  |           | 2            | 0000_0000  | GPIO[2]    | SIUL2     |   |

| 22               | PA[2]  |           |              | 0000_0001  | E0UC_2_G   | EMIOS0    |   |

| 23               | PA[2]  |           |              | 0000_0010  | E2UC_0_X   | EMIOS2    |   |

| 24               | PA[2]  |           |              | 0000_0011  | ADC0_MA[2] | ADC_0     |   |

| 25               | PA[2]  |           |              | -          | WKPU[3]    | WKPU      |   |

| 26               | PA[2]  |           | 514          | 0000 0010  | FOUC 2 G   | FMIOS0    |   |

#### Interrupt / wakeup - pads list

List is filtered from MPC5748G IO Signals spreadsheet attached to reference manual

| <u>Port</u> | <b>Function</b> | <u>Module</u> |        |              |      |

|-------------|-----------------|---------------|--------|--------------|------|

| PA[0]       | WKPU[19]        | WKPU          | PE[0]  | WKPU[6]      | WKPU |

| PA[1]       | WKPU[2]         | WKPU          | PE[3]  | WKPU[29]     | WKPU |

| PA[2]       | WKPU[3]         | WKPU          | PE[5]  | WKPU[30]     | WKPU |

| PA[4]       | WKPU[9]         | WKPU          | PE[9]  | WKPU[7]      | WKPU |

| PA[15]      | WKPU[10]        | WKPU          | PE[11] | WKPU[14]     | WKPU |

| PB[1]       | WKPU[4]         | WKPU          | PF[9]  | WKPU[22]     | WKPU |

| PB[3]       | WKPU[11]        | WKPU          | PF[11] | WKPU[15]     | WKPU |

| PB[8]       | WKPU[25]        | WKPU          | PF[13] | WKPU[16]     | WKPU |

| PB[9]       | WKPU[26]        | WKPU          | PG[3]  | WKPU[17]     | WKPU |

| PB[10]      | WKPU[8]         | WKPU          | PG[5]  | WKPU[18]     | WKPU |

| PC[7]       | WKPU[12]        | WKPU          | PG[7]  | WKPU[20]     | WKPU |

| PC[9]       | WKPU[13]        | WKPU          | PG[9]  | WKPU[21]     | WKPU |

| PC[11]      | WKPU[5]         | WKPU          | PI[1]  | WKPU[24]     | WKPU |

| PD[0]       | WKPU[27]        | WKPU          | PI[3]  | WKPU[23]     | WKPU |

| PD[1]       | WKPU[28]        | WKPU          | PJ[13] | WKPU[31]     | WKPU |

|             | _               |               | CC     | MPANY PUBLIC | 12   |

#### Wakeup Pin Terminations

- All wakeup pins, whether used in the application or not, must be terminated for STANDBY mode

- Terminations can be either

- -internal, configured by software

- External, with hardware

- Do not have BOTH internal and external terminations with opposite directions.

## MPC574xG Internal Pullups/Pulldowns (per MPC574xG Ref. Man. Rev6)

Has priority

#### Over WKPU Table 24-2. Pull control of wakeup pads

| Device Mode        | SIUL2_MSCRn[PUE] | SIUL2_MSCRn[PUS] | WKPU_WIPUER[IPUE<br>] | Affect on WKPU PAD |

|--------------------|------------------|------------------|-----------------------|--------------------|

| All except STANDBY | 1                | 0                | x                     | Pull down          |

| modes              | 1                | 1                | x                     | Pull up            |

|                    | 0                | x                | 0                     | Highz              |

|                    | 0                | 0                | 1                     | Pull down          |

|                    | 0                | 1                | 1                     | Pull up            |

#### **Determines STANDBY** Table 24-3. Pull control of wakeup pads pull up or down state **Device Mode** State of WKPU\_WIPER[IPUE] Affect on WKPU PAD SIUL2\_MSCRn[PUS] before entering Standby STANDBY modes/ 0 Highz х LPU\_STANDBY mode Pull down 0 Pull up

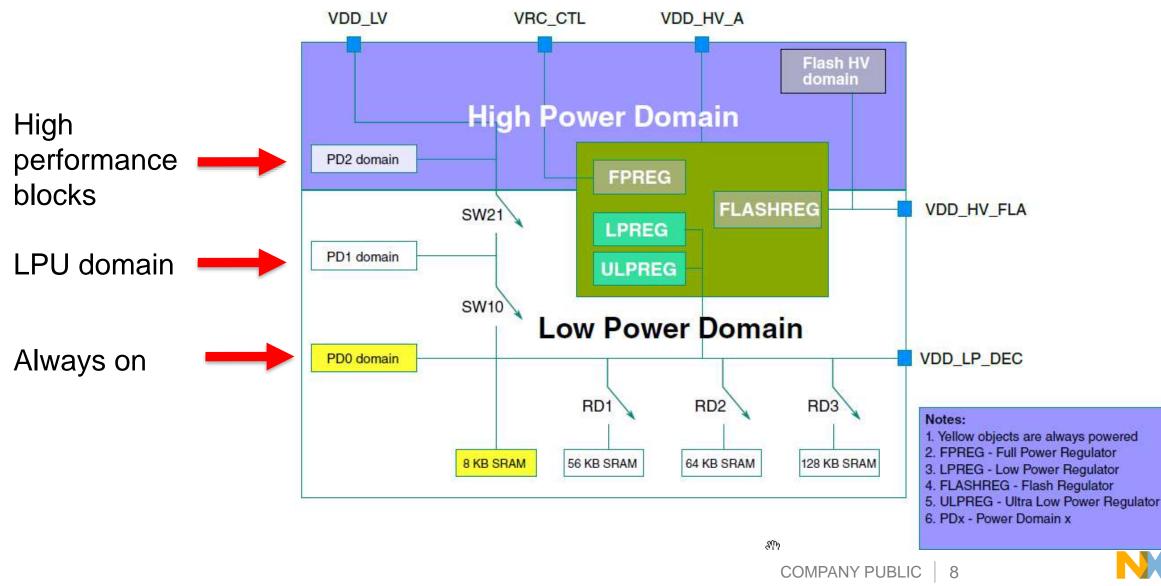

## Pad keeping feature in LPU/STANDBY mode

(Reference: MPC5748G Ref. Manual section 4.2)

- The device is capable to retain the output value of some selected pads when device is power gated i.e. in LPU or STANDBY mode.

- These pads reside in always alive power domain(PD0).

- Table 4-1 in the reference manual lists which pads support PAD Keeping feature.

- To enable this feature, set PMCDIG\_RDCR[PAD\_KEEP\_EN] to '1'.

- NOTE: Upon LPU or STANDBY mode exit, you must clear this bit or else the pads output values will be retained!

#### Debugger notes

- By default, debugger connection will break after STANDBY exit if Pad Keeper functionality is enabled in STANDBY modes. (per reference manual)

- For a debugger to maintain connection through STANDBY, PASS\_LCSTAT[CNS] must be cleared by programming the Censorship DCF client. For example, DCF record 0x000055AA, 0x001000B0

#### Interrupt / wakeup - routing (ref: MPC574xG Ref. Man. Fig. 24-2)

# MPC5748G channels 0, 1 and 2 have multiple options MPC5748G channels 0, 1 and 2

| Channel | Source                                                                         | MCAL 4.2 STOP/STANDBY Support            |

|---------|--------------------------------------------------------------------------------|------------------------------------------|

| 0       | Software Watchdog Timeout 0 (SWT_0)<br>RTC Autonomous Periodic Interrupt (API) | Y<br>Y                                   |

| 1       | RTC Real Time Counter interrupt (RTC)<br>System Timer Module 0 (STM_0)         | N (RTC not supported by GPT driver)<br>Y |

| 2       | Pad 0<br>ADC comparators 0, 1, 2 (CMP 0,1,2)                                   | Y<br>N (CMP not supported by ADC driver) |

#### MCAL Wakeup Unit Channel Selection

Channels are in the Input capture unit (Icu) module

| 셈 *Icu (Icu) 🛛             |                        |     |

|----------------------------|------------------------|-----|

| lcuWkpuChannels            |                        |     |

| Name 🗁 IcuWkpuChannels_0   |                        |     |

| Wkpu Channels              |                        |     |

| Wkpu Channel               | WKPU_CH_0              |     |

| ICU Wakeup Filter Enable 🙀 | WKPU_CH_0<br>WKPU_CH_1 | lab |

|                            | WKPU_CH_2<br>WKPU_CH_3 | E   |

|                            | WKPU_CH_4              |     |

|                            | WKPU_CH_5              |     |

|                            | WKPU_CH_6<br>WKPU_CH_7 |     |

|                            | WKPU_CH_8              |     |

|                            | WKPU_CH_9              | +   |

## Startup Code

- Determine why micro is starting:

- Reset event If a reset status flag is set (in Functional or Destructive Event Status Registers):

- Normal initializations including wakeup logic such as wakeup unit, wakeup timers like RTC.

- Normally clear all SRAM

- Clear reset flags

- Wakeup event (STANDBY mode low power exit) If a wakeup unit status flag is set (in WISR register):

- Normal initializations excluding wakeup logic such as wakeup unit, wakeup timers like RTC

- Wakeup logic's power was maintained during STANDBY

- Only clear SRAM sections not powered during STANDBY

- Clear wakeup flags

# Wakeup logic initialization

- Mode Entry module:

- Configure STANDBY mode

- Enable STANDBY mode

- Wakeup Module

- Enable desired pads for wakeup

- Configure whether pads wakeup on rising and/or falling edges

- Configure desired timers

- Configure desired ADC comparators

# **Entering STANDBY**

- Ensure there are no pending interrupts or wakeup events

- Write to Mode Control register for entering STANDBY mode

MC\_ME.MCTL.R = 0xD0005AF0; /\* Attempt STANDBY Mode (0xD) & Key \*/

MC\_ME.MCTL.R = 0xD000A50F; /\* Attempt STANDBY Mode (0xD) & Inverted Key\*/

- Wait for mode transition. (Suggest adding timeout logic) while (MC\_ME.GS.B.S\_MTRANS) {} /\* Wait for mode transition to complete \*/

# Wakeup to Flash or SRAM?

- Wakeup to flash advantages

- Less complexity

- Wakeup to SRAM advantages

- Less power

- Less time

- Wakeup address is in MC\_ME\_CADDR1[ADDR]

- To wakeup to SRAM, program desired SRAM start address into MC\_ME\_CADDR1

- To wakeup to flash, leave original flash start address in register that was loaded at power on reset by BAF.

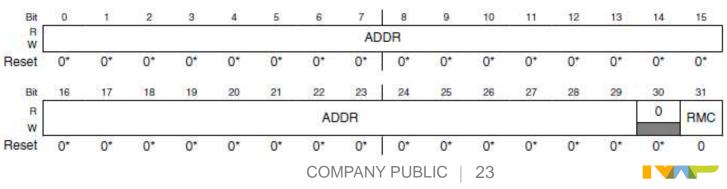

#### 38.3.93 CORE1 Address Register (MC\_ME\_CADDR1)

This register contain the boot address of each Z4A and a bit for controlling whether the Z4A core is to be reset on the next mode change that has the core configured to be running in the target mode.

This register can be written only as words and cannot be written after a mode change request has been made until the mode transition has completed (i.e., while the S\_MTRANS bit of the ME\_GS register = '1'). A write access to any of this register during this time will result in the ICONF\_CC flag in the ME\_IS register being asserted.

ME\_CADDR1 is pre-loaded with the value provided by the device configuration just before reset exit in order to ensure that Z4A boots from the correct address after any chip reset if the DRUN bit in the ME\_CCTL1 register has a default value of '1'.

The value of the ADDR field just before entering STANDBY0 mode is the value of the ADDR field on STANDBY0 exit.

#### Address: FFFB\_8000h base + 1E4h offset = FFFB\_81E4h

#### Low Power Wake up with Multicore Guidelines

- Before entering STANDBY mode, <u>make sure the other cores will not</u> <u>automatically start on STANDBY exit</u>.

- Reason: software on other cores may depend on startup code completing by main core on STANDBY exit

- Prevent other cores automatically starting on exit by disbling DRUN in ME\_CCTL2, ME\_CCTL3.

- After STANDBY wakeup <u>make sure the prior wakeup to DRUN</u> <u>completed</u>

- -Wait for ME\_GS[S\_MTRANS]

- Reason: if you exit STANDBY to, for example, turn on the external oscillator and use it to start the PLL, then the clocks may not be stable for code that needs them.

# Debugging and when things go wrong

6

## DCF Record Required for MPC574xG Low Power Debug

- PASS\_LCSTAT [CNS] must be cleared for low power debug mode to work across low power mode STANDBY transitions.

- -Only a DCF record in UTEST can clear CNS.

- If CNS =1 (default per factory shipped) then no DCF record has been written to affect its value.

| Table 23-1. | INTC | Vector | Table | (continued) |

|-------------|------|--------|-------|-------------|

|-------------|------|--------|-------|-------------|

#### Mode Interrupts

- Mode transition issues can be enabled to generate an interrupt.

- Example: MPC5748G Ref Manual v6, Mode Entry's Interrupt Status Register:

| Vector number | Vector offset | Source module | Source description                              |

|---------------|---------------|---------------|-------------------------------------------------|

| 244           | 13D0          | SIUL          | EIRQ [8-15] - SIUL Combined External Interrupt  |

| 245           | 13D4          | SIUL          | EIRQ [16-23] - SIUL Combined External Interrupt |

| 246           | 13D8          | SIUL          | EIRQ [24-31] - SIUL Combined External Interrupt |

| 250           | 13E8          | LPU_CTL       | LPU_ICR[NEM]   LPU_ICR[MRIG]                    |

| 251           | 13EC          | MC_ME         | ME_IS[I_SAFE]                                   |

| 252           | 13F0          | MC_ME         | ME_IS <mark>[I_MTC</mark> ]                     |

| 253           | 13F4          | MC_ME         | ME_IS[I_IMODE]                                  |

| 254           | 13F8          | MC_ME         | ME_IS[I_ICONF]                                  |

| 255           | 13EC          | MC BGM        | MC_BGM Functional and destructive reset         |

| 26<br>I_ICONF_CC | Invalid mode configuration interrupt (core configuration) — This bit is set if a write access to one of the ME_CADDRn registers is attempted while a mode transition is in progress.                                                                                                   |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | 0 No write to an ME_CADDRn register was attempted during an ongoing mode transition                                                                                                                                                                                                    |

|                  | 1 A write to an ME_CADDRn register was attempted during an ongoing mode transition                                                                                                                                                                                                     |

| 29<br>I_IMODE    | Invalid mode interrupt — This bit is set whenever an invalid mode transition is requested. It is cleared by writing a '1' to this bit.                                                                                                                                                 |

|                  | 0 No invalid mode interrupt occurred                                                                                                                                                                                                                                                   |

|                  | 1 Invalid mode interrupt is pending                                                                                                                                                                                                                                                    |

| 30<br>I_SAFE     | SAFE mode interrupt — This bit is set whenever the chip enters SAFE mode on hardware requests generated in the system. It is cleared by writing a '1' to this bit.                                                                                                                     |

|                  | 0 No SAFE mode interrupt occurred                                                                                                                                                                                                                                                      |

|                  | 1 SAFE mode interrupt is pending                                                                                                                                                                                                                                                       |

| 31<br>I_MTC      | Mode transition complete interrupt — This bit is set whenever the mode transition process completes (S_MTRANS transits from 1 to 0). It is cleared by writing a '1' to this bit. This mode transition interrupt bit will not be set while entering low-power modes STOP0, or STANDBY0. |

|                  | 0 No mode transition complete interrupt occurred                                                                                                                                                                                                                                       |

|                  | 1 Mode transition complete interrupt is pending                                                                                                                                                                                                                                        |

|                  |                                                                                                                                                                                                                                                                                        |

#### MC\_ME\_IMTS field descriptions

#### Invalid Mode Possible Causes

- Mode transitions are aborted when they are invalid.

- Example: Attempt to enter STANDBY mode but a wakeup event exists.

IMTS[S\_MRIG] is set

| Field            | Description                                                                                                                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0–25<br>Reserved | This field is reserved.<br>This read-only field is reserved and always has the value 0.                                                                                                                                                                                                             |

| 26<br>S_MRIG     | Mode Request Ignored status — This bit is set whenever a new mode is requested while a transition to the SAFE mode is in progress. It is cleared by writing a '1' to this bit.                                                                                                                      |

|                  | This bit is also set when a transition to STANDBY0/STOP0 mode is requested while a wakeup event is active.                                                                                                                                                                                          |

|                  | <ul> <li>Mode transition requested is not illegal</li> <li>Mode transition requested is illegal</li> </ul>                                                                                                                                                                                          |

| 27<br>S_MTI      | Mode Transition Illegal status — This bit is set whenever a new mode is requested while some other non-<br>SAFE mode transition process is active (S_MTRANS is '1'). Please refer to Mode Transition Interrupts for<br>the exceptions to this behavior. It is cleared by writing a '1' to this bit. |

|                  | <ul> <li>Mode transition requested is not illegal</li> <li>Mode transition requested is illegal</li> </ul>                                                                                                                                                                                          |

| 28<br>S_MRI      | Mode Request Illegal status — This bit is set whenever the target mode requested is not a valid mode with respect to current mode. It is cleared by writing a '1' to this bit.                                                                                                                      |

|                  | <ul> <li>Target mode requested is not illegal with respect to current mode</li> <li>Target mode requested is illegal with respect to current mode</li> </ul>                                                                                                                                        |

| 29<br>S_DMA      | Disabled Mode Access status — This bit is set whenever the target mode requested is one of those disabled modes determined by ME_ME register. It is cleared by writing a '1' to this bit.<br>0 Target mode requested is not a disabled mode                                                         |

|                  | 1 Target mode requested is a disabled mode                                                                                                                                                                                                                                                          |

| 30 ੴ<br>S_NMA    | Non-existing Mode Access status — This bit is set whenever the target mode requested is one of those non existing modes determined by ME_ME register. It is cleared by writing a '1' to this bit.                                                                                                   |

|                  | 0 Target mode requested is an existing mode<br>1 Target mode requested is a non-existing mode                                                                                                                                                                                                       |

| 31<br>S_SEA      | SAFE Event Active status — This bit is set whenever the chip is in SAFE mode, SAFE event bit is pending<br>and a new mode requested other than RESET/SAFE modes. It is cleared by writing a '1' to this bit.                                                                                        |

|                  | <ul> <li>No new mode requested other than RESET/SAFE while SAFE event is pending</li> <li>New mode requested other than RESET/SAFE while SAFE event is pending</li> </ul>                                                                                                                           |

|                  |                                                                                                                                                                                                                                                                                                     |

#### Bare code debugging for incomplete mode transitions

- Incorporate a timer for mode transitions.

- Timer expiration can be used to call error recovery function or simply trap for debug

- Examine Mode Entry status registers:

- ME\_GS

- $-ME_{IS}$

- ME\_IMTS

- ME\_DMTS

#### MCAL debugging for incomplete mode transitions

C:\NXP\AUTOSAR\MPC574XG\_MCAL4\_2\_RTM\_1\_0\_0\eclipse\plugins\Mcu\_TS\_T2D3 5M10I0R0\src\Mcu\_MC\_ME.c file has the function Mcu\_MC\_ME\_ApplyMode:

FUNC( void, MCU\_CODE) Mcu\_MC\_ME\_ApplyMode( VAR( Mcu\_PowerModeType, AUTOMATIC) ePowerMode )

• In this function there is a timeout to wait for the mode transition to complete.

```

while (((uint32)MC_ME_GS_S_MTRANS_MASK32 == (REG_READ32(MC_ME_GS_ADDR32) &

(uint32)MC_ME_GS_S_MTRANS_MASK32)) && (u32Timeout > (uint32)0x0U))

{

/* (ME_GS[S_MTRANS]=1) <=> (Transition ongoing). */

u32Timeout--;

}

```

Modify code so before timeout expires you branch somewhere and have a breakpoint there.

#### MCAL behavior on standby entry failure

- MCAL McuSetMode function implements a timeout on attempting mode entry

- If a timeout occurs, a diagnostic error is reported to the diagnostic manager with dem\_seteventstatus function.

- When dem\_eventstatus function is called, the first parameter is "timeout from Mcu driver".

- After that, the McuSetMode function returns and execution continues.

- Customers must implement handling this error with their own code.

## MCAL LPU support

- NXP MCAL

- Supports transition to LPU\_RUN mode

- User must write LPU application code and place in RAM

- MCAL will not run in LPU\_RUN mode. (e200z4 cores do not have power in LPU\_RUN.)

- Does not support LPU\_STOP, LPU\_SLEEP, LPU\_STANDBY

- Rational: LPU\_RUN mode is intended for small tasks to be performed while executing from RAM (when the AUTOSAR stack is not needed).

- So the LPU\_STOP, LPU\_SLEEP and LPU-STANDBY are intentionally not supported.

#### SECURE CONNECTIONS FOR A SMARTER WORLD

www.nxp.com

NXP, the NXP logo, and NXP secure connections for a smarter world are trademarks of NXP B.V. All other product or service names are the property of their respective owners. © 2018 NXP B.V.