QorlQ T1040 and T2081 Communication Processors Compatible Design Guidelines APF-NET-T0457

Chun Chang | Application Engineer

A P R . 2 0 1 4

External Use

Presscala, the Presscale Jogo, AMVer, C.-6, Code/TERT, Code/Wantor, ColeFine, ColleFine, C.Ware, the Energy Efficient Solutions logo, Kinetis, mobileGT, PEG, Posee/QUICC, Processor Expert, QorXD, Ocrive, Taskaaune, the BaleAssare logo, StarCore, Symptony and VortiGa are trademarks of Presscale Semiconductor, Inc., Reg. U.S. Pat, & Trix, Ott, Arthes, BaeXD, See/Stack, ConNex, Fasis, Layerscape, MagNV, MRC, Reatorn in a Package, QorXD Converge, QUICC Engine, Ready Play, SMARTMOS, Tower, TuroLink, UMENE, World and Xinnets are trademarks of Presscale Semiconductor, Inc. At other product or semicine areas are the property of their trademarks of 2014 Presscale Semiconductor, Inc.

# Agenda

- Hardware Compatibility

- Software Compatibility

- Pinout comparision

- Session Review and Wrap-Up

### Use a common board

With the introduction of the T1040 and T2081, customers can now create common boards for both devices.

- T1040 and T2081 are pin compatible

- One common board design would reduce design time and save cost

- Make migration much faster and easier

# Hardware Compatibility

- Hardware Compatibility

- Commonality and difference

- Overcome the difference

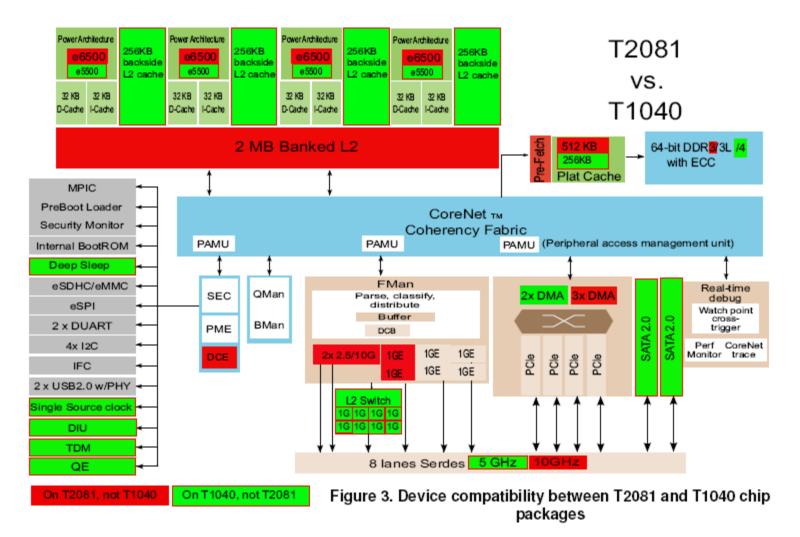

### **Device Comparison – T1040 and T2081**

### **Commonality and Difference**

| Features                                        | T2081                                         | T1040                        | T1042                        |  |  |  |  |

|-------------------------------------------------|-----------------------------------------------|------------------------------|------------------------------|--|--|--|--|

|                                                 | Cores                                         |                              |                              |  |  |  |  |

| Number of cores                                 | 4 × e6500 dual threaded Power<br>Architecture | 4 × e5500 Power Architecture | 4 x e5500 Power Architecture |  |  |  |  |

| Architecture width                              | 64-bit                                        | 64-bit                       | 64-bit                       |  |  |  |  |

| Max frequency (MHz)                             | 1800                                          | 1400                         | 1400                         |  |  |  |  |

| DMIPS/MHz                                       | 6                                             | 3                            | 3                            |  |  |  |  |

|                                                 | Memory                                        | / Size                       |                              |  |  |  |  |

| L1 cache                                        | 32 KB I/D                                     | 32 KB I/D                    | 32 KB I/D                    |  |  |  |  |

| L2 cache                                        | Shared 2MB                                    | 256KB per core backside      | 256KB per core backside      |  |  |  |  |

| CoreNet platform cache<br>(CPC) 512KB frontside |                                               | 256KB frontside              | 256KB frontside              |  |  |  |  |

| Cache-line size                                 | 64 bytes                                      | 64 bytes                     | 64 bytes                     |  |  |  |  |

| Main memory type                                | 1 × DDR3/3L 2133 MT/s                         | 1 × DDR3L/4 1600 MT/s        | 1 DDR3L/4 1600 MT/s          |  |  |  |  |

| Maximum size of main<br>memory                  | 32 GB (1Gbit x8 device)                       | 32 GB (1Gbit x8 device)      | 32 GB (1Gbit x8 device)      |  |  |  |  |

### **Commonality and Difference (continue)**

| Ι/O                                  |                                                                          |                                                      |                                                       |  |  |  |

|--------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------|--|--|--|

| Ethernet controllers                 | 2× 10Gbps XFI; 6x 1Gbps<br>SGMII; 2x 2.5Gbps SGMII; 2x<br>RGMII          | 2× 5Gbps QSGMII; 6x 1Gbps<br>SGMII; 2x RGMII; 1x MII | 5x 1Gbps SGMII; 2x 2.5Gbps<br>SGMII; 2x RGMII; 1x MII |  |  |  |

| SerDes lanes                         | 8 lanes at up to 10 GHz                                                  | 8 lanes at up to 5 GHz                               | 8 lanes at up to 5 GHz                                |  |  |  |

| PCI Express controllers              | 3 × Gen 2.0 controllers; 5 Gbps<br>and<br>1× Gen 3.0 controllers; 8 Gbps | 4 × Gen 2.0 controllers;<br>5 Gbps                   | 4 × Gen 2.0 controllers;<br>5 Gbps                    |  |  |  |

| SATA                                 | None                                                                     | 2 x SATA controllers upto<br>3.0Gbps operation       | 2 x SATA controllers upto<br>3.0Gbps operation        |  |  |  |

| TDM                                  | None                                                                     | Full duplex serial port                              | Full duplex serial port                               |  |  |  |

| Display Interface Unit               | None                                                                     | 12 bit dual data rate                                | 12 bit dual data rate                                 |  |  |  |

| CoreNet                              | 700 MHz at 256 bits                                                      | 600 MHz at 128 bits                                  | 600 MHz at 128 bits                                   |  |  |  |

| L2 switch                            | None                                                                     | 8 Port                                               | None                                                  |  |  |  |

| QE                                   | None                                                                     | HDLC, Transparent UART,<br>TDM/SI                    | HDLC, Transparent UART,<br>TDM/SI                     |  |  |  |

| Integrated Flash Controller<br>(IFC) | 8-/16-bit data width, 32-bit<br>address width                            | 8-/16-bit data width, 32-bit<br>address width        | 8-/16-bit data width, 32-bit<br>address width         |  |  |  |

# Hardware Compatibility

- Identical Interfaces

- DDR Controller

- eSDHC Controller

- TEST\_SEL Pin

- Sense Pin

- Power Sequencing

- Power Supply

- Sysclk

External Use 7

### **Identical interfaces**

The following interfaces are identical between the T2081 and T1040:

- Integrated Flash Controller (IFC)

- Enhanced SPI controller (eSPI)

- DUART controller

- USB controller

### **DDR Controller**

The T2081 supports DDR3/3L DDR controller, T1040 supports DDR3L/4 DDR controller. As DDR3L is common to both T2081 and T1040, it should be used for common board design.

|       | MDIC[0]    | MDIC[1]    |

|-------|------------|------------|

| T1040 | 162 ohm 1% | 162 ohm 1% |

| T2081 | 187 ohm 1% | 187 ohm 1% |

#### Table 4. DDR calibration resistor values

External Use 9

### **eSDC** Controller

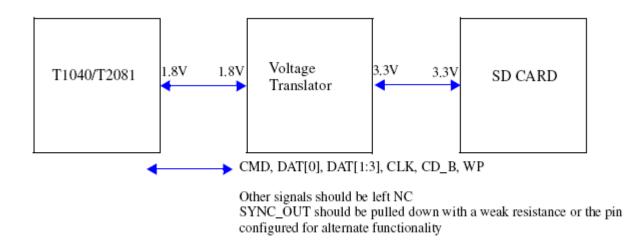

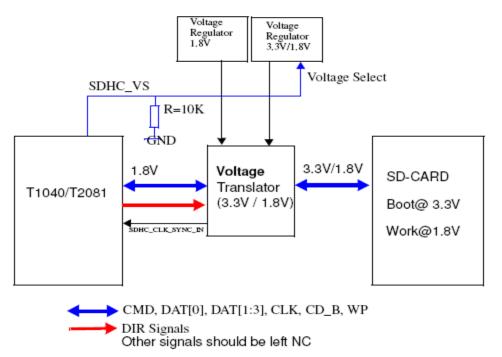

### 3.3 eSDHC controller recommendations

Both T2081 and T1040 support SD 3.0 specification introducing higher capacity upto 2 TB and frequency up to 208 MHz.

In order to support these modes, dynamic switching of I/O voltage from 3.3 V to 1.8 V is required. This dynamic switching is not supported on T2081 and board level shifters are required for common board design.

Figures below shows the SD card connections for T2081 compatibility for different modes.

Figure 4. SD card connections for T2081 compatability (DS and HS modes)

# **SD Card Connection example**

#### Figure 5. SD card connections for T2081 compatability (SDR 12, 25, 50, 104 and DDR50 modes)

#### NOTE

#### In Figure 5,

- SYNC\_OUT should be pulled-down with a weak resistor or the pin should be configured for alternate functionality

- SYNC\_IN connection is needed in DDR50 mode only

- · In SDR50, DDR50 modes, all the input signals are sampled with respect to SYNC\_IN

- · Resistor R is only needed when RCW loading is required to be done from SD card

# **TEST\_SEL\_B** pin

### 3.11 TEST\_SEL\_B requirements

External Use | 12

When migrating between the T1020 and T1040, the connection of TEST\_SEL\_B needs to be considered. This table lists the different TEST\_SEL\_B connection requirements for each chip.

| Device       | TEST_SEL_B pin requirement |

|--------------|----------------------------|

| T1040, T1042 | Pull to O1V <sub>DD</sub>  |

| T1020, T1022 | Pull to GND                |

| T2081        | Pull to OV <sub>DD</sub>   |

Table 13. TEST\_SEL\_B pin connection requirements

### **Sense Pins**

### 3.9.4 SENSE Pins requirements

If sense pins are to be used for the regulators,  $SENSEV_{DD}$  should be used.  $SENSEV_{DDC}$  can be left floating.

| Ball | T2081    | T1040                |

|------|----------|----------------------|

| G19  | SENSEVDD | SENSEV <sub>DD</sub> |

| AB9  | RSVD28   | SENSEVDDC            |

#### Table 12. Regulator sense-pin source

### **Power Sequencing**

### 3.10 Power Sequencing requirements

T1040 requires its power rails to rampup in a specific sequence, whereas T2081 has no such requirement. Common board should follow T1040 hardware specification for the Power sequencing requirements.

### **Power Supply for Core**

### 3.9.1 Core Power island requirements

External Use | 15

T1040 has  $V_{DD}$  and  $V_{DDC}$  power domains for Core and platform supply whereas there is only  $V_{DD}$  power domain for core and platform supply in T2081. For a common board design, it is recommended to use a single rail for  $V_{DD}$  and  $V_{DDC}$  in T1040.

| T2081                                     | T1040                                                        | Recommnedation                                                                   |

|-------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------|

| V <sub>DD</sub> ,<br>USB_SV <sub>DD</sub> | V <sub>DD</sub> , V <sub>DDC</sub> ,<br>USB_SV <sub>DD</sub> | V <sub>DD</sub> and V <sub>DDC</sub><br>should be connected<br>to a common rail. |

| Table | 10. | VDD | configuration |

|-------|-----|-----|---------------|

|-------|-----|-----|---------------|

### **Power Supply for I/O**

### 3.9.3 I/O Power island requirements

External Use | 16

The table below summarizes the Power island requirements for T2081 and T1040 and provides recommendations for common board design.

| Supply           | T2081 | T1040 | Recommendation for a<br>common board design | Interface wise recommendation                                                                                                                                                                                                         | Interfaces          |

|------------------|-------|-------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| $O1V_{DD}$       | -     | 1.8V  | Use Single regulator for OV <sub>DD</sub>   | eSDHC interface of T2081 is on                                                                                                                                                                                                        | Common: MPIC, GPIO, |

| OV <sub>DD</sub> | 1.8V  | 1.8V  | and O1V <sub>DD</sub> on T1040 at 1.8V      | $OV_{DD}$ supply while IO power<br>supply of eSDHC in T1040 is fed<br>by $EV_{DD}$ . If eSDHC is used, $EV_{DD}$<br>and $OV_{DD}$ should be connected to<br>1.8V. On board level shifters are<br>required to support SD 3.0<br>modes. | RTC and power       |

#### Table 11. I/O Power island configuration

### I/O Power Supply (continue)

| Supply            | T2081         | T1040                | Recommendation for a<br>common board design                                                                | Interface wise recommendation                                                                                                                                                                                 | Interfaces                                                      |

|-------------------|---------------|----------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| DV <sub>DD</sub>  | 2.5V<br>1.8V  | 3.3V<br>2.5V<br>1.8V | Use 2.5V or 1.8V only for DV <sub>DD</sub> supply                                                          | DIU and TDM are supported at<br>3.3V so voltage translators may<br>be required on a common board.<br>QE interface is supported at 2.5V<br>and 3.3V, restricting DV <sub>DD</sub> to 2.5V<br>for common board. | Common: DUART, I2C,<br>DMA, MPIC<br>T1040 only: QE, TDM,<br>DIU |

| CV <sub>DD</sub>  | 2.5V<br>1.8V  | 3.3V<br>1.8V         | Use 1.8V for CV <sub>DD</sub> supply                                                                       | —                                                                                                                                                                                                             | Common: eSPI,<br>SDHC_DAT[4:7]                                  |

| EV <sub>DD</sub>  | _             | 3.3V<br>1.8V         | Use OV <sub>DD</sub> supply for EV <sub>DD</sub>                                                           | SDHC_DAT[0:3], SDHC_CMD<br>and SDHC_CLK are the signals<br>on EV <sub>DD</sub> supply in T1040. These<br>signals are on OV <sub>DD</sub> supply in<br>T2081. See OV <sub>DD</sub> supply for<br>details.      | Common: eSDHC<br>See Note                                       |

| G1V <sub>DD</sub> | 1.5V<br>1.35V | 1.35V<br>1.2V        | Use G1V <sub>DD</sub> at 1.35V                                                                             | Use DDR3L only                                                                                                                                                                                                | Common:DDR3L<br>T1040: DDR4<br>T2081: DDR3                      |

| L1V <sub>DD</sub> | _             | 3.3V<br>2.5V<br>1.8V | Use Single regulator for LV <sub>DD</sub><br>and L1V <sub>DD</sub> on T1040<br>It can support 2.5V or 1.8V | Use RGMII interface at 2.5V only.                                                                                                                                                                             | Common:GPIO,<br>RGMII@2.5V<br>T1040: MII, RGMII@1.8V            |

| LV <sub>DD</sub>  | 2.5V<br>1.8V  | 3.3V<br>2.5V<br>1.8V |                                                                                                            |                                                                                                                                                                                                               |                                                                 |

### Sysclk

### 4 Internal clocking differences

T1040 supports additional clocking schemes and differences are summarised in the table below.

| Clocking scheme                                                                                | T2081 | T1040                                                                  | Recommendation                                                                                                              |

|------------------------------------------------------------------------------------------------|-------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Single Reference clock mode No Yes T1040: Supported through DIFF_SYSCLK/Di<br>clock input pair |       | T1040: Supported through DIFF_SYSCLK/DIFF_SYSCLK_B<br>clock input pair |                                                                                                                             |

| Multiple reference clock mode                                                                  | Yes   | Yes                                                                    | Through separate oscillators for SYSCLK, DDRCLK,<br>USBCLK, SDREF_CLKn inputs. Recommended mode for<br>common board design. |

#### Table 14. T2081/T1040 clocking comparison

### NOTE

For a common board design, use SYSCLK as the system clock input and leave the differential pair as floating or connect through 10K resistor to GND

### **Exceptions**

### 2.2 Pin-compatibility considerations

Exceptions and recommendations in regards to pin compatibility between the T2081 and T1040 processor family are as follows:

- T1040 supports MII interfaces on EC1 which is not supported by T2081. Only RGMII interfaces should be used for EC1 and EC2.

- T2081 supports XFI interface, while T1040 does not.

- T1040 supports an 8 port L2 switch, while T2081 does not.

- T1040 supports up to two QSGMII interfaces, while T2081 does not.

- T1040 has four PCI Express controllers supporting PCI Express 2.0 protocol while the T2081 has three PCI express controllers supporting PCI Express 2.0 protocol and one PCI Express controllers supporting PCI Express 3.0 protocol at 8 Gbps.

- T1040 supports two SATA 2.0 interfaces, while T2081 does not.

- T1040 supports TDM or HDLC over uQE interface. uQE is not supported on T2081.

- T1040 supports 12 bit DIU interface, while T2081 does not.

- T1040 supports Deep sleep, a low power state, this state is not supported by T2081.

- TEST\_SEL pin connection requirements vary per device family derivative; see Section 3.11, "TEST\_SEL\_B requirements."

# **Software Compatibility**

- e6500 and e5500mc

- RGMII

- Serdes configurations

- RCW

# e6500 and e500mc Compatibility

- User code runs equally well on e6500 or e500mc

- Interrupts per thread

- Soft reset per thread (hard reset per core only)

- Debug state per thread

- Changes are hidden by OS

- L2 initialization uses a different register

External Use

- Cache locking controlled differently

- P4080 SDK, emulated for e6500, didn't require changes.

- Additional enablement for new features not present on e500mc:

64b, drowsy power manager, Altivec.

### e500mc/e6500 Caching Structure Differences

|    | e500mc                  | e6500                    | Implication                                                                    |

|----|-------------------------|--------------------------|--------------------------------------------------------------------------------|

| L1 | 32kB. Can lock per core | 32kB. Can lock per core. | e6500 doesn't lock per thread.                                                 |

| L2 | 128kB per core          | 2MB shared               | There will be a somewhat different latency profile, overall improved for e6500 |

| L3 | 512MB for SC4080        | 512kB                    |                                                                                |

- Cache changes are transparent to user application.

- L1 locking is less granular in e6500.

### RGMII

### 3.8 Ethernet MACs options

While the two RGMII interfaces are pin compatible, the configurations for RGMII mode are different between the T2081 and T1040 devices. This table lists the RGMII configuration options and the assigned FMan/MACx on both T2081 and T1040.

| Configuration   | RGMII assignment |                           |                     |  |

|-----------------|------------------|---------------------------|---------------------|--|

| Configuration   | T2081            | T1040                     |                     |  |

| RCW[EC1] = 0b00 | FMan MAC3        | FMan MAC4 MAC2_GMII_SEL = |                     |  |

|                 |                  | FMan MAC2                 | MAC2_GMII_SEL = 0b1 |  |

| RCW[EC2] = 0b00 | FMan MAC4        | FMan MAC5                 | —                   |  |

| RCW[EC2] = 0b01 | FMan MAC10       | _                         |                     |  |

| Table 8. Configuration | for RGMII mode |

|------------------------|----------------|

|------------------------|----------------|

Additionally T1040 also supports MII interface on EC1 Interface. When using MII interface,  $L1V_{DD}$  and  $LV_{DD}$  are restricted to 3.3V and RGMII cannot be supported on EC1 or EC2.

### **Serdes configurations**

| T1040<br>SRDS_PRCTL_S1                 | A               | в               | с                | D                 | E                                         | F               | G                                         | н                      | T2081<br>SRDS_PRTCL_S1         |  |

|----------------------------------------|-----------------|-----------------|------------------|-------------------|-------------------------------------------|-----------------|-------------------------------------------|------------------------|--------------------------------|--|

| 0x00<br>(2 RGMII; FMAN<br>MAC4 & MAC5) | PEX1<br>(5/2/5) |                 |                  | PEX2<br>(5/2.5)   |                                           |                 | 0xAA<br>(2 RGMII; FMAN<br>MAC3 & MAC4/10) |                        |                                |  |

| MAC4 & MAC5)                           | PEX3<br>(5/2.5) |                 |                  | PEX4<br>(8/5/2.5) |                                           |                 |                                           |                        |                                |  |

| 0x40<br>(2 RGMII; FMAN                 |                 | EX1<br>2.5)     | sg.m1<br>(1.25)  | sg.m2<br>(1.25)   | PEX2<br>(5/2.5)                           |                 |                                           | 0xBC<br>(2 RGMII; FMAN |                                |  |

| MAC4 & MAC5)                           |                 | EX3<br>2.5)     | SG1<br>(1.25)    | SG2<br>(1.25)     | PEX4<br>(8/5/2.5)                         |                 | MAC3 & MAC4/10)                           |                        |                                |  |

| 0xA5<br>(0 RGMII)                      | PEX1<br>(5/2.5) | sg.m3<br>(1.25) | sg.m1<br>(3.125) | sg.m2<br>(3.125)  | PEX2 sg.m4 sg.m5<br>(5/2.5) (1.25) (1.25) |                 | 0xC8                                      |                        |                                |  |

|                                        | PEX3<br>(5/2.5) | SG10<br>(1.25)  | SG1<br>(3.125)   | SG2<br>(3.125)    | PEX4<br>(5/2.5)                           |                 | SG5<br>1.25)                              | SG6<br>(1.25)          | (2 RGMII; FMAN<br>MAC3 & MAC4) |  |

| 0xAA<br>(0 RGMII)                      | PEX1<br>(5/2.5) | sg.m3<br>(1.25) | sg.m1<br>(3.125) | sg.m2<br>(3.125)  | PEX2<br>(5/2.5)                           | PEX3<br>(5/2.5) | sg.m4<br>(1.25)                           | sg.m5<br>(1.25)        | 0xFA<br>(2 RGMII; FMAN         |  |

|                                        | PEX3<br>(5/2.5) | SG10<br>(1.25)  | SG1<br>(3.125)   | SG2<br>(3.125)    | PEX4<br>(5/2.5)                           | PEX1<br>(5/2.5) | SG5<br>(1.25)                             | SG6<br>(1.25)          | MAC3 & MAC4)                   |  |

| 0x85<br>(0 RGMII)                      | PEX1<br>(5/2.5) | sg.m3<br>(1.25) | sg.m1<br>(1.25)  | sg.m2<br>(1.25)   |                                           | X2<br>2.5)      | sg.m4<br>(1.25)                           | sg.m5<br>(1.25)        | 0xD6<br>(2 RGMII; FMAN         |  |

|                                        | PEX3<br>(5/2.5) | SG10<br>(1.25)  | SG1<br>(1.25)    | SG2<br>(1.25)     |                                           | X4<br>/2.5)     | SG5<br>(1.25)                             | SG6<br>(1.25)          | MAC3 & MAC4)                   |  |

# **Reset Configuration Word**

RCW are mostly compatible, detail listed in T1040 and T2080 reference manual.

#### Table 10. Reset Configuration Word Comparison (continued)

| RCW Bit(s) | P4 Function | P5 Function | Notes                                                                                            |  |  |

|------------|-------------|-------------|--------------------------------------------------------------------------------------------------|--|--|

| 8–9        | MEM_P       | LL_CFG      | —                                                                                                |  |  |

| 10–14      | MEM_P       | LL_RAT      | Cutoff frequencies for the P4 and P5 differ.<br>19:1 async mode setting is available for P5.     |  |  |

| 15–63      | Reserved    |             |                                                                                                  |  |  |

| 64–65      | CC1_PL      | L_CFG       | 0b01 is not a valid setting for P5                                                               |  |  |

| 66–70      | CC1_PI      | LL_RAT      | Synchronous mode ratios are available for<br>P5. 17:1 async mode setting is available for<br>P5. |  |  |

| 71         |             | Reserved    |                                                                                                  |  |  |

| 72–73      | CC2_PL      | L_CFG       | 0b01 is not a valid setting for P5                                                               |  |  |

| 74–78      | CC2_PI      | LL_RAT      | Synchronous mode ratios are available for<br>P5. 17:1 async mode setting is available for<br>P5. |  |  |

# **Pinout Comparison**

| Pin                                                                       | T2081     | T1040         | Compatible connection                                                                                                                                   |  |  |  |

|---------------------------------------------------------------------------|-----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Ethernet MI 2 pins                                                        |           |               |                                                                                                                                                         |  |  |  |

| L6                                                                        | EMI2_MDC  | RSVD10        | All the Ethernet PHY's to be used with                                                                                                                  |  |  |  |

| M6                                                                        | EMI2_MDIO | RSVD11        | T1040 should be managed through the EMI1 interface.                                                                                                     |  |  |  |

| Ethernet Cont. 1 pins                                                     |           |               |                                                                                                                                                         |  |  |  |

| AC4                                                                       | RSVD34    | EC1_TX_ER     | EC1 Interface on T1040 also supports<br>MII interface (see Section 3.8,<br>"Ethernet MACs options")This output<br>pin can be left floating if not used. |  |  |  |

| AC2                                                                       | RSVD33    | EC1_RX_ER     | Tie low through a 2-10 kohm resistor if                                                                                                                 |  |  |  |

| AC1                                                                       | RSVD32    | EC1_COL       | not used.                                                                                                                                               |  |  |  |

| Differential SYSCLK pins (see Section 4, "Internal clocking differences") |           |               |                                                                                                                                                         |  |  |  |

| G14                                                                       | RSVD07    | DIFF_SYSCLK   | Differential SYSCLK input is available                                                                                                                  |  |  |  |

| F14                                                                       | RSVD05    | DIFF_SYSCLK_B | only in T1040. These can be left floating<br>or connected to GND if unused.                                                                             |  |  |  |

| · · ·                                                                     |           |               |                                                                                                                                                         |  |  |  |

### Software Development Kit (need to update)

- The Software Development Kit (SDK) 1.5 was released for T1040 and T2080 on Feb. 14, 2014. The components (described in more detail in the SDK product brief for the P4080) are:

- T2080 rev. 1 silicon + QDS

- Bare-metal support

- U-boot debug

- Register details

- Linux Kernel and Application Debug

External Use 27

### **CodeWarrior**

- CodeWarrior for Power Architecture v10.3.3 Service pack 2 product with T1040 and T2080 support are available along with first silicon. It features the next generation of CodeWarrior tools based on the Eclipse framework:

- T2080 rev. 1 silicon + QDS

- Bare-metal support

- U-boot debug

- Register details

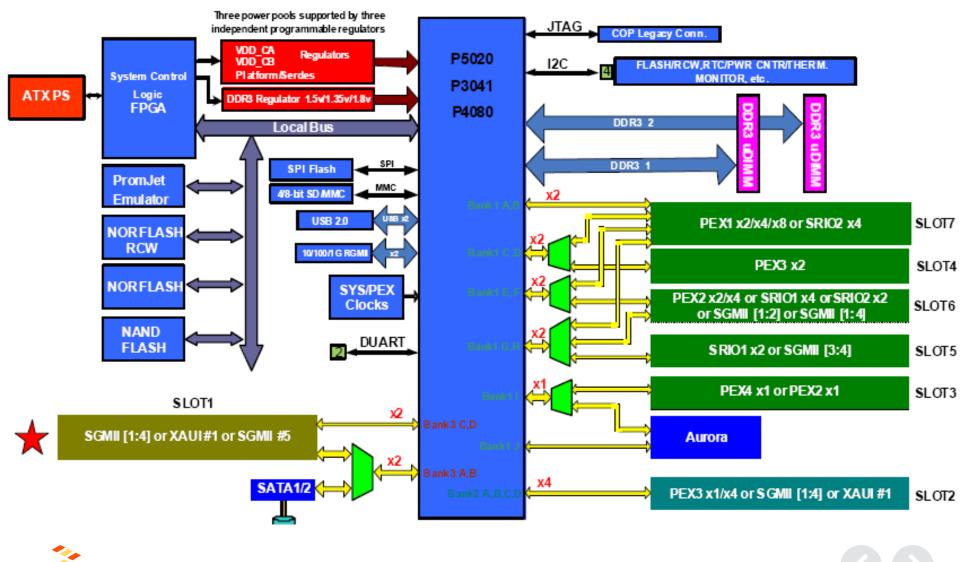

### T1040/T2081 Development System (need to update with T1040 RDB picture)

# T1040 Development System Block Diagram (need to update with T1040 RDB)

30

### **Reference Documentation**

- T1040 Hardware Specification and Reference Manual

- T2081 Hardware Specification and Reference Manual

- Application note (AN4733) T1040 to T2081 Migration Guide

- T1040/T2081 Design Checklist

- T1040 RDB User Manual

- T1040 RDB Schematic

# **Session Closing**

- By now, you should be able to:

- Use Freescale's design collateral to aid your own T1040 and T2081 designs

- Understand the commonality and difference between these devices

- Understand the unique challenges facing P4, P5 and P3 common design and the solutions to overcome them

www.Freescale.com

© 2014 Freescale Semiconductor, Inc. | External Use