#### **TUTORIAL: S32DS ISP VISUAL GRAPH TOOL**

S32 DESIGN STUDIO 3.1 or higher with S32V2xx development package and Vision extension package for S32V2xx

NP

EXTERNAL USE

Interactive

**Tutorial?**

Welcome to S32 Design Studio for Vision, Version 2.0

GETTING STARTED DOCUMENTATION VIDEO SUPPORT

#### QUICK LINKS

Getting Started 83

-S32DS--VISION-NEW Application Project NEW Library Project NEW Project from Examp

-S32DS--VGT-NEW APEX2 Program Project NEW APEX2 Kernel Project NEW APEX2 Graph Project NEW ISP Data Flow Project

-S32DS- -DDR-NEW S32V DDR Configurati Project INTRODUCTION

Continue training with video. Use training video resources from the Getting Started with the S32DS for Vision 2.0 collection case studies, if you Browse real examples of successful device programming across the Platform of all Products using CONTRACT CONT

You can view this tutorial as a video under the VIDEO tab of Getting Started page of S32 Design Studio

Create a New APEX2 Project Create an APEX2 Project from Example Debug an APEX2 Project using Emulator Debug an APEX2 Project using Lauterbach TRACE32

Debug an A53 Project using GDB PEMicro Interface Debug an A53 Project using GDB Remote Linux

#### **Prerequisite to the tutorial**

- Knowing the S32V234 product

- Have an understanding of the ISP architecture

- Be familiar with the vision SDK software

#### Agenda

- Tutorial Overview

- Make an ISP graph (project)

- -Make a basic graph

- Configure graph/block properties

- Generate source code from graph

- Validate graph

- Generate source code

- Application code for ISP

- Make an application

- Compile

- -Run

#### **Tutorial Overview:**

- 1. To start with, we will make an ISP graph using ISP Dataflow Project option

- -Just to make it simple we will use the ISP kernels available in Vision SDK

- Vision SDK provides many built-in Kernels readily available for user development

- -Once graph is made we will autogenerate code for ISP engine

- 2. Moving forward, we will use the code derived above and make a Linux application project

- This application will integrate ISP code with the host to run together smoothly.

Complete application will take an image from camera, processes it in ISP and put the processed image in DDR buffers. Once the image is in DDR buffer, host(A53 core running Linux) will direct the display control unit(DCU) to display it on screen

## MAKE A GRAPH

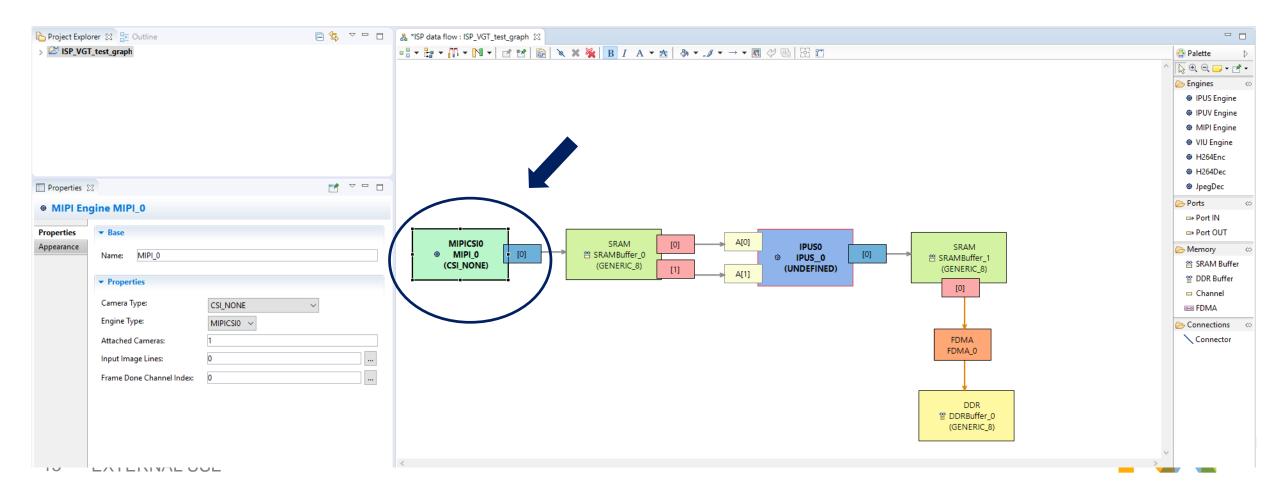

First of all we will simply connect different blocks to make a basic graph

#### Make an ISP Dataflow Project

- We will make a simple graph that does following:

- Grab an image from MIPI-CSI port >> Run Debayer kernel >> Transfer data to DDR buffer using Fast DMA

- Make a new ISP Dataflow Project named : ISP\_VGT\_test\_graph

| WorkspaceS32DS.3.1 - C/C++ - isp_so                                           |                        | 3_src/main.cpp - S32 Design Studio                                                                               |                                        |   |                                 |               |               | IV New ISP Data Flow Project                                                 | – 🗆 X                       |                                                               |            |

|-------------------------------------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------|---|---------------------------------|---------------|---------------|------------------------------------------------------------------------------|-----------------------------|---------------------------------------------------------------|------------|

| File Edit Source Refactor Navigate                                            |                        | figTools Run Creation VDK Debug Window H                                                                         | elp                                    |   | 🞬 New                           | – 🗆 X         |               |                                                                              |                             |                                                               |            |

| New<br>Open File<br>Open Projects from File System                            | Alt+Shift+N            | <ul> <li>S32DS Project from Example</li> <li>S32DS Application Project</li> <li>S32DS Library Project</li> </ul> | Ctrl+Alt+E<br>Ctrl+Alt+A<br>Ctrl+Alt+L |   | Select a wizard                 | -             |               | Create a new ISP Data Flow project<br>Create a new ISP Data Flow project     |                             |                                                               |            |

| Close<br>Close All                                                            | Ctrl+W<br>Ctrl+Shift+W | Makefile Project with Existing Code     C++ Project     C Project                                                |                                        |   | Create an ISP Dataflow project  |               |               | Project ni me: ISP_VGT_test_graph                                            |                             |                                                               |            |

| Save<br>Save As                                                               | Ctrl+S<br>Ctrl+Shift+S | C/C++ Project                                                                                                    |                                        |   | Wizards:<br>type filter text    |               |               | Use default location Location: C:\Users\nxa17459\workspaceS32DS.Vision.2018. | .R1\JSP_VGT_test_gri Browse |                                                               |            |

| Revert<br>Move                                                                | Ctri+Snirt+S           | <ul> <li>Convert to a C/C++ Project (Adds C/C++ Natu</li> <li>Source Folder</li> </ul>                           | re) **:                                |   | Visual Graph Tools              | ,             | `             | Choose file system: default \vee                                             |                             | Project Explorer 🛛 📴 Outline                                  | ₽\$₽ ▽ □ □ |

| Move Rename Refresh Convert Line Delimiters To                                | F5                     | Source File<br>Header File<br>File from Template                                                                 | ec.<br>ayı                             |   | C APEX2 Graph Project           |               | $\rightarrow$ | Working sets Add project to working sets Working sets:                       | Ne <u>w</u>                 | ISP_VGT_test_graph         ISP data flow : ISP_VGT_test_graph |            |

| <ul> <li>Print</li> <li>Switch Workspace</li> <li>Restart</li> </ul>          | Ctrl+P                 | G Class<br>☐ Evample<br>☐ Other                                                                                  | Ctrl+N                                 |   | ISP Dataflow Project            |               | ~             | Use default target project                                                   | Browse                      | 🕨 🗁 model                                                     |            |

| <ul> <li>Import</li> <li>Export</li> </ul>                                    |                        | <pre>int loomel, COMMON HeleMaccost(<br/>if(idxHelp &lt; 0)<br/>{ // print help message even if n</pre>          | , beln option is t                     |   |                                 |               |               | Static Sequencer                                                             | D/ Official                 |                                                               |            |

| Properties<br>1 main.cpp [isp_sonyimx224_csi_dcu,                             |                        | <pre>printf("%s", helpMsg_str); }</pre>                                                                          | o neip option is p                     |   | ? < <u>B</u> ack <u>N</u> ext > | Einish Cancel | ]             |                                                                              |                             |                                                               |            |

| 2 ISP data flow : ISP_VGT_test_graph<br>3 ISP data flow : mipi_simple [resour |                        | <pre>#ifndefSTANDALONE<br/>fflush(stdout);<br/>sleep(1);</pre>                                                   |                                        | I |                                 |               |               | (?) < <u>B</u> ack <u>N</u> ext >                                            | Einish Cancel               |                                                               |            |

| Exit                                                                          |                        | #endif // ifndefSTANDALONE                                                                                       |                                        |   |                                 |               |               |                                                                              |                             |                                                               |            |

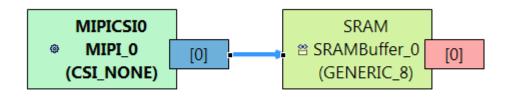

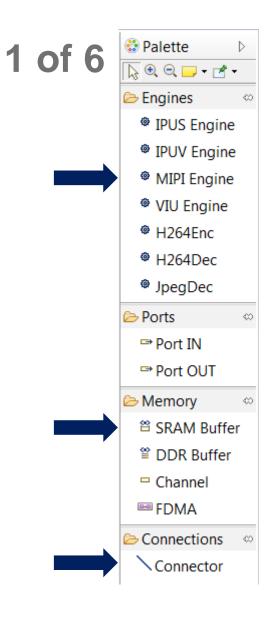

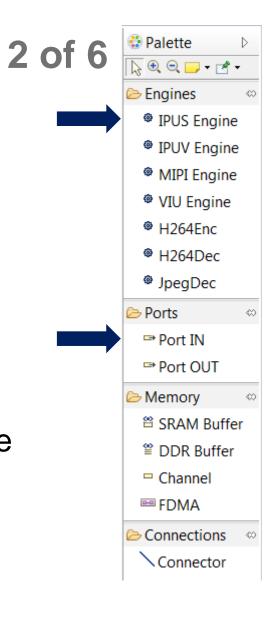

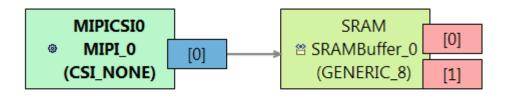

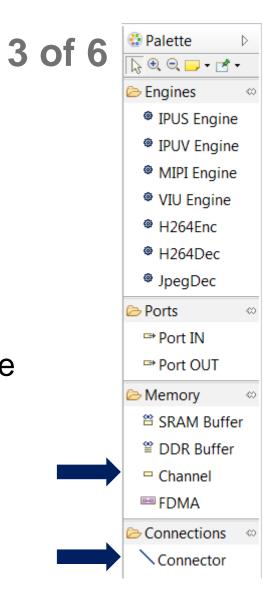

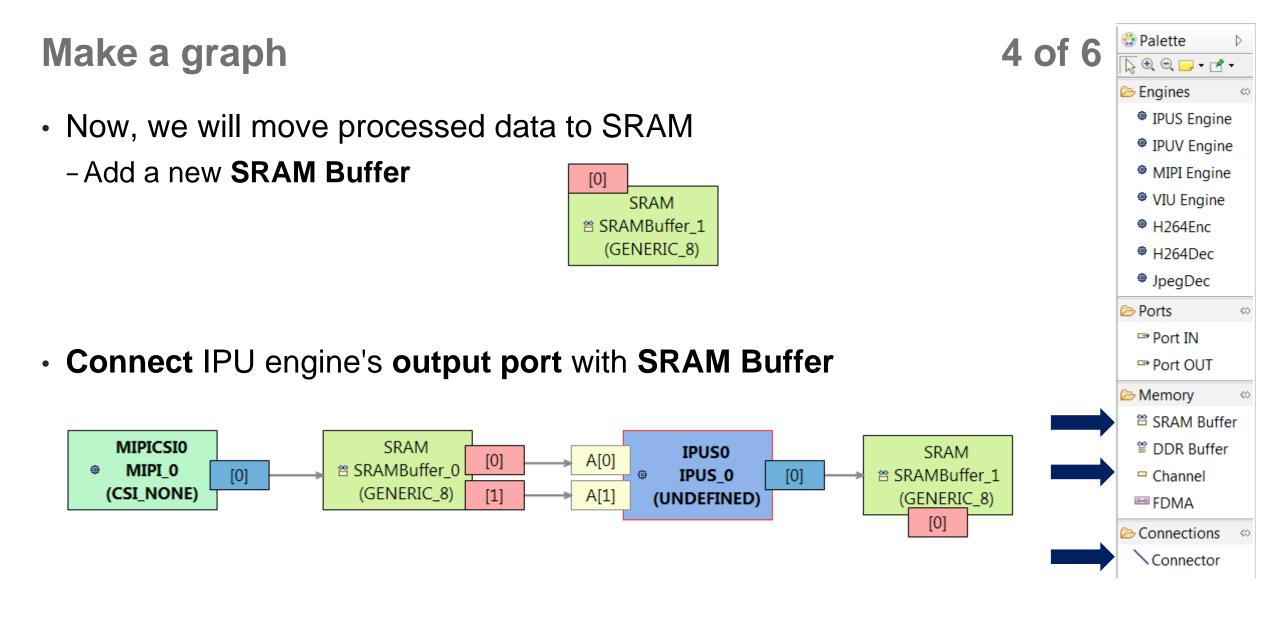

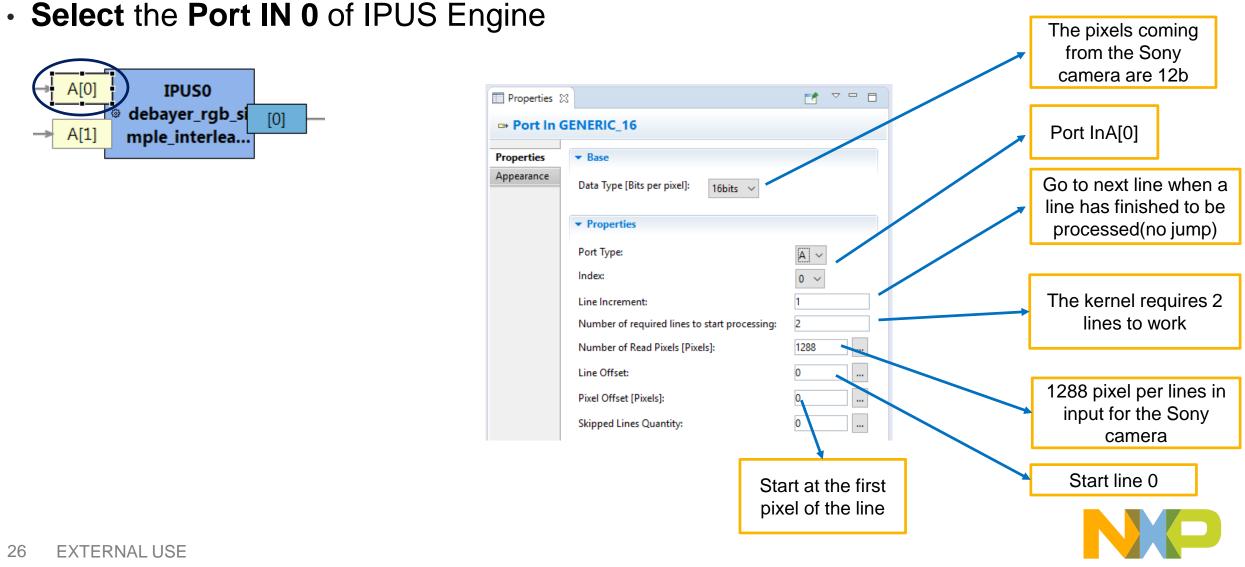

- From the **Palette** windows (right side of the S32DS window):

- Camera is connected to MIPI-CSI interface. Hence, we will start our pipeline from MIPI interface

- Select MIPI Engine block

- Image lines fetched from MIPI-CSI will now go to SRAM

- Select SRAM Buffer

- Connect both using Connector

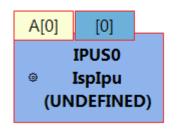

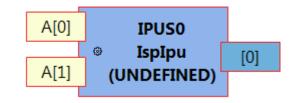

- Once necessary image lines are in SRAM, IPU(Image Processing Unit) engine grabs the image data and start processing it

- So we will add IPUS Engine

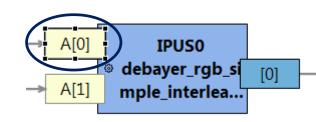

- We will be using "debayering kernel: that requires 2 images lines from the SRAM buffer to start processing, so we will add one more input port

- Add a new input port to it: Port In

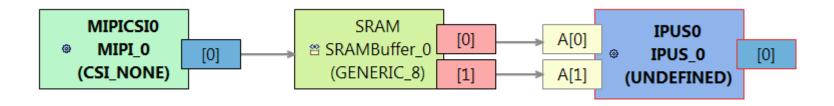

• For the same reason, add an output **Channel** to **SRAM Buffer**

Connect each SRAM channel with each input port of IPU engine

## NP

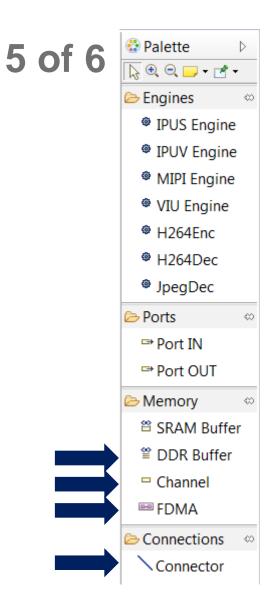

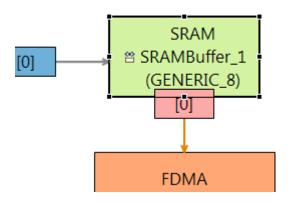

We will move processed line to DDR buffer via Fast DMA

Add a new Fast DMA block: FDMA

**FDMA**

FDMA 0

Connect Output Channel of SRMA Buffer to FDMA and FDMA to DDR Buffer

## CONFIGURE THE BLOCKS PROPERTIES

The basic graph is not able to process image unless it is directed. So, we will configure graph blocks to process image information in particular manner

#### **Graph properties**

- Click on the white area of the graph and look at the Properties

- Look at (open if not visible) the properties window

| Properties  Froperties Rulers & Grid Appearance | P_VGT_test_graph                                   | 0<br>4096<br>\${\$32DS_V\$DK_DIR}/isp/kernels/generic | Represent the space used<br>in SRAM by the graph. In<br>most cases, it should not<br>go over 1024kB                                                        |                |

|-------------------------------------------------|----------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|                                                 | Heart Beat Source:<br>Variables Suffix:<br>Headers |                                                       | Represents the space in SRA<br>unused by the graph. Althou<br>it covers all 4MBs of SRAM<br>remember that only <b>1MB</b> is<br>optimized for the ISP usag | igh<br>1,<br>s |

|                                                 | Defines                                            |                                                       | Folder containing the ISP kernels (assembly files)                                                                                                         |                |

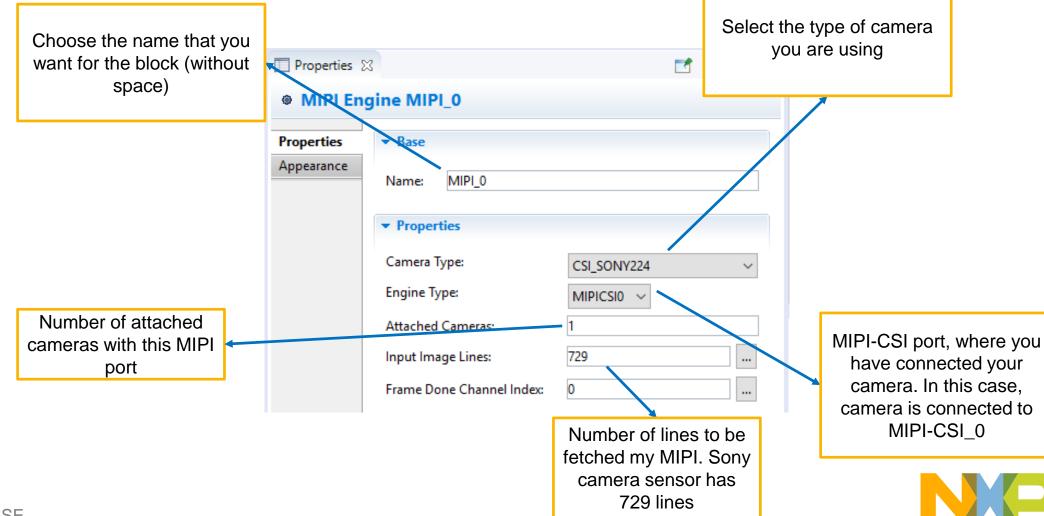

- Select the MIPI Block

- Again, look at the properties window

• MIPI Block : Configure the properties like follow:

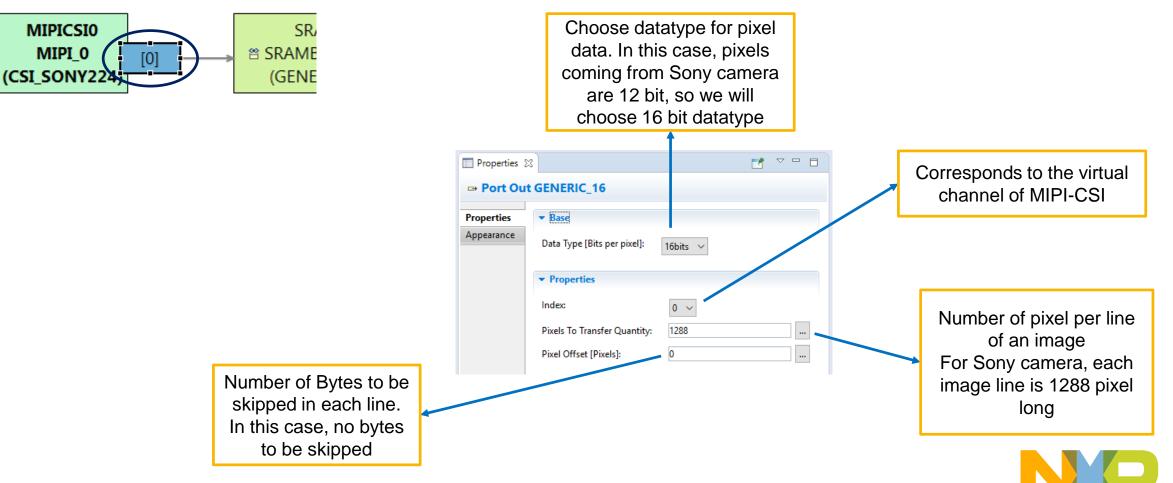

Select the Port OUT of MIPI Engine

۲

### 4 of 13

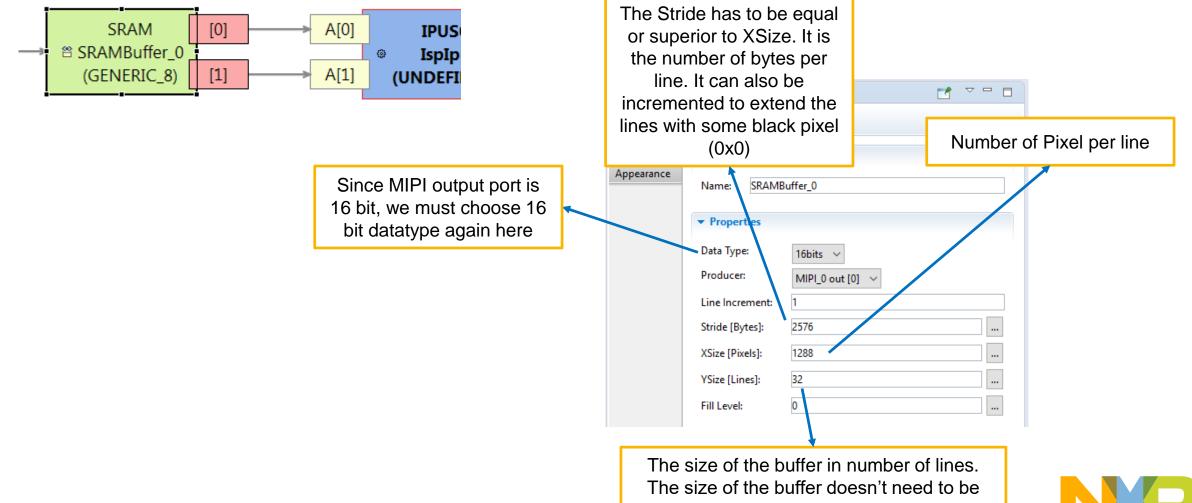

#### Select the SRAM Buffer

The size of the buffer doesn't need to be very big in particular in this case where only one Fast DMA channel will be running

#### 6 of 13

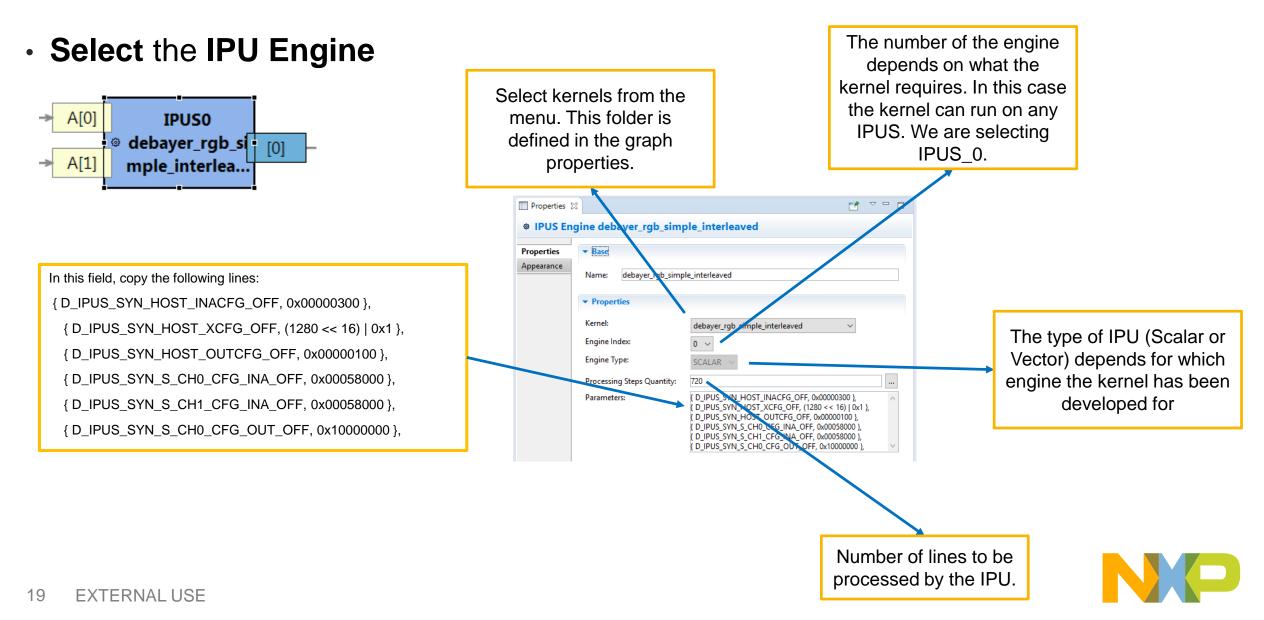

- The description of the registers can be found in the RM

- The example configurations for different kernels could be found in another graph(s32ds\_installation\_directory\S32DS\s32v234\_sdk\isp\graphs)

- Here is its meaning:

{ D\_IPUS\_SYN\_HOST\_INACFG\_OFF, 0x00000300 },

=> Enable InA[0] and InA[1] inputs

{ D\_IPUS\_SYN\_HOST\_XCFG\_OFF, (1280 << 16) | 0x1 },

=> 1280 pixels per lines, pixel processed one at a time (XPOS incremented by 1 with "pixel done" kernel instruction)

{ D\_IPUS\_SYN\_HOST\_OUTCFG\_OFF, 0x00000100 },

=> Enable OUT[0] output

{ D\_IPUS\_SYN\_S\_CH0\_CFG\_INA\_OFF, 0x00058000 },

=> InA[0] configuration: 16 bits, streamed pixel not repeated, every pixels of a lines is used, no added padding on the image border

{ D\_IPUS\_SYN\_S\_CH1\_CFG\_INA\_OFF, 0x00058000 },

=> InA[1] configuration: 16 bits, streamed pixel not repeated, every pixels of a lines is used, no added padding on the image

#### border

{ D\_IPUS\_SYN\_S\_CH0\_CFG\_OUT\_OFF, 0x10000000 },

=> OUT[0] configuration: 8bits (the frame will be in RGB888: R, G and B will be outputted one per one)

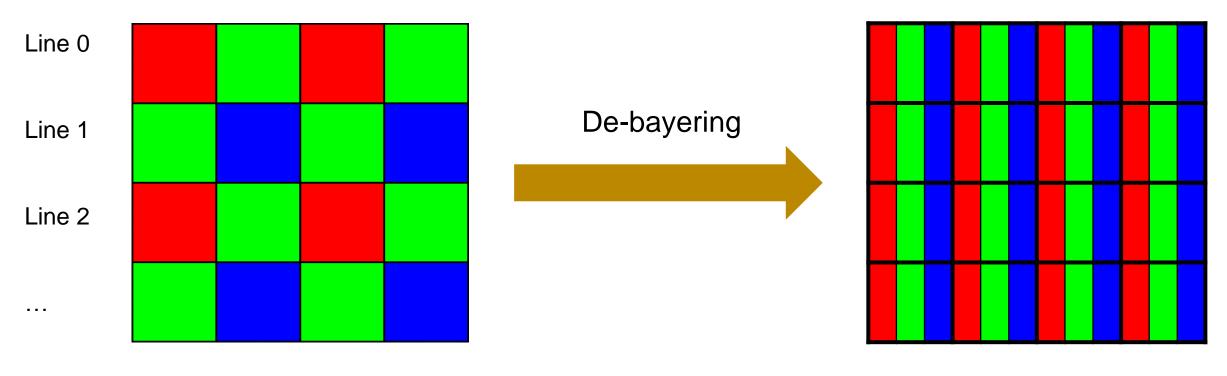

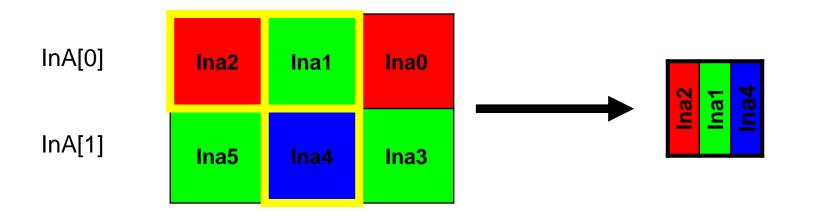

• Debayering is used to get the RGB value

#### 12b raw data

RGB888 (24b data)

Simple debayering scheme used here is copying neighbouring pixel value to find RGB value of the one pixel

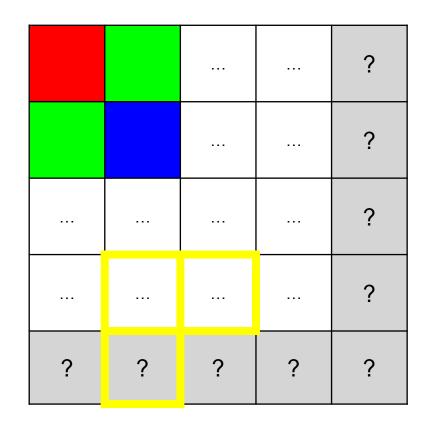

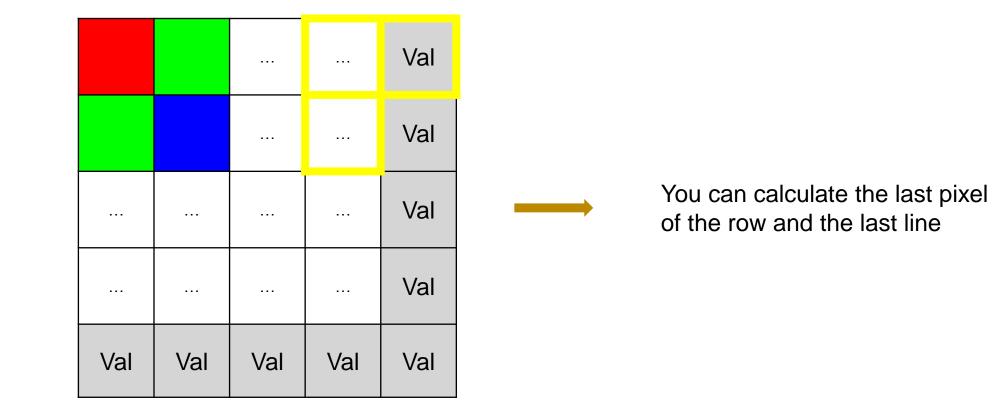

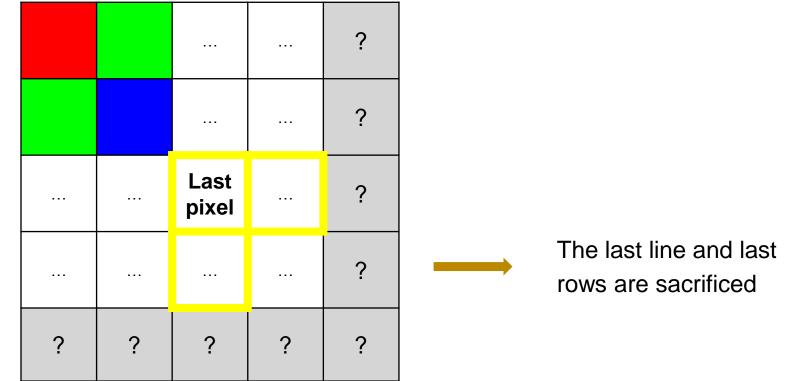

- With this scheme certain questions arise...

- -What happens when computing the last pixel of a line?

- -What happens when computing the last line of the frame?

• How to do on the border of the frame:

? . . . . . . ? . . . ... ? . . . . . . . . . . . . ? . . . . . . . . . . . . ? ? ? ? ? You cannot calculate the last pixel of the row and the last line

• Two solutions:

**Solution 1**: Use the Stream DMA to add lines (configuration in D\_IPUS\_SYN\_S\_CHx\_CFG\_INA\_OFF)

• Two solutions:

Solution 2: Not compute the last line and last row, decrease the resolution

In this example the solution 2 is chosen. The Sony camera has some extra lines and columns: 1296x726

#### 8 of 13

• Select the Port IN 1 of IPUS Engine

| ⇔ Port In ( | GENERIC_16                                    |      |   |                   |

|-------------|-----------------------------------------------|------|---|-------------------|

| Properties  | ▼ Base                                        |      |   |                   |

| Appearance  | Data Type [Bits per pixel]: 16bits 🗸          |      | [ |                   |

|             | ▼ Properties                                  |      |   | Port InA[1]       |

|             | Port Type:                                    | Α ~  |   |                   |

|             | Index:                                        | 1 ~  |   |                   |

|             | Line Increment:                               | 1    |   |                   |

|             | Number of required lines to start processing: | 2    |   |                   |

|             | Number of Read Pixels [Pixels]:               | 1288 |   |                   |

|             | Line Offset:                                  | 1    |   |                   |

|             | Pixel Offset [Pixels]:                        | 0    |   |                   |

|             | Skipped Lines Quantity:                       | 0    |   |                   |

|             |                                               |      |   | InA[1] is used to |

InA[1] is used to get the line below: start with line 1

#### 10 of 13

• Select the Port OUT of IPUS Engine

####

| Properties | rt GENERIC_8<br>▼ Base                                                                                            | The kernel outputs<br>R, G and B                             |

|------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Appearance | Data Type [Bits per pixel]: 8bits ~                                                                               | successively to create RGB888                                |

|            | ▼ Properties                                                                                                      | pixels                                                       |

|            | Index: 0 V                                                                                                        |                                                              |

|            | Pixels To Transfer Quantity: 3840                                                                                 |                                                              |

|            | Pixel Offset [Pixels]: 0                                                                                          |                                                              |

|            |                                                                                                                   |                                                              |

| ima        | his configuration we are cropping the ge by ignoring the right column. We add an offset to re-center the cropping | We want the output to<br>be 1280 pixel wide<br>(3x1280=3840) |

### 11 of 13

Select the other SRAM Buffer

| The Stride has to be equal<br>or superior to XSize. It is<br>the number of bytes per<br>line. It can also be<br>incremented to extend the<br>lines with some black pixel<br>(0x0)                                                                                                                                                                     | Number of Pixel per line           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| 암 SRAM Buffer SRAMBuffer_1                                                                                                                                                                                                                                                                                                                            |                                    |

| Properties         Appearance         Name:       SRAMBuffer_1 <ul> <li>Properties</li> <li>Data Type:</li> <li>Bbits ~</li> <li>Producer:</li> <li>debayer_rgk</li> <li>Line Increment:</li> <li>Stride [Bytes]:</li> <li>3840</li> <li>XSize [Pixels]:</li> <li>3840</li> <li>YSize [Lines]:</li> <li>16</li> <li>Fill Level:</li> <li>0</li> </ul> | o_simple_interleaved out [0] ∨<br> |

The size of the buffer in number of lines. The size of the buffer doesn't need to be very big in particular in this case where only one Fast DMA channel will be running

#### 12 of 13

• Select the FDMA (Fast DMA block)

| 📼 FDMA F   | 0_AMC                      |                     |   |

|------------|----------------------------|---------------------|---|

| Properties | ▼ Base                     |                     |   |

| Appearance | Name: FDMA_0               |                     |   |

|            | - Propeties                |                     |   |

|            | Line Increment:            |                     | 1 |

|            | Number of required lines t | o start processing: | 1 |

|            | Line Offset:               |                     | 0 |

#### 13 of 13

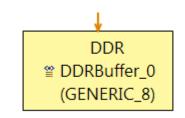

Select the DDR Buffer

ISP graph is now completely READY!

## GENERATE SOURCE CODE FROM GRAPH

Once graph is constructed completely, the graph tool allows us to autogenerate source code from it. In this part, we will generate ISP source code for Linux application

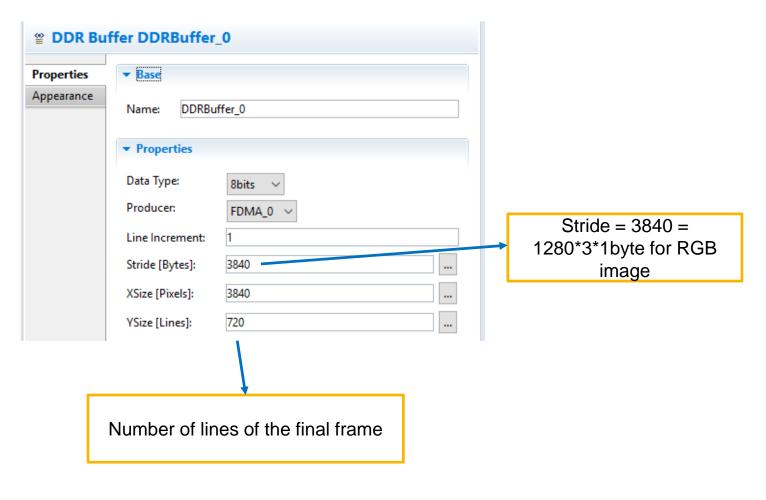

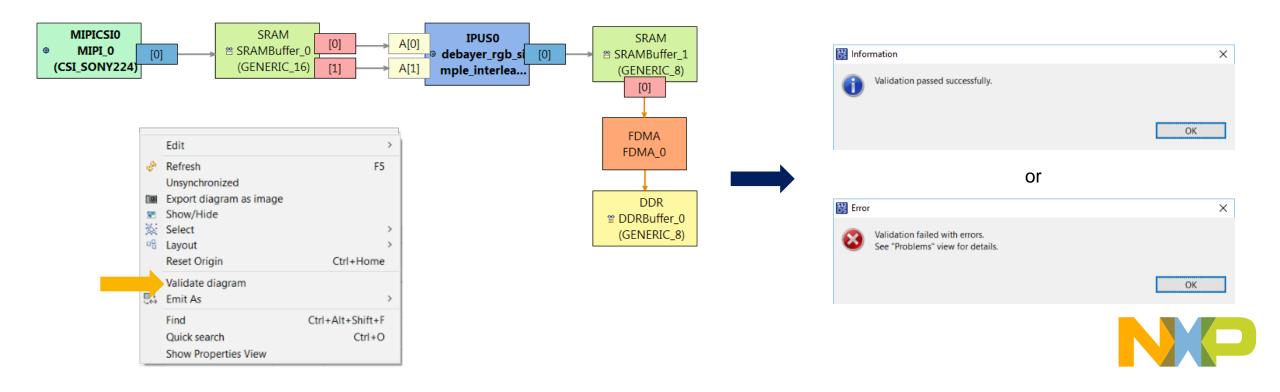

#### Validate graph for correctness

- Save the graph

- Right Click anywhere in the white part of the graph

- Validate graph

- -You will see a pop-up window showing status of validation.

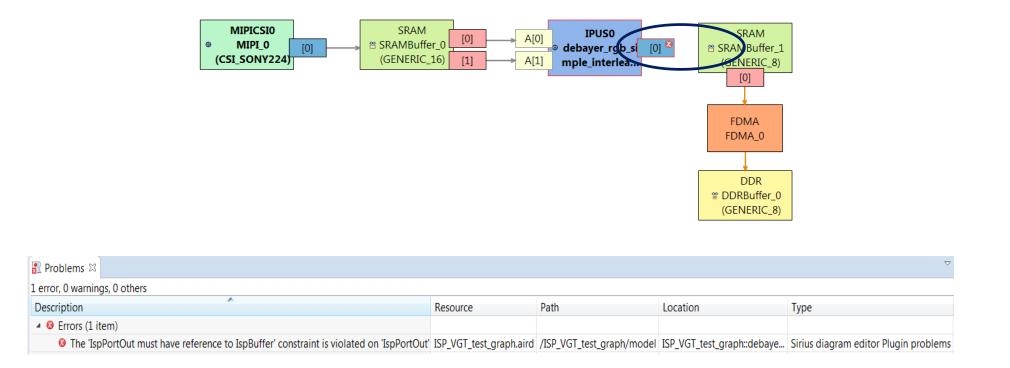

### **Validation Error**

#### 1 of 2

• Error will be indicated by red cross on the block and description can be seen in the **Problems View**

• Find the root cause of the error(s), correct it and Validate your graph.

#### **Validation Error**

• Data type not matching

One 'data\_type\_must\_be\_the\_same' constraint is violated on '<ISPGraphClass>

>The data type between an input port of the IPU and the SRAM buffer is different

• Name error

O The 'name\_has\_to\_start\_with\_alphabet\_letter' constraint is violated on '

#### DDR buffer configuration

One 'stride\_must\_be\_multiple\_of\_32' constraint is violated on

#### Make a Linux application project without an ISP graph

- Once graph is validated, next step is to generate source code from graph

- We will generate ISP code directly in this Linux application project

- So the next step is:

- Make a new application project named : ISP\_test\_application

1. Go to File -> New -> S32DS Application Project

| \$32<br>DS | works          | paceS32[  | OS.3.1 - Vis | ual Graph To | ools - ISP | _test_app | olication/   | A53_      | src/ma                                                                                                                                              | iin.cpp - S | 32 Design Stud | lio       |      |

|------------|----------------|-----------|--------------|--------------|------------|-----------|--------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|-----------|------|

| File       | Edit           | Source    | Refactor     | Navigate     | Search     |           |              |           |                                                                                                                                                     |             | VDK Debug      | Window    | Help |

|            | New            |           |              |              |            | Alt+S     | Shift+N >    | <b>P</b>  |                                                                                                                                                     |             | rom Example    | Ctrl+Alt- |      |

|            | Open           |           |              |              |            |           | Contract (1) | L.        | \$32D                                                                                                                                               | S Applicat  | ion Project    | GI+Alt+   |      |

| ٥,         | Open           | Projects  | from File S  | ystem        |            |           |              | -         | 3520                                                                                                                                                | - Library I | i i je ti      | Ctrl+Alt  | +L   |

|            | Close          |           |              |              |            |           | Ctrl+W       |           | <ul> <li>APEX2 Graph Project</li> <li>ISP Dataflow Project</li> <li>APEX2 Kernel Project</li> <li>APEX2 Program Project</li> <li>Project</li> </ul> |             |                |           |      |

|            | Close          | All       |              |              |            | Ctrl+S    | hift+W       |           |                                                                                                                                                     |             |                |           |      |

|            | Save           |           |              |              |            |           | Ctrl+S       |           |                                                                                                                                                     |             |                |           |      |

| Q.         | Save /         |           |              |              |            |           |              |           |                                                                                                                                                     |             |                |           |      |

|            | Save /         |           |              |              |            | Ctrl+     | Shift+S      | 📑 Example |                                                                                                                                                     |             |                |           |      |

|            |                |           |              |              |            |           |              |           | Other                                                                                                                                               |             |                | Ctrl+     | N    |

| 1          | Move.<br>Renar |           |              |              |            |           | F2           | Г         |                                                                                                                                                     |             |                |           |      |

| e<br>S     | Refres         |           |              |              |            |           | F2           |           |                                                                                                                                                     |             |                |           |      |

| _          | Conve          | rt Line D | elimiters To | 0            |            |           | >            | E .       |                                                                                                                                                     |             |                |           |      |

| <u>-</u>   | Print          |           |              |              |            |           | Ctrl+P       | Ŀ         |                                                                                                                                                     |             |                |           |      |

|            | Switch         | Worksp    | ace          |              |            |           | >            |           |                                                                                                                                                     |             |                |           | _    |

|            | Restar         | t         |              |              |            |           |              | Ŀ.        |                                                                                                                                                     |             |                |           |      |

| è          | Impor          | t         |              |              |            |           |              |           |                                                                                                                                                     |             |                |           |      |

| 2          | Expor          | t         |              |              |            |           |              | L .       |                                                                                                                                                     |             |                |           |      |

|            | Prope          | rties     |              |              |            | Alt       | t+Enter      |           |                                                                                                                                                     |             |                |           |      |

|            | 1 maii         | n.cpp [IS | P_test_app   | lication/A5  | 3_src]     |           |              | Ŀ         |                                                                                                                                                     |             |                |           |      |

|            | 2 ISP_         | VGT_test  | graph.aird   | [ISP_VGT_    | te]        |           |              |           |                                                                                                                                                     |             |                |           |      |

|            | 3 ISP o        | data flow | : ISP_VGT_   | test_graph   |            |           |              |           |                                                                                                                                                     |             |                |           |      |

|            | 4 maii         | n.c [S328 | 276_K2TV     | _Hello_Worl  | d/src]     |           |              |           |                                                                                                                                                     |             |                |           |      |

|            | Exit           |           |              |              |            |           |              |           |                                                                                                                                                     |             |                |           |      |

- 2. Type the **project name**: **ISP\_test\_application**

- 3. Select **project type** as shown

- 4. Hit Next

| reate a S32 Design Studio Project                                                                                                                                                                 |                                          |                    |                  |             |           |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------|------------------|-------------|-----------|------|

| New S32DS Application Project                                                                                                                                                                     |                                          |                    |                  |             |           |      |

| roject name                                                                                                                                                                                       |                                          |                    |                  |             |           |      |

| ISP_test_application                                                                                                                                                                              |                                          |                    |                  |             |           |      |

| Use default location                                                                                                                                                                              |                                          |                    |                  |             |           |      |

| ocation: C:\Users\nxa17459\workspaceS32DS.3                                                                                                                                                       | 3 1\ISP test appl                        | ication            |                  |             | Browse    |      |

|                                                                                                                                                                                                   | sintion_test_appi                        | leation            |                  |             | DIOWSC    |      |

| Processors:                                                                                                                                                                                       | ToolChain Sel                            | lection:           |                  |             |           |      |

|                                                                                                                                                                                                   | Core Kind                                | Name               | Toolchain        |             |           |      |

| type filter text                                                                                                                                                                                  | Core Kind                                | Name               | Toolchain        |             |           |      |

| type filter text  Comparison family S32V2                                                                                                                                                         | Core Kind<br>A53                         | Name<br>Cortex-A53 | ARM Linux 64-bit | Target Bina | ry Toolci | ha v |

| 71                                                                                                                                                                                                |                                          |                    |                  | Target Bina | ry Toolcl | h≀ ∨ |

| ✓ ➢ Family S32V2                                                                                                                                                                                  |                                          |                    |                  | Target Bina | ry Toolci | hi ∨ |

| <ul> <li>Content Service Context - M4</li> <li>S32V232 Cortext - M4</li> <li>S32V232 Cortext - A53</li> <li>S32V232 Cortext - A53 Linux</li> </ul>                                                | A53<br><                                 |                    |                  | Target Bina | ry Toolch |      |

| <ul> <li>Family S32V2</li> <li>S32V232 Cortex-M4</li> <li>S32V232 Cortex-A53</li> <li>S32V232 Cortex-A53 Linux</li> <li>S32V234 Cortex-A53 APEX2/ISP Linux</li> </ul>                             | A53<br><<br>Description:                 | Cortex-A53         | ARM Linux 64-bit |             |           | >    |

| <ul> <li>Family S32V2</li> <li>S32V232 Cortex-M4</li> <li>S32V232 Cortex-A53</li> <li>S32V232 Cortex-A53 Linux</li> <li>S32V234 Cortex-A53 APEX2/ISP Linux</li> <li>S32V234 Cortex-A53</li> </ul> | A53<br><<br>Description:<br>Linux Cortex | Cortex-A53         |                  |             |           |      |

| <ul> <li>Family S32V2</li> <li>S32V232 Cortex-M4</li> <li>S32V232 Cortex-A53</li> <li>S32V232 Cortex-A53 Linux</li> <li>S32V234 Cortex-A53 APEX2/ISP Linux</li> </ul>                             | A53<br><<br>Description:                 | Cortex-A53         | ARM Linux 64-bit |             |           | >    |

- Since we are developing separate ISP graph project and not using APEX, deselect unnecessary options as shown

- 3. Hit Finish

|                                | maken far iken            |      |

|--------------------------------|---------------------------|------|

| Select required cores and para | meters for them.          |      |

| Project Name                   | ISP_test_application      |      |

| Core                           | Cortex-A53                |      |

| SDKs                           | VSDK_MODULE_WIN           |      |

| Debugger                       | GDR Remote Linux Debugger |      |

| APEX2 programming              |                           |      |

| ISP programming                |                           |      |

| ISP visual modeling            |                           | <br> |

|                                |                           | <br> |

|                                |                           |      |

|                                |                           |      |

|                                |                           |      |

|                                |                           |      |

|                                |                           |      |

|                                |                           |      |

|                                |                           |      |

|                                |                           |      |

|                                |                           |      |

|                                |                           |      |

#### Select the destination of autogenerated source code 1 of 3

- By default all source code will be generated inside the ISP dataflow project itself

- We can reconfigure the destination of source code to any other open projects.

- -We will use this feature and generate the source code in Linux application project.

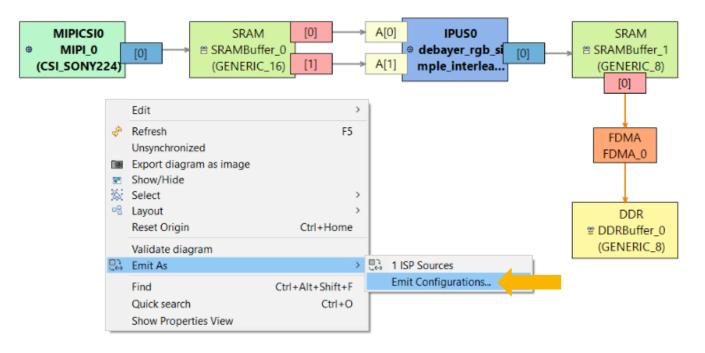

1. Select the **Emit Configuration..** option.

#### Select the destination of autogenerated source code 2 of 3

- Define a new configuration and specify where we want to generate our source code.

- 2. Create new configuration as shown in the picture

- 3. Click on **Apply** to save the changes

| ICommon]: Please use shared configuration. Shared fi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | le should be [target_project_name]/.launches                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Image: Second system         Image: Second system | Name:       emit_to_application         Image:       Main       Refresh       Common         Graph       //SP_VGT_test_graph/model/ISP_VGT_test_graph       Browse Workspace         Output       \${workspace_loc:/ISP_test_application}       Browse File System       Variables         Dynamic sequencer sources folder:       A53_gen       Static sequencer       Static sequencer         Image:       Static sequencer       Revert       Apply |

38 EXTERNAL USE

#### Select the destination of autogenerated source code

- Edit some more configuration

- 2. Go to **Common** tab.

- 3. Select the **\ISP\_test\_application\.launches** folder under "Shared files" option here.

- 4. Apply the settings and Hit Emit button to generate a source code at the designated location

| -                           |                                                                                                                                           |                                                              |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| type filter text            | Name: emit_to_application                                                                                                                 | n                                                            |

|                             | Save as<br>O Local file<br>O Shared file:<br>\ISP_test_a                                                                                  | application\.launches <u>B</u> rowse                         |

|                             | Display in favorites menu<br>□ E⇔Emit                                                                                                     | Encoding<br>Default - inherited (Cp1252)<br>Other ISO-8859-1 |

|                             | Standard Input and Output          Image: Standard Input and Output         Image: Allocate console (necessary         Image: Imput File: | for input)                                                   |

|                             | Workspace                                                                                                                                 |                                                              |

|                             | <u>W</u> orkspace                                                                                                                         | File <u>S</u> ystem Variables                                |

|                             | Launch in background                                                                                                                      |                                                              |

| Filter matched 4 of 4 items |                                                                                                                                           | Revert Apply                                                 |

3 of 3

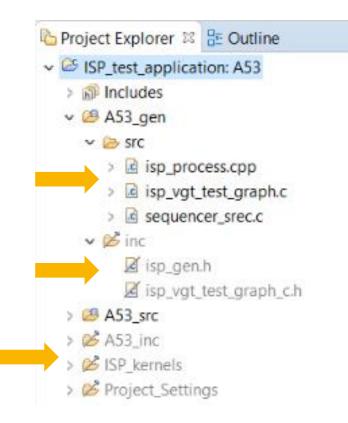

#### **Emit the source code**

- Auto generated code can be seen inside the project folder

- -Note: If you can not see source code, please right clock on the project and click on **Refresh** from the menu.

## LINUX APPLICATION PROJECT FOR ISP

Now, we have everything to build an application. Let's start building Linux application.

#### **Application Code for ISP**

- Basic, auto generated, application code template for ISP can be found in isp\_process.cpp in the function ISP\_CALL()

- ISP\_CALL() inside the **main.cpp** is just a place holder.

- User should move/add/change code inside the isp\_process.cpp and main.cpp according to his/her application needs or structure

- -Note: In this tutorial we will not change default structure as it is not necessary

#### **Application code for ISP : Compile**

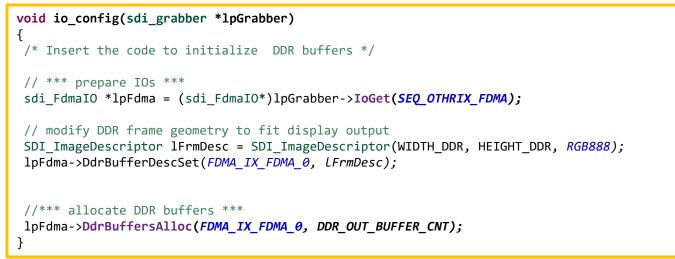

- We need to make changes & add code into application according to our requirement

- Our image is RGB888 type and by default DCU is configured to take YCbCr422 format. Hence, modify A53\_inc/isp\_user\_define.h with following...

17 #define DCU\_BPP DCU\_BPP\_24

٠

- 2. Modify main.cpp to define DDR buffers that stores images coming from ISP.

- Do not forget to add a header file: #include "isp\_vgt\_test\_graph\_c.h"

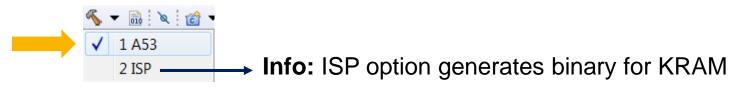

Go to C/C++ perspective and compile the application for A53 core

# Execute your ISP\_test\_application.elf binary on the target!

#### **Connect and Observe**

- Do not forget to connect Sony camera to MIPI-A port and HDMI output to display

- Run the application

- You can see camera captures streaming on the screen

- If no output image is shown and program exits instead of continuous loop, user should check that all settings were correctly entered in the graph diagram blocks

44 EXTERNAL USE

#### Tips

- Don't forget to <u>save</u> and <u>re-generate</u> the source code when you change your graph

- Emit source code step validates graph first then generates source code. So, graph validation is an optional step.

### SECURE CONNECTIONS FOR A SMARTER WORLD