User manual

#### **Document information**

| Info     | Content                                                                                                                                                                          |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords | SJA1105TEL, Ethernet, software registers                                                                                                                                         |

| Abstract | This user manual describes the configuration (including the static configuration interface), register structure and mapping of the SJA1105TEL 5-port automotive Ethernet switch. |

# UM10944

#### SJA1105TEL user manual

#### **Revision history**

| Rev | Date     | Description |

|-----|----------|-------------|

| 1   | 20170125 | first issue |

# **Contact information**

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

All information provided in this document is subject to legal disclaimers.

User manual

UM10944

2 of 81

# 1. Introduction

This software user manual describes the configuration of the SJA1105TEL 5-port automotive Ethernet switch. Topics covered include the static configuration interface and format, the register structure and mapping of the IP blocks. This document should be read along with the SJA1105 data sheet, available from NXP Semiconductors.

# 2. Functional overview

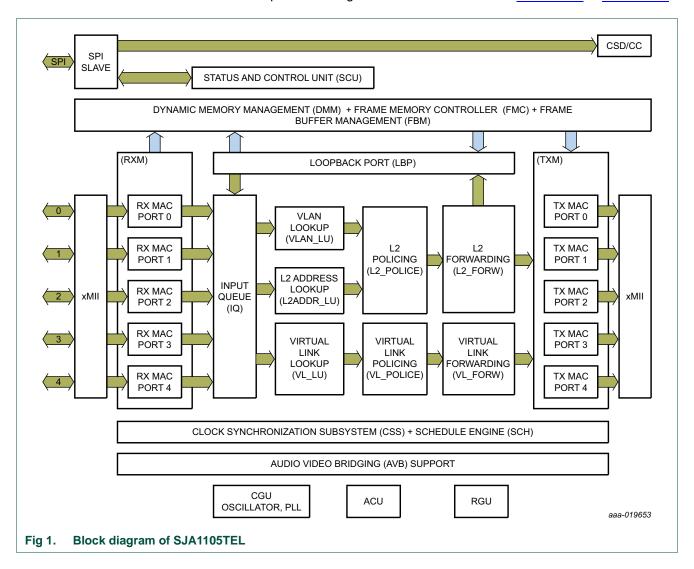

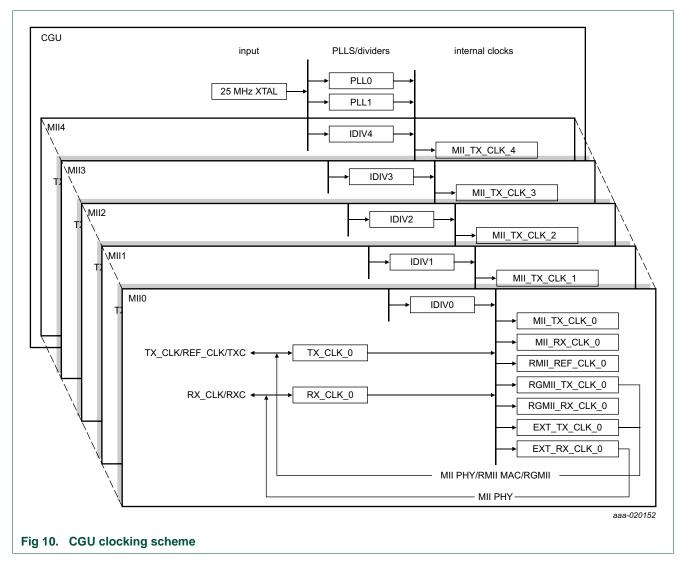

Figure 1 shows the building blocks that make up the SJA1105TEL. The base addresses of the core, CGU, RGU and ACU are given in <u>Table 1</u>. The dataflow followed by a single received frame as it passes through the switch is described in <u>Section 2.1</u> to <u>Section 2.3</u>.

UM10944

3 of 81

| SJA1105TEL memor | ry map                                                         |

|------------------|----------------------------------------------------------------|

| SPI base address | Description                                                    |

| 00000000h        | switch core, ingress, forwarding and egress configuration      |

| 00100000h        | clock generation unit to control Oscillator, PLLs and clocking |

| 00100400h        | reset generation unit                                          |

| 00100800h        | auxiliary configuration unit                                   |

|                  | <b>SPI base address</b><br>00000000h<br>00100000h<br>00100400h |

#### 0 14440FTE

#### 2.1 Ingress stage

A frame is received from a neighboring PHY or MAC on one of the available ports. The xMII block passes received data to the Receive MAC (RX MAC) connected to the reception port. The RX MAC performs low-level checks on the frame data and reports any CRC or MII errors detected to the status and control unit. The frame is immediately discarded when a low-level error is detected. A frame that passes all low-level checks is stored in frame memory in 128 byte segments. The RX MAC captures an ingress timestamp, extracts meta information from the frame and forwards it to the Input Queue (IQ). If a VLAN tag was not embedded in the received frame, the RX MAC block assigns a configured Port VLAN ID and a configured Port VLAN Priority to the frame. The IQ module stores the frame meta information in a deterministic order and passes it to the forwarding stage for further processing. If multiple frames are received at the same time on different ports, the processing order is determined by the port numbers; a frame received on a port with a lower ID is processed before a frame received on a port with a higher ID. Note that this only influences the frame order on the egress stage if multiple concurrently received frames are forwarded to the same destination port.

## 2.2 Forwarding stage

Once a valid MAC-level frame has been forwarded by the ingress stage, the forwarding stage applies several higher-layer checks on the frame and extracts the forwarding information.

The VLAN Lookup (VLAN\_LU) block reads the VLAN information configured for the VLAN ID associated with the frame. If a VLAN tag is embedded in the frame, the block checks if the reception port is configured to be a member of this VLAN. If it is not, the frame is dropped and reported to the status and control unit. It also checks if the VLAN associated with the frame is configured for mirroring or retagging and determines which egress port it should be transferred to.

The Address Lookup (L2ADDR LU) block extracts forwarding information from the source MAC address and VLAN ID to be used with future frames addressed to this MAC address and VLAN ID combination. The VLAN ID is ignored during this process if shared address learning is activated. This block also looks up the destination MAC address and combines it with the VLAN ID to determine the forwarding information for the frame.

The Policing (L2\_POLICE) block meters the incoming frame rate. The switch can be configured to drop packets if the maximum frame rate is exceeded.

The Forwarding (L2 FORW) block uses the information obtained from the other blocks to determine the set of ports to which the frame is forwarded. The switch can be configured to limit the number of egress ports accessible to frames received on a specific ingress port. For example, it is possible to direct that any frame received on a particular ingress port is only forwarded to a specific egress port, regardless of the forwarding information

UM10944

© NXP Semiconductors N.V. 2017. All rights reserved.

provided. This block also determines the VLAN priority to be embedded in frames forwarded by the switch as well as the egress priority queue in which a frame is stored on a per priority and per port basis. It also determines if the mirroring port shall be included in the set of ports to which the frame is forwarded, based on the information configured for port-based and VLAN-based ingress and egress mirroring. The L2\_FORW block also reserves the required memory space in the partition assigned to the frame by the policing module.

The Loopback Port (LBP) replicates frames that are configured to be retagged based on the associated VLAN configuration. A different VLAN ID is embedded in the replicated frame. It is associated with the same source port as the frame that triggered the replication when fed to the forwarding stage. It follows the configured forwarding rules for this MAC address and VLAN configuration.

# 2.3 Egress stage

The egress stage recomposes the frame from the data stored in the frame memory and the information gathered by the forwarding stage. It also performs the one-step transparent clock update for IEEE 1588 event frames which have the one-step bit set in the frame header. The Transmit MAC (TX MAC) assigns the frame to the priority queue determined by the forwarding stage. It monitors the number of frames stored in the priority queue. If the maximum number allowed has been exceeded, the frame is dropped and an error condition is signaled to the status and control unit. The TX MAC also performs priority selection based on the strict-priority algorithm and considers whether the credit-based shaper assigned to the priority queue is in the transmission-allowed state.

# 3. SPI interface

All memory, control and status registers can be accessed via the Serial Peripheral Interface (SPI). The device operates as a slave device in transfer mode 1 with CPOL = 0 and CPHA = 1. Both master and slave must operate in the same mode.

The SJA1105TEL expects a frame format in which the access type, address and data are encoded in a single SPI transaction. The format must conform to the SPI framing described in <u>Section 3.1</u> to <u>Section 3.3</u>. The device uses a double word addressing scheme.

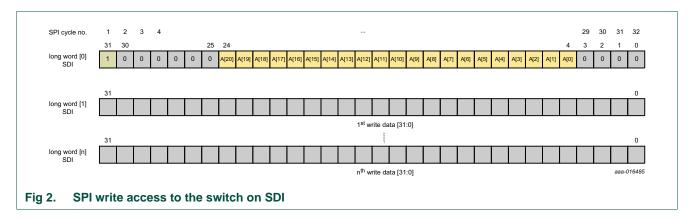

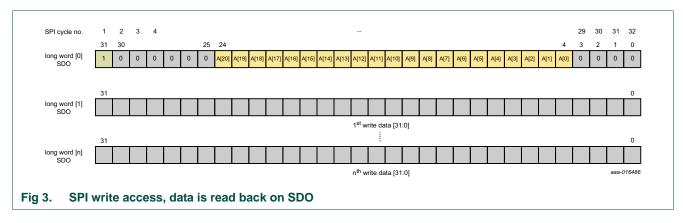

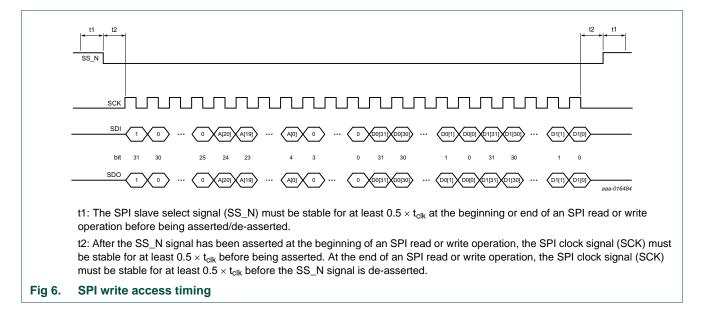

## 3.1 Write access

A write access consists of a 32-bit control phase followed by a data phase of up to  $64 \times 32$  bits. The 21-bit address is encoded in control bits[24:4]. The access type is encoded in the MSB, control bit[31]. Both control and data phases are transmitted from MSB to LSB.

Bit[31] is set to 1 to indicate a write operation. A data phase of at least 32 bits, but no more than  $64 \times 32$  bits, is transmitted after the control phase. Both control and data phases are mirrored to SDO during a write operation. Unused control bits must be logic 0.

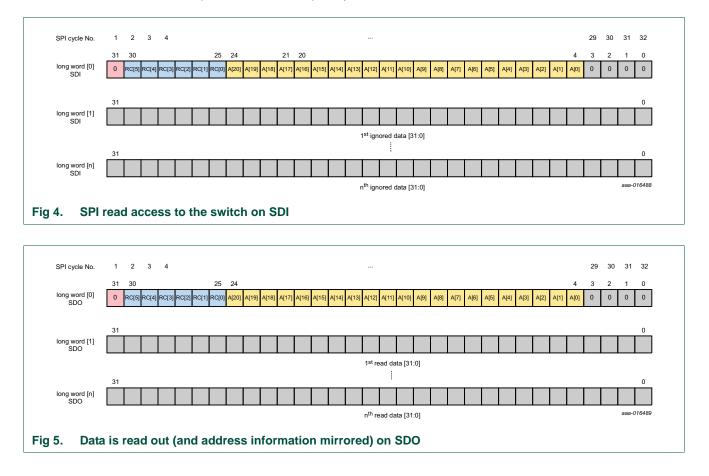

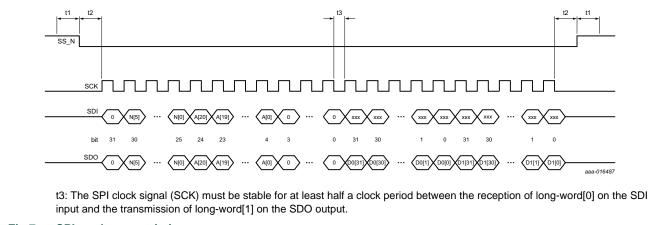

## 3.2 Read access

A read access is similar to a write access. The access bit (bit[31]) is 0 to indicate a read operation. Bits[30:25] contain the number of 32-bit double words to be read from the device. The device shifts out the corresponding data in the data phase. As with a write access, the address phase is mirrored to SDO. Unused control bits must be logic 0. A read count value of 0 (RC = 0) specifies a read of 64 consecutive words.

**Remark:** When CGU registers are read, a 64 ns delay must be inserted between the control and data phases to allow the CGU to retrieve the data. Alternatively, the access can be performed at a frequency below 17.8 MHz.

#### Fig 7. SPI read access timing

# 4. Ethernet switch core interface control

Two distinct interfaces are used to configure the switch core. When the device is powered up, it expects to receive an input stream containing initial setup information over the configuration interface. The initial configuration data sets the port modes, sets up VLANs and defines other forwarding and quality-of-service rules. Once the device is operational, it can be reconfigured at runtime over the programming interface (see <u>Section 5</u>).

This section explains the loader format, the individual configuration blocks (tables) and associated fields. A host microcontroller must upload a valid configuration stream every time the SJA1105TEL is reset or power-cycled. The CONFIGS flag in the Initial device configuration flag register (<u>Table 26</u>) is set once the device has been configured successfully.

# 4.1 Loading configuration data

Configuration information for the switch core must be loaded at start-up, using the generic loader format as described in <u>Section 4.1.1</u>. The configuration area starts at address 0x2 0000. The entire configuration area is write only. A read access to any address in this area returns arbitrary data.

The configuration data is divided into a number of blocks via the SPI interface, as described in Section 4.2. The blocks can be loaded in any order. The SPI interface is described in Section 3.

## 4.1.1 Generic loader format

Data is loaded into the configuration area as a continuous stream of 32-bit data. The load operation is initiated by writing the device ID (0x9E00 030E) to the configuration address space at address 0x2 0000. The format for subsequent write operations is illustrated in Figure 8. The configuration data blocks, listed in Table 2, are loaded in turn. The first double-word after the device ID contains the block ID; the second double-word contains length of the first data block to be loaded (i.e. the number of data double-words, excluding the checksum). This is followed by the CRC checksum and the data.

UM10944

9 of 81

# **UM10944**

#### SJA1105TEL user manual

|          | device ID    |

|----------|--------------|

|          |              |

| block ID | unused       |

| unused   | block length |

|          | CRC          |

|          | data         |

|          |              |

|          | data         |

|          | CRC          |

|          |              |

| block ID | unused       |

| unused   | block length |

|          | CRC          |

|          | data         |

|          |              |

|          | data         |

|          | CRC          |

|          |              |

|          | unused       |

| unused   | 0            |

|          | CRC          |

The data blocks can be loaded in any order. For the VLAN Lookup table, for example, the first 8 bits of the first double-word would contain the block id (0x07). The last 24 bits of the second double-word would define the number of entries (or data double-words) to be loaded. The VLAN Lookup table supports a maximum of 4096 entries, so the block length would be a value between 0x00 0000 and 0x00 2000.

Once all the configuration blocks have been successfully loaded, subsequent write operations are ignored.

A block length of 0 signals the end of the configuration file and a global CRC is expected to follow. Fields labeled 'not used' (e.g bits 0 to 26 in the VLAN Lookup table; see <u>Table 12</u>) are not interpreted by the IP and may be set to any value. However, the values assigned to 'not used' fields must be reflected in the checksum.

Checksums are calculated as CRC-32 Ethernet checksums with the lower bytes of each double-word included first in the CRC calculation. See IEEE 802.3-2015, clause 3 for details on how CRC checksums are calculated for Ethernet frames.

# 4.2 Switch configuration tables

This section describes the contents of the configuration tables. Configuration data is split into separate configuration blocks as shown in <u>Table 2</u>. These blocks must be loaded using the generic loader format. Blocks can be loaded in any order and a configuration block may be split into several loader format blocks.

Each entry is composed of an integer number of 32-bit double words, padded at the LSB. These padding bits are reserved and should be filled with zeros. An entry in the VLAN Lookup table (<u>Table 12</u>), for example, consists of two double words (64 bits). The upper 37 bits (63:27) are used to store valid configuration data; the lower 27 bits (27:0) are padding bits. An entry in the MAC Configuration table is 224 bits long (seven double words, see <u>Table 14</u>) and has a single padding bit (bit 0).

Entries provided first are written to the lower addresses in the respective table. Unused bits are located the lower end of each entry. An entry in the VLAN Lookup table, for example, contains 37 data bits, with 27 unused bits (see <u>Table 12</u>). The lower 27 bits of the first data double-word received contain the unused bits; the upper 5 bits contain the lower 5 bits of the data entry (bits 31 to 27). The second data double-word received contains the upper 32 bits (bits 63 to 32). This format is repeated for each entry in the table.

| Table name                             | Block ID | Loading mandatory?                       |

|----------------------------------------|----------|------------------------------------------|

| Schedule table                         | 00h      | no                                       |

| Schedule Entry Points table            | 01h      | yes, if Schedule table is loaded         |

| VL Lookup table                        | 02h      | no                                       |

| VL Policing table                      | 03h      | yes, if VL Lookup table is loaded        |

| VL Forwarding table                    | 04h      | yes, if VL Lookup table is loaded        |

| L2 Address Lookup table                | 05h      | no                                       |

| L2 Policing table                      | 06h      | yes, at least one entry                  |

| VLAN Lookup table                      | 07h      | yes, at least the default untagging VLAN |

| L2 Forwarding table                    | 08h      | yes                                      |

| MAC Configuration table                | 09h      | yes                                      |

| Schedule Parameters table              | 0Ah      | yes, if Schedule table is loaded         |

| Schedule Entry Points Parameters table | 0Bh      | yes, if Schedule table is loaded         |

| VL Forwarding Parameters table         | 0Ch      | yes, if VL Forwarding table is loaded    |

| L2 Lookup Parameters table             | 0Dh      | no                                       |

| L2 Forwarding Parameters table         | 0Eh      | yes                                      |

| Clock Synchronization Parameters table | 0Fh      | no                                       |

| AVB Parameters table                   | 10h      | no                                       |

| General Parameters table               | 11h      | yes                                      |

| Retagging table                        | 12h      | no                                       |

| xMII Mode Parameters table             | 4Eh      | yes                                      |

#### Table 2. Configuration tables

#### 4.2.1 Schedule table

<u>Table 3</u> shows the layout of entries in the Schedule table. A schedule can host up to 8 periods of arbitrary length. These periods are referred to as subschedules. The user may decide to use any number of subschedules but, if a schedule is enabled, subschedule zero must be one of, or the only, active subschedule. The number of subschedules defined, as well as whether the schedule is enabled, is determined by the settings of the Schedule Entry Points table as discussed in Section 4.2.2.

If the schedule is disabled, writing to this configuration block has no effect (and can be omitted). Entries for a particular subschedule must be provided in back-to-back write accesses and must be ordered according to their appearance on the timeline. The order in which the subschedules are provided is arbitrary (but it determines the contents of the Schedule Entry Points table, <u>Table 4</u>). Entries of subschedules with lower indices must be provided prior to entries of subschedules with higher indices. The entries are referenced by the ADDRESS field in the Schedule Entry Points table (<u>Table 15</u>) where the reference equals the ordinal number used to load the respective entry decremented by one (so the first entry of the Schedule table is referenced as 0). The table contains up to 1024 entries. This table is compulsory if entries are provided for the Schedule Entry Points table.

| Table 3.     Schedule table (block 00h) |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|-----------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit                                     | Symbol     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 63:54                                   | WINSTINDEX | Defines the index in the VL Forwarding table referred to by the WINST flag of the trigger. It is only used when WINST set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 53                                      | WINEND     | When set, indicates that the reception window of the entry of the VL Forwarding table indexed by VLINDEX ends here.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 52                                      | WINST      | When set, indicates that the reception window of the entry of the VL Forwarding table as indexed by WINSTINDEX starts here.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 51:47                                   | DESTPORTS  | Defines the ports (1 bit per each port) that the respective trigger event applies to. Bits at lower bit positions are assigned to ports with lower port numbers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 46                                      | SETVALID   | This flag is used to mark the first trigger to apply on a sampled non-time-triggered input. it allows the delivery order of a sampled non-time-triggered input to be fixed off-line. If such a delivery order is not needed, the flag is set for all triggers having the same VLINDEX value. For time-triggered input, the flag is usually set for all entries (since input and transmit triggers are in phase anyway). The TXEN flag of an entry must be set for this flag to have an effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 45                                      | TXEN       | If this flag is set, the current entry triggers dispatch of an output VL as indexed by the VLINDEX of the entry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 44:36                                   | RESMEDIA   | Contains an 'enable' flag at the highest bit position and one flag per priority at the output port, where the flag at the lowest bit position is assigned to priority 0. If the 'enable' flag is set, the switch stops processing all priority queues whose respective flags are in the lower bit positions of this field for all Ethernet ports that have their respective flag set in DESTPORTS; it enables processing of all priority queues whose respective flag set in DESTPORTS. The reservation state of ports not having their respective flag set in DESTPORTS does not change. Media reservation is processed individually for each subschedule and a priority queue at a specific port remains suspended as long as at least one subschedule has a reservation pending for this priority at this port. Transmission of locally sourced protocol control frames cannot be blocked by media reservation. At times that the schedule is stopped (not synchronized), all media reservation. |  |

Table 3. Schedule table (block 00h)

| Table 3. | Schedule table | (DIOCK UUN)continued                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit      | Symbol         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 35:26    | VLINDEX        | Defines the VL Forwarding table index (as discussed in <u>Section 4.2.5</u> ) the trigger refers to. The contents of the field are arbitrary when the TXEN flag of the entry is not set. If the TXEN flag of the entry is set, the VLINDEX field must contain a value smaller than the number of entries defined for the VL Forwarding table.                                                                                                                     |

| 25:8     | DELTA          | This parameter defines by how much the current trigger event precedes the next trigger event of the same subschedule in multiples of 200 ns. The user must ensure that no two entries in this, or another, subschedule, ever fire at the same time. To avoid the former, a value of zero is not allowed for this field. Schedule analysis is needed to prevent the latter (this analysis must take the contents of the Schedule Entry Points table into account). |

| 7:0      | not used       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

# Table 3. Schedule table (block 00h) ...continued

# 4.2.2 Schedule Entry Points table

Table 4 shows the layout of an entry in the Schedule Entry Points table. This table establishes the link between the synchronization algorithm and the schedule. If the user does not load this table, the schedule will not be active (whether or not the user loads the Schedule table). Each entry point into the schedule consists of 8 entries in the Schedule Entry Points table. The entries included in an entry point must be sorted in ascending order (i.e. those having smaller values must be loaded before those with larger values) according to their respective DELTA values. Undefined entries (if the subschedules are not all used) must be provided after the valid entries. The entry point must contain exactly one valid entry for each active subschedule (the table thus provides space for up to 2048 entries). No two entries of an entry point can contain identical DELTA values and zero is not allowed. The schedule starts when the local clock of the synchronization algorithm wraps with the entry point as indexed by the integration cycle number contained in the PCF used for integration.

|       |            | y rolling table (block off)                                                                                                                                                                                                                                                                                                                                                                             |

|-------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Symbol     | Description                                                                                                                                                                                                                                                                                                                                                                                             |

| 31:29 | SUBSCHINDX | This field defines the subschedule the respective entry point refers to. The value provided here must identify an active subschedule as defined by the SUBSCHEIND field of the Schedule Parameters configuration block. Any two entries of an entry point assigned to an active subschedule must contain different values for this field. An arbitrary value may be provided for inactive subschedules. |

| 28:11 | DELTA      | This field defines the delay before this entry fires in multiples of 200 ns. Any two entries of an entry point assigned to an active subschedule must contain different values for this field. A value of zero is not allowed. An arbitrary value may be provided for inactive subschedules.                                                                                                            |

| 10:1  | ADDRESS    | This field provides the index in the Schedule table holding the event to fire at the respective time. This index must be within the range assigned to the subschedule as identified by the SUBSCHINDX field of this entry and defined by the respective SUBSCHEIND field of the Schedule Parameters configuration block. An arbitrary value may be provided for inactive subschedules.                  |

| 0     | not used   |                                                                                                                                                                                                                                                                                                                                                                                                         |

| Table 4. | Schedule E | <b>Entry Points</b> | table (block 01h | ) |

|----------|------------|---------------------|------------------|---|

|          |            |                     |                  |   |

UM10944

13 of 81

# 4.2.3 VL Lookup table

<u>Table 5</u> and <u>Table 6</u> show the layout of an entry in the VL Lookup table. The table establishes the link between the stream identifier and the entry of the VL Policing table. The layout depends on the setting of the VLLUPFORMAT flag in the General Parameters configuration block (see <u>Table 22</u>). If the user does not load this table, all critical input traffic is dropped. The table has 1024 entries.

If VLLUPFORMAT is set to 0, the entries in the VL Lookup table must be sorted in ascending order (i.e. the smallest value must be loaded first) according to the following sort order: MACADDR, VLANID, PORT, VLANPRIOR. If VLLUPFORMAT is set to 1, the entries in the VL Lookup table must be sorted in ascending order according to the following sort order: VLLD, PORT.

#### Table 5. VL Lookup table when VLLUPFORMAT = 0 (block 02h)

| Bit   | Symbol     | Description                                                                                                                                                                                                                                                                                                                                    |

|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 95:91 | DESTPORTS  | This field contains the set of destination ports to which a frame matching this entry is forwarded if ISCRITICAL is cleared.                                                                                                                                                                                                                   |

| 90    | ISCRITICAL | When this field is set, the configured entry is treated as rate-constrained or time-triggered; if this field is cleared, the configured entry is a static configuration of a best-effort flow and is treated as best-effort.                                                                                                                   |

| 89:42 | MACADDR    | This field contains the destination MAC address to be associated with the respective table index.                                                                                                                                                                                                                                              |

| 41:30 | VLANID     | This field contains the VLAN ID to be associated with the respective table index position.                                                                                                                                                                                                                                                     |

| 29:27 | PORT       | This field contains the number of the input port the respective stream (as identified by MACADDR, VLANID and VLANPRIOR) is allowed to access. A stream may be allowed on any number of ports. If allowed on more than one port, it will have dedicated entries within the VL Policing table configuration block for each eligible source port. |

| 26:24 | VLANPRIOR  | This field contains the VLAN Priority to be associated with the respective table index position.                                                                                                                                                                                                                                               |

| 23:0  | not used   |                                                                                                                                                                                                                                                                                                                                                |

#### Table 6. VL Lookup table when VLLUPFORMAT = 1 (block 02h)

| Bit   | Symbol   | Description                                                                                                                                                                                                                                                                  |

|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 95:91 | EGRMIRR  | All traffic matching the stream identified by the VLLD and PORT fields of the entry, and routed to any of the ports having its flag asserted in this field, is routed to the mirror port (as defined by the MIRRORPORT field of the General Parameters configuration block). |

| 90    | INGRMIRR | If this flag is set, all traffic matching the stream identified by the VLLD and PORT fields of the entry is routed to the mirror port as defined by the MIRRORPORT field of the General Parameters configuration block.                                                      |

| 89:58 | not used |                                                                                                                                                                                                                                                                              |

| 57:42 | VLLD     | This field contains the VL ID to be associated with the respective table index position.                                                                                                                                                                                     |

| 41:30 | not used |                                                                                                                                                                                                                                                                              |

| 29:27 | PORT     | This field contains the number of the port the respective VL ID is allowed to access. A VL ID may be allowed on any number of ports. If allowed on more than one port, it will have dedicated entries in the VL Policing table configuration block for each source port.     |

| 26:0  | not used |                                                                                                                                                                                                                                                                              |

## 4.2.4 VL Policing table

Table 7 and Table 8 show the layout of an entry in the VL Policing table. This table provides timing and sizing rules for critical traffic. The rules to be applied depend on the type of traffic and, consequently, the table entries have different layouts depending on whether they are used to police time-triggered traffic or rate-constrained traffic. The table has 1024 entries.

VL Policing table - time-triggered VLs (block 03h) Table 7.

| Bit   | Symbol   | Description                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 63    | 1        | A value of 1 at this bit position indicates that the entry defines a time-triggered VL.                                                                                                                                                                                                                                                                                                                                                 |

| 62:52 | MAXLEN   | This field defines the maximum length of frames of this entry in bytes including all Ethernet overhead (6-byte destination MAC address, 6-byte source MAC address, 2-bytes EtherType field, 4-byte frame checksum). The maximum allowed value for this field is 2043.                                                                                                                                                                   |

| 51:42 | SHARINDX | Contains the index in the VL Forwarding table to be used with this entry. This index is usually the index of the entry itself. All entries for time-triggered VLs having identical values set for this field share memory space. They can be used to implement a pick-first-valid redundancy mechanism on time-triggered VLs on input. The dispatch policy is determined by the entry in the VL Forwarding table indexed by this field. |

| 41:0  | not used |                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### VL Policing table - rate-constrained VLs (block 03h) Table 8.

| Bit   | Symbol   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 63    | 0        | A value of 0 at this bit position indicates that the entry defines a rate-constrained VL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 62:52 | MAXLEN   | This field defines the maximum length of frames of this entry in bytes including all Ethernet overhead (6-byte destination MAC address, 6-byte source MAC address, 2-bytes EtherType field, 4-byte frame checksum). The maximum allowed value for this field is 2043.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 51:42 | SHARINDX | Contains the index within this table that holds the BAG and JITTER fields to be used for this entry. Usually, this index is the index of the entry. For shared BAGs, all entries in this table that share the BAG must contain the same value for this field and this value must be the index of one of the entries sharing the BAG. The values of the BAG and JITTER fields of entries that are not pointed to by any entry are not used. Unlike time-triggered VLs, the contents of this field is not used to access the VL Forwarding table. Rather, the index received from searching the VL Lookup table is used to access the VL Forwarding table for VLs being policed in rate-constrained fashion. |

| 41:28 | BAG      | The bandwidth allocation gap (BAG) value to be used for this entry in multiples of 100 $\mu$ s. A value of zero disables the bag check. In the latter case, JITTER must also be set to zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 27:18 | JITTER   | The bandwidth allocation gap (BAG) jitter value to be used for this entry in multiples of 10 $\mu$ s. The value provided for this field must not be larger (in seconds) than the value provided for the BAG field. For example, if the value of BAG was 5, the maximum allowed value for JITTER would be 50. This is deemed sufficient to police traffic received from an end system, which, according to the ARINC 664 p7 specification, exhibits a maximum jitter of 500 $\mu$ s at a minimum BAG value of 1 ms. Should jitter accumulate in a multi-hop network to exceed the BAG value, policing must be disabled (by setting BAG to zero) starting at the first switch where jitter exceeds the BAG.  |

| 17:0  | not used |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### 4.2.5 VL Forwarding table

<u>Table 9</u> shows the layout of an entry in the VL Forwarding table. This table provides forwarding definitions for critical traffic. The table has 1024 entries.

Table 9. VL Forwarding table (block 04h)

| Bit   | Symbol    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | ТҮРЕ      | A value of 1 at this bit position indicates that the entry defines a time-triggered VL (i.e., frames of the VL are dispatched to destination ports in response to triggers from the schedule). A value of 0 at this bit position indicates that the entry defines a rate-constrained VL (i.e., frames of the VL are immediately dispatched to destination ports).                                                                                                                                                                             |

| 30:28 | PRIORITY  | Priority at the output port for frames matching this entry where larger values indicate higher priority.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 27:25 | PARTITION | VL memory partition that frames matching this entry draw from.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 24:20 | DESTPORTS | Defines the ports that frames matching this entry are routed to (1 bit per port). Bits at lower bit positions are assigned to ports with lower port numbers. In the case of rate-constrained VLs, these flags define the ports the frame is dispatched to when all policing checks have been passed. In the case of time-triggered VLs, this field should be set to the bit-wise-or of the DESTPORTS fields of all the Schedule table entries that have set VLINDEX to point to this entry of the VL Forwarding table and have TXEN asserted. |

| 19:0  | not used  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

#### 4.2.6 L2 Address Lookup table

Table 10 shows the layout of an entry in the L2 Address Lookup table. Parts of the table can be statistically configured prior to dynamic address learning. Unlike other configuration blocks, loading of this block must not start before the L2BUSYS flag in the status area has been cleared (see Table 28). Entries in this table share memory with entries dynamically learned during operation. However, loaded entries never time-out and cannot be replaced by learned entries even in the case of a hash conflict. Physically, the memory used to store the lookup table has 1024 entries, organized in 256 rows each having 4 columns. The computed hash value maps to the row, so each hash conflict can be resolved four times.

#### Table 10. L2 Address Lookup table (block 05h)

| Bit   | Symbol    | Description                                                                                                                                                                                                                                           |

|-------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 95:84 | VLANID    | The VLAN ID associated with this entry. VLANID is only included in the lookup process if SHARED_LEARN in <u>Table 18</u> is cleared, otherwise this parameter is ignored. If SHARED_LEARN is set, the VLANID is set to zero for the hash computation. |

| 83:36 | MACADDR   | the MAC address associated with this entry                                                                                                                                                                                                            |

| 35:31 | DESTPORTS | Defines the ports (1 bit per port) to which frames carrying MACADDR as destination MAC address are forwarded. Bits at lower bit positions are assigned to ports with lower port numbers.                                                              |

|       | Table 10. Lz Address Lookup table (block 001)continded |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|-------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit   | Symbol                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 30    | ENFPORT                                                | If this flag is set, MACADDR is enforced as the source MAC address on ports having their flag set in DESTPORTS; i.e., an Ethernet frame with MACADDR as its source MAC address that is received on a port other than those set in DESTPORTS is dropped.                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 29:20 | INDEX                                                  | Contains the address in physical memory where this entry is stored. The physical address of an entry is calculated as INDEX = $4 \times hash$ (MACADDR, VLANID) + i, where i C {0;1;2;3}. If more than four MAC address/VLAN IDs pairs produce identical hashes, a different value for the POLY must be chosen or MAC addresses and VLAN IDs of endpoints or default VLANs of switch ports must be changed. If SHARED_LEARN is set, the VLANID portion of the hash computation is set to zero, regardless of the actual VLANID of the frame. The 8-bit CRC hash computation operates on 62 bits consisting of the 48-bit MAC address, 10-bit VLANID and 4 bits padded with 0. |  |

| 19:0  | not used                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

# Table 10. L2 Address Lookup table (block 05h) ... continued

# 4.2.7 L2 Policing table

<u>Table 11</u> shows the layout of an entry in the L2 Policing table. This table defines traffic policing rules for each port individually, along with a priority value for each port and switch broadcast traffic. The table has 45 entries. Ethernet frames received on mappings for which the user has not provided an entry are automatically mapped to entry 0 (all such traffic is dropped). The entry to which an incoming frame maps is determined in the following way: if the incoming frame is classified as broadcast, the matching entry is 40 + PORT (where PORT is the physical port number between 0 and 4); if the frame is not classified as broadcast, the matching entry is  $8 \times PORT + VLANPRIO$  where VLANPRIO is the VLAN priority value associated with the frame.

The switch allows traffic from different ports or priorities to share common policing blocks. Resolving the actual policing block is a two stage process. First, the device determines the entry as discussed above (i.e.  $8 \times PORT + VLANPRIO$  or 40 + PORT). The SHARINDX field of this entry is then used to determine the policing block. This SHARINDX field can point to any of the 45 available policing blocks.

The algorithm used for bandwidth budgeting works as follows. Each policing block contains the parameters SMAX and RATE. Initially, the bandwidth credit of an entry gets set to SMAX. When a valid Ethernet frame mapping to this entry is received, the value of the bandwidth credit is decreased by the number of bytes in the frame (including Ethernet header and checksum). At times when no traffic associated with this entry is received, the bandwidth credit gets increased by the value of RATE every 8  $\mu$ s, to a maximum of SMAX. An associated frame gets dropped if the resulting value of the bandwidth credit is less than or equal to zero. This makes it possible to control the traffic rate individually for each port. In addition to the rate, each entry specifies the maximum length of frames associated with this entry and the memory partition that gets credited for this frame. This makes it possible to partition the maximum amount of frame memory available for different traffic classes.

| Bit   | Symbol    | Description                                                                                                                                                                                                                                                                                                                                                                                   |

|-------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 63:58 | SHARINDX  | This field contains the index pointing to the policing entry associated with this frame. It is a pointer to the L2 Policing table itself and can be used to merge several traffic classifications in one combined policing entry. As an example, if all incoming L2 traffic from port 0 is to be policed by policing block 0, the value of SHARINDX for entries 0 through 7 must be set to 0. |

| 57:42 | SMAX      | This field contains the maximum burst size for received frames which map to this entry in bytes.<br>Its value is used to initialize the bandwidth budget for this entry on start-up. This field defines the<br>maximum bandwidth budget when no traffic associated with this entry has been received for a<br>long time.                                                                      |

| 41:26 | RATE      | This field contains the rate at which the bandwidth budget of traffic associated with this entry is credited when the port does not receive any traffic. The budget is credited RATE divided by 64 bytes every 8 $\mu$ s with a maximum value of SMAX. A port allowed to source traffic at 1 Gbit/s would thus have a value of 64000 set for this field.                                      |

| 25:15 | MAXLEN    | This field defines the maximum length of frames of this entry in bytes including all Ethernet overhead (6-byte destination MAC address, 6-byte source MAC address, 2-bytes EtherType field, 4-byte frame checksum). The maximum allowed value for this field is 2043.                                                                                                                         |

| 14:12 | PARTITION | Memory partition that Ethernet frames matching this entry will draw from.                                                                                                                                                                                                                                                                                                                     |

| 10:0  | not used  |                                                                                                                                                                                                                                                                                                                                                                                               |

Table 11. L2 Policing table (block 06h)

## 4.2.8 VLAN Lookup table

Table 12 shows the layout of an entry in the VLAN Lookup table. This table is used to statically configure VLAN information. A table entry defines the ports that are members of a specific VLAN. It also defines the broadcast domain together with the set of ports on which a VLAN tag has to be inserted or removed on egress. The table supports 4096 entries. If no entry is loaded, the switch is initialized with default entry: VING\_MIRR:0, VEGR\_MIRR:0, VMEMB\_PORT:0x1F, VLAN\_BC:0x1F, TAG\_PORT:0x1F, VLANID:0.

| Bit   | Symbol     | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 63:59 | VING_MIRR  | All traffic tagged with VLANID and received on any of the ports whose flag is asserted in this field is forwarded to the mirror port as defined by the MIRR_PORT field of the General Parameters configuration block.                                                                                                                                                                                                        |

| 58:54 | VEGR_MIRR  | All traffic tagged with VLANID and forwarded to any of the ports whose flag is asserted in this field is forwarded to the mirror port as defined by the MIRR_PORT field of the General Parameters configuration block.                                                                                                                                                                                                       |

| 53:49 | VMEMB_PORT | Defines the set of ports on which a frame tagged with the respective VLAN ID may be received.<br>All bits must be set in order to deactivate VLAN-based ingress port admission.                                                                                                                                                                                                                                              |

| 48:44 | VLAN_BC    | This field restricts the broadcast domain of the specific VLAN. That means that, if a bit is cleared, a frame tagged with the specific VLAN ID cannot reach the respective port. All bits must be set to deactivate reachability limitations for certain VLANs.                                                                                                                                                              |

| 43:39 | TAG_PORT   | Defines if a frame associated with the respective VLAN ID is transmitted untagged (the flag of these ports would be cleared in TAG_PORT), i.e., not containing an IEEE 802.1Q VLAN tag field, or transmitted with a tag (the flag of these ports would be set in TAG_PORT). As each untagged frame gets tagged on ingress with the port VLAN ID, all bits must be cleared in order to receive untagged frames at the output. |

| 38:27 | VLANID     | The VLAN ID associated with this entry.                                                                                                                                                                                                                                                                                                                                                                                      |

| 26:0  | not used   |                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### Table 12. VLAN Lookup table (block 07h)

## 4.2.9 L2 Forwarding table

<u>Table 13</u> shows the layout of an entry in the L2 Forwarding table. This table defines the mapping of ingress VLAN priority values to egress VLAN priority values as well as the mapping of egress VLAN priority values to priority queues physically available on the transmission ports. In addition, this table is used to define forwarding limitations for each ingress port.

The first five entries in the table are used for a per-port based remapping of the ingress priority values to egress priority values. For instance, the value of VLAN\_PMAP in entry 0 defines the mapping of either a received or per-port assigned ingress priority value  $p_i$  to an egress priority value  $p_0$  for frames received on port 0 by assigning  $p_0 = VLAN_PMAP[p_i]$ . This means that  $p_0$  will be used as the PCP (Priority Code Point) value on all egress ports forwarding the frame with a VLAN tag included (obtained by the TAG\_PORT parameter in the VLAN configuration, see Table 12).

The last eight entries in the table are used for a per-egress priority-based mapping of logical priority values to physical priority queues of the different ports. For the previously obtained egress priority value  $p_0$ , the resulting mapping to priority queues on each port i is obtained by assigning qi = VLAN\_PMAP[i], where qi is the priority queue used for  $p_0$  on port i. For example, to map priority value  $p_0 = 4$  to priority queue 1 on port 0 and to priority queue 2 on port 3, the value of VLAN\_PMAP for entry 5 + 4 = 9 must be set to 1 for index 0 and to 2 for index 3.

| Bit   | Symbol       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 63:59 | BC_DOMAIN    | Only valid for the first five entries in the table. Defines the broadcast domain of the port associated with the entry. Each port is assigned a bit in this field with the LSB mapping to port 0. Broadcast Ethernet frames received from the respective port are forwarded to the ports whose flags are set in this vector. The flag of the port associated with the entry itself must be cleared (to prevent loops).                                                                                                                                                                                              |

| 58:54 | REACH_PORT   | Only valid for the first five entries in the table. Defines which ports can be reached by traffic received on the port associated with the entry. Each port is assigned a bit in this field with the LSB mapping to port 0. If a frame is received on the port associated with the entry and its destination MAC address is known (i.e. is contained in the L2 Address Lookup table), the frame is forwarded to the destination port only if the flag of the destination port is set in this field.                                                                                                                 |

| 53:49 | FL_DOMAIN    | Only valid for the first five entries in the table. Defines the destination ports of unknown traffic at the port associated with this entry. Each port is assigned a bit in this field with the LSB mapping to port 0. If an Ethernet frame (that is not a broadcast frame) is received on the port associated with the entry and its destination MAC address is not known (i.e. is not contained in the L2 Address Lookup table), the frame is forwarded to those ports that have their respective flag set in this field. The flag of the port associated with the entry itself must be cleared (to avoid loops). |

| 48:46 | VLAN_PMAP[7] | For the first five entries in the table, this value defines the ingress VLAN priority remapping. The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| :     | :            | source port associated with the incoming frame is used as an index into the table, allowing ingress VLAN priority to egress VLAN priority mapping for each port. The result of the mapping                                                                                                                                                                                                                                                                                                                                                                                                                          |

| :     | :            | is embedded in the transmitted frame on all ports included in the tagged set of the VLAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |