# Simplified Industrial Safety Solutions

FTF-IND-F0108

Aaron McDonald

Industrial Automation & Control Marketing

Freescale, the Freescale logo. AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, mobileGT, PowerQUICC, Processor Expert, OorlQ, Oorivva, StarCore, Symphony and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airfast, BeeKit, BeeStack, CoreNet, Flexis, Magnir), MXC, Platform in a Package, Cord Qonverge, QUICC Engine, Ready Play, SafeAssure, the SafeAssure logo, SMARTMOS, TurboLink, Vybrid and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc.

### **Agenda**

- IEC61508

- Standard Explanation

- How Freescale Addresses the Standard

- SafeAssure

- Product Offerings

- Safety Process

- Safety Hardware

- Safety Software: Third-Party

- Safety Support

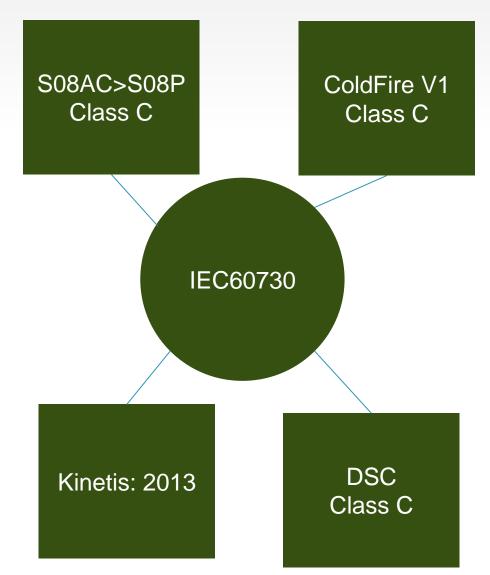

- IEC60730

- Standard Explanation

- How Freescale Addresses the Standard

- Software Coverage

- Product Offerings

## **Freescale and Safety**

- Safety is difficult and you need a partner who understands safety and your needs.

- Freescale offers industrial solutions for many safety applications, including IEC 61508 functional safety and IEC 60730 safety for automation electronics for household appliances

- Unique IP and architectures —

including safety checks, on-chip

redundancy, watchdogs and more

are used to satisfy the safety

requirements

Industrial disasters happen have happened and *will* happen. **Robust safety systems** are a key to **prevention**.

## **Safety Market Trends and Challenges**

# 1 Trends

- Recent events (Japan tsunami, BP oil spill) have continued to reinforce the need for automated process safety systems

- Functional safety increasingly becoming part of system designs (operations) and at corporate level

# 2 Increasing integration and system complexity

- Increasingly complex electronic control is driving designs with safety requirements in non-traditional markets, e.g. solar energy

- Increase in use of high-performance sensor systems and complex control algorithms results in substantially higher MCU performance requirements

# 3 Functional safety & mounting cost pressures

- An increasing number of industrial control systems require IEC61508 (SIL3) system safety certification

- Applications typically need to duplicate system and/or have additional system level components in order for this

to be to achieved

- Safety designs need to be designed from the ground up to ensure standards compliance

- Continuing pressure to reduce development cycle time and cost

# 4 Market trends outpacing customer experience levels

- Growing need for design-for-safety consultation and software support

# **Functional Safety Defined**

- Functional safety is the absence of unreasonable risk due to hazards caused by malfunctioning behavior of electrical/electronic systems

- Hazards: potential source of harm

- Harm: physical injury or damage to the health of people

- Failures are main impairment to safety:

- Systematic: failures, related in a deterministic way to a certain cause, that can only be eliminated by a change of the design or manufacturing process, operational procedures, documentation or other relevant factors

- Random: failures that can occur unpredictably during the lifetime of a hardware element and that follow a probability distribution

## What are Functional Safety Standards About?

- Functional safety standards impose a structured way for the industry to proceed

- IEC61508 V1 published as international standard ~2000

- IEC61508 V2 published as international standard 2010

- The standards address

- Architectural & functional aspects

- Procedural aspects (incl. safety lifecycle)

- How to avoid faults and to control faults

- Considering systematic faults and random hardware faults

- Rigorous documentation serves as evidence for complying to the safety standards

# **Evolving Functional Safety Standards**

## Safety Integrity Levels (SIL)

- Safety standards defining five levels with

- Availability, probabilities and consequences of failure

- Naming and definition vary by standard, e.g.:

- Industry (IEC61508): SIL 0 - SIL 4

Automotive (ISO26262):

ASIL A – ASIL D

- Medical (IEC60601): Level 1 - Level 3

| Safety<br>Integrity<br>Level | Demand Mode  |                                          | Continuous Mode                             | Consequence of a                             |  |

|------------------------------|--------------|------------------------------------------|---------------------------------------------|----------------------------------------------|--|

|                              | Availability | Probability of a failure on demand       | Probability of a dangerous failure per hour | failure                                      |  |

| SIL 4                        | > 99.99%     | >=10 <sup>-5</sup> to < 10 <sup>-4</sup> | $>=10^{-9}$ to $< 10^{-8}$                  | Potential for fatalities in the community    |  |

| SIL 3                        | 99.9%        | >=10 <sup>-4</sup> to < 10 <sup>-3</sup> | $>=10^{-8}$ to $< 10^{-7}$                  | Potential for multiple fatalities            |  |

| SIL 2                        | 99% - 99.9%  | >=10 <sup>-3</sup> to < 10 <sup>-2</sup> | $>=10^{-7}$ to $< 10^{-6}$                  | Potential for major injuries or one fatality |  |

| SIL 1                        | 90% - 99%    | >=10 <sup>-2</sup> to < 10 <sup>-1</sup> | $>=10^{-6}$ to $< 10^{-5}$                  | Potential for minor injuries                 |  |

| SIL 0                        |              | n/a                                      |                                             |                                              |  |

# Ifety and Performance in Motion

Unmatched performance and ruggedized safety features for almost anything that moves

### **Unmatched MCU** Performance

Get up to 600 DMIPS the most powerful core for MCUs today enabling single-chip design for complex algorithms

# Market- Leading Integration

Get up to 4 MB embedded flash and a rich set of analog, connectivity and timing peripherals to support complex realtime control

# Assured Safety, Quality & Reliability

Meets industrial, medical, and transportation requirements to ease safety approvals and durability mandates

# **Easy Development**

Make development a snap with run-time software, reference designs and tools for rapid prototyping, advanced debug and system modeling

# **PX** Series MCU Families for Industrial Applications

Safety and Performance in Motion

### Performance

### Performance-Leading MCU

### **PXR** Family

Built for single-chip, highperformance real-time applications

#### Target Applications:

- · Precision factory control

- Industrial automation

- Industrial transportation

- Motor control/drives

- Medical

- Timing applications

#### Features:

- · Up to 4MB Flash

- · 264MHz core frequency

- 600DMIPS

- · 2x eTPU

- 64ch Quad ADC

### **Functional Safety**

Redundancy Reliability Quality

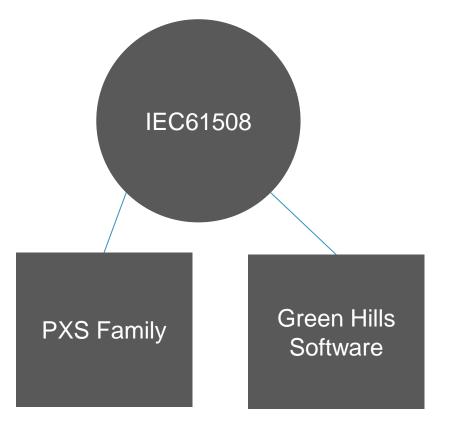

### **PXS Family**

Simplifying safety certification while implementing zero defect methodologies

#### Target Applications:

- · Industrial automation

- Aerospace control

- Motor control/drives

- Industrial transportation

- Power generation and management

- Medical

- Robotics

#### Features:

- Up to 2MB Flash

- Dual Locking Core

- · Sphere of Replication

- · up to 600DMIPS

- · Fault Control & Collection Unit

- · Optional Ethernet

### Connectivity

# Connected Performance

### **PXN Family**

Enabling data concentration and algorithm computation

#### **Target Applications:**

- · Industrial gateways

- Process measurement and control

- Industrial hub

- · Input/output (I/O) control

- · Programmable logic control

#### · Features:

- Up to 2MB Flash

- 2nd core to offload communication processing

- Up to 25 serial communication modules

- · Optional Ethernet

### HMI/User Interface

Single-Chip Display Solution

### **PXD Family**

Reduce footprint and cost for industrial display applications

#### Target Applications:

- Factory display units

- Building control display units

- Ruggedized displays

- Industrial instrumentation

#### Features:

- Up to 2MB Flash

- Display Control Unit driving up to WVGA

- Optional Video Input

- Stepper Motor Drivers

- Quad SPI Interface

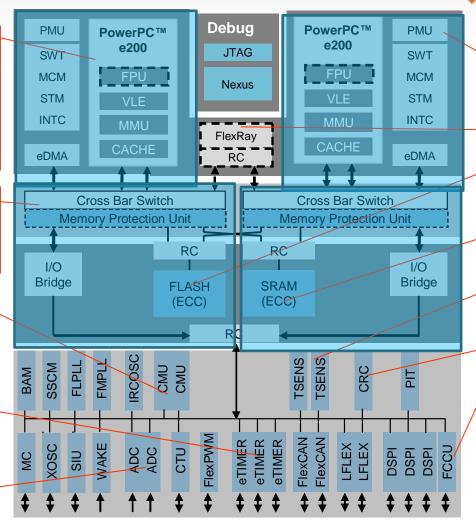

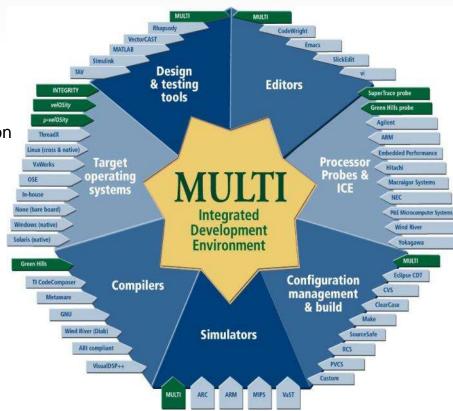

## **PXS Family**

Functional safety & performance: Designed for IEC 61508 SIL 3.

Only dual-core, dual-issue controller available that can switch between lock-step mode and dual-parallel mode

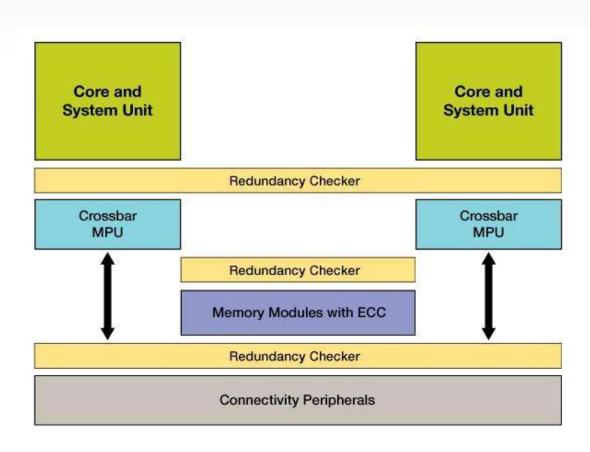

### **Sphere of Replication:**

Typically only the actual cores in lock-step MCUs are replicated. PXS goes beyond this with duplication of **all** computational elements.

Over 600 DMIPS performance from dual-core, dual-issue e200 running at 120 MHz

#### **Motor Control:**

Fast 12-bit ADCs, PWM and the new CTU (cross triggering unit) enable control of up to two brushless DC motors with minimum interrupt load

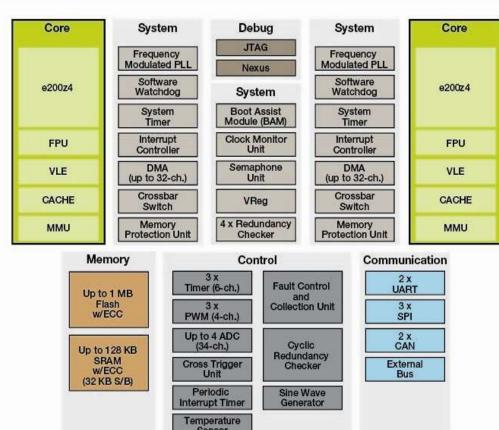

#### PXS20 Block Diagram

### **Functional Safety. Simplified.**

**Simplifies the process** of system compliance, with solutions designed to address the requirements of automotive and industrial functional safety standards

Reduces the time and complexity required to develop safety systems that comply with ISO 26262 and IEC 61508 standards

Supports the most stringent Safety Integrity Levels (SILs), enabling designers to build with confidence

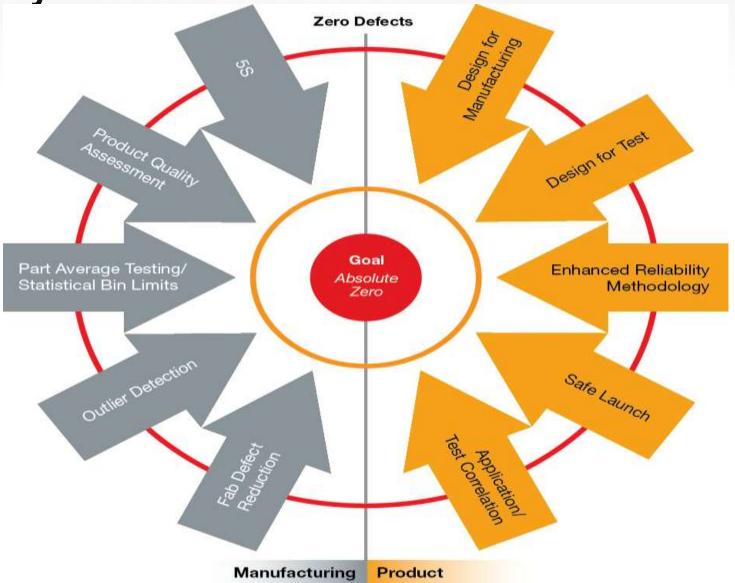

**Zero defect methodology** from design to manufacturing to help ensure our products meet the stringent demands of safety applications

# Freescale Approach to Functional Safety

**Safety Process: Zero Defect**

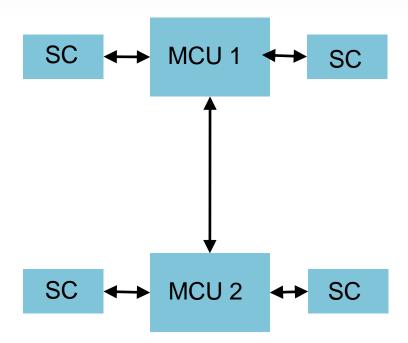

### Safety Hardware: Traditional Safety Approach

Multi-chip, single-core systems

Redundancy is created by using multiple chips and external safety components

### **New Safety System**

Single-chip, dual-core solution

One chip with replicated dual cores and integrated safety features

# (S20 Safety Measures at Module

### Level

#### **Sphere of Replication:**

- · Replicated e200Core

- · Replicated eDMA

- · Redundant INTC, SWT, etc

- Redundant MMU

- RC units at gates to non redundant sphere

#### XBAR + MPU:

- Redundant

- RC units at gates to non redundant sphere

#### **Clock Monitoring**

- Detects and mitigates clock disturbances

- PLL

#### **Timer**

eTimer0 channels "isolated"

#### **ADC**

On line assisted hardware BIST

#### **PMU**

- Internal Vreg

- Redundant Vmonitor

#### **Flexray**

#### Flash

• ECC

#### **RAM**

• ECC

#### **Temp Sensor**

Redundant

#### **CRC Unit**

· Application signature

#### **Fault Collection Unit**

- Detects when errors have occurred

- Indicates error to external

- Independent of software operation

### **Dual-Core Modes of Operation**

LSM Lock Step Mode

- 1x performance

- MCU mode which allows SIL3 with minimal software overhead

- Formal check of outputs for replicated IP modules

- Checker (RC) guarantee detection of noncommon cause faults when redundant channels are merged

- Up to 2x performance

- MCU mode which allows SIL3 with algorithm diversity

- CPU cores and subsystems run independently

- Checker units (RC) are disabled in this mode

- Device concept supports static configuration of the operating mode during Reset

- Selection between the two modes is done by programming a user option bit stored in the shadow sector of the flash array

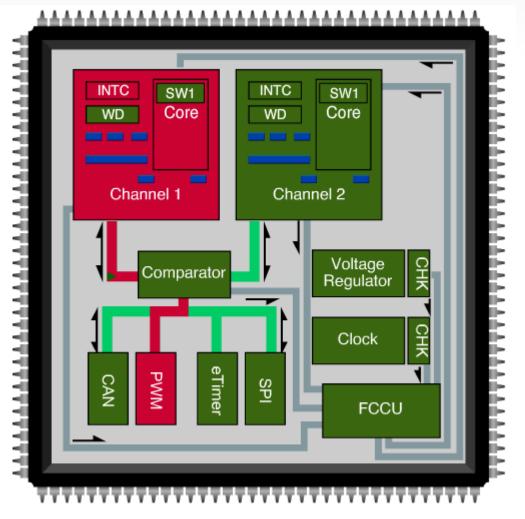

# Single-Chip Dual Core Fault Handling

- Fault constantly raises an interrupt at Core 1

- Core 1 can no longer execute safety-relevant application

- Core 1 does not issue expected commands to the PWM

- PWM considered failed

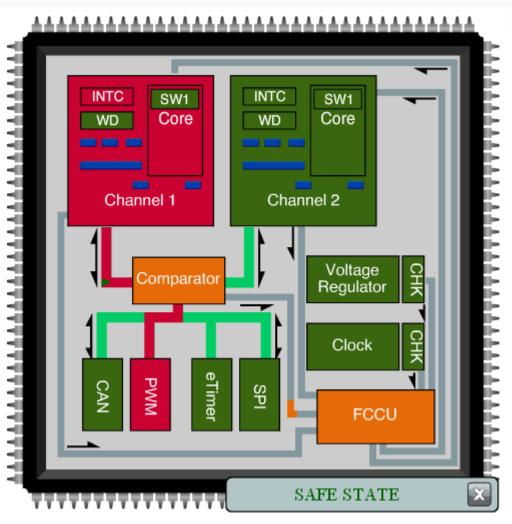

# Single-Chip Dual Core Fault Handling

- The comparator detects that both channels show different behaviors: Core 1 does not write to PWM where Core 2 does

- Comparator signals deviation to Fault Collection & Control Unit

- FCCU determines the fault is critical

- Triggers external system

- System moves itself into a safe state

## **Safety Software:**

#### IEC 61508

Safety BSP & Test, Best Practices Training, **Cert Documentation**

ISO 26262 EN 50128

Trace-powered analysis and backward execution to FIND EVERY BUG

Safety Certified Real Time Operating Systems, and Middleware

Safety qualified development tools and optimizing compilers

JTAG and Trace Probes

# **INTEGRITY Real-Time Operating System**

- Unique real-time operating system architecture

- · Separation kernel architecture

- Partition scheduling / resource guarantees

- Advanced multicore/multiprocessor support

- Single-Core, AMP, SMP

- Safely consolidate software on same processor

- The most highly certified RTOS in embedded industry

- Common Criteria EAL 6+, highest software security certification in world

- IEC-61508 SIL3 for industrial

- CENELEC EN50128 for railway

- DO-178B Level A for avionics

- FDA Class II, III approvals for medical

- Extensive middleware and ecosystem

- · Networking, routing, graphics and much more

- Open platform support

- POSIX conformant, BSD sockets, upgradeable and flexible

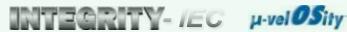

# ...TEGRITY Unique Architecture

### Separation Kernel Architecture

- Separation kernel technology

- User-defined brick wall partitioning

- Contains errors & attacks

- Isolates stack and application

- Guaranteed resource allocation

- Access control between partitions

Separation kernel enables far-reaching benefits for customer's functional safety software

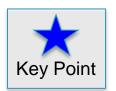

## μ-velOSity RTOS Highlights

- Royalty-free

- Delivered in source code

- Simple native API

- Fits in under 5 KB of ROM

- Boots in less than 1,500 instructions

- Integrated middleware support

- Full TCP/IPv4/v6 with IP Apps

- MS/DOS file system with FLASH wear leveling

- USB device with Mass Storage Class

- PEG Embedded graphics

- Upward compatible API with INTEGRITY

- Integration with Green Hills bestin-class MULTI Tools

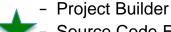

### **MULTI Integrated Development Environment**

# Debug, Analyze and Optimize Embedded Projects

- Optimizing C/C++ /EC++ cross compiler and toolchain

- \*

- Multicore, multithread source level debugger

- OS-Aware, Run-Mode, Stop-Mode Debugging

- Run-time Error Detection & Memory Leak Detection

- 4

- Instruction Set Simulator

- Trace-assisted TimeMachine & Path Analyzer

- Code Coverage Analysis

- Performance Profiler

- \*

- Flash programming

- DoubleCheck® Source Code Analyzer

- The MathWorks™ Link MU Integration

- Debug 3rd Party RTOS (VxWorks, Linux, homegrown)

### **Better Managed Embedded Projects**

- Source Code Editor

- MISRA C Checker safe code checker

### Safety Qualified version of MULTI in Q3

- ISO 26262

- IEC 61508

- EN 50128

# Flexible Solutions For PX Customer Requirements

| General Purpose Platform                                              | IEC                                                              |  |  |  |

|-----------------------------------------------------------------------|------------------------------------------------------------------|--|--|--|

| INTEGRITY RTOS                                                        | Pre-certified INTEGRITY RTOS for                                 |  |  |  |

| or<br>u-velOSity RTOS                                                 | IEC 61508 SIL3 (Industrial) and CENELEC EN 50128 SWIL4 (Railway) |  |  |  |

| Extensive middleware including flash programming, USB, and more       |                                                                  |  |  |  |

| MULTI multicore debugging, MISRA C Wizard, source code analysis tools |                                                                  |  |  |  |

|                                                                       | Certified code generation tools                                  |  |  |  |

| Record-breaking optimizing compilers                                  |                                                                  |  |  |  |

| TimeMachine reverse execution debugging and profiling                 |                                                                  |  |  |  |

| Green Hills Probe and SuperTrace Probe                                |                                                                  |  |  |  |

| Training and services                                                 | Certification services for design, safety                        |  |  |  |

|                                                                       | BSP development, and certification strategies                    |  |  |  |

# Flexible Solutions For PX Customer Requirements

| General Purpose Platform                                              | Industrial Safety Platform                                                             |  |  |  |  |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|--|

| INTEGRITY RTOS                                                        | Pre-certified INTEGRITY RTOS                                                           |  |  |  |  |

| or                                                                    | or                                                                                     |  |  |  |  |

| u-velOSity RTOS                                                       | Certifiable u-velOSity                                                                 |  |  |  |  |

| Extensive middleware including flash programming, USB, and more       |                                                                                        |  |  |  |  |

| MULTI multicore debugging, MISRA C Wizard, source code analysis tools |                                                                                        |  |  |  |  |

|                                                                       | Safety Qualified tool chain                                                            |  |  |  |  |

| Record-breaking optimizing compilers                                  |                                                                                        |  |  |  |  |

| TimeMachine reverse execution debugging and profiling                 |                                                                                        |  |  |  |  |

| Green Hills Probe and SuperTrace Probe                                |                                                                                        |  |  |  |  |

| Training and services                                                 | Certification services for design, safety BSP development, certification documentation |  |  |  |  |

### **PX Solutions from Green Hills**

| Product<br>Family | MULTI<br>Toolchain +<br>TimeMachine +<br>Probes | RTOS                                 | Functional Safety Solution                                  |                |                                                                              |

|-------------------|-------------------------------------------------|--------------------------------------|-------------------------------------------------------------|----------------|------------------------------------------------------------------------------|

|                   |                                                 |                                      | Qualified*<br>MULTI<br>Toolchain<br>IEC61508 &<br>ISO 26262 | Preferred RTOS | Safety BSP, Best Practices Training, Life Cycle Data, Risk Management Report |

| PXR40             | <b>✓</b>                                        | u-velOSity                           | <b>~</b>                                                    | u-velOSity     | ~                                                                            |

| PXN20             | V                                               | u-velOSity<br>INTEGRITY              | <b>&gt;</b>                                                 | INTEGRITY-IEC  | <b>&gt;</b>                                                                  |

| PXD10             | <b>✓</b>                                        | u-velOSity                           | <b>~</b>                                                    | u-velOSity     | ~                                                                            |

| PXD20             | V                                               | u-velOSity<br>INTEGRITY <sup>1</sup> | V                                                           | INTEGRITY-IEC  | ~                                                                            |

| PXS20             | <b>V</b>                                        | u-velOSity                           | <b>✓</b>                                                    | u-velOSity     | V                                                                            |

| PXS30             | V                                               | u-velOSity<br>INTEGRITY              | <b>&gt;</b>                                                 | INTEGRITY-IEC  | <b>✓</b>                                                                     |

(1) Port to INTEGRITY per customer demand

# Green Hills Platform for Industrial Safety for PX

### Platform Overview

Green Hills Platform for Industrial Safety is a complete solution for creating safe, reliable, secure industrial embedded systems.

- For industrial control & automation, automotive, rail and nuclear industries

- 2. Pre-certified partition architecture RTOS for highest safety levels

- 1. IEC 61508 SIL3 (Industrial)

- 2. CENELEC EN 50128 SWIL4 (Railway)

- Certifiable lightweight and simple u-velOSity RTOS

- 4. Extensive middleware

- 5. Integrated development tools for the complete lifecycle

- 6. Certified code generation tools

- 7. Consulting for Safety BSP, Best Practices Training, Life Cycle Data, Risk Management Report

# **Safety Software**

Sciopta: Safe RTOS

- Multi tasking, high-performance real time safety kernel

- TÜV certified IEC61508 at Safety Integrity Level 3

- High-value diagnostic test functions for all kernel internal data

- Direct Message Transferring for increased safety

### Safety Support: Safety Manual

- Functional safety concept

- Description of safety offering of the device

- Functional Safety Requirements on system level

- Description of software mechanisms

- Description of required functions by external hardware

- Basic interaction with complementary Freescale products

- Failure rates and FMEDA

- Introduction to FMEDA and presentation of key values

- Provisions against dependent failures

- Code examples / pseudo-code

- Exemplification of selected software interactions through code fragments

# Lailure Mode, Effect and Diagnostic Analysis

- FMEDA

- Processing units

- Power supply

- Clock

- Non-volatile memory

- Volatile memory

- Raw failure rates

- Digital I/O

- Analogue I/O

- External communication

- => for system level analysis

# Freescale Product Longevity Program

Freescale formally offers many devices for a minimum of 10 or 15 years from the time of launch

Participating Freescale products and program terms are listed at

www.freescale.com/productlongevity

### **PXS Software and Tools**

Full-featured, scalable, proven RTOS and middleware

MULTI IDE: Multicore development & verification, optimized compilers, MISRA C error checking

Safe RTOS: IEC 61508 SIL 3 Certified

### **RAppID**

Toolbox w/Simulink

PinWizard

Init Tool

- Model-based design

- Configuring function assignment to pins

- Initialization setup

### **FreeMASTER**

Real-time debugging tool

### **CodeWarrior**

- Build, debug and flash tools

- Software analysis

- Kernel-aware debug

# Series Tower Boards

### TWR-PXS20

MSRP: \$139 Available: Now

### TWR-PXD10

MSRP: \$139 Available: Now

### TWR-PXR40

MSRP: \$249 Available: Now

### TWR-PXS30

MSRP: \$219 Available: Now

### TWR-PXD20

MSRP: \$169 Available: Now

### TWR-PXN20

MSRP: \$219 Available: Now

### IEC 60730 Explained

- The Underwriters Laboratory (UL) has adopted IEC 60730 for certifying consumer devices and industrial products with automatic controls, e.g. appliances or HVAC systems. UL1998, Software in Programmable Components, specifies "detection of all single bit errors." This means microcontrollers must detect faults and force motors and systems to a safe state if the fault is not corrected.

- This session will explain the IEC 60730 standard, how it can impact your next design, and how Freescale can help you quickly gain 60730 compliance.

## IEC 60335-1 (IEC 60730-1)

- IEC 60335-1 Household and similar electrical appliances Safety-Part 1. General Requirements.

- Compliance safety requirements for large appliance manufacturers.

- IEC 60335-1 Annex R Software Evaluation

- Software shall be evaluated in accordance with the following clauses of Annex H of IEC 60730-1, as modified below ...

- IEC 60730-1 Annex H Requirements for electronic controls.

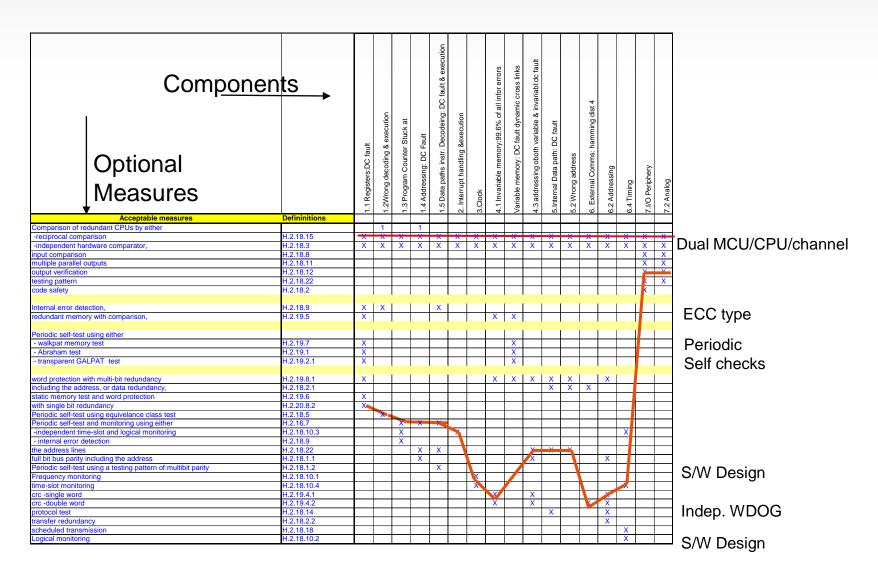

- This chapter centres around Table H.11.12.7

- IEC 60730-1 Annex H Table H.11.12.7

- Discusses the various embedded "components" that have to be tested to comply for class

B and class C electronic controls.

- Provides optional "measures" that are required to ensure reliable and safe operation of the embedded "component".

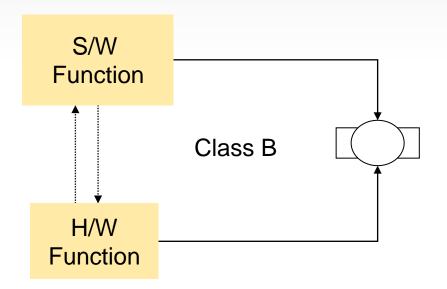

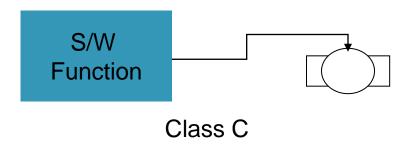

#### **IEC 60730 Classification of Appliances**

Class A are products with no feature/function that can harm a human being.

#### Class B

- IEC 60730-1: Control functions intended to prevent unsafe operation of the controlled equipment. Examples are: thermal cut-offs and door locks for laundry equipment.

- IEC 60335-1: Software that includes code intended to prevent hazards if a fault, other than a software fault, occurs in the appliance

#### Class C

- IEC 60730-1: Control functions which are intended to prevent special hazards (e.g. explosion of the controlled equipment). Examples are: automatic burner controls and thermal cut-outs for closed water heater systems (unvented).

- IEC 60335-1: Software that includes code intended to prevent hazards without the use of other protective devices.

## **Example Hazard: Overheating of Motor**

Hardware PTC monitor temp Software also monitors motor current. If one function fails, the other ensures safe operation

Class B – A fault occurring in a safety-critical software routine will not result in a hazard due to another software routine or redundant hardware intervening.

Software only monitors motor current.

If function fails, then hazard will occur.

Need more thorough diagnostics to ensure the software function is working reliably

Class C – A fault occurring in a safety-critical software routine will result in a hazard.

### **60730 Class B Components**

|    | Class B 60730 Components required to be                | Fault/error                             |

|----|--------------------------------------------------------|-----------------------------------------|

|    | tested on Electronic Control (see Table H.11.12.7)     |                                         |

| 1  | 1.1 CPU Registers                                      | Stuck at                                |

| 2  | 1.3 CPU Program Counter                                | Stuck at                                |

| 3  | 2.Interrupt Handling & Execution                       | No Interrrupt or too frequent interrupt |

| 4  | 3. Clock                                               | Wrong frequency                         |

| 5  | 4.1 Invariable memory                                  | All single bit faults                   |

| 6  | 4.2 Variable memory                                    | DC fault                                |

| 7  | 4.3 addressing (relevant to variable/invariable memory | Stuck at                                |

| 8  | 5. Internal data Path                                  | Stuck at                                |

| 9  | 5.2 Addressing                                         | Wrong addr                              |

| 10 | 6 External Communications                              | Hamming Distance 3                      |

| 11 | 6.3 Timing                                             | Wrong point in time/sequence            |

| 12 | 7 I/O Periphery                                        | Fault conditions specified in H.27      |

| 13 | 7.2.1 Analog A/D & D/A Converters                      | Fault conditions specified in H.27      |

| 14 | 7.2.2 Analog multiplexor                               | Wrong adressing                         |

Appliance manufacturers are required to implement "measures" to ensure that the above components are working reliably.

#### **Class B Test Matrix**

| IEC 60730 CLASS B                                           | Components    | Registers Stuck at: | Program Counter stuck at | Interrupt handling and execution | clock | Invaraible Memory | Varaible memory | addressing Stuck at | Internal data path Stuck at | Addressing Wrong address | Hamming Distance 3 | Timing | Wrong sequence | Input/Output Periphery |              |

|-------------------------------------------------------------|---------------|---------------------|--------------------------|----------------------------------|-------|-------------------|-----------------|---------------------|-----------------------------|--------------------------|--------------------|--------|----------------|------------------------|--------------|

| Acceptable measures                                         | Defininitions |                     |                          |                                  |       |                   |                 |                     |                             |                          |                    |        |                |                        |              |

| Comparison of redundant CPUs be either                      | Dominione     |                     |                          |                                  |       |                   |                 |                     |                             |                          |                    |        |                |                        | _            |

| reciprocal comparison,                                      | H.2.18.15     |                     |                          |                                  |       |                   |                 | Х                   |                             |                          |                    | Х      |                |                        | Dua          |

| independent hardware comparator,                            | H.2.18.3      |                     |                          |                                  |       |                   |                 | Х                   |                             |                          |                    | X      |                |                        |              |

| full bus redundancy.                                        | H.2.18.1.1    |                     |                          |                                  |       |                   |                 | X                   |                             |                          |                    |        |                |                        |              |

| Tall Sacrodaliaality!                                       |               |                     |                          |                                  |       |                   |                 |                     |                             |                          |                    |        |                |                        |              |

| Word protection with single bit redundancy                  | H.2.19.8.2    | Х                   | X                        |                                  |       | /X                | Х               | Х                   | Х                           | X                        |                    |        |                |                        | EC           |

| Word protection with multi-bit redundancy including address | H.2.19.8.1    |                     | $\neg \top$              |                                  |       |                   |                 |                     | Х                           |                          | X                  |        |                |                        | EC           |

|                                                             |               |                     |                          |                                  | /     |                   |                 |                     |                             |                          |                    |        |                |                        |              |

| Frequency monitoring                                        | H.2.18.10.1   |                     |                          |                                  | /x    |                   |                 |                     |                             |                          |                    |        |                |                        |              |

| Time-slot and logical monitoring,                           | H.2.18.10.3   |                     |                          |                                  |       |                   |                 |                     |                             |                          |                    | X      |                |                        | Ind          |

| Independent time-slot monitoring or                         | H.2.18.10.4   |                     | Х                        | X                                | Х     |                   |                 |                     |                             |                          |                    | Х      | X              |                        | IIIu         |

| Logical monitoring of the program sequence.                 | H.2.18.10.2   |                     | Х                        |                                  |       |                   |                 |                     |                             |                          |                    |        | Х              |                        |              |

| Transfer redundancy                                         | H.2.18.2.2    |                     |                          |                                  |       |                   |                 |                     |                             |                          | Х                  |        |                |                        | S/V          |

| Protocol test                                               | H.2.18.14     |                     |                          |                                  |       |                   |                 |                     |                             |                          |                    |        |                |                        | <b>O</b> , . |

| Scheduled transmission.                                     | H.2.18.18     |                     |                          |                                  |       |                   |                 |                     |                             |                          |                    | X      | X              |                        |              |

|                                                             |               |                     |                          |                                  |       |                   |                 |                     |                             |                          |                    | /      | - 11.          |                        |              |

| Periodic self-test                                          | H.2.16.6      |                     |                          |                                  |       |                   |                 |                     |                             |                          |                    |        |                |                        |              |

| Static memory test                                          | H.2.19.6      | Х                   | X                        |                                  |       |                   | Ä               |                     |                             |                          |                    |        |                |                        | D            |

| Periodic modified checksum;                                 | H.2.19.3.1    |                     |                          |                                  |       | X/                |                 |                     |                             |                          |                    |        |                |                        | Per          |

| Multiple checksum,                                          | H.2.19.3.2    |                     |                          |                                  |       | X                 |                 |                     |                             |                          |                    |        |                |                        | Sel          |

| Periodic CRC-single word,                                   | H.2.19.4.1    |                     |                          |                                  |       |                   |                 | X                   | Х                           |                          | <b>X</b>           |        |                |                        |              |

| Periodic CRC double word                                    | H.2.19.4.2    |                     |                          |                                  |       |                   |                 | X                   | Х                           |                          |                    |        |                |                        |              |

| testing pattern                                             | H.2.18.22     |                     |                          |                                  |       |                   |                 | Х                   | X                           | Х                        |                    |        |                |                        |              |

|                                                             |               |                     |                          |                                  |       |                   |                 |                     |                             |                          |                    |        |                |                        | Pre          |

| Functional test                                             | H.2.16.5      | Х                   | Х                        | Х                                |       |                   |                 |                     |                             |                          |                    |        |                |                        |              |

| Plausibility check                                          | H.2.18.13     |                     |                          |                                  |       |                   |                 |                     |                             |                          |                    |        |                | X                      |              |

Dual MCU/CPU

CC type

Indep. WDOG

S/W Design

Periodic Self checks

Pre-application code

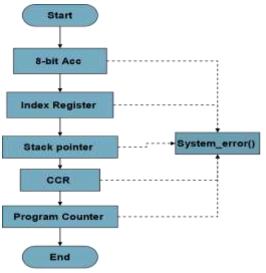

### **CPU Registers Stuck At**

- Functional test H.2.16.5: A single channel structure in which test data is introduced to the functional unit prior to its operation.

- Periodic self-test H.2.16.6: A single channel structure in which components of the control are periodically tested during operation.

using either:

- Static memory test H.2.19.6: A fault/error control technique which is intended to detect only static errors.

- Word protection with single bit redundancy H.2.19.8.2: A fault/error control technique in which a single bit is added to each word in the memory area under test and saved, creating either even or odd parity. As each word is read, a parity check is conducted.

Using #0x55 and #0xAA data Check each CPU register for "stuck at"

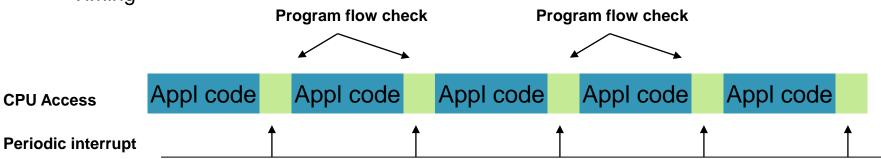

#### **Time Slot Monitoring**

- Time-slot monitoring for H.2.18.10.4: A fault/error control technique in which timing devices with an independent time base are periodically triggered in order to monitor the program function and sequence. An example is a watchdog timer.

- Covers checking and verifying of the following components:

- CPU program counter

- Interrupt handling

- Clock

- External communications

- Timing

Time-slot monitoring; a periodic check on program code flow

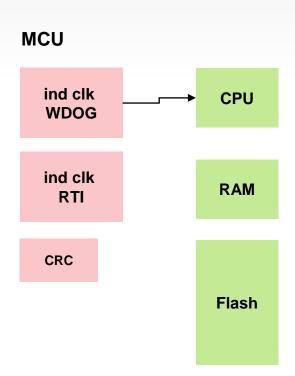

A periodic interrupt, e.g. timer overflow, interrupts the application periodically, and within the ISR some checks are made.

#### **Time Slot Monitoring**

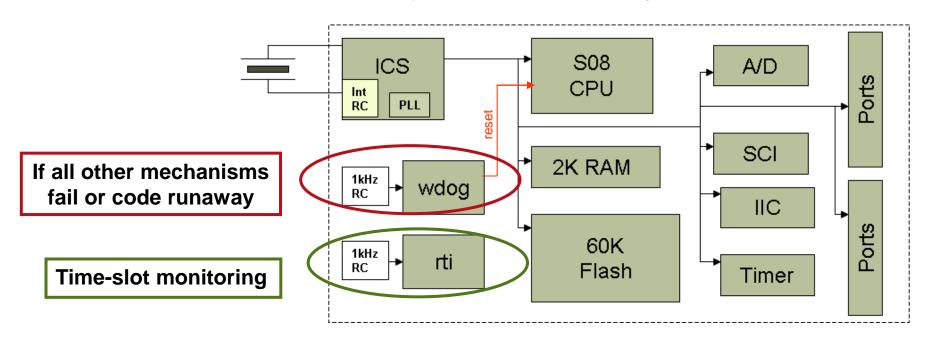

- Watchdogs should and must be deployed as the backup if all other safety mechanisms fail and/or there is code runaway.

- Not really designed for periodic interrupts to execute time slot monitoring.

- A better feature is an "independently clock" timer module, e.g. S08AC60 RTI.

Block diagram of Freescale MC9S08AC60 microcontroller

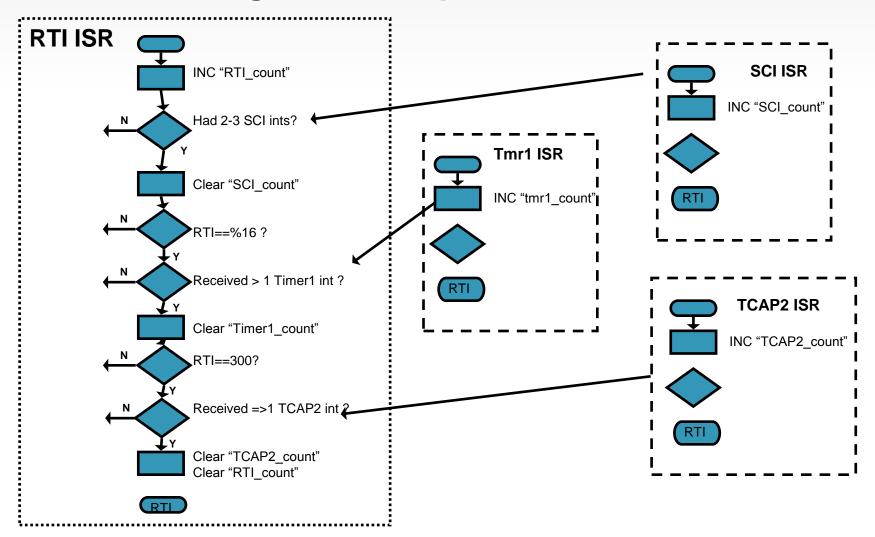

### **Token Passing: Program Flow**

- A simple form of token passing is that you deploy a variable in RAM called COUNTBYTE and for each significant function you increment this COUNTBYTE by 1.

- On the knowledge of how long the program takes to execute these various functions, then the COUNTBYTE can be read within the ISR and compared to previous captured values.

- Caution: Within each software function it is not recommended that you increment the COUNTBYTE by a certain value, but actually set the COUNTBYTE to a fixed value.

- On real time embedded systems interrupts can occur at any random time and therefore are more difficult to monitor along with the program flow as described above. Therefore only the frequency of interrupts can be monitored then checked within the same periodic ISR routine.

| F{11}           | F{12}           | F{13}           | Check<br>flow |

|-----------------|-----------------|-----------------|---------------|

| COUNTBYTE=0x11; | COUNTBYTE=0x12; | COUNTBYTE=0x13; |               |

If (COUNTBYTE < (previousCOUNTBYTE+2)) Error;

If (COUNTBYTE > (previousCOUNTBYTE+6)) Error;

/\* program flow OK \*/

previousCOUNTBYTE = COUNTBYTE;

# **Token Passing on Interrupts**

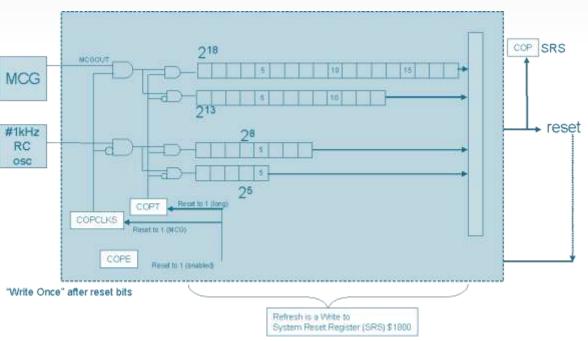

# **Independent Clocked Watchdog**

S08AC60 watchdog using 1 Khz RC oscillator is independent of CPU clock source

Providing reliable protection against clock faults (too fast/slow, stuck clock) and code runaway

Watchdog must provide a asynchronous reset to all peripherals and input/output ports

A timeout test should be initiated after power on reset, prior to running application code

### **Invariable Memory: All Single Bits Faults**

Periodic modified checksum, H.2.19.3.1: A fault/error control technique in which a single word representing the contents of all words in memory is generated and saved. During self test, a checksum is formed from the same algorithm and compared with the saved checksum. This technique recognizes all the odd errors and some of the even errors.

#### Or

Multiple checksum, H.2.19.3.2: A fault/error control technique in which separate words

representing the contents of the memory areas to be tested are generated and tested. During

self test, a checksum is formed from the same algorithm and compared with the saved

checksum for that area. This technique recognizes all odd errors and some of the even

errors.

#### Or

Word protection with single bit redundancy H.2.19.8.2

A CRC (16-bit) signature of the invariable memory is the preferred method of ensuring there are no single faults.

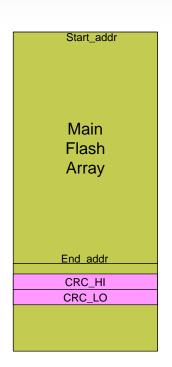

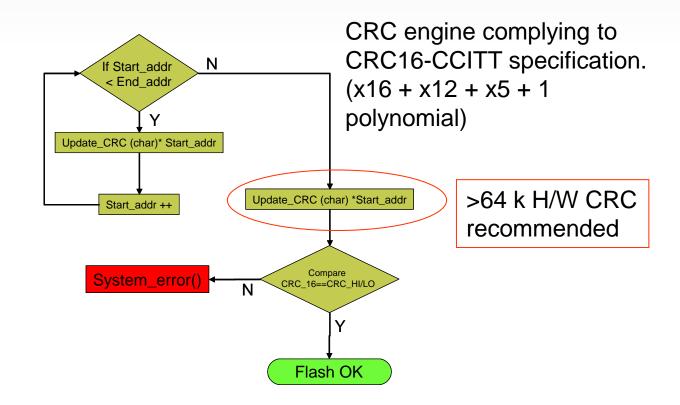

#### Flash CRC Test

#### Note:

It is recommended that one CRC 16-bit signature is reliable for detecting single bit faults flash blocks < 48 Kbytes. Large flash arrays will require multiple CRC signatures.

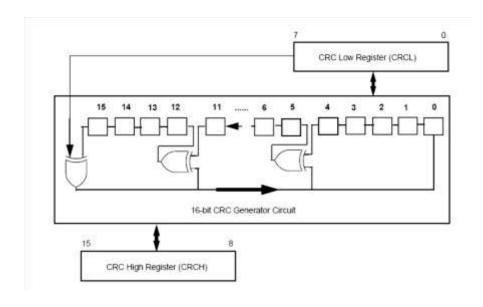

# Flash CRC Test: Hardware Implementation

CRC engine complying to CRC16-CCITT specification. (x16 + x12 + x5 + 1 polynomial).

One byte shifted through CRC in 1-CPU cycles.

~ 15x faster than software implementation on an 8-bit core.

Deployed on HCS08ACxx and MCF51ACxx devices.

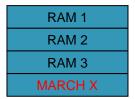

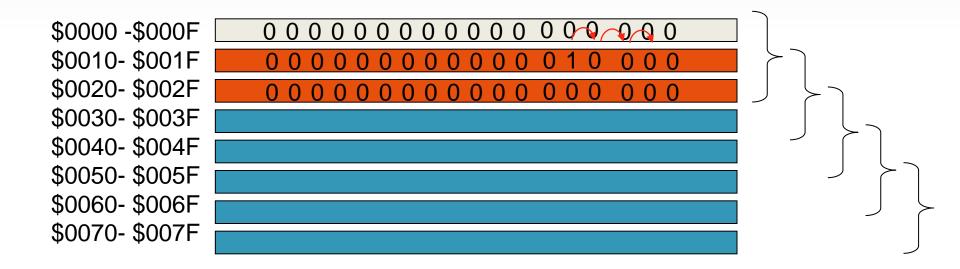

#### Variable Memory: DC fault

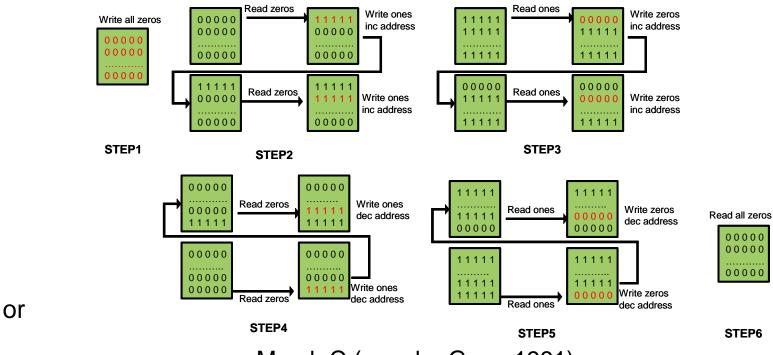

Periodic static memory test H.2.19.6: A fault/error control technique which is intended to detect only static errors

March C (van der Goor, 1991)

Word protection with single bit redundancy H.2.19.8.2 (hardware error code correction)

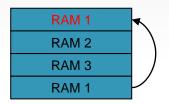

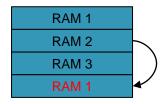

#### March X Pattern

March X pattern is a subset of the March C pattern, which detects the majority of failure mechanisms of the March C but with a faster execution time.

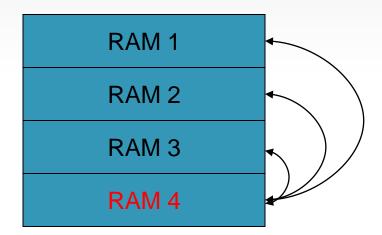

#### **Transparent March**

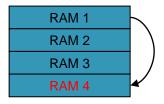

- Split RAM into four segments

- Fourth segment is "shadow"

RAM used to temporarily store

other segments variables until

March test completed.

- At a convenient time, complete the following:

- RAM 1 copy to RAM 4

- Verify copy is successful

- Deploy MARCH test on RAM 1

- Copy RAM 4 to RAM 1

- Verify copy is successful

- Deploy normal application code

### Making "Destructive" into "Transparent"

| RAM 1 |  |

|-------|--|

| RAM 2 |  |

| RAM 3 |  |

| RAM 4 |  |

Segment RAM

Redundant RAM segment

Copy RAM4 to RAM1. Verify data copied.

March X on RAM4

Copy RAM2 to RAM4. Verify data copied.

Copy RAM1 to RAM4. Verify data copied.

| RAM 1   |

|---------|

| MARCH X |

| RAM 3   |

| RAM 2   |

March X on RAM2

| MARCH X |

|---------|

| RAM 2   |

| RAM 3   |

| RAM 1   |

March X on RAM1

#### Class B Memory Address and Data Path

4.3 Addressing

(relevant to variable and invariable memory) stuck at

- 5. Internal data path stuck at

- 5.2 Addressing: Wrong address

These components intended for external memory microprocessor based designs. These components are tested by other measures on single chip microcontrollers.

Class B 60730 Components required to be

1.1 CPU Registers

4.1 Invariable memory

4.2 Variable memory

5. Internal data Path

6 External Communications

7.2.2 Analog multiplexor

7.2.1 Analog A/D & D/A Converters

5.2 Addressing

7 I/O Periphery

6.3 Timing

Clock

1.3 CPU Program Counter

2.Interrupt Handling & Execution

ested on Electronic Control (see Table H.11.12.7)

4.3 addressing (relevant to variable/invariable memory

Fault/error

Wrong frequency

All single bit faults

Hamming Distance 3

Wrong adressing

Wrong point in time/sequence

Fault conditions specified in H.27

Fault conditions specified in H.27

No Interrrupt or too frequent interrupt

Stuck at Stuck at

DC fault Stuck at

Stuck at

Wrong addr

# Laternal Communications

#### **Hamming Distance 3**

- Word protection with multi-bit redundancy including address H.2.19.8.1.

Or

- CRC-single word, H.2.19.4.1: A fault/error control technique in which a single word is generated to represent the contents of memory. During self test the same algorithm is used to generate another signature word which is compared with the saved word. The technique recognizes all one-bit, and a high percentage of multibit, errors.

Or

Transfer redundancy H.2.18.2.2: A form of code safety in which data is transferred at least twice in succession and then compared. This technique will recognize intermittent errors.

Or

Protocol test H.2.18.14: A fault/error control technique in which data is transferred to and from computer components to detect errors in the internal communications protocol.

### **Plausibility Check**

- 7. I/O Periphery: Fault conditions specified in H.27

- 7.2.1 A/D & D/A converters: Fault conditions specified in H.27

- 7.2.2 Analog Multiplexer: Wrong addressing

Plausibility check H.2.18.13: A fault/error control technique in which program execution, inputs or outputs are checked for inadmissible program sequence, timing or data. Examples are the introduction of an additional interrupt after the completion of a certain number of cycles or checks for division by zero.

**I/O Periphery**: For digital outputs, checks can be made to verify no short circuits or open circuits between adjacent signals and power supply. Manufacturers will utilize redundant input pins on MCUs to check on key signal pins that a short or open-circuit would lead to a hazard.

**For analogue signals A/D and D/A** checks on the boundary limits of the absolute value should be made. For example, an input A/D pin should only see a small range of values with the full voltage conversion range, any value outside would be ignored in software.

**Analogue multiplexers**: Today most manufacturers will need to have the capability to provide a known d.c. value to all input A/P pins. This allows test software to check the multiplexer is working. Future analogue multiplexers should provide additional redundant channels on each pin so that a comparison between two channels can be made to verify that the multiplexer is working as expected.

### Class B Generic MCU Requirements Summary

#### Software

- CPU register "SA faults" test

- March C and MARCH X (transparent) RAM test

- Modified checksum or CRC flash test

- Independent WDOG test

- Plausibility tests for key digital and analogue I/O signals

- Time slot monitoring of program flow and interrupt behavior

- Token passing

- Independent RTI

#### **Hardware**

- Independent clocked WDOG

- Independent real time interrupt

- Nice to have

- CRC engine for 64K+ memory devices

- Loss of clock/lock reset

# 60730 Class C: Components to Be Tested

|    | Class C 60730 Components required to be tested on Electronic Control (see Table H.11.12.7) | Fault/error                            |

|----|--------------------------------------------------------------------------------------------|----------------------------------------|

| 1  | 1.1 CPU Registers                                                                          | DC fault                               |

| 2  | 1.3 CPU Program Counter                                                                    | Stuck at                               |

| 3  | 1.2 CPU Instruction Decoding & Execution                                                   | Wrong decoding or execution            |

| 4  | 2. Interrupt Handling & Execution                                                          | No Interrupt or too frequent interrupt |

| 5  | 3. Clock                                                                                   | Wrong frequency                        |

| 6  | 4.1 Invariable Memory                                                                      | 99.6% coverage of all info errors      |

| 7  | 4.2 Variable Memory                                                                        | DC fault & dynamic cross links         |

| 8  | 4.3 Addressing (relevant to variable/invariable memory                                     | Stuck at                               |

| 9  | 5. Internal Data Path                                                                      | Stuck at                               |

| 10 | 5.2 Addressing                                                                             | Wrong addr                             |

| 11 | 6 External Communications                                                                  | Hamming distance 4                     |

|    |                                                                                            | 3                                      |

| 12 | 6.3 Timing                                                                                 | Wrong point in time/sequence           |

| 12 | 6.3 Timing 7 I/O Periphery                                                                 |                                        |

|    |                                                                                            | Wrong point in time/sequence           |

#### Class C Test Matrix

## 1.2 Instruction Decoding And Execution

#### Acceptable measures are:

| 1.2 Instruction | Wrong decoding | rq | Comparison of redundant CPUs by either                              | Or | H.2.18.15 |

|-----------------|----------------|----|---------------------------------------------------------------------|----|-----------|

| decoding and    | and execution  |    | <ul> <li>Reciprocal comparison</li> </ul>                           |    | H.2.18.3  |

| execution       |                |    | <ul> <li>Independent hardware comparator</li> </ul>                 |    | H.2.18.9  |

|                 |                |    | Internal error detection                                            |    | H.2.18.5  |

|                 |                |    | <ul> <li>Periodic self-test using equivalence class test</li> </ul> |    |           |

IEC 60730 Class C Requirement to test Instruction Decoding & Execution.

Acceptable measure to test is:

Periodic self-test using equivalence class test

#### H.2.18.5 Equivalence Class Test

A systematic test intended to determine whether the instruction decoding and execution are performed correctly. The test data is derived from the CPU instruction specification.

Similar instructions are grouped and the input data set is subdivided into specific data intervals (equivalence classes) Each instruction within a group processes at least one set of test data, so that the entire group processes the entire test data set. The test can be formed from the following:

- Data from a valid range

- Data from invalid range

- Data from the bounds

- Extreme values and their combinations

The tests within a group are run with different addressing modes, so that the entire group executes all addressing modes.

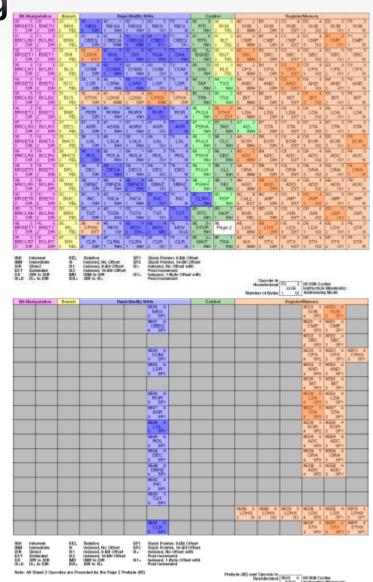

# **S08 CPU Instruction Grouping**

The S08 instructions were analysed and placed into the 6 different groups (as shown in Instruction map diagrams below):

- 1. Register/Memory Tests

- 2. Control

- 3. Read Modify Write

- 4. Branch

- 5. Bit Manipulation

- 6. Stack Pointer

#### **S08 CPU Instruction Test**

- Memory Footprint: 2148 bytes (this can be reduced if instructions are not utilised in application code)

- Execution Time: 3666 CPU BUS cycles (183.3 µs at 20 MHz)

- Reviewed, tested and certified by Tuev-Sued GmbH

- Instructions not tested (as they require hardware considerations):

- STOP WAIT BGND BIH BIL RSP SWI

## 4.2 Variable Memory

#### Acceptable measures for class C systems are:

| 4.2 Variable memory | DC fault and dynamic cross links | rq | Comparison of redundant CPUs by either  Reciprocal comparison  Independent hardware comparator, Redundant memory with comparison Periodic self-test using either  Walkpat memory test | Or<br>Or<br>Or | H.2.18.15<br>H.2.18.3<br>H.2.19.5<br>H.2.19.7 |

|---------------------|----------------------------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------|

|                     |                                  |    | <ul><li>Abraham test</li><li>Transparent GALPAT test</li></ul>                                                                                                                        | Or             | H.2.19.1<br>H.2.19.2.1                        |

|                     |                                  |    | Word protection with multi-bit redundancy                                                                                                                                             | Or             | H.2.19.8.1                                    |

- IEC 60730 Class C Requirement to test variable memory(RAM) for DC faults

- Acceptable measure to test is:

- Periodic self-test using "walkpat memory test"

#### H.2.19.7 Equivalence Class Test

#### H.2.19.7 walkpat memory test

A fault/error control technique in which a standard data pattern is written to the memory area under test as in normal operation. A bit inversion is performed on the first cell and the remaining memory area is inspected. Then the first cell is again inverted and the memory inspected. This process is repeated for all memory cells under test. A second test is conducted by performing a bit inversion of all cells in memory under test and proceeding as above.

This technique recognises all static bit errors as well as errors in interfaces between memory cells.

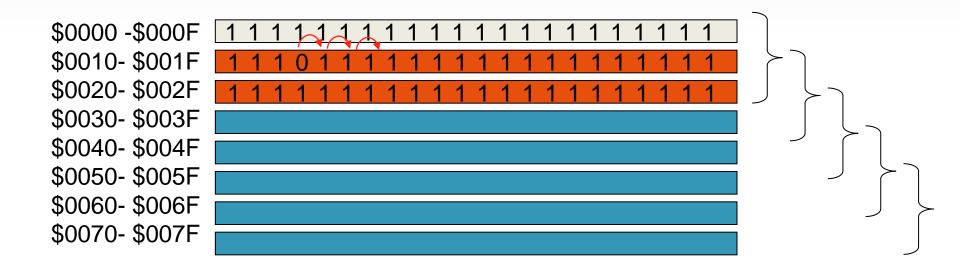

A walking 1s pattern followed by a walking 0s pattern

### Walkpat RAM Test

|             | 0x00 0x01 |          |   |   |   |   |   |   |   |   |   |   |   |   | 0x02 |   |   |   |   |   |   | 0x03 |   |   |   |   |   |   |   |   |   |   |

|-------------|-----------|----------|---|---|---|---|---|---|---|---|---|---|---|---|------|---|---|---|---|---|---|------|---|---|---|---|---|---|---|---|---|---|

| 0b0000 00xx | 0         | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0b0000 01xx | 0         | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0b0000 10xx | 0         | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0b0000 10xx | 0         | <b>♦</b> | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0b0001 00xx | 0         | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|             | 0         | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|             | 0         | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|             | 0         | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|             | 0         | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|             | 0         | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| /           | 0         | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|             | 0         | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Walkpat test demands that each adjacent cell to the written cell is checked to have the opposite state.

Two things are required to ensure speedy execution times in application:

- 1) RAM split into sizeable segments

- 2) Need to understand the RAM topology to ensure that the walking 1s pattern is testing the adjacent cells as intended.

# Walking 1s

0 0 0 When cell set to 1

0 1 0 the 8 adjacent cells to the

0 0 0 0 test cell are verified to be 0.

# NIP Walking 0s

1 1 1 When cell set to 0

1 0 1 the 8 adjacent cells to the

1 1 1 test cell are verified to be 1.

### Walking 1s RAM Test

Memory footprint: Walking 1s only: 1245 bytes

Walking1s and 0s: 2174 bytes

- Execution time for 16 byte row:

- Walking1s 12544 CPU cycles (627uS @20 Mhz)

- Walking1s+0s 27016 CPU cycles (1.35ms @20 Mhz)

- Execution time for 2048 bytes (16 bytes at a time)

- Walking 1s+0s 2.765 seconds @20 Mhz

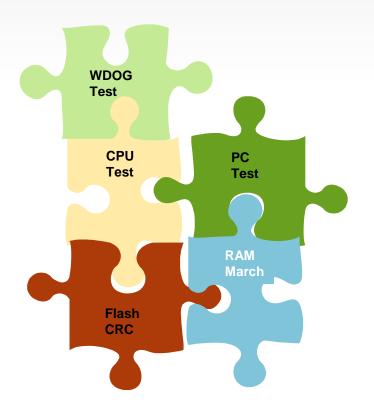

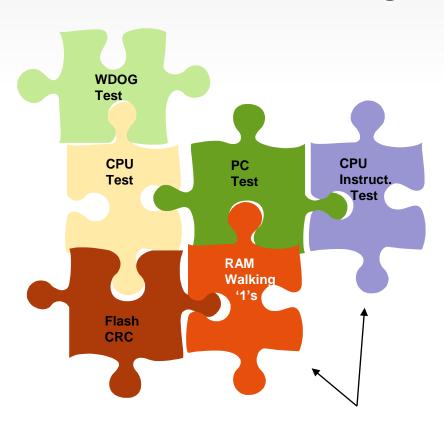

# Freescale Will Provide Pieces of the 60730 Jigsaw

Class C Routines

# **Example Roadmap: Legend Horizontal**

#### **Features** Class B Class C **Kinetis** 32-bit ColdFireV1 ColdFireV1 16-bit **DSC** DSC 8-bit **S08AC > S08P S08AC > S08P**

### Generic MCU Requirements for IEC/UL 60730

### Class B

#### **Hardware**

Independent clocked WDOG Independent real time interrupt

#### **Software**

CPU register "SA faults" test

March C and MARCH X (transparent) RAM

test

Modified checksum or CRC flash test Independent WDOG / RTI test

Plausibility tests

Time slot monitoring of program flow

and interrupt behavior

#### Class C

#### **Hardware**

Independent clocked WDOG

Independent real time interrupt

2nd CPU or RAM error correction coding

CRC engine

#### **Software**

CPU register "walkpat" test

CPU instruction set test

GALPAT/walking 1's RAM test

CRC flash test

Independent WDOG / RTI test

Plausibility tests

Time slot monitoring of program flow

and interrupt behavior

# **Safety Products**

Thank you

Tag yourself in photos and upload your own!

Session materials will be posted @ www.freescale.com/FTF Look for announcements in the FTF Group on LinkedIn or follow Freescale on Twitter