### 88MW300-88MW302

Wireless Microcontroller - IEEE 802.11n/g/b

Rev. 6 - December 9, 2020

**Product Data Sheet**

### PRODUCT OVERVIEW

The 88MW300/302 is a highly integrated, low-power WLAN Microcontroller System-on-Chip (SoC) solution designed for a broad array of smart devices for Internet of Things (IoT), wearables, accessories, Machine-to-Machine (M2M), home automation, and Smart Energy applications.

A high degree of integration enables very low system costs requiring only a single 3.3V power input, a 38.4 MHz crystal, and SPI Flash. The RF path needs only a low pass filter for antenna connection.

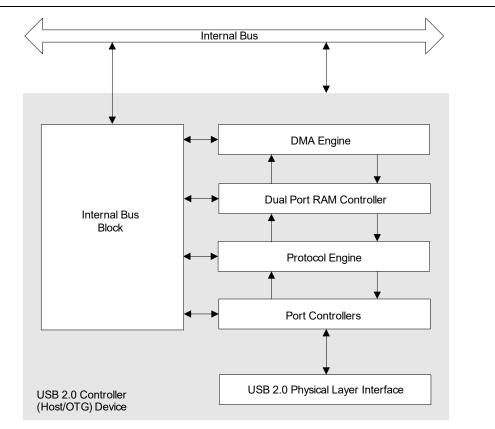

The SoC includes a full-featured WLAN subsystem powered by proven and mature IEEE 802.11b/g/n technology. The WLAN subsystem integrates a WLAN MAC, baseband, and direct-conversion RF radio with integrated PA, LNA, and transmit/receive switch. It also integrates a CPU subsystem with integrated memory to run NXP WLAN firmware to handle real time WLAN protocol processing to off-load many WLAN functions from the main application CPU.

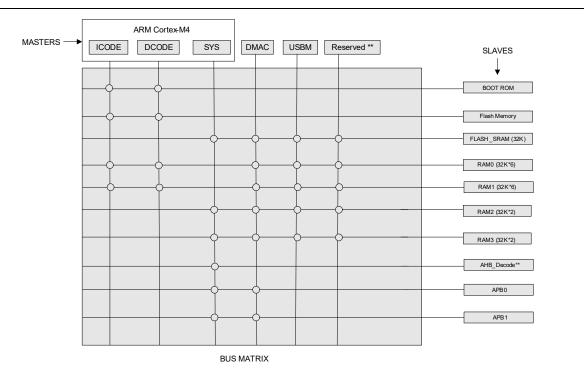

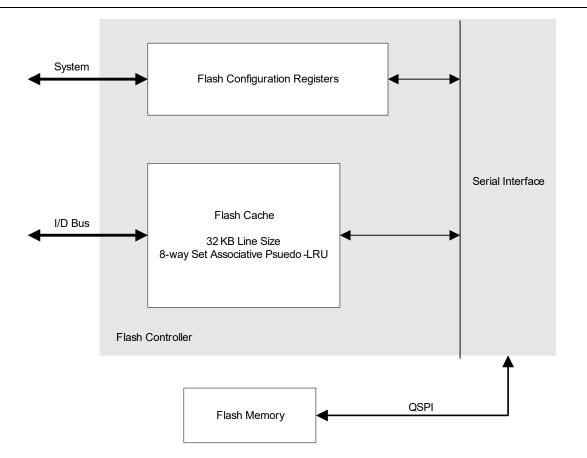

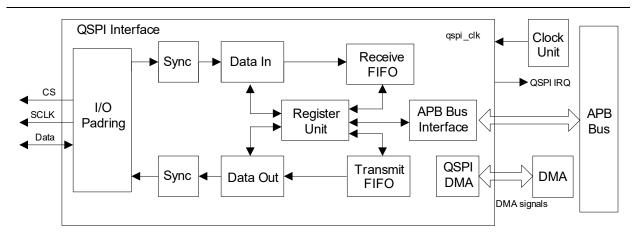

The application subsystem is powered by an ARM Cortex-M4F CPU that operates up to 200 MHz. The device supports an integrated 512 KB SRAM, 128 KB mask ROM, and a QSPI interface to external Flash. An integrated Flash Controller with a 32 KB SRAM cache enables eXecute In Place (XIP) support for firmware from Flash.

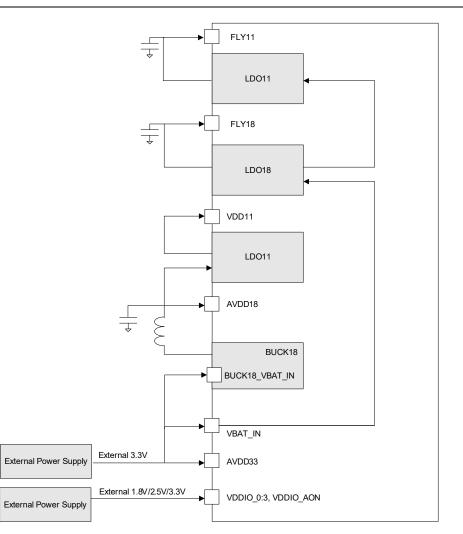

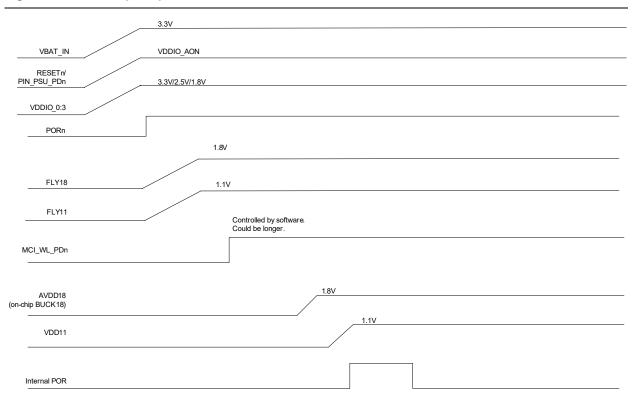

The SoC is designed for low-power operation and includes several low-power states and fast wake-up times. Multiple power domains and clocks can be individually shut down to save power. The SoC also has a high-efficiency internal PA that can be operated in low-power mode to save power. The microcontroller and WLAN subsystems can be placed into low-power states, independently, supporting a variety of application use cases. An internal DC-DC regulator provides the 1.8V rail for the WLAN subsystem.

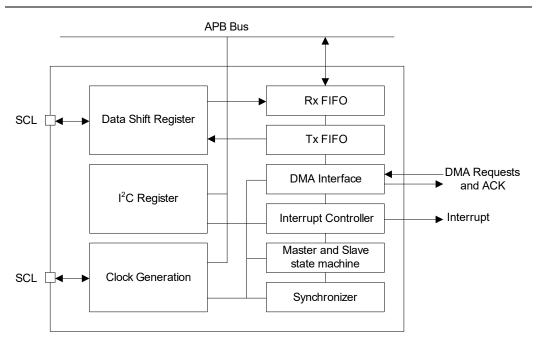

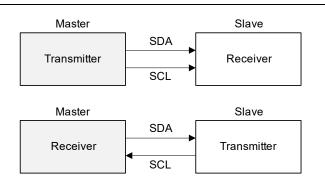

The SoC provides a full array of peripheral interfaces including SSP/SPI/I<sup>2</sup>S (3x), UART (3x), I<sup>2</sup>C (2x), General Purpose Timers and PWM, ADC, DAC, Analog Comparator, and GPIOs. It also includes a hardware cryptographic engine, a Secure Boot element, RTC, and Watchdog Timer.

The 88MW302 includes a high speed USB On-The-Go (OTG) interface to enable USB audio, video, and other applications.

A complete set of digital and analog interfaces enable direct interfacing for I/O avoiding the need for external chips. The application CPU can be used to support custom application development avoiding the need for another microcontroller or processor.

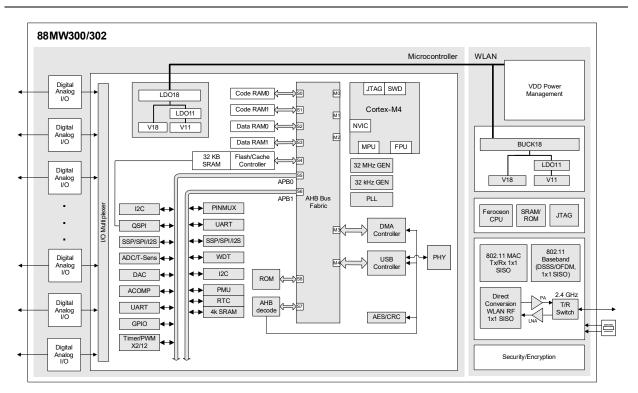

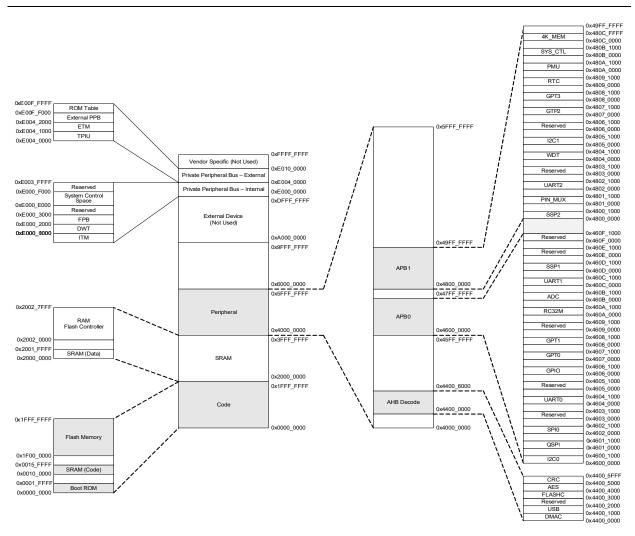

Figure 1 shows an overall block diagram of the device.

#### Figure 1: Block Diagram

#### Applications

- White goods/appliances—refrigerator, washer, dryer, oven range, microwave, dishwasher, water heater, air conditioner

- Consumer devices and accessories—toys, speakers, headset, alarm clock, gaming accessory, remote control

- Home automation—smart outlet, light switch, security camera, thermostat, sprinkler controller, sensor, door lock, door bell, garage door, security system

- Personal health devices-weighing scale, glucometer, blood pressure monitor, fitness equipment

- IoT/wearables—coffee pot, rice cooker, vacuum cleaner, air purifier, smart watch, fitness bracelet, pet monitor

- Commercial/industrial—lighting, building automation, asset management, Point of Sale (POS) sales

- Gateways—Connecting IR, sub-Gig or Legacy RF, Bluetooth Smart, ZigBee, ZWave and other radios to Wi-Fi/IP network

#### **Key Features**

- Highly integrated SoC requiring very few external components for a full system operation

- Multiple low-power modes and fast wake-up times

- Full-featured, single stream 802.11b/g/n WLAN

- High-efficiency PA with a low-power (10 dB) mode

- Cortex-M4F application CPU for applications with integrated 512 KB SRAM and 128 KB mask ROM

- Flash Controller with embedded 32 KB SRAM cache to support XIP from external SPI Flash

- Secure boot

- Full set of digital and analog I/O interfaces

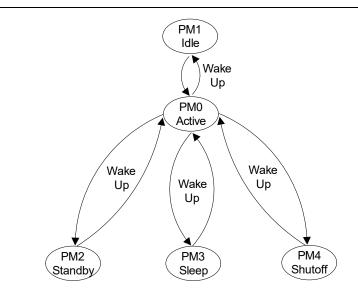

#### **Power Management**

- Power modes—active, idle, standby, sleep, shutoff, power-down

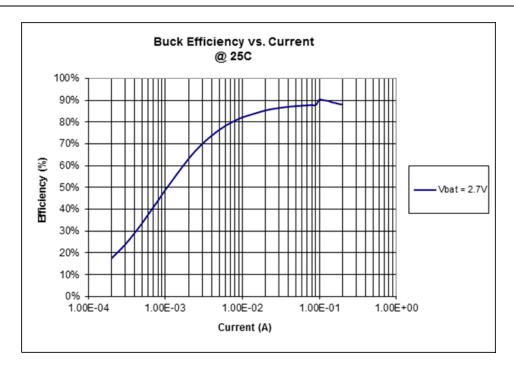

- Integrated high-efficiency buck DC-DC converter

- Independent power domains

- Brown-out detection

- Integrated POR

- Wake-up through dedicated GPIO, IRQ, and RTC

#### Package

- 88MW300—68-pin QFN, 8x8 mm

- USB OTG not supported

- 35 GPIOs

- 2 GPTs

- 88MW302—88-pin QFN, 10x10 mm

- USB OTG supported

- 50 GPIOs

- 4 GPTs

#### Table 1: Package Feature Differences<sup>a</sup>

| Feature        | 68-Pin                                                                               | 88-Pin                           |

|----------------|--------------------------------------------------------------------------------------|----------------------------------|

| GPIO           | 35 total<br>GPIO_0 to GPIO_10<br>GPIO_16<br>GPIO_22 to GPIO_33<br>GPIO_39 to GPIO_49 | 50 total<br>GPIO_0 to<br>GPIO_49 |

| USB 2.0<br>OTG |                                                                                      | 1                                |

| GPT            | 2                                                                                    | 4                                |

All I/O features are muxed on GPIOs, except WLAN RF TX/RX, USB, reference clock, and reset functionality.

#### Temperature

- Extended: -30 to 85°C

- Industrial: -40 to 85°C

- Storage: -55 to 125°C

#### Wireless

- IEEE 802.11b/g/n, 1x1 SISO 2.4 GHz and HT20

- Integrated CPU, memory, MAC, DSSS/OFDM baseband, direct conversion RF radio, encryption

- Antenna diversity

- CMOS and low-swing sine wave input clock

- Low-power with deep sleep and standby modes

- Pre-regulated supplies

- Integrated T/R switch, PA, and LNA

- Optional 802.11n features

- One Time Programmable (OTP) memory to eliminate need for external EEPROM

#### WLAN Rx Path

- Direct conversion architecture eliminates need for external SAW filter

- On-chip gain selectable LNA with optimized noise figure and power consumption

- High dynamic range AGC function in receive mode

#### WLAN Tx Path

- Integrated PA with power control

- Optimized Tx gain distribution for linearity and noise performance

#### WLAN Local Oscillator

- Fractional-N for multiple reference clock support

- Fine channel step

#### WLAN Encryption

- WEP 64- and 128-bit encryption with hardware TKIP processing (WPA)

- AES-CCMP hardware implementation as part of 802.11i security standard (WPA2)

- Enhanced AES engine performance

- AES-Cipher-Based Message Authentication Code (CMAC) as part of the 802.11w security standard

- WLAN Authentication and Privacy Infrastructure (WAPI)

- WPA3 (SAE)

#### IEEE 802.11 Standards

- 802.11 data rates of 1 and 2 Mbps

- 802.11b data rates of 5.5 and 11 Mbps

- 802.11g data rates 6, 9, 12, 18, 24, 36, 48, and 54 Mbps for multimedia content transmission

- 802.11g/b performance enhancements

- 802.11n compliant with maximum data rates up to 72.2 Mbps (20 MHz channel)

- 802.11d international roaming

- 802.11e quality of service

- 802.11h transmit power control

- 802.11i enhanced security

- 802.11k radio resource measurement

- 802.11n block acknowledgment extension

- 802.11r fast hand-off for AP roaming

- 802.11w protected management frames

- Fully supports clients (stations) implementing IEEE Power Save mode

- Wi-Fi direct connectivity

#### Microprocessor

#### Processor

- ARM Cortex-M4F, 32-bit

- 200 MHz main bus clock

#### Memory

- 128 KB ROM

- 512 KB RAM

#### **Flash Controller**

- Supports QSPI Flash devices

- Memory-mapped access to QSPI Flash devices

- 32 KB SRAM cache

#### **Digital Interfaces**

- 3x I<sup>2</sup>S stereo

- 3x SPI master/slave

- 2x I<sup>2</sup>C master/slave

- 3x UART

- 1x USB OTG 2.0, high-speed

- 1x QSPI

- Up to 50 GPIOs

- 2x wake-up pins

#### Analog

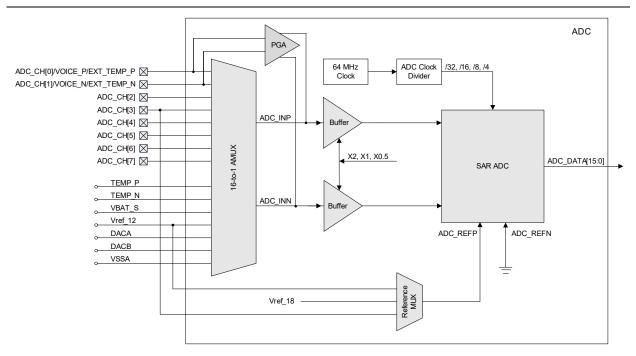

- 2-step ADC with integrated PGA and configurable resolution/speed

- 12-bit/2 MHz sample(s) for fast conversion

- 16-bit/16 kHz sample/s with voice quality

- 8 single channels or 4 differential channels

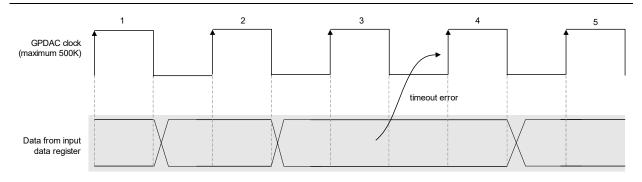

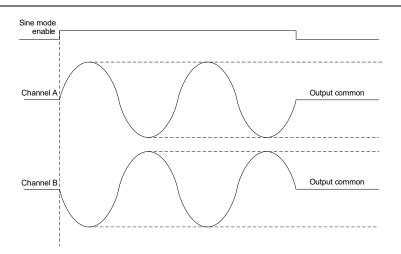

- 2-Channel or 1 differential channel DAC, 10-bit/500 ksps

- 2 Analog Comparators with programmable speed/current

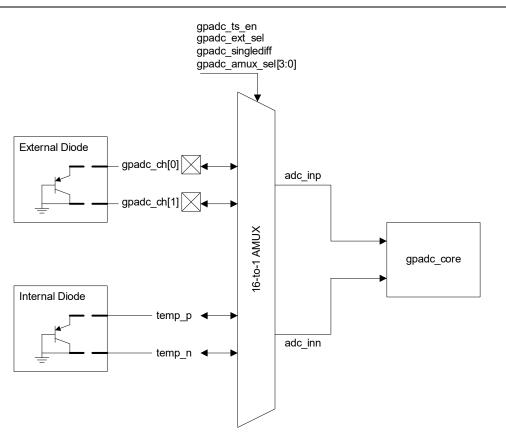

- On-die/off-chip temperature sensing and battery monitor

#### Counters/Timers/PWM

- General Purpose Timers (GPT) with LED PWM support

- Real Time Clock (RTC)

- CM4 system tick

- Watchdog Timer

# 1 Package

### 1.1 Signal Diagram

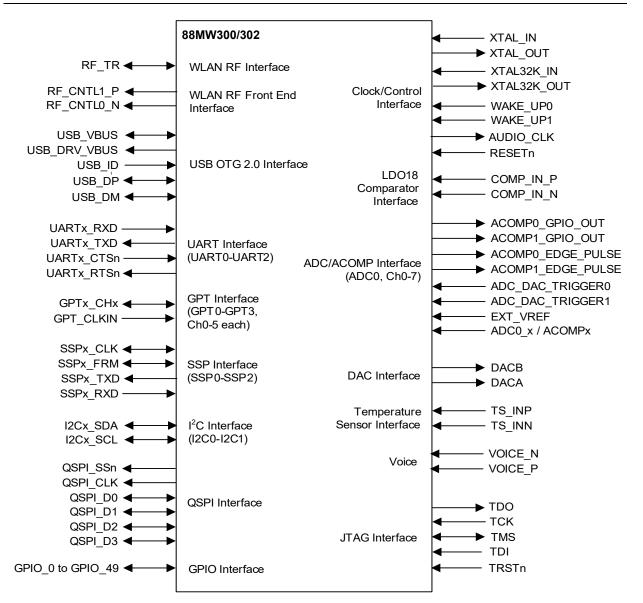

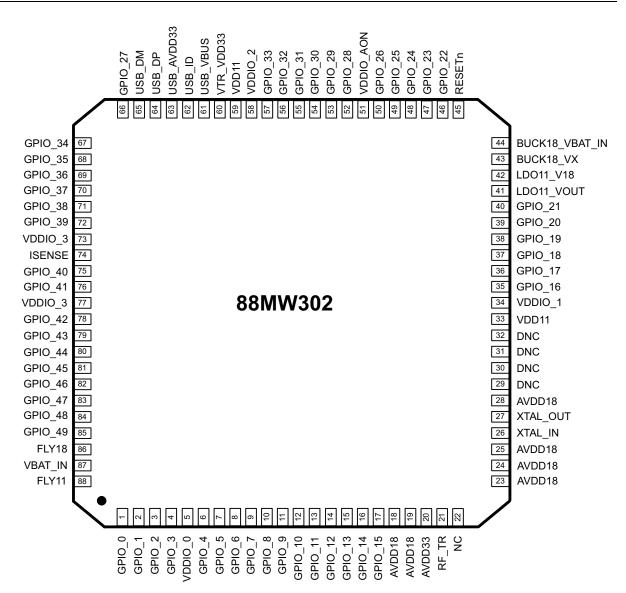

Figure 2: Signal Diagram<sup>1 2 3 4</sup>

1. Signals are muxed on dedicated pins. See Section 1.4, Pin Description, on page 11 for dedicated pin / muxed signal descriptions.

2. Some pins/signals are available on the 88-pin QFN only. See Section 1.4, Pin Description, on page 11.

3. RF\_TR, USB OTG, XTAL\_IN/OUT, and RESETn pins are dedicated. Others are muxed on GPIOs.

4. See Table 16, Power and Ground, on page 32 for power signals.

### 1.2 Pinout

### 1.2.1 Pinout—68-Pin QFN

Figure 3: Pinout—68-Pin QFN<sup>1</sup>

1. Connect pin 17 to ground.

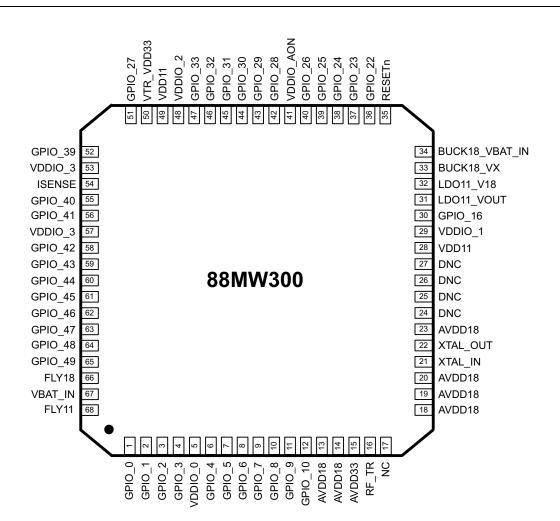

### 1.2.2 Pinout—88-Pin QFN

1. Connect pin 22 to ground.

#### 1.3 **Mechanical Drawing**

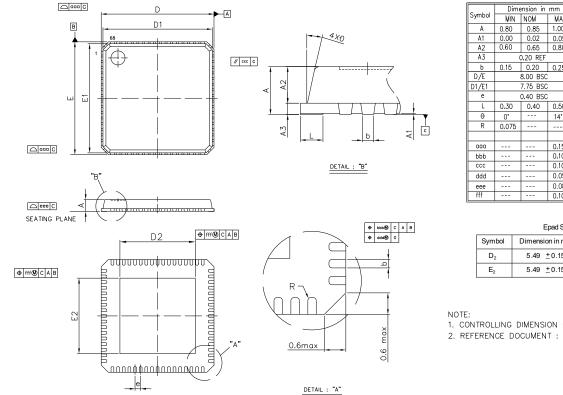

#### Mechanical Drawing—68-Pin QFN 1.3.1

Figure 5: Mechanical Drawing-68-Pin QFN

| <u> </u> |       | sinatori in |      | Dimension in inch |           |       |

|----------|-------|-------------|------|-------------------|-----------|-------|

| Symbol   | MIN   | NOM         | MAX  | MIN               | NOM       | MAX   |

| A        | 0.80  | 0.85        | 1.00 | 0.031             | 0.033     | 0.039 |

| A1       | 0.00  | 0.02        | 0.05 | 0.000             | 0.001     | 0.002 |

| A2       | 0.60  | 0.65        | 0.80 | 0.024             | 0.026     | 0.031 |

| A3       | -     | 0.20 REF    |      |                   | 0.008 REF | -     |

| b        | 0.15  | 0.20        | 0.25 | 0.006             | 0.008     | 0.010 |

| D/E      |       | 8.00 BSC    |      |                   | 0.315 BS0 | )     |

| D1/E1    |       | 7.75 BSC    | ;    |                   | 0.305 BS  | 2     |

| е        |       | 0.40 BSC    | ;    |                   | 0.016 BS0 | )     |

| L        | 0.30  | 0.40        | 0.50 | 0.012             | 0.016     | 0.020 |

| θ        | 0°    |             | 14.  | 0.                |           | 14*   |

| R        | 0.075 |             |      | 0.003             |           |       |

|          |       |             |      |                   |           |       |

| 000      |       |             | 0,15 |                   |           | 0.006 |

| bbb      |       |             | 0,10 |                   |           | 0.004 |

| CCC      |       |             | 0.10 |                   |           | 0.004 |

| ddd      |       |             | 0.05 |                   |           | 0.002 |

| eee      |       |             | 0.08 |                   |           | 0.003 |

| fff      |       |             | 0.10 |                   |           | 0.004 |

|          |       |             |      |                   |           |       |

Dimension in inch

| Epad Size      |                    |                     |  |  |  |  |  |  |

|----------------|--------------------|---------------------|--|--|--|--|--|--|

| Symbol         | Dimension in mm    | Dimension in inch   |  |  |  |  |  |  |

| D <sub>2</sub> | 5.49 <u>+</u> 0.15 | .216 <u>+</u> 0.006 |  |  |  |  |  |  |

| E <sub>2</sub> | 5.49 <u>+</u> 0.15 | .216 <u>+</u> 0.006 |  |  |  |  |  |  |

1. CONTROLLING DIMENSION : MILLIMETER 2. REFERENCE DOCUMENT : JEDEC MO-220.

Note: See Section 22.5, Package Thermal Conditions, on page 279 for electrical specifications. See Section 23.2, Package Marking, on page 302 for package marking.

Wireless Microcontroller

88MW300-88MW302

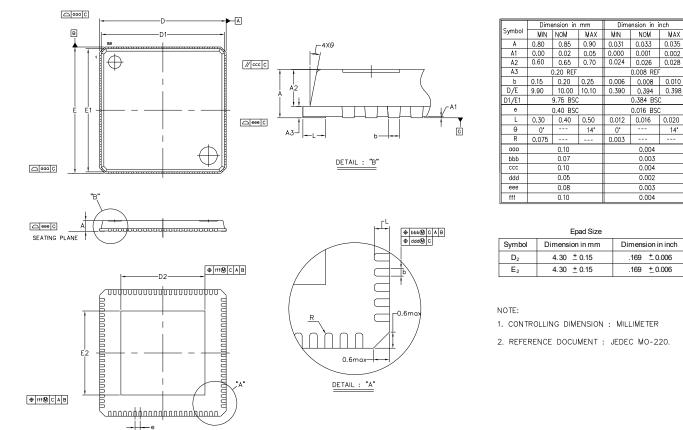

#### 1.3.2 Mechanical Drawing-88-Pin QFN

#### Figure 6: Mechanical Drawing-88-Pin QFN

Note: See Section 22.5, Package Thermal Conditions, on page 279 for electrical specifications. See Section 23.2, Package Marking, on page 302 for package marking.

Product Data Sheet

MAX

0.035

0.002

0.028

14'

## 1.4 Pin Description

| Table 2: Pin Types |                      |  |  |  |

|--------------------|----------------------|--|--|--|

| Pin Type           | Description          |  |  |  |

| I/O                | Digital input/output |  |  |  |

| 1                  | Digital input        |  |  |  |

| 0                  | Digital output       |  |  |  |

| A, I               | Analog input         |  |  |  |

| A, O               | Analog output        |  |  |  |

| NC                 | No connect           |  |  |  |

| DNC                | Do not connect       |  |  |  |

| PWR                | Power                |  |  |  |

| Ground             | Ground               |  |  |  |

#### Table 3: WLAN RF Interface

| 88-Pin | 68-Pin | Pin Name | Туре   | Supply | Description                                                                |

|--------|--------|----------|--------|--------|----------------------------------------------------------------------------|

| 21     | 16     | RF_TR    | A, I/O | AVDD18 | WLAN RF Interface (2.4 GHz Transmit/Receive)<br>Baseband input/output data |

#### Table 4: WLAN RF Front End Interface

| 88-Pin  | 68-Pin | Pin Name   | Туре | Supply  | Description                                           |

|---------|--------|------------|------|---------|-------------------------------------------------------|

| GPIO_44 |        | RF_CNTL1_P | A, O | VDDIO_3 | WLAN Radio Control 1<br>Power-down output high signal |

| GPIO_45 |        | RF_CNTL0_N | Α, Ο | VDDIO_3 | WLAN Radio Control 0<br>Power-down output low signal  |

#### Table 5: USB 2.0 OTG Interface<sup>1</sup>

NOTE: Available on 88-pin package only (88MW302)

| 88-Pin | 68-Pin | Pin Name     | Туре   | Supply     | Description                                                                                                                                                                                               |

|--------|--------|--------------|--------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 61     |        | USB_VBUS     | A, I/O |            | VBUS Selection<br>Input in device mode; unused in host mode.                                                                                                                                              |

| 62     |        | USB_ID       | A, I   | USB_AVDD33 | USB 2.0 OTG IDPIN                                                                                                                                                                                         |

| 63     |        | USB_AVDD33   | A, I   |            | USB 3.3V Analog Power Supply<br>See Table 16, Power and Ground, on<br>page 32.                                                                                                                            |

| 64     |        | USB_DP       | A, I/O | USB_AVDD33 | USB 2.0 Bus Data+                                                                                                                                                                                         |

| 65     |        | USB_DM       | A, I/O | USB_AVDD33 | USB 2.0 Bus Data-                                                                                                                                                                                         |

| 66     |        | USB_DRV_VBUS | 0      | VDDIO_3    | Drive 5V on VBUS<br>0 = do not drive VBUS<br>1 = drive 5V on VBUS<br>The USB_DRV_VBUS port is connected to<br>the SoC pad to drive an external power<br>management chip to provide power for USB<br>VBUS. |

1. After POR, if USB is in host mode, USB\_DP/USB\_DM will be SE0. If USB is in device mode, USB\_DP/USB\_DM will be High-z.

| 88-Pin  | 68-Pin | Signal Name | Туре | Supply    | Description              |

|---------|--------|-------------|------|-----------|--------------------------|

| GPIO_0  |        | UART0_CTSn  | 1    | VDDIO_0   | UART 0 CTSn (active low) |

| GPIO_1  |        | UART0_RTSn  | 0    | VDDIO_0   | UART 0 RTSn (active low) |

| GPIO_2  |        | UART0_TXD   | 0    | VDDIO_0   | UART 0 TXD               |

| GPIO_3  |        | UART0_RXD   | I    | VDDIO_0   | UART 0 RXD               |

|         |        |             | -    | 1         |                          |

| GPIO_23 |        | UART0_CTSn  | 1    | VDDIO_AON | UART 0 CTSn (active low) |

| GPIO_24 |        | UART0_RXD   | I    | VDDIO_AON | UART 0 RXD               |

|         |        | ·           |      |           | ·                        |

| GPIO_30 |        | UART0_CTSn  | I    | VDDIO_2   | UART 0 CTSn (active low) |

| GPIO_31 |        | UART0_RTSn  | 0    | VDDIO_2   | UART 0 RTSn (active low) |

| GPIO_32 |        | UART0_TXD   | 0    | VDDIO_2   | UART 0 TXD               |

| GPIO_33 |        | UART0_RXD   | I    | VDDIO_2   | UART 0 RXD               |

|         |        |             |      | ·         |                          |

| GPIO_37 |        | UART0_RTSn  | 0    | VDDIO_3   | UART 0 RTSn (active low) |

| GPIO_27 | -      | UART0_TXD   | 0    | VDDIO_3   | UART 0 TXD               |

|         |        |             |      |           |                          |

| GPIO_11 |        | UART1_CTSn  | I    | VDDIO_0   | UART 1 CTSn (active low) |

| GPIO_12 |        | UART1_RTSn  | 0    | VDDIO_0   | UART 1 RTSn (active low) |

| GPIO_13 |        | UART1_TXD   | 0    | VDDIO_0   | UART 1 TXD               |

| GPIO_14 |        | UART1_RXD   | I    | VDDIO_0   | UART 1 RXD               |

|         |        |             |      |           |                          |

| GPIO_35 |        | UART1_CTSn  | I    | VDDIO_3   | UART 1 CTSn (active low) |

| GPIO_36 |        | UART1_RTSn  | 0    | VDDIO_3   | UART 1 RTSn (active low) |

| GPIO_38 |        | UART1_TXD   | 0    | VDDIO_3   | UART 1 TXD               |

| GPIO_39 |        | UART1_RXD   | I    | VDDIO_3   | UART 1 RXD               |

| GPIO_42 |        | UART1_CTSn  | I    | VDDIO_3   | UART 1 CTSn (active low) |

| GPIO_43 |        | UART1_RTSn  | 0    | VDDIO_3   | UART 1 RTSn (active low) |

| GPIO_44 |        | UART1_TXD   | 0    | VDDIO_3   | UART 1 TXD               |

| GPIO_45 |        | UART1_RXD   | I    | VDDIO_3   | UART 1 RXD               |

### Table 6: UART Interface<sup>1</sup>

| Table 6: UART Interface' (Continued) |        |             |      |         |                          |  |  |

|--------------------------------------|--------|-------------|------|---------|--------------------------|--|--|

| 88-Pin                               | 68-Pin | Signal Name | Туре | Supply  | Description              |  |  |

|                                      |        |             |      |         |                          |  |  |

| GPIO_7                               |        | UART2_CTSn  | I    | VDDIO_0 | UART 2 CTSn (active low) |  |  |

| GPIO_8                               |        | UART2_RTSn  | 0    | VDDIO_0 | UART 2 RTSn (active low) |  |  |

| GPIO_9                               |        | UART2_TXD   | 0    | VDDIO_0 | UART 2 TXD               |  |  |

| GPIO_10                              |        | UART2_RXD   | I    | VDDIO_0 | UART 2 RXD               |  |  |

|                                      |        |             |      |         |                          |  |  |

| GPIO_46                              |        | UART2_CTSn  | I    | VDDIO_3 | UART 2 CTSn (active low) |  |  |

| GPIO_47                              |        | UART2_RTSn  | 0    | VDDIO_3 | UART 2 RTSn (active low) |  |  |

| GPIO_48                              |        | UART2_TXD   | 0    | VDDIO_3 | UART 2 TXD               |  |  |

| GPIO_49                              |        | UART2_RXD   | I    | VDDIO_3 | UART 2 RXD               |  |  |

#### Table 6: UART Interface<sup>1</sup> (Continued)

1. All UART signals are muxed on GPIO pins. See Table 11, GPIO Interface, on page 19 for GPIO muxing.

| Table 7: | GPT Inter | ace         |      |           |                                      |

|----------|-----------|-------------|------|-----------|--------------------------------------|

| 88-Pin   | 68-Pin    | Signal Name | Туре | Supply    | Description                          |

| GPIO_0   |           | GPT0_CH0    | I/O  | VDDIO_0   | General Purpose Timer 0, Channel 0   |

| GPIO_1   |           | GPT0_CH1    | I/O  | VDDIO_0   | General Purpose Timer 0, Channel 1   |

| GPIO_2   |           | GPT0_CH2    | I/O  | VDDIO_0   | General Purpose Timer 0, Channel 2   |

| GPIO_3   |           | GPT0_CH3    | I/O  | VDDIO_0   | General Purpose Timer 0, Channel 3   |

| GPIO_4   |           | GPT0_CH4    | I/O  | VDDIO_0   | General Purpose Timer 0, Channel 4   |

| GPIO_5   |           | GPT0_CH5    | I/O  | VDDIO_0   | General Purpose Timer 0, Channel 5   |

| GPIO_35  |           | GPT0_CLKIN  | I    | VDDIO_3   | General Purpose Timer 0, Clock Input |

|          |           |             |      |           |                                      |

| GPIO_28  |           | GPT1_CH0    | I/O  | VDDIO_2   | General Purpose Timer 1, Channel 0   |

| GPIO_29  |           | GPT1_CH1    | I/O  | VDDIO_2   | General Purpose Timer 1, Channel 1   |

| GPIO_30  |           | GPT1_CH2    | I/O  | VDDIO_2   | General Purpose Timer 1, Channel 2   |

| GPIO_31  |           | GPT1_CH3    | I/O  | VDDIO_2   | General Purpose Timer 1, Channel 3   |

| GPIO_32  |           | GPT1_CH4    | I/O  | VDDIO_2   | General Purpose Timer 1, Channel 4   |

| GPIO_33  |           | GPT1_CH5    | I/O  | VDDIO_2   | General Purpose Timer 1, Channel 5   |

| GPIO_24  |           | GPT1_CH5    | I/O  | VDDIO_AON | General Purpose Timer 1, Channel 5   |

| GPIO_36  |           | GPT1_CLKIN  | I    | VDDIO_3   | General Purpose Timer 1, Clock Input |

|          |           |             |      |           |                                      |

| GPIO_11  |           | GPT2_CH0    | I/O  | VDDIO_0   | General Purpose Timer 2, Channel 0   |

| GPIO_12  |           | GPT2_CH1    | I/O  | VDDIO_0   | General Purpose Timer 2, Channel 1   |

| GPIO_13  |           | GPT2_CH2    | I/O  | VDDIO_0   | General Purpose Timer 2, Channel 2   |

| GPIO_14  |           | GPT2_CH3    | I/O  | VDDIO_0   | General Purpose Timer 2, Channel 3   |

| GPIO_15  |           | GPT2_CH4    | I/O  | VDDIO_0   | General Purpose Timer 2, Channel 4   |

| GPIO_37  |           | GPT2_CH5    | I/O  | VDDIO_3   | General Purpose Timer 2, Channel 5   |

| GPIO_38  |           | GPT2_CLKIN  | I    | VDDIO_3   | General Purpose Timer 2, Clock Input |

|          | -         |             |      |           |                                      |

| GPIO_17  |           | GPT3_CH0    | I/O  | VDDIO_1   | General Purpose Timer 3, Channel 0   |

| GPIO_18  |           | GPT3_CH1    | I/O  | VDDIO_1   | General Purpose Timer 3, Channel 1   |

| GPIO_19  |           | GPT3_CH2    | I/O  | VDDIO_1   | General Purpose Timer 3, Channel 2   |

| GPIO_20  |           | GPT3_CH3    | I/O  | VDDIO_1   | General Purpose Timer 3, Channel 3   |

|          | 1         | 1           |      | 1         | <u> </u>                             |

#### Table 7: GPT Interface<sup>1</sup>

| 88-Pin  | 68-Pin | Signal Name | Туре | Supply  | Description                          |

|---------|--------|-------------|------|---------|--------------------------------------|

| GPIO_21 |        | GPT3_CH4    | I/O  | VDDIO_1 | General Purpose Timer 3, Channel 4   |

| GPIO_34 |        | GPT3_CH5    | I/O  | VDDIO_3 | General Purpose Timer 3, Channel 5   |

| GPIO_39 |        | GPT3_CLKIN  | I    | VDDIO_3 | General Purpose Timer 3, Clock Input |

#### Table 7: GPT Interface<sup>1</sup> (Continued)

1. All GPT signals are muxed on GPIO pins. See Table 11, GPIO Interface, on page 19 for GPIO muxing.

| 88-Pin  | 68-Pin | Pin Name | Туре | Supply  | Description           |

|---------|--------|----------|------|---------|-----------------------|

| GPIO_0  |        | SSP0_CLK | I/O  | VDDIO_0 | SSP 0 Serial Clock    |

| GPIO_1  |        | SSP0_FRM | I/O  | VDDIO_0 | SSP 0 Frame Indicator |

| GPIO_2  |        | SSP0_TXD | 0    | VDDIO_0 | SSP 0 TXD             |

| GPIO_3  |        | SSP0_RXD | I    | VDDIO_0 | SSP 0 RXD             |

|         |        |          |      |         |                       |

| GPIO_30 |        | SSP0_CLK | I/O  | VDDIO_2 | SSP 0 Serial Clock    |

| GPIO_31 |        | SSP0_FRM | I/O  | VDDIO_2 | SSP 0 Frame Indicator |

| GPIO_32 |        | SSP0_TXD | 0    | VDDIO_2 | SSP 0 TXD             |

| GPIO_33 |        | SSP0_RXD | I    | VDDIO_2 | SSP 0 RXD             |

|         |        |          |      |         |                       |

| GPIO_11 |        | SSP1_CLK | I/O  | VDDIO_0 | SSP 1 Serial Clock    |

| GPIO_12 |        | SSP1_FRM | I/O  | VDDIO_0 | SSP 1 Frame Indicator |

| GPIO_13 |        | SSP1_TXD | 0    | VDDIO_0 | SSP 1 TXD             |

| GPIO_14 |        | SSP1_RXD | I    | VDDIO_0 | SSP 1 RXD             |

|         |        |          |      |         |                       |

| GPIO_18 |        | SSP1_CLK | I/O  | VDDIO_1 | SSP 1 Serial Clock    |

| GPIO_19 |        | SSP1_FRM | I/O  | VDDIO_1 | SSP 1 Frame Indicator |

| GPIO_20 |        | SSP1_TXD | 0    | VDDIO_1 | SSP 1 TXD             |

| GPIO_21 |        | SSP1_RXD | I    | VDDIO_1 | SSP 1 RXD             |

|         |        |          |      |         |                       |

| GPIO_35 |        | SSP1_CLK | I/O  | VDDIO_3 | SSP 1 Serial Clock    |

| GPIO_36 |        | SSP1_FRM | I/O  | VDDIO_3 | SSP 1 Frame Indicator |

| GPIO_38 |        | SSP1_TXD | 0    | VDDIO_3 | SSP 1 TXD             |

#### Table 8: SSP Interface<sup>1</sup>

| 88-Pin  | 68-Pin | Pin Name | Туре | Supply  | Description           |  |  |  |

|---------|--------|----------|------|---------|-----------------------|--|--|--|

| GPIO_39 |        | SSP1_RXD | I    | VDDIO_3 | SSP 1 RXD             |  |  |  |

|         |        |          |      |         |                       |  |  |  |

| GPIO_42 |        | SSP1_CLK | I/O  | VDDIO_3 | SSP 1 Serial Clock    |  |  |  |

| GPIO_43 |        | SSP1_FRM | I/O  | VDDIO_3 | SSP 1 Frame Indicator |  |  |  |

| GPIO_44 |        | SSP1_TXD | 0    | VDDIO_3 | SSP 1 TXD             |  |  |  |

| GPIO_45 |        | SSP1_RXD | I    | VDDIO_3 | SSP 1 RXD             |  |  |  |

|         |        |          |      |         |                       |  |  |  |

| GPIO_7  |        | SSP2_CLK | I/O  | VDDIO_0 | SSP 2 Serial Clock    |  |  |  |

| GPIO_8  |        | SSP2_FRM | I/O  | VDDIO_0 | SSP 2 Frame Indicator |  |  |  |

| GPIO_9  |        | SSP2_TXD | 0    | VDDIO_0 | SSP 2 TXD             |  |  |  |

| GPIO_10 |        | SSP2_RXD | I    | VDDIO_0 | SSP 2 RXD             |  |  |  |

|         |        |          |      |         |                       |  |  |  |

| GPIO_46 |        | SSP2_CLK | I/O  | VDDIO_3 | SSP 2 Serial Clock    |  |  |  |

| GPIO_47 |        | SSP2_FRM | I/O  | VDDIO_3 | SSP 2 Frame Indicator |  |  |  |

| GPIO_48 |        | SSP2_TXD | 0    | VDDIO_3 | SSP 2 TXD             |  |  |  |

| GPIO_49 |        | SSP2_RXD | I    | VDDIO_3 | SSP 2 RXD             |  |  |  |

#### Table 8: SSP Interface<sup>1</sup> (Continued)

1. All SSP signals are muxed on GPIO pins. See Table 11, GPIO Interface, on page 19 for GPIO muxing.

| 88-Pin             | 68-Pin | Pin Name | Туре | Supply    | Description            |

|--------------------|--------|----------|------|-----------|------------------------|

| GPIO_4<br>GPIO_7   |        | I2C0_SDA | I/O  | VDDIO_0   | I <sup>2</sup> C 0 SDA |

| GPIO_5<br>GPIO_8   |        | I2C0_SCL | I/O  | VDDIO_0   | I <sup>2</sup> C 0 SCL |

| GPIO_6<br>GPIO_9   |        | I2C1_SDA | I/O  | VDDIO_0   | I <sup>2</sup> C 1 SDA |

| GPIO_10            |        | I2C1_SCL | I/O  | VDDIO_0   | I <sup>2</sup> C 1 SCL |

|                    |        | 1        |      |           |                        |

| GPIO_20            |        | I2C0_SDA | I/O  | VDDIO_1   | I <sup>2</sup> C 0 SDA |

| GPIO_21            |        | I2C0_SCL | I/O  | VDDIO_1   | I <sup>2</sup> C 0 SCL |

| GPIO_18            |        | I2C1_SDA | I/O  | VDDIO_1   | I <sup>2</sup> C 1 SDA |

| GPIO_17<br>GPIO_19 |        | I2C1_SCL | I/O  | VDDIO_1   | I <sup>2</sup> C 1 SCL |

|                    |        |          |      |           |                        |

| GPIO_25            |        | I2C1_SDA | I/O  | VDDIO_AON | I <sup>2</sup> C 1 SDA |

| GPIO_26            |        | I2C1_SCL | I/O  | VDDIO_AON | I <sup>2</sup> C 1 SCL |

|                    |        |          |      |           | ·                      |

| GPIO_28            |        | I2C0_SDA | I/O  | VDDIO_2   | l <sup>2</sup> C 1 SDA |

| GPIO_29            |        | I2C0_SCL | I/O  | VDDIO_2   | l <sup>2</sup> C 1 SCL |

### Table 9: I<sup>2</sup>C Interface<sup>1</sup>

1. All I<sup>2</sup>C signals are muxed on GPIO pins. See Table 11, GPIO Interface, on page 19 for GPIO muxing.

#### Table 10: QSPI Interface<sup>1</sup>

| 88-Pin  | 68-Pin | Pin Name | Туре | Supply  | Description                   |

|---------|--------|----------|------|---------|-------------------------------|

| GPIO_28 |        | QSPI_SSn | 0    | VDDIO_2 | QSPI Chip Select (active low) |

| GPIO_29 |        | QSPI_CLK | 0    | VDDIO_2 | QSPI Clock                    |

| GPIO_30 |        | QSPI_D0  | I/O  | VDDIO_2 | QSPI Data 0                   |

| GPIO_31 |        | QSPI_D1  | I/O  | VDDIO_2 | QSPI Data 1                   |

| GPIO_32 |        | QSPI_D2  | I/O  | VDDIO_2 | QSPI Data 2                   |

| GPIO_33 |        | QSPI_D3  | I/O  | VDDIO_2 | QSPI Data 3                   |

1. QSPI signals are used for external Flash only. All QSPI signals are muxed on GPIO pins. See Table 11, GPIO Interface, on page 19 for GPIO muxing.

| 60 Di- | Din/Girnal Mars | Turre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Questa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | -               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1      | GPIO_0          | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | VDDIO_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | General Purpose I/O 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | GPT0_CH0        | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | General Purpose Timer 0, Channel 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | UART0_CTSn      | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | UART 0 CTSn (active low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

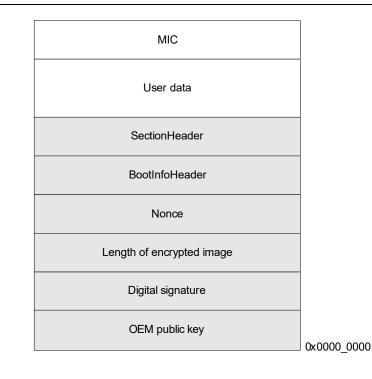

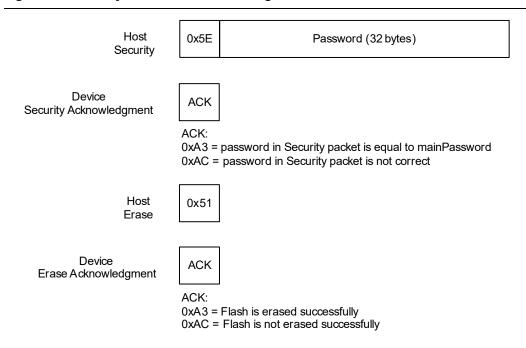

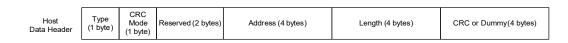

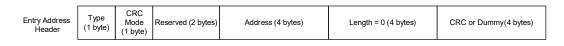

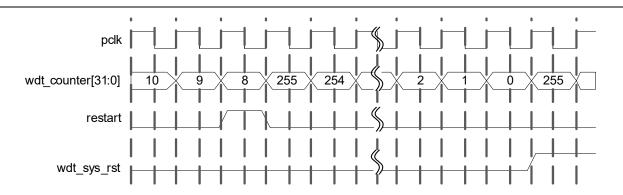

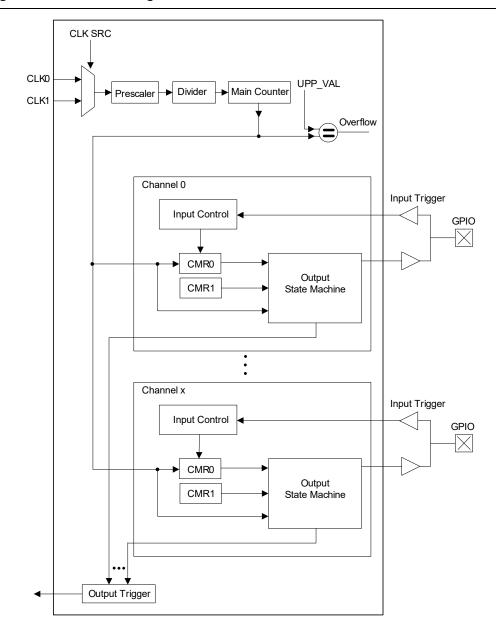

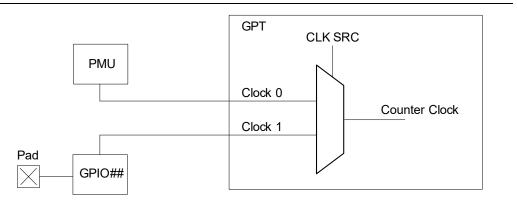

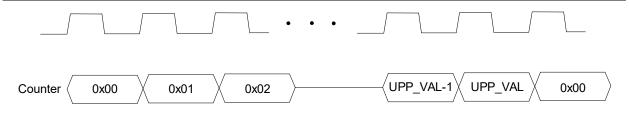

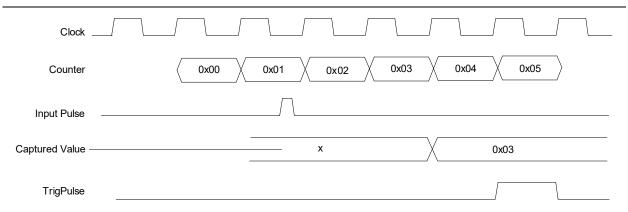

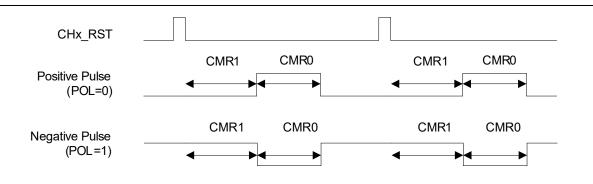

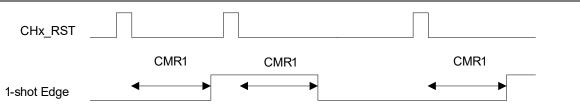

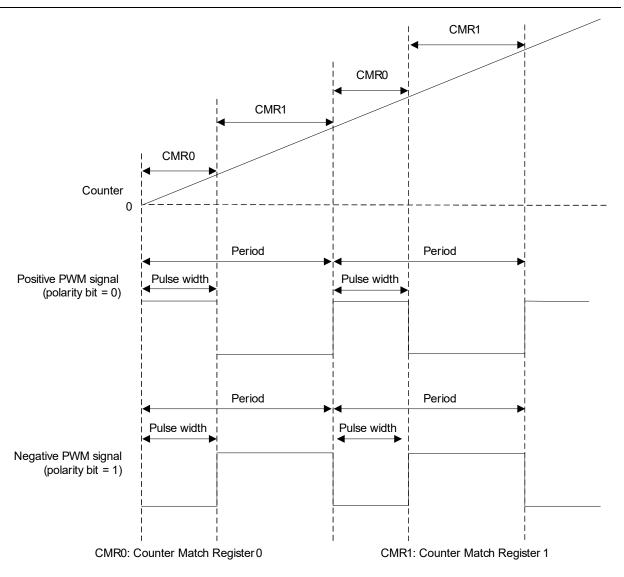

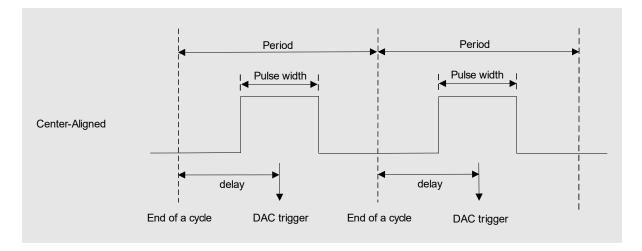

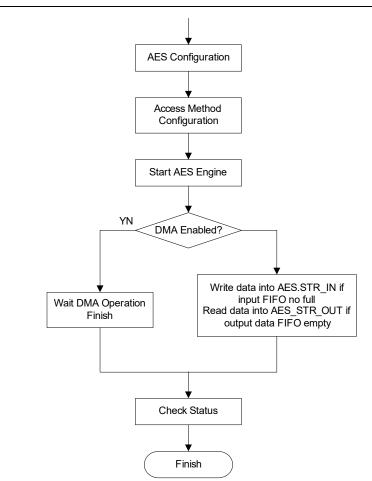

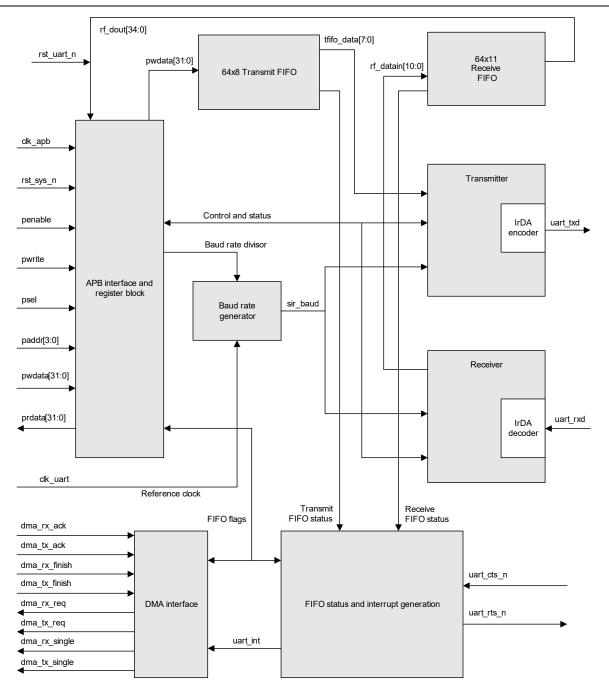

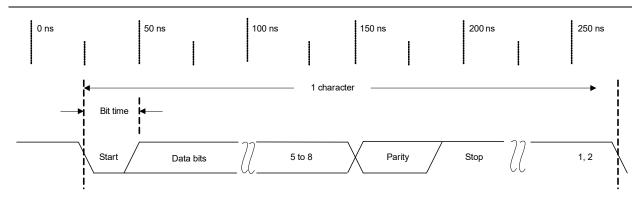

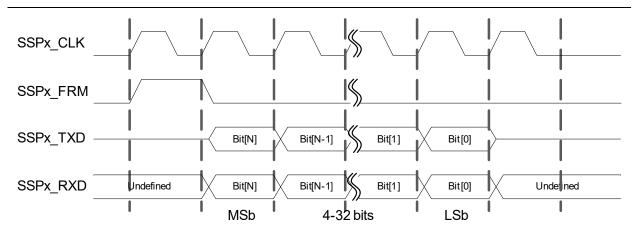

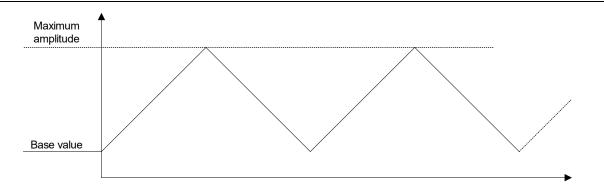

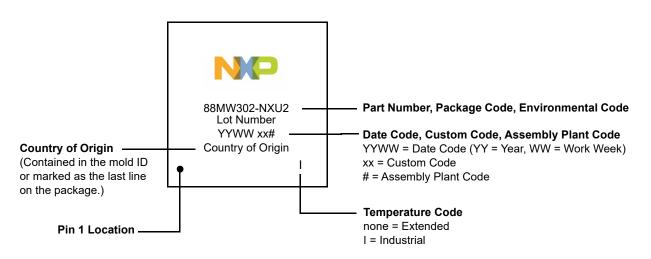

|        | SSP0_CLK        | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SSP 0 Serial Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |