Speed Your Time to Market by Leveraging Freescale's Software, Tools and Professional Services for **QorlQ Development**

EUF-SNT-T1467

Gino Gatto | Senior Field Application Engineer

MAY.2015

External Use

Prescule, the Prescule tops, AIVAn; G-5, GodeTEST, GodeMerov, CollFine, GoldFinex, G-Nam, the Emergy Efficient Solutions tops, Kinetis, Magnik, mobileCT, FEG, PowerGLAGG, Processer Espen, Quint, Gorid Camerge, Darive, Ready Pag, Salakasan, the Salakasan tops, SterCine, Styrephony, Vertilla, Vythet and Xinnak are trademarks of Presseals Semicontaction: (in, Reju, U.S. Pat, & Th. CH. Antat, BeeK), Bashkasan, Fers (Salakasan, Kork, SterCine, Symphony, Vertilla, Vythet and Xinnak are trademarks of Presseals Semicontaction: Fund, Reju, U.S. Pat, & Th. CH. Antat, BeeK), Bashkasan, Fers (Layerson, MXC, Partform in a Fackage, QUCC). Engine, SAMATINOS, Tawa: TrateLink and UMEMS are trademarks of Presscale Beniconductor, Inc. All other product or service norms are the property of their respective owners. © 2015 Presscale Beniconductor, Inc.

## Agenda

### Overview

- Complexity Increasing

- Freescale Technology and Ecosystem

## **Freescale Commercial Capabilities**

- Software

- Hardware

- Systems

External Use

### **Questions and Answers**

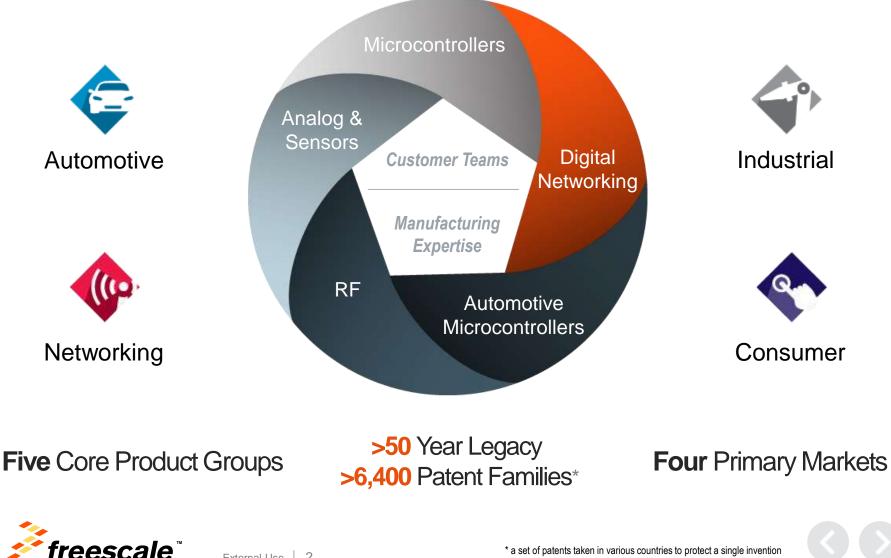

## We Are a Global Leader in **Embedded Processing Solutions**

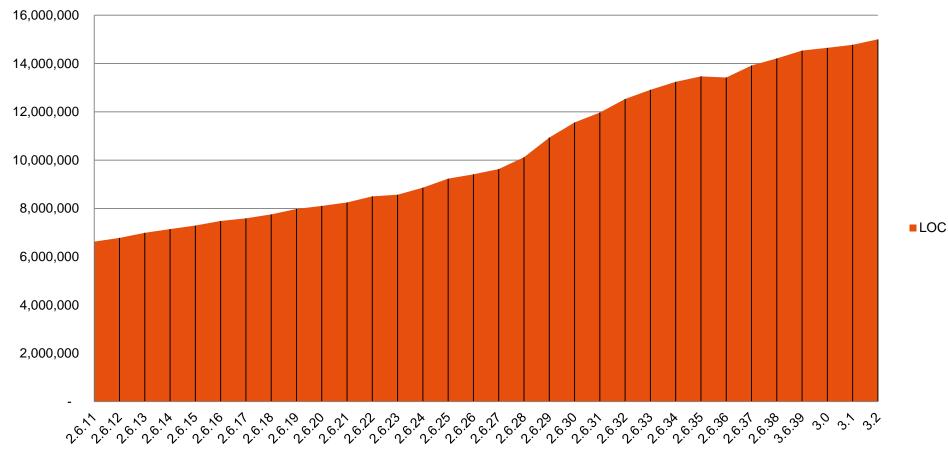

## **Software Complexity Increasing**

#### Linux<sup>®</sup> Kernel Lines of Code

#### The Explosive Growth In Connected Devices – **Requiring Faster Time to Market** Θ 50 BILLION --25 BILLION 12.5 BILLION - A 🗟 7.6B **7.2**B **6.8**B 1 6.5B World 6.3B Population Ŧ # Connected <1x **1**x 2x 3.5x 6.5x Devices/Person 2003 2008 2010 2015 2020 freescale

External Use 5

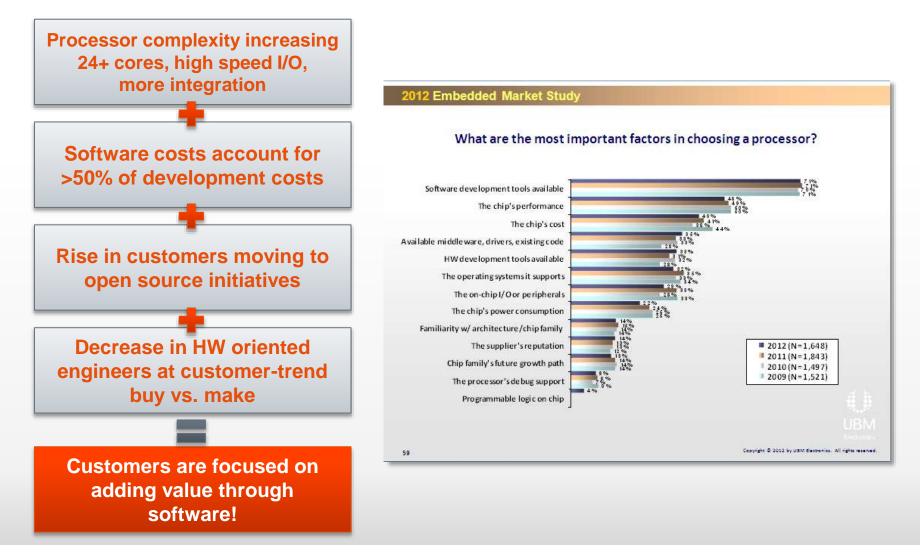

## **Market Trends for Software in Embedded Devices**

## **Freescale Software and Systems Organization**

- Freescale has 1,000+ software engineers, 700+ focused on Digital Networking

- Increasing investment on software through hiring and acquisition

- Run-Time Technologies, Multi-core, Tools, Key Applications

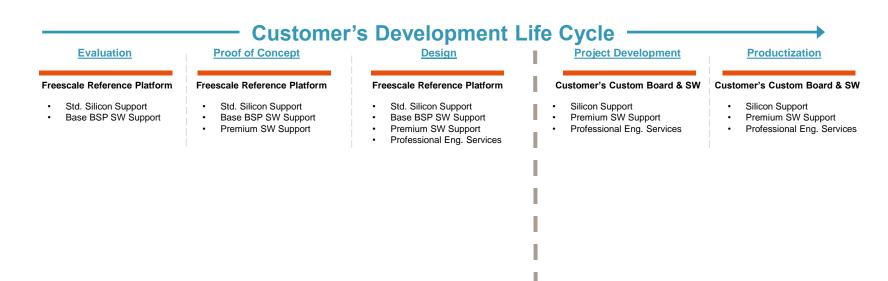

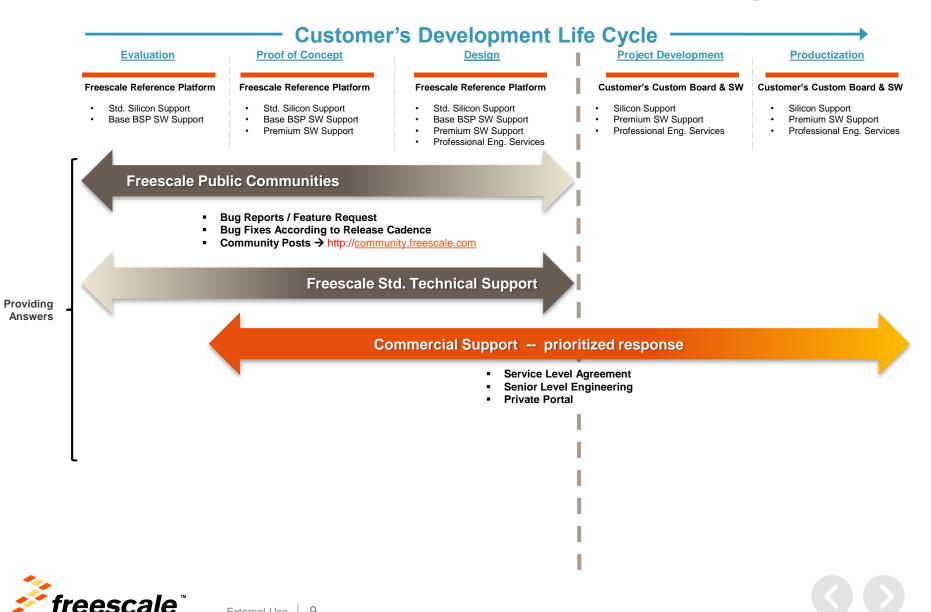

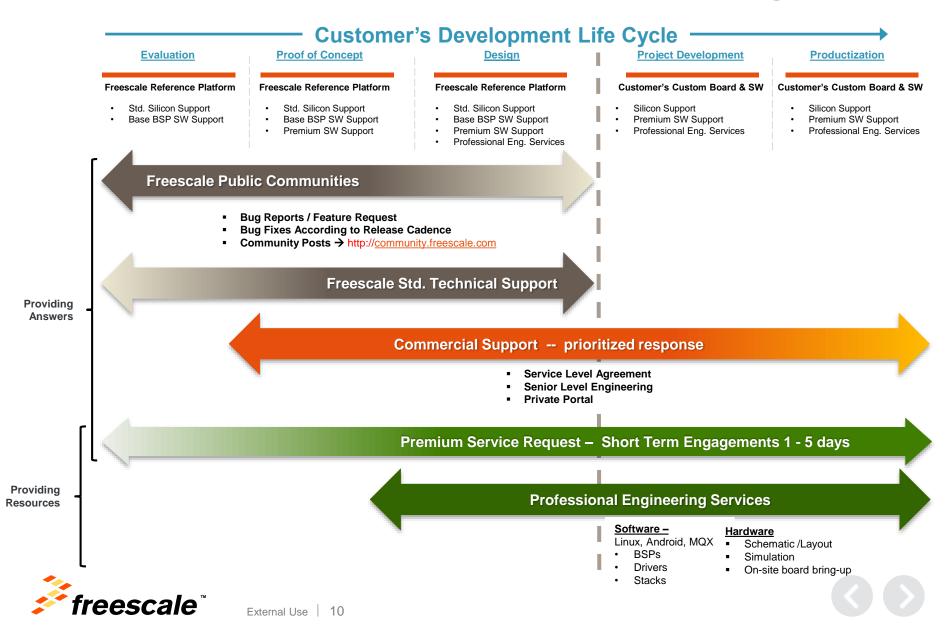

## **Software Support / Professional Services Coverage**

## Software Support / Professional Services Coverage

## **Software Support / Professional Services Coverage**

## **Networking Software and Services Group**

|                                                                                                                                                                                                        | Software Products and Custom Services                                                                                                                                                                           |                                                                                                                                                                           |                                                                                                                                                 |                                                                                                         |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Development<br>Tools                                                                                                                                                                                   | Runtime<br>Products                                                                                                                                                                                             | Solutions<br>Reference                                                                                                                                                    | Linux®<br>Services                                                                                                                              | Integration<br>Services                                                                                 |  |  |  |  |  |  |

| <ul> <li>CodeWarrior <ul> <li>IDE</li> <li>Debug</li> <li>Compiler</li> <li>Trace</li> </ul> </li> <li>QorIQ <ul> <li>Optimization Suite</li> <li>Scenarios Tools</li> <li>DDrV</li> </ul> </li> </ul> | <ul> <li>VortiQa Software<br/>Products         <ul> <li>Application<br/>Identification<br/>Software (AIS)</li> <li>Open Networking<br/>Switching<br/>Framework</li> <li>Mobile Transport</li> </ul> </li> </ul> | <ul> <li>Storage Controller</li> <li>SDN Switch</li> <li>Wireless LAN</li> <li>Data Concentrator</li> <li>Smart Converged<br/>Gateway</li> <li>Digital Signage</li> </ul> | <ul> <li>Commercial<br/>Support</li> <li>Frozen Branch</li> <li>Application<br/>Specific Hardening</li> <li>Feature<br/>Acceleration</li> </ul> | <ul> <li>Systems<br/>Consulting</li> <li>Design Services</li> <li>Porting</li> <li>Migration</li> </ul> |  |  |  |  |  |  |

| CodeWarrior<br><i>QorIQ</i>                                                                                                                                                                            | VortiQa                                                                                                                                                                                                         |                                                                                                                                                                           |                                                                                                                                                 | Øo                                                                                                      |  |  |  |  |  |  |

Development

## **CodeWarrior for Networking**

- Systems are complex -CodeWarrior makes debugging easy

- Multicore or multiple cores

- Heterogeneous or homogenous

- Linux or Multi-OS Systems

- ARM<sup>®</sup>, Power Architecture<sup>®</sup> and StarCore

- Use one CodeWarrior software

External Use

12

freescale.com/CodeWarrior

Linux Services

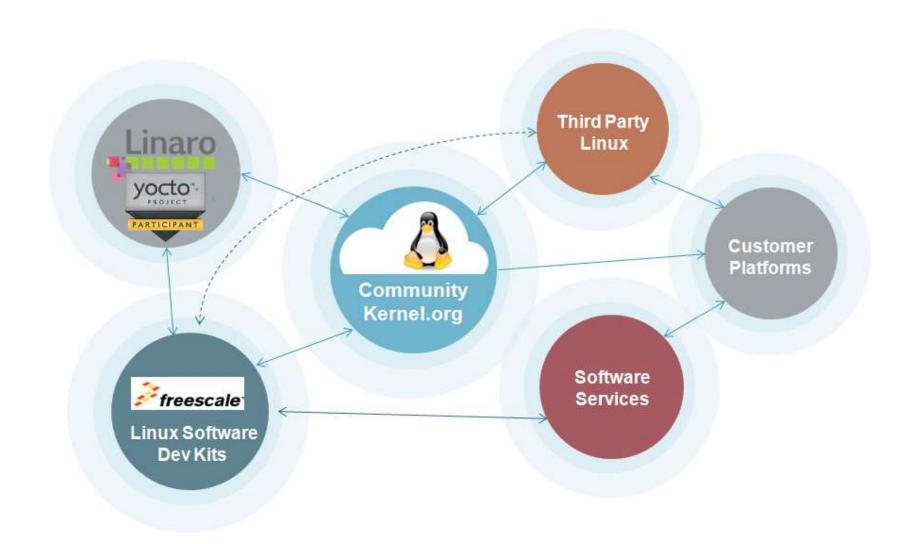

### **Freescale Linux Overview**

External Use | 13

## **Freescale Networking Linux SDK**

- Linux Software Development Kit (SDK) for Power Architecture

- Optimized Linux software

- Complete range of QorlQ and PowerQUICC platforms

- Hardware accelerated

- Rigorous testing

- Multiple configurations, Host OSes

- Performance tuned

- Flexible AMP/SMP support

- Yocto-based

- Bi-annual update

- No-cost download

- <u>http://freescale.com/sdk</u>

## **Freescale Linux SDK Highlights**

- Freescale Linux Investment

- Hundreds of man-years per year

- Global Board Farms

- Top 15 Company Contributor to kernel.org

- Systems Designed, Tightly Integrated with Freescale SOC

- Systems Validated Tightly aligned with Freescale NPI

- Quality

- ISO-9000 Quality Processes Externally Audited

- On-going Maintenance, regular kernel updates (LTSi)

- Open Source Compatible Upstreamed, Dedicated Team

- Standards based Yocto

- Ease of Use

- Common Kernel Across support platforms

- Combined P, T and Layerscape support in unified SDK

Solutions References

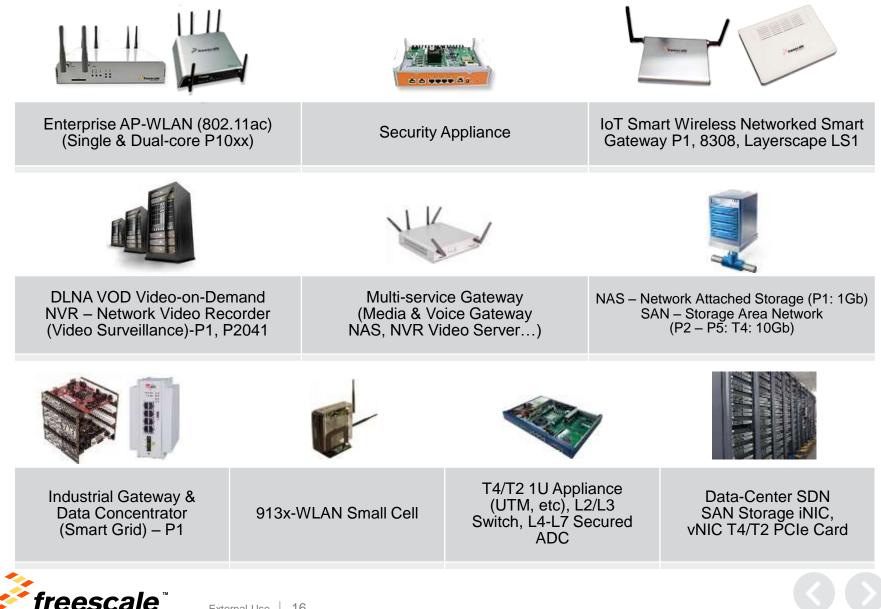

## Segment Solutions Reference Platform Solutions

## **Business Models**

| Product                               | License Fee | Royalty | Paid Support | Engineering<br>Services |

|---------------------------------------|-------------|---------|--------------|-------------------------|

| Linux / Android Support &<br>Services |             |         |              |                         |

| VortiQa Run-Time Software             |             |         |              |                         |

| Embedded Applications                 |             |         |              |                         |

| PEG                                   |             |         |              |                         |

| Development Tools                     |             |         |              |                         |

Freescale MQX Software

Runtime Products

### VortiQa

## VortiQa Portfolio

| Module                                                                                                                      | Application                                                 |  |

|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|

| VortiQa—Application Identification                                                                                          | VortiQa—Mobility Transport                                  |  |

| Suite                                                                                                                       | Transport Functions: IPsec, QoS,                            |  |

| Deep Packet Inspection: Identify the type of traffic on the network                                                         | PDCP and GTP                                                |  |

| NEXT-GENERATI                                                                                                               | ON TECHNOLOGY                                               |  |

| SDN—Open Network Switch                                                                                                     | SDN—Open Network Director                                   |  |

| VortiQa—Software Defined<br>Networks (SDN)—Switch                                                                           | VortiQa—Software Defined<br>Networks (SDN)—Controller       |  |

| Data Plane Functions: layer 2, layer 3<br>and above; Firewall, NAT, QoS, DPI,<br>etc. POC available; product in<br>planning | Controller Functions: PoC available;<br>product in planning |  |

## **Networking Software and Services Group**

- Accelerate Customer Time to Market

- Speed Adoption of Multicore

- Dedicated expert staff with access to software and SoC teams

- **Deliver** Commercial Software, Support, Services and Solutions

- Commercial Software: VortiQa, CodeWarrior, Processor Expert

- Accelerate new technology adoption

- Simplify Software Engagement

with Freescale

- Consolidate Freescale software and solutions

- Streamline business processes

- Create Success!

- Partner with customers

- Leverage *your* strengths, add *our* capabilities

# Introduction to the QorlQ Configuration Suite (QCS)

## **QorIQ Software Enablement Strategy**

- Provide development systems

- Complete boards for evaluation of QorIQ devices

- Provide Runtime software for QorlQ products

- Hypervisor, Linux BSPs, Reference Designs

- Provide bring-up tools and development systems

- GNU tools, CodeWarrior debuggers, probes, boards

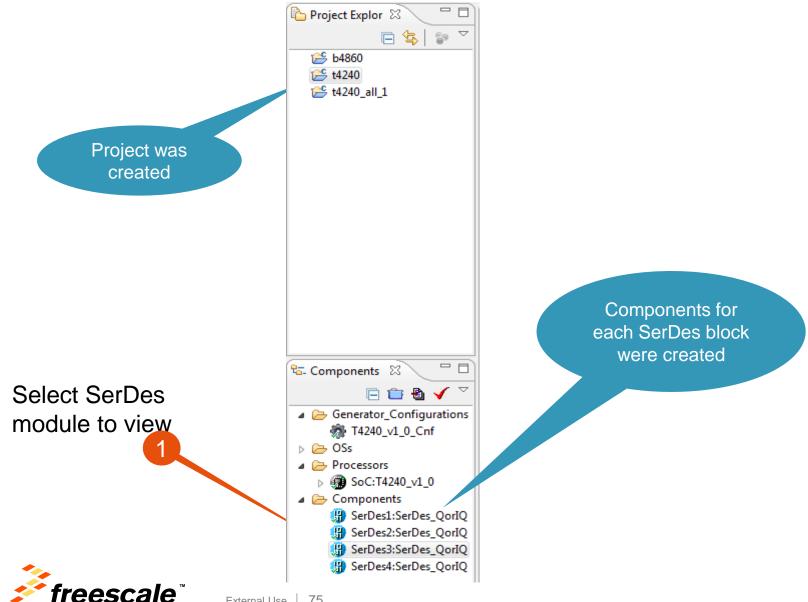

- Provide configuration tools to support your application of QorIQ on your custom board.

- RCW, BootROM, Pin Mux

- DDR Configuration

- Device Tree Editing

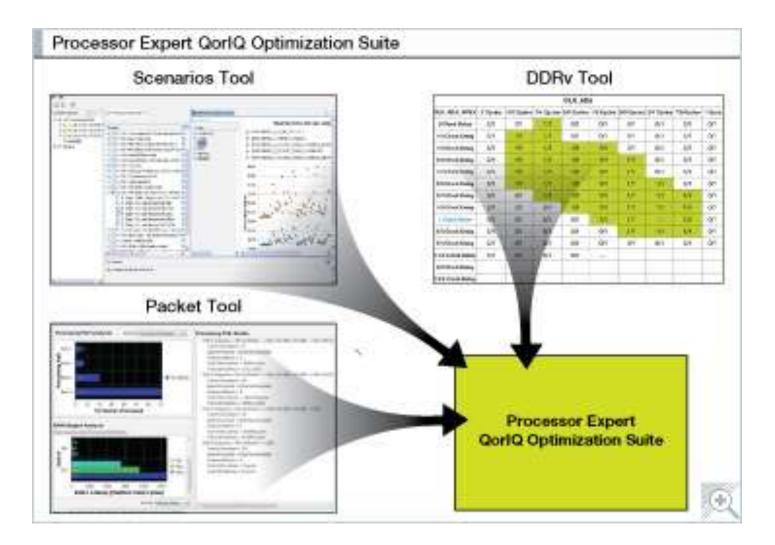

- Provide optimization tools to support runtime visibility into these complex parts to help calibrate and debug your systems.

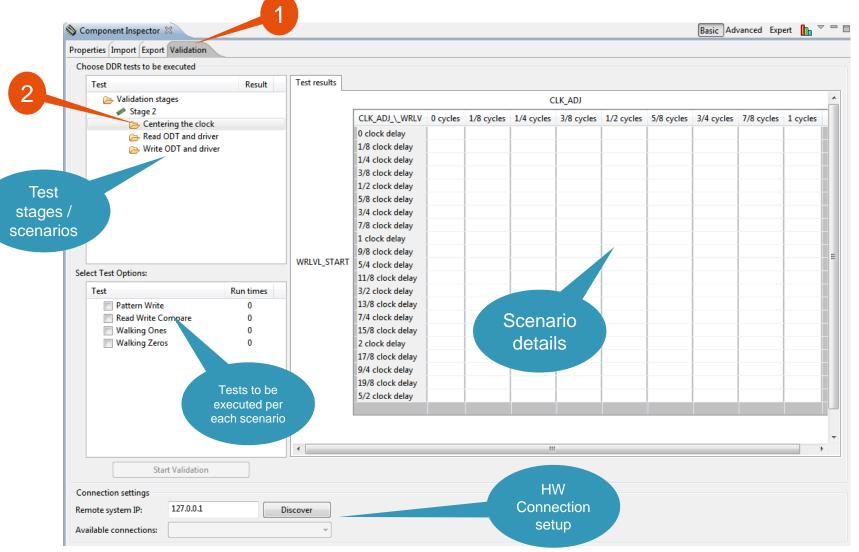

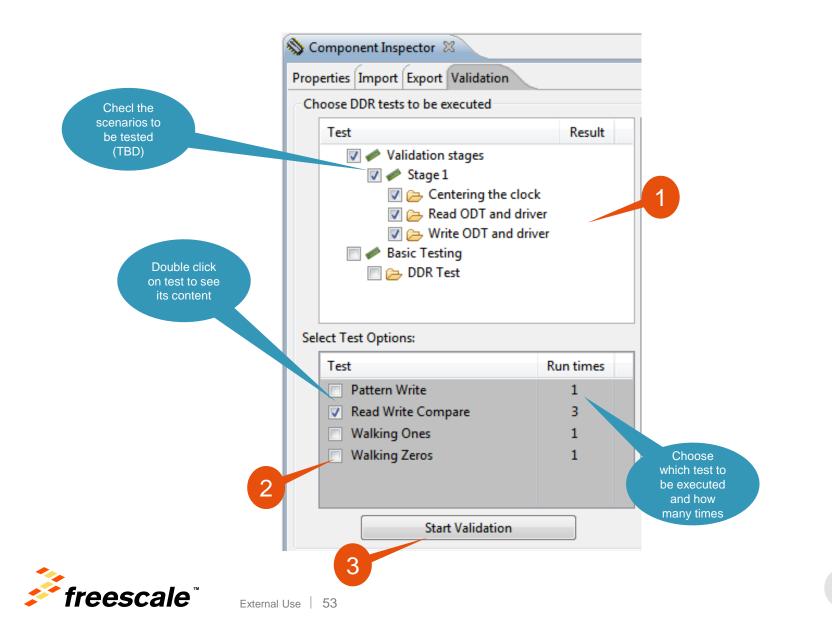

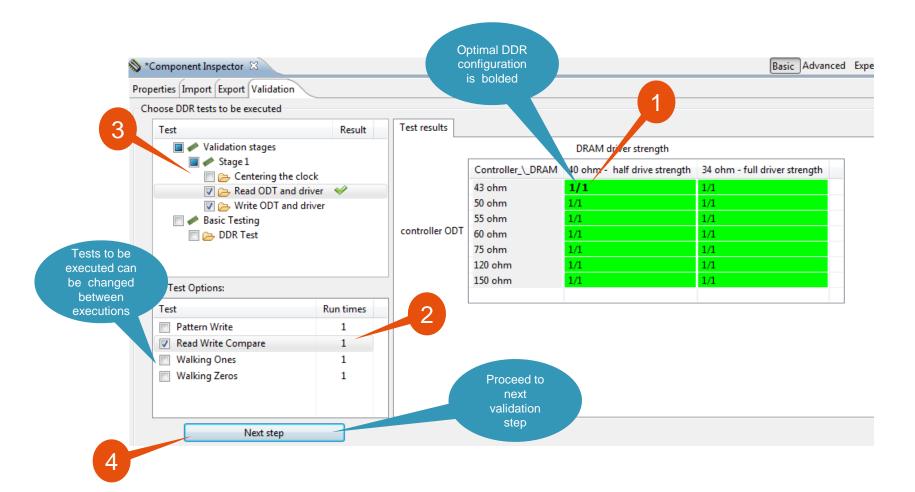

- DDR validation tool to ensure DDR functionally configured for custom board

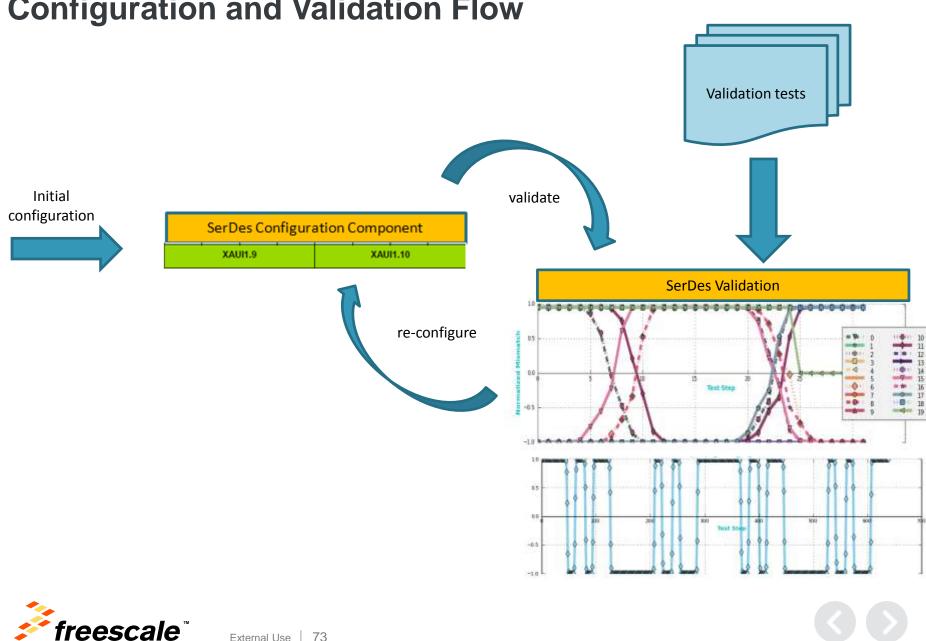

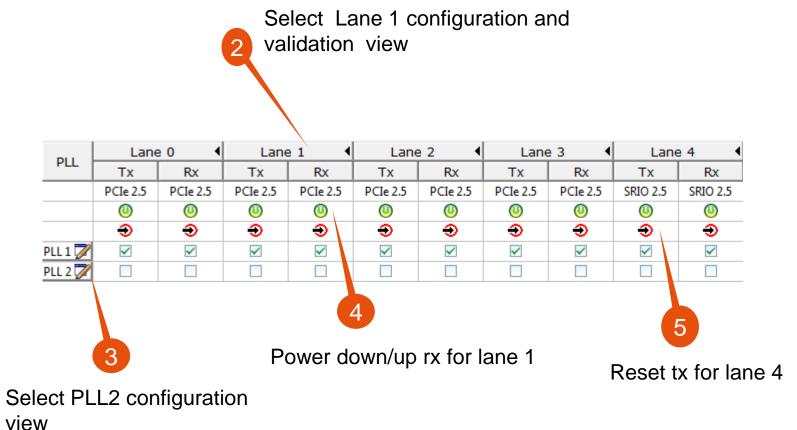

- Serdes validation with internal and external loopback

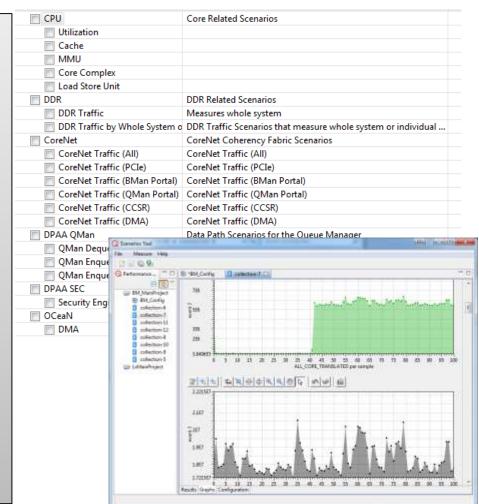

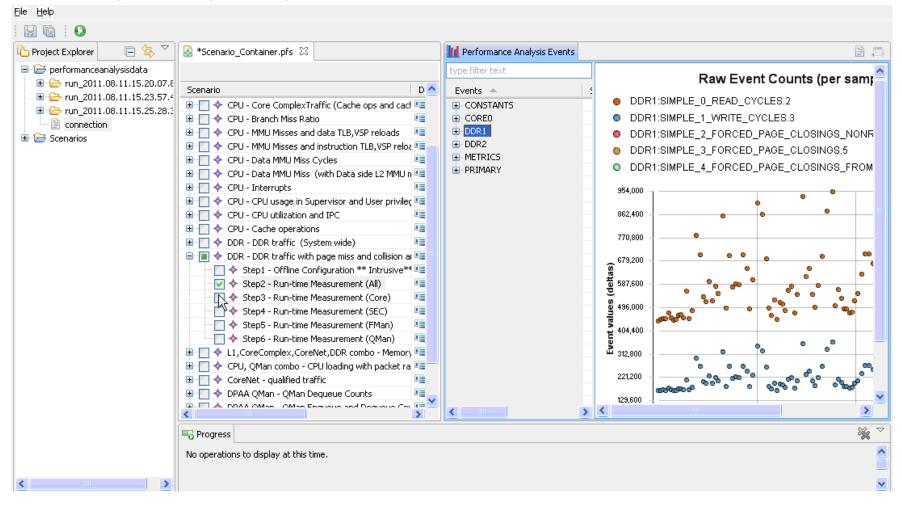

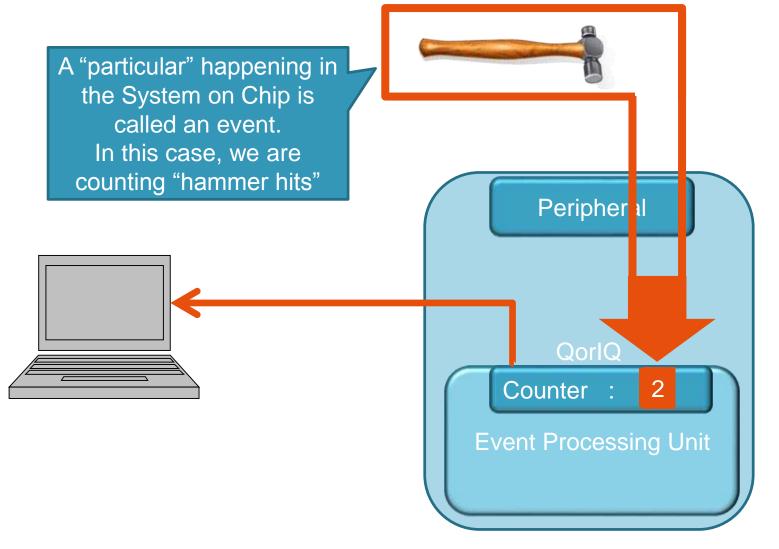

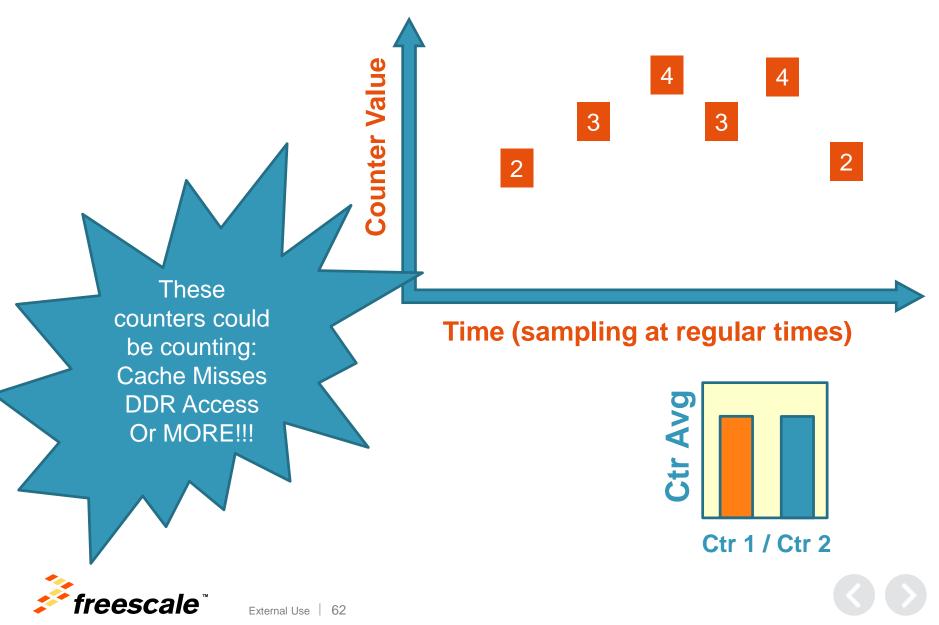

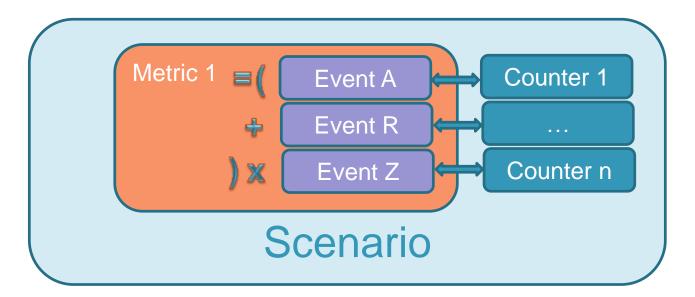

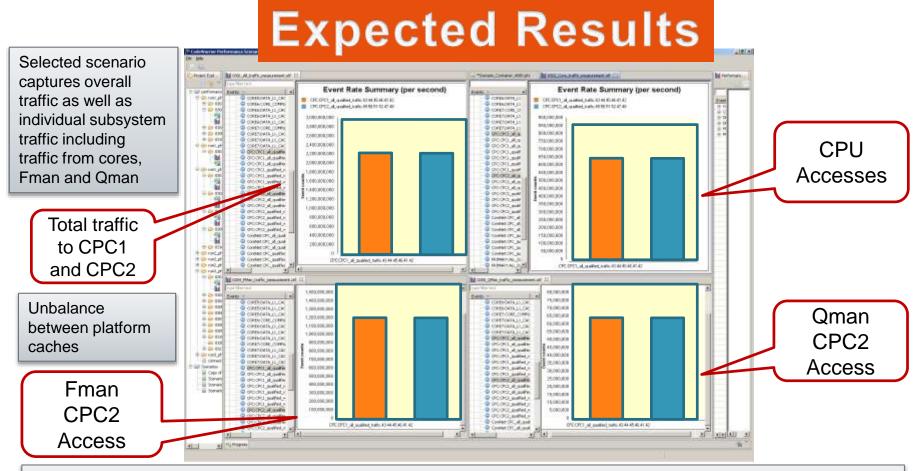

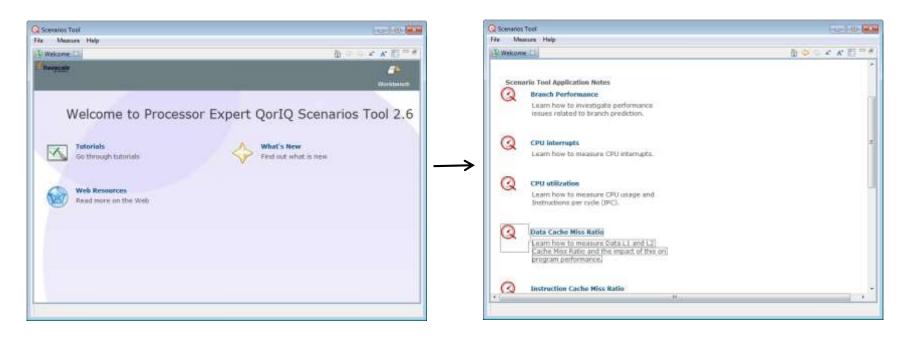

- Scenarios tool for collecting and visualizing runtime trace data

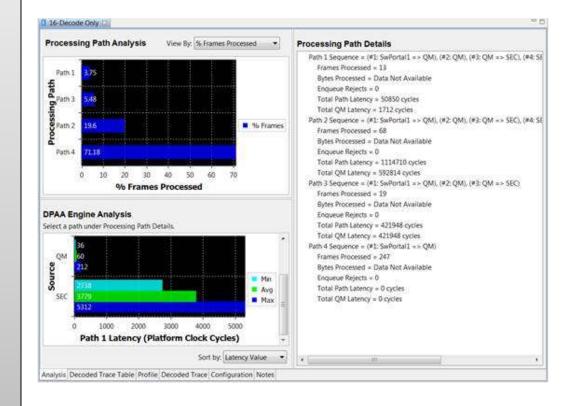

- Packet tool for understanding the flow of packets within a QorIQ device

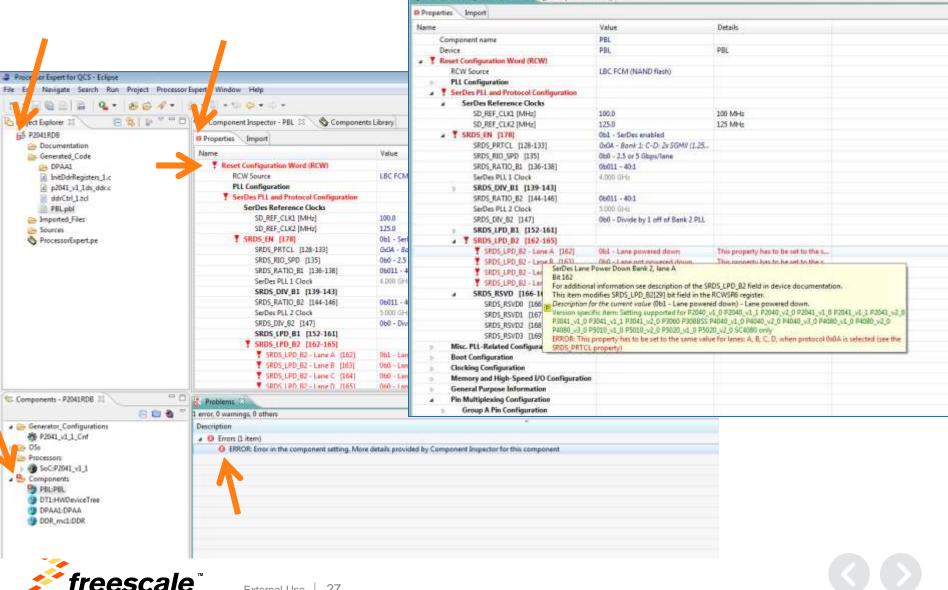

# **QorIQ Configuration Suite**

The configuration suite supports the generation of valid configurations of a QorIQ / Qonverge part for a custom board design complimentary to boot loaders (aka uboot).

**Pre-boot loader / RCW configuration** Defines the Reset Control Word configuration for pre-boot configuration

**DDR Configuration Tool** Configures the DDR controllers, supports SPD, validates configuration on-chip

#### **Boot ROM Tool**

Supports configuration of pin strapping and Bootrom process in P1/P2 devices

### Device Tree Editor

Supports visual editing of device trees

External Use 23

## Why QorlQ Configuration Suite?

- Configuration of QorIQ processors is increasing in complexity

- Even more complexity is around the corner

- We support many, many configuration settings

- Reference manuals are huge and intimidating to new customers

- Configuration problems during board bring-up are HARD and COSTLY

- Learning command line tools requires more training, etc.

- Solution/Strategy to solve these problems:

- Extensible suite of tools with a common user interface

- Consolidate into a common tools framework (Processor Expert)

- Provide new device support aligned with silicon roadmap

- Add more configuration tools over time

- Allow customers to add their own configuration tools to extend what we offer

## **Processor Expert for QorIQ – Configuration Suite**

| Propert Englanes 12 England and an an a                                | S "Component Ingrestor - PBL 51 S Components                                                                                                                                                                                                                                                                                                                                                                                        | Liking                              |                                                                        |                                                                                                    |                                                                                                |                                          |          |                                  |                                          |                                           | Baux /                            | interest Supert In       | -          |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------|----------|----------------------------------|------------------------------------------|-------------------------------------------|-----------------------------------|--------------------------|------------|

| 15 P2041RD8                                                            | Properties Impart                                                                                                                                                                                                                                                                                                                                                                                                                   |                                     |                                                                        |                                                                                                    |                                                                                                |                                          |          |                                  |                                          |                                           |                                   |                          |            |

| Securimentation<br>Securimentation                                     | Name                                                                                                                                                                                                                                                                                                                                                                                                                                | . SHDS,PRTCL (12)                   | 8-1331                                                                 |                                                                                                    |                                                                                                |                                          |          |                                  |                                          |                                           |                                   |                          |            |

| Les DPAAL                                                              | Component name                                                                                                                                                                                                                                                                                                                                                                                                                      | SHDS, PRTCL                         |                                                                        |                                                                                                    |                                                                                                | Bank J                                   |          |                                  |                                          | rik J                                     |                                   | Barrit 3                 |            |

| a bitDubflegisters_Lc                                                  | Device<br>Reset Configuration Word (RCW)                                                                                                                                                                                                                                                                                                                                                                                            |                                     | A B                                                                    | ¢ .                                                                                                | 0                                                                                              | 1 F G H                                  | 1.1.1    | A                                | 8                                        | . C                                       | 0                                 | A 8 C                    | U          |

| ddrCet.3.ad                                                            | Reset Configuration Word (W.W)<br>BCW Source                                                                                                                                                                                                                                                                                                                                                                                        | 0.640                               | Reperved                                                               |                                                                                                    | 2e1<br>156i                                                                                    | PCIe 2<br>(5/2.56)                       | Reserved |                                  |                                          | Cle 3<br>7 10i                            |                                   | Peterved                 |            |

| Pill.phi<br>Important Film                                             | PLL Configuration<br>SerDes PLL and Protocol Configuration                                                                                                                                                                                                                                                                                                                                                                          | - Outs                              | Reserved                                                               | 10                                                                                                 | 0.2                                                                                            | 680 1<br>(5/1123/2.56)                   | Received | \$GM81<br>(3.125/                | 50ME2<br>(0.125/                         | SGME3<br>(3.125/                          | SGME 4<br>(3.325/                 | Revenuel                 |            |

| in Searces                                                             | SerDes Reference Clocks                                                                                                                                                                                                                                                                                                                                                                                                             |                                     | Reserved                                                               |                                                                                                    | 81                                                                                             | (80)                                     | Reserved | 1250 (1)<br>SOMET                | 3,2500 (*3)                              | 1.25(0 (*1)<br>SGME 1                     | 1.2500 (*3)<br>SGME 4             | Reserved                 |            |

| S ProcessorEspert.pe                                                   | SD_NEF_CLK3 [MH4]<br>SD_NEF_CLK3 [MH4]                                                                                                                                                                                                                                                                                                                                                                                              | # 0.40                              | (interested)                                                           |                                                                                                    | 150)                                                                                           | (\$/2.36)                                | HODINI   | (3.1250/<br>1.2500 (*1)          | (3.1256/<br>1.2562 (*1)                  | 13.1250/                                  | (3.3256/<br>1.256) (°3)           | (2011)                   |            |

|                                                                        | SRDS_EN_[178]<br>SRDS_PETCL_[128-134]                                                                                                                                                                                                                                                                                                                                                                                               | 0 0403                              | Reserved                                                               |                                                                                                    | 0.2                                                                                            | Ptle 2<br>(5/7.56)                       | Reserved | \$0M81<br>(0.125/                | SGM8.1<br>(0.125/                        | 50ME 3<br>(8325/                          | 50ME 4<br>(3.325/                 | Reserved                 |            |

|                                                                        | SRD5_RATIO_R0_LL181<br>SRD5_RATIO_R1_LL18-L181                                                                                                                                                                                                                                                                                                                                                                                      |                                     | Baserved                                                               | PCk1                                                                                               | PCH2                                                                                           | 100 g 00 g                               | Reserved | 1.2560 (*1)<br>50MB1             | 3.2500 (°3)<br>50M8.2                    | 1.2560 (*3)<br>SOME 3                     | 1.250) (*1)<br>SGME 4             | Reserved                 |            |

|                                                                        | SerDes PLL 1 Clock<br>SRDS_DEV_81_(139-143)                                                                                                                                                                                                                                                                                                                                                                                         | * 0.04                              |                                                                        | 0/2300                                                                                             | 6/2.50)                                                                                        | (5/2.50) (5/2.50)                        |          | (0.125/<br>1.25(0/21)            | (0.125/<br>1.25(0-(*3)                   | (0.125/<br>1.2500 (*1)                    | 0335/<br>1.2500 (**)              |                          |            |

|                                                                        | SRD5_07V_81 - Lanes A/8 (1.99)<br>SRD5_07V_81 - Lanes C/0 (140)<br>SRD5_07V_81 - Lanes C/F (141)                                                                                                                                                                                                                                                                                                                                    | 0.45                                | Reserved                                                               | PCk1<br>0/2300                                                                                     | PCk3<br>(5/236)                                                                                | PCIe 2<br>(5/230)                        | Reserved | 50/01<br>(3.1250/<br>1.250) (*1) | 50M82<br>(3.1250/<br>1.250 (*1)          | 50ME3<br>(3.3250/<br>1.250) (*1)          | 56ME4<br>8.3256/<br>1.25(0 (*3)   | Reserved                 |            |

|                                                                        | SHD5_DIV_RL - Laves G/H (142)<br>SHD5_DIV_RL - Laves G/H (142)<br>SHD5_DIV_RL - Laves V/ D42)                                                                                                                                                                                                                                                                                                                                       | 0.0406                              | Reserved                                                               | \$0M81<br>0.2500                                                                                   | 30A48.2<br>0.2503                                                                              | PCte I<br>CM2.5G                         | Reserved | PCh 3<br>(5/2.30)                | 30ME5<br>0.2503                          | 3GME 8<br>(0.250)                         | 10ME 4<br>(L.25G)                 | Reserved                 |            |

|                                                                        | SHDS, KATIO_R2 (344-346)<br>SerDes PLL 2 Clock                                                                                                                                                                                                                                                                                                                                                                                      | 0.8407                              | Reserved                                                               | \$5ME1<br>(0.250)                                                                                  | \$6ME2<br>(3.250)                                                                              | PCIe 2<br>(5/2.50)                       | Reserved | Betog<br>(5/3.125/               | \$0ME5<br>(0.125/                        | 5GME3<br>(3.525/                          | SGME4<br>(3.525/                  | Reserved                 |            |

| Components - #2940#08 12                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.0408                              | Reserved                                                               | 30481                                                                                              | SGALE 2                                                                                        | PCIe 2                                   | Received | 2.5(l) (*1)<br>Res               | 1.25(0/P1)<br>reved                      | 1.250) (*1)<br>SATA 1                     | 1.250) (°1)<br>SATA 2             | Reserved                 |            |

| 📄 🖬 🖏 🕈                                                                | SRD1_LPO_R1 - Larra A (LSJ)                                                                                                                                                                                                                                                                                                                                                                                                         | 0.049                               | Reserved                                                               | 0.2500                                                                                             | 0.2500<br>\$6M812                                                                              | (S/2.5G)<br>PCIe 2                       | Reserved |                                  | XAL                                      | 0/1.500<br>13668C                         | 0/130                             | Neserved                 |            |

| #254L_vE_3_Cvt<br>OSx                                                  | 38D5_LPD_81 - Lave 8 (153)<br>58D5_LPD_81 - Lave C (154)                                                                                                                                                                                                                                                                                                                                                                            | O daba                              | Reserved                                                               | 0.2500<br>SOMR 1                                                                                   | (1.250)<br>SGM2.2                                                                              | 0/2.50)<br>PCIe J                        | Reserved |                                  |                                          | Cle 3                                     |                                   | Reserved                 |            |

| as Processon                                                           | SRD5_LPO_81 - Lane D [135]<br>SRD5_LPO_81 - Lane E [136]                                                                                                                                                                                                                                                                                                                                                                            | 0.0408                              | Reserved                                                               | (1.250)<br>508481                                                                                  | (1.350)<br>50948.2                                                                             | 6/236)<br>1/00 1                         | Reserved | POLI                             | SOMES                                    | SGME F                                    | SGMEA                             | Reserved                 |            |

| <ul> <li>SaCP2043_v1_1</li> <li>Camponentic</li> <li>PBUFBU</li> </ul> | 9825, LPO, 81 - Lane F (157)<br>SRD5, JPO, 81 - Lane G (158)<br>SRD1, LPO, 81 - Lane H (159)                                                                                                                                                                                                                                                                                                                                        | E adc                               | Reserved                                                               | (1.25G) (*2)<br>SGME1<br>(1.25G)                                                                   | 0.256) (*2)<br>SGM8.2<br>(1.256)                                                               | 0/236 er 33256) (72)<br>x80 3<br>(3/256) | Reserved | (5/230)<br>Dahug<br>(5/2325V     | 0.350)<br>50M15<br>0.125/<br>1.2560 (*1) | (1.350)<br>50548.3<br>(3.125/             | (1.256)<br>SOME 4<br>(3.325/      | Received                 |            |

| DTLHRDeviceTree<br>DPAALDPAA                                           | SRD5_LFO_81 - Lave 1 (169)<br>SRD5_LFO_81 - Lave 1 (161)                                                                                                                                                                                                                                                                                                                                                                            | 0460                                | Reserved                                                               | 55M81<br>0.350                                                                                     | SGME2<br>(1.350)                                                                               | (40)<br>(A/230)                          | Reserved | 2.59( (*1)<br>Rm                 | 1.256((1)                                | 1.2500 (*1)<br>SATA 1<br>(1/1.500         | 1.250) (*1)<br>SATA 2<br>(3/1.30) | Reserved                 |            |

| DOIL_mcLiDDB                                                           | SRD5_LPD_B2 [162-163]<br>SRD5_LPD_82 - Lave A (102)                                                                                                                                                                                                                                                                                                                                                                                 | O GADE                              | Received                                                               | 305481                                                                                             | SGM8.2                                                                                         | 1990 S                                   | Reserved |                                  |                                          | Cia 3                                     | 11.001100                         | Reserved                 |            |

|                                                                        | SRD5_LP0_82 [162-165]                                                                                                                                                                                                                                                                                                                                                                                                               | 0 0.6E                              | Reserved<br>SRDS_PATCL[31.3<br>oversil volue (0x0<br>to Setting respon | (1.250)<br>50848 1<br>0.7900<br>25) N# Tekkt in the f<br>12 - Bank 1: C-D: P<br>Had for P2040, v1, | (1.250)<br>50248.2<br>9 3470<br>RCW585 register<br>Chil (5/2.50); E-H<br>0 92040; yit, 3 P0540 | (5/2.96)                                 | Received | L C D PON O                      | р<br>А<br>3/2300 С.Н. Я                  | 0/1.50<br>Gel 1<br>7.50<br>KU 0/2.50; Bar | 0/130                             | Fasar<br>47 0.255 er 312 | red<br>500 |

|                                                                        | - PRatf Con                                                                                                                                                                                                                                                                                                                                                                                                                         |                                     |                                                                        |                                                                                                    |                                                                                                |                                          |          |                                  |                                          |                                           |                                   |                          |            |

|                                                                        | pecencen: AASS AASS ELET CLOB 1014 DODD<br>excession: LC12 Codd codd Dodd Dodd Dodd<br>excession: CCD Codd alle Orde Dodd Dodd<br>excession: CCD Codd alle Orde Dodd Dodd<br>excession: CCD Codd Dodd Dodd Dodd Dodd<br>excession: CCD Codd Dodd Dodd Dodd Dodd Dodd<br>excession: CCD Codd Dodd Dodd Dodd Dodd Dodd Dodd<br>excession: CCD Codd Dodd Dodd Dodd Dodd Dodd Dodd<br>excession: CCD Codd Dodd Dodd Dodd Dodd Dodd Dodd | 0000 0000<br>0000 0000<br>0000 0000 |                                                                        |                                                                                                    |                                                                                                |                                          |          |                                  |                                          |                                           |                                   |                          |            |

# **Pre-Boot Loader**

**RCW Configuration Tool**

## **Pre-Boot Loader (RCW) Configuration**

S \*Component Inspector - PIIL COM S Components Library

## **Pre-Boot Loader Standard Component Interface**

- Pre-Boot Loader (PBL) tool establishes all Reset Control Word settings

- PLL Configurations

- SerDes Configuration

- Pin Muxing Configuration

- Output format selection

- Possibility to add PBI data

### Possibility to import RCW settings

| Properties Import                       |                      |        |

|-----------------------------------------|----------------------|--------|

| Name                                    | Value                | Detail |

| Component name                          | PBL                  |        |

| Device                                  | PBL                  | PBL    |

| Reset Configuration Word (RCW)          |                      |        |

| RCW Source                              | LBC FCM (NAND flash) |        |

| PLL Configuration                       |                      |        |

| SerDes PLL and Protocol Configuration   |                      |        |

| Misc. PLL-Related Configuration         |                      |        |

| Boot Configuration                      |                      |        |

| Clocking Configuration                  |                      |        |

| Memory and High-Speed I/O Configuration | n                    |        |

| General Purpose Information             |                      |        |

| Pin Multiplexing Configuration          |                      |        |

| b Group A Pin Configuration             |                      |        |

| ⊿ PBI Data                              |                      |        |

| PBI Data input                          | (string list)        |        |

| PBL Data                                |                      |        |

| Offset                                  | 0                    | H      |

| Output Format                           | XXD Object Dump      |        |

|                                         |                      |        |

# **DDR Configuration**

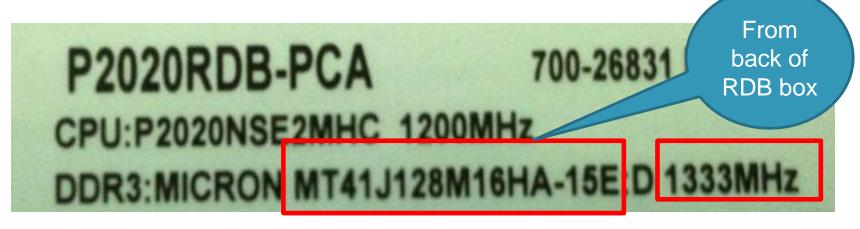

## **Get DRAM Information – P2020RDB-PCA**

# **DDR3 SDRAM**

MT41J512M4 – 64 Meg x 4 x 8 Banks

MT41J256M8 – 32 Meg x 8 x 8 Banks

External Use 30

MT41J128M16 – 16 Meg x 16 x 8 Banks

From DRAM datasheet

## How about the Rest of the Timing Parameters?

#### Table 1: Key Timing Parameters

| Speed Grade                | Data Rate (MT/s) | Target <sup>t</sup> RCD- <sup>t</sup> RP-CL | <sup>t</sup> RCD (ns) | <sup>t</sup> RP (ns) | CL (ns) |

|----------------------------|------------------|---------------------------------------------|-----------------------|----------------------|---------|

| -093 <sup>1, 2, 3, 4</sup> | 2133             | 14-14-14                                    | 13.09                 | 13.09                | 13.09   |

| -107 <sup>1, 2, 3</sup>    | 1866             | 13-13-13                                    | 13.91                 | 13.91                | 13.91   |

| -125 <sup>1, 2,</sup>      | 1600             | 11-11-11                                    | 13.75                 | 13.75                | 13.75   |

| -15E <sup>1,</sup>         | 1333             | 9-9-9                                       | 13.5                  | 13.5                 | 13.5    |

| -187E                      | 1066             | 7-7-7                                       | 13.1                  | 13.1                 | 13.1    |

- Tool automatically computes tRCD, tRP, and CL!

- User can change these values if required.

#### Features

- $V_{DD} = V_{DDQ} = 1.5V \pm 0.075V$

- 1.5V center-terminated push/pull I/O

- Differential bidirectional data strobe

- 8n-bit prefetch architecture

- Differential clock inputs (CK, CK#)

- · 8 internal banks

- Nominal and dynamic on-die termination (ODT) for data, strobe, and mask signals

- Programmable CAS READ latency (CL)

- Posted CAS additive latency (AL)

- Programmable CAS WRITE latency (CWL) based on <sup>1</sup>CK

- Fixed burst length (BL) of 8 and burst chop (BC) of 4 (via the mode register set [MRS])

- Selectable BC4 or BL8 on-the-fly (OTF)

- · Self refresh mode

- +  $T_{\rm C}$  of 0°C to 95°C

- 64ms, 8192 cycle refresh at 0°C to 85°C

- 32ms, 8192 cycle refresh at 85°C to 95°C

- Self refresh temperature (SRT)

- Write leveling

- Multipurpose register

- Output driver calibration

| Options <sup>1</sup>                                     | Marking     |

|----------------------------------------------------------|-------------|

| <ul> <li>Configuration</li> </ul>                        | 12000000000 |

| - 512 Meg x 4                                            | 512M4       |

| – 256 Meg x 8                                            | 256M8       |

| - 128 Meg x 16                                           | 128M16      |

| <ul> <li>FBGA package (Pb-free) – x4, x8</li> </ul>      |             |

| - 78-ball (8mm x 10.5mm) Rev. H.M.LK                     | DA          |

| - 78-ball (9mm x 11.5mm) Rev. D                          | HX          |

| <ul> <li>FBGA package (Pb-free) – x16</li> </ul>         |             |

| - 96-ball (9mm x 14mm) Rev. D                            | HA          |

| - 96-ball (8mm x 14mm) Rev. K                            | IT          |

| <ul> <li>Timing – cycle time</li> </ul>                  |             |

| – 938ps @ CL = 14 (DDR3-2133)                            | -093        |

| <ul> <li>1.071ns @ CL = 13 (DDR3-1866)</li> </ul>        | -107        |

| - 1.25ns @ CL = 11 (DDR3-1600)                           | -125        |

| - 1.5ns@CL=9(DDR3-1333)                                  | -15E        |

| - 1.87ns ⊕ CL = 7 (DDR3-1066)                            | -187E       |

| <ul> <li>Operating temperature</li> </ul>                |             |

| - Commercial ( $0^{\circ}C \le T_C \le +95^{\circ}C$ )   | None        |

| - Industrial ( $-40^{\circ}C \le T_C \le +95^{\circ}C$ ) | IT          |

| Revision                                                 | :D/:H/:J/:K |

| 000000                                                   | :M          |

Note: 1. Not all options listed can be combined to define an offered product. Use the part catalog search on http://www.micron.com for available offerings.

## **DDR Wizard Simplifies Configuration**

| New Qor      | IQ Configuration Project                                               |                                           |

|--------------|------------------------------------------------------------------------|-------------------------------------------|

| DDR Con      | figuration                                                             |                                           |

| Configure    | d device P2020                                                         |                                           |

| Configure:   | 1st DDR Controller                                                     | •]                                        |

| ⊚ Au<br>⊘ Im | tion mode<br>ito configuration<br>port from memory file<br>screte DRAM | Module                                    |

| DDR Cont     | troller                                                                | DRAM Settings                             |

| Туре         | DDR 3 👻                                                                | DRAM Configuration per Rank 1Gb: 128Mb x8 |

| Data Rate    | 800 MT/s 🔻                                                             | DRAM Speed Rating                         |

| Ranks        | 1 🔹                                                                    |                                           |

| Data Bus     | width 64 bits 🔻                                                        |                                           |

| CAS# Late    | ency (tCL) 6 clocks 🔻                                                  |                                           |

| tRP/tRCD     | 13.5 ns 🔻                                                              |                                           |

| ECC Er       | nabled                                                                 |                                           |

| Select 1st   | DDR Controller                                                         | *                                         |

| ?            | < <u>B</u> ack                                                         | <u>N</u> ext > <u>Finish</u> Cancel       |

- From memory data sheet:

- Maximum speed rating

- Capacity

## **QCS Project Explorer**

| 🗄 Project Panel 🛛 📃 🗖                                        | Scomponent Inspector                                                                |                                                      |                         |

|--------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------|-------------------------|

|                                                              | Properties Import Export Validati                                                   | on                                                   |                         |

| ⊿ 😂 p2020rdb-pca1                                            | Name                                                                                | Value                                                | Details                 |

| Documentation Generated_Code                                 | Device                                                                              | DDR_Controller_1                                     | DDR_Controller_1        |

| Sources Sources Sources Sources Sources                      | Memory type<br>DDR Bus Clock                                                        | DDR 3<br>400 MHz                                     | DDR Data Rate: 800 MT/s |

| a 🗁 Configurations                                           | Type of DIMM<br>Bus mode                                                            | Unbuffered DIMMs<br>64-bit bus                       |                         |

| P2020_Cnf<br>Operating System                                | ▲ SDRAM Control Configuration                                                       |                                                      |                         |

| <ul> <li>Processors</li> <li></li></ul>                      | Control Configuration 1     Control Configuration 2                                 |                                                      |                         |

| <ul> <li>Embedded Components</li> <li>DDR_mc1:DDR</li> </ul> | SDRAM Timing Configurations     Auto-adjust chip select addressin     Chip Select 0 | yes<br>Enabled                                       |                         |

|                                                              | <ul> <li>Chip Select 0</li> <li>Memory Bounds</li> </ul>                            |                                                      |                         |

|                                                              | Start Address<br>Size                                                               | 0 H<br>1 GB                                          |                         |

|                                                              | ▲ Configuration                                                                     |                                                      |                         |

|                                                              | Auto Precharge Always<br>Internal Banks Number                                      | no<br>8 internal banks                               |                         |

|                                                              | Number of row bits                                                                  | 14 row bits                                          |                         |

|                                                              | Number of column bits<br>ODT for writes configurati                                 | 10 column bits<br>Assert ODT only during writes to C |                         |

|                                                              | ODT for reads configuration                                                         | Never assert ODT for reads                           |                         |

|                                                              | Partial array self refresh<br>Chip Select 1                                         | Full Array<br>Disabled                               |                         |

|                                                              | Chip Select 2                                                                       | Disabled                                             |                         |

|                                                              | b Chip Select 3                                                                     | Disabled                                             |                         |

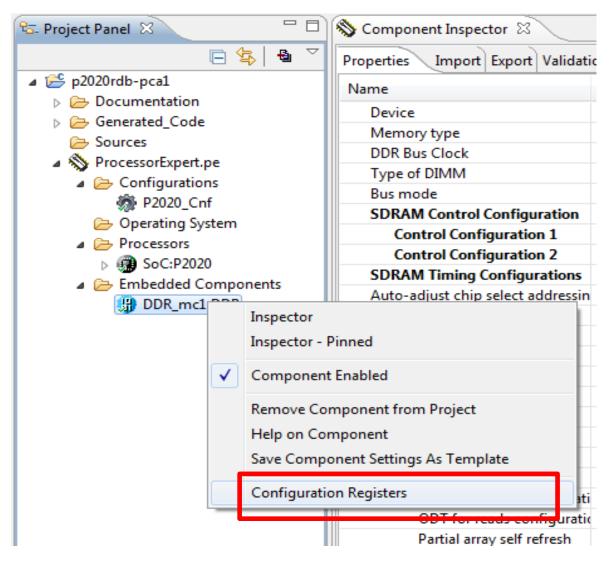

## **Review DDR Registers Values**

## **Review DDR Registers Values (continued)**

| Reg. name            | Init. value | After reset |

|----------------------|-------------|-------------|

| Peripheral registers |             |             |

| DDR1_CS0_BNDS        | 000003F     | 00000000    |

| DDR1_CS1_BNDS        | 00000000    | 00000000    |

| DDR1_CS2_BNDS        | 00000000    | 00000000    |

| DDR1_CS3_BNDS        | 00000000    | 00000000    |

| DDR1_CS0_CONFIG      | 80014202    | 00000000    |

| DDR1_CS1_CONFIG      | 0000000     | 00000000    |

| DDR1_CS2_CONFIG      | 00000000    | 00000000    |

| DDR1_CS3_CONFIG      | 00000000    | 00000000    |

| DDR1_CS0_CONFIG_2    | 00000000    | 00000000    |

| DDR1_CS1_CONFIG_2    | 00000000    | 00000000    |

| DDR1_CS2_CONFIG_2    | 00000000    | 00000000    |

| DDR1_CS3_CONFIG_2    | 00000000    | 00000000    |

| DDR1_TIMING_CFG_3    | 00030000    | 00000000    |

| DDR1_TIMING_CFG_0    | 00330104    | 00110105    |

| DDR1_TIMING_CFG_1    | 6E6B8846    | 00000000    |

| DDR1_TIMING_CFG_2    | 0FA8D0CC    | 00000000    |

| DDR1_SDRAM_CFG       | 47000008    | 03000000    |

| DDR1_SDRAM_CFG_2     | 24401050    | 00000000    |

| DDR1_SDRAM_MODE      | 00061421    | 00000000    |

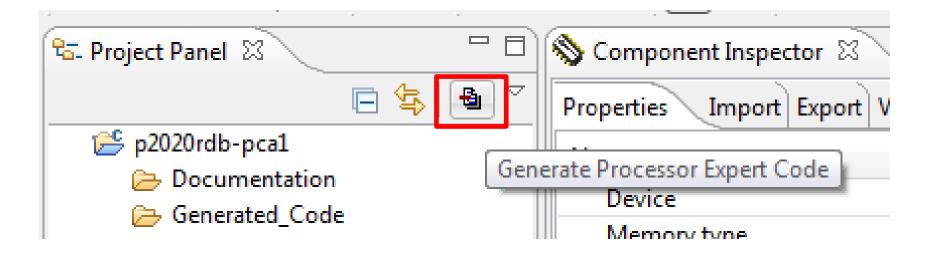

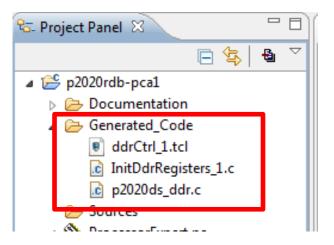

## **Generate DDR Configuration**

## **Generated Files – CW, uboot, ddrinit.c**

| # DDR Controller 1 Registers                  | #define DDR_1_INIT_EXT_ADDR_ADD           | DR 0xFF70214C                              |                      |               |

|-----------------------------------------------|-------------------------------------------|--------------------------------------------|----------------------|---------------|

|                                               | <pre>#define DDR_1_SDRAM_RCW_1_ADDR</pre> |                                            |                      |               |

| # DDR SDRAM CFG                               | <pre>#define DDR_1_SDRAM_RCW_2_ADDR</pre> |                                            |                      |               |

| mem $[0xFF702110] = 0x47000008$               | <pre>#define DDR_1_DATA_INIT_ADDR</pre>   | 0xFF702128                                 |                      |               |

| mem [CALL/OLIES] CALLOUDE                     | #define DDR_1_SDRAM_MD_CNTL_ADD           | DR 0xFF702120                              |                      |               |

| # CS0 BNDS                                    | <pre>#define DDR_1_DDRCDR_1_ADDR</pre>    | 0xFF702B28                                 |                      |               |

| $mem [0_{x}FF702000] = 0_{x}3F$               | <pre>#define DDR_1_DDRCDR_2_ADDR</pre>    | 0xFF702B2C                                 |                      |               |

|                                               | #define SDRAM CFG MEM EN MASK             | 0x80000000                                 |                      |               |

| # CSO_CONFIG<br>mem [0xFF702080] = 0x80014202 | #define SDRAM_CFG2_D_INIT_MASK            | 0x0000010                                  |                      |               |

|                                               | /* DDR Controller configured re           | -                                          |                      |               |

| # CS0_CONFIG_2                                | <pre>#define DDR_1_CS0_BNDS_VAL</pre>     | 0x3F                                       |                      |               |

| mem $[0_{x}FF7020C0] = 0_{x}00$               | <pre>#define DDR_1_CS1_BNDS_VAL</pre>     |                                            |                      |               |

|                                               | <pre>#define DDR_1_CS2_BNDS_VAL</pre>     | 0x00                                       |                      |               |

| <pre># TIMING_CFG_3</pre>                     | <pre>#define DDR_1_CS3_BNDS_VAL</pre>     | 0x00                                       |                      |               |

| mem $[0xFF702100] = 0x00030000$               | <pre>#define DDR_1_CS0_CONFIG_VAL</pre>   | 0x80014202                                 |                      |               |

|                                               | <pre>#define DDR_1_CS1_CONFIG_VAL</pre>   | 0x00                                       |                      |               |

| <pre># TIMING_CFG_0</pre>                     |                                           |                                            |                      |               |

| mem [0xFF702104] = 0x00330104                 |                                           | #define PEX_CONFIG_DD                      | R1 INIT EXT ADDR     | 0x00000000    |

|                                               |                                           | #define PEX CONFIG DD                      | R1 TIMING 4          | 0x00220001    |

| <pre># TIMING_CFG_1</pre>                     |                                           | #define PEX_CONFIG_DD                      | R1_TIMING_5          | 0x02401400    |

| mem [0xFF702108] = 0x6E6B8846                 |                                           | #define PEX CONFIG DD                      | R1 ZO CNTL           | 0x89080600    |

|                                               |                                           | #define PEX_CONFIG_DD                      | R1_WRLVL_CNTL        | 0x8655F614    |

| # TIMING CFG 2                                |                                           | #define PEX_CONFIG_DD                      |                      | 0x00000000    |

| mem $[0xFF70210C] = 0x0FA8D0CC$               |                                           | #define PEX_CONFIG_DD                      | R1_RCW_2             | 0x00000000    |

|                                               |                                           |                                            |                      |               |

| # DDR SDRAM CFG 2                             |                                           |                                            |                      |               |

| mem $[0xFF702114] = 0x24401050$               |                                           | /* DDR Controller 1 c                      |                      | structures */ |

|                                               |                                           | fsl_ddr_cfg_regs_t dd                      |                      |               |

| # DDR SDRAM MODE                              |                                           | .cs[0].bnds = PEX_C                        |                      |               |

| mem $[0xFF702118] = 0x00061421$               |                                           | .cs[1].bnds = PEX_C                        |                      |               |

| mem [CALL/OLIE] CACCOLLE                      |                                           | .cs[2].bnds = PEX_C                        |                      |               |

|                                               |                                           | .cs[3].bnds = PEX_C                        |                      |               |

|                                               |                                           | .cs[0].config = PEX<br>.cs[1].config = PEX |                      |               |

|                                               |                                           | .ca[i].coniig - FEA                        | _CONFIG_DDR1_CD1_COI |               |

.cs[2].config = PEX\_CONFIG\_DDR1\_CS2\_CONFIG,

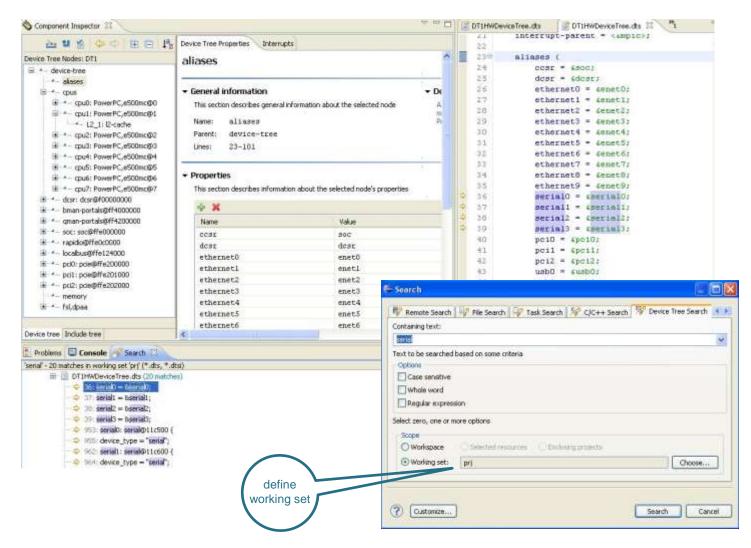

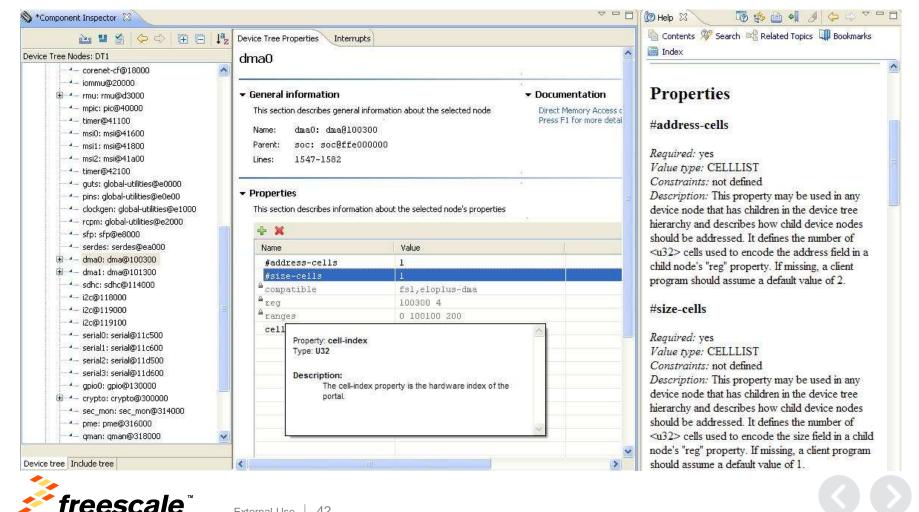

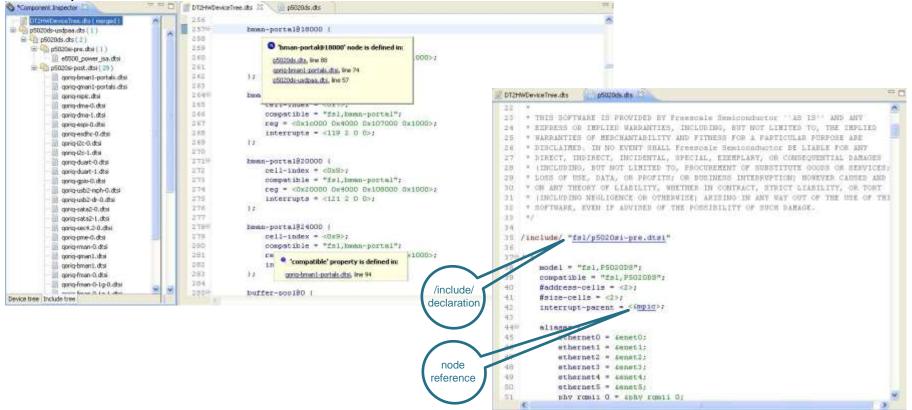

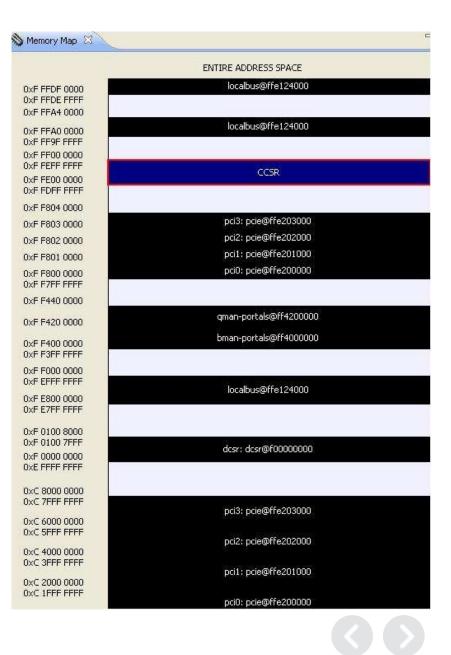

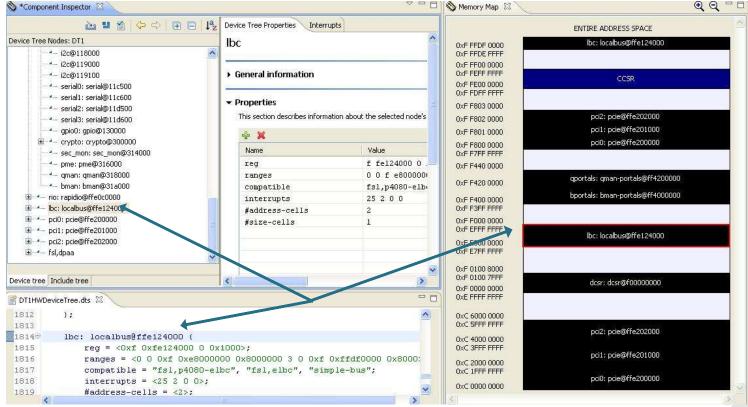

# **Device Tree Editor**

Supports Hardware Device Trees (\*.dts)

# **Hardware Device Tree Workflow**

| <ul> <li>New Optil) Configuration Project</li> </ul>                                                                                       | 10 |

|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| Device Tree Configuration<br>Choose Device Tree Configuration                                                                              |    |

| Saled action:<br>Disposi configuration from an existing device tree file<br>Other default device tree configuration<br>Other configuration |    |

| The a default device the Ne for the chosen SoC.<br>Default device the rADDOB sedges do<br>Source DRAA SDP 2011(2020)                       |    |

| HIDeviceTree                             | Sector I reveal                                                                                                |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------|

|                                          | 「日本」                                                                                                           |

| Ξ device-cree                            |                                                                                                                |

| eleses .                                 |                                                                                                                |

| 岸 thun                                   | 215                                                                                                            |

| 12 0                                     | + lost and                                                                                                     |

| E cpul: Po                               | X Delate nocle                                                                                                 |

| i⊞ cpu2: Po                              | Rename node                                                                                                    |

| in cputs Pa                              |                                                                                                                |

| E quit Pa                                | C Refresh                                                                                                      |

| E COUS PO                                | and a second |

| El cpuár Pe                              | E-pand                                                                                                         |

| Ξ cpi.7: Po                              | Collapse                                                                                                       |

| -rodet                                   | <u> </u>                                                                                                       |

| DEDDTy                                   |                                                                                                                |

| iii brian-portaist                       | 9(14000000                                                                                                     |

| i inter-portast                          |                                                                                                                |

| i soci sco⊈ffe0                          | 00000                                                                                                          |

| republicity require                      | ing Falsting                                                                                                   |

| 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1 | 0.4000                                                                                                         |

#### Generate Code

#### Select Component

| = id-pri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | HACE AND A DESCRIPTION OF A DESCRIPTION OF<br>A DESCRIPTION OF A DESCRIPTIONO |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| · de Documentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ⇒ < 10 P5 in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Construction Code  Code Code | III. do-taz fister         A           -adaptes         B           III. (2004)         III. (2014)           III. (2014)         III. (2014)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |