# Case Study: Some i.MX8X boards eMMC boot failure issue

Yangrui Aug 2023

## Issue Phenomenon

#### **Issue Phenomenon**

- Customer some i.MX8X boards black screen and boot failed issue in their manufacture line;

- 2. The failure rate is 100% in issue boards, but the issue board can boot normally after "heat gun" test, or hand touch eMMC CMD and DATA lines;

- 3. Add debugging logs, find SW halt in bootloader of their QNX's uSDHC driver, dead loop in CMD\_INHIBIT and DATA\_INHIBIT, means uSDHC CMD and DATA lines are always busy and can't use when this issue happened;

| 1     | Command inhibit (DATA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| CDIHB | This status field is generated if either the DAT Line Active or the Read Transfer Active is set to 1. If this field is 0, it indicates that uSDHC can issue the next SD / MMC Command. Commands with a busy signal belong to Command Inhibit (DATA) (for example. R1b, R5b type). Changing from 1 to 0 generates a Transfer Complete interrupt in the Interrupt Status register.                                                                                                                                                                                                                                                               |  |  |  |  |  |

|       | NOTE: The SD host driver can save registers for a suspend transaction after this field has changed from 1 to 0.  0b - Can issue command that uses the DATA line 1b - Cannot issue command that uses the DATA line                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| 0     | Command inhibit (CMD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| CIHB  | If this status bit is 0, it indicates that the CMD line is not in use and uSDHC can issue a SD / MMC command using the CMD line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|       | This field is set also immediately after the Transfer Type register is written. This field is cleared when the command response is received. Even if the Command Inhibit (DATA) is set to 1, commands using only the CMD line can be issued if this field is 0. Changing from 1 to 0 generates a Command Complete interrupt in the Interrupt Status register. If uSDHC cannot issue the command because of a command conflict error (see Command CRC Error) or because of a Command Not Issued By Auto CMD12 Error, this field remains 1 and the Command Complete is not set. The Status of issuing an auto CMD12 does not show on this field. |  |  |  |  |  |

|       | 0b - Can issue command using only CMD line<br>1b - Cannot issue command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

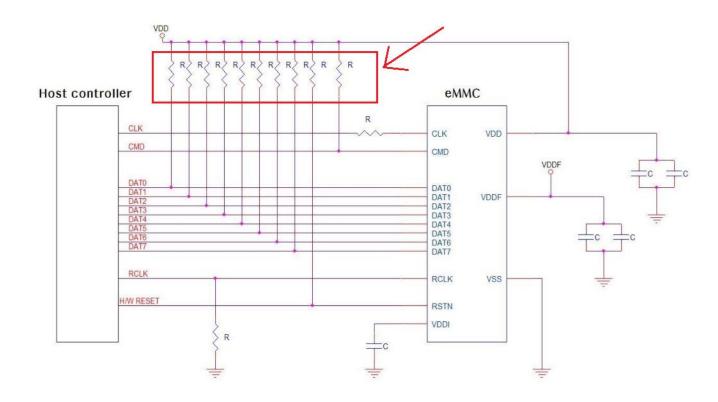

Suggest customer to add external pull-up resistors on eMMC\_CMD and eMMC\_DAT0~7 as following, this issue has gone in i.MX8X issue boards.

### eMMC SPEC JESD84-B51 & JESD84-A441 request user to add pull-up resistance in DAT0~7 and CMD as following:

$$C_{L} = C_{HOST} + C_{RUS} + C_{CARD}$$

and requiring the sum of the host and bus capacitances not to exceed 20 pF (see Table 108).

Table 108 — Capacitance

| Parameter                                | Symbol                          | Min | Тур | Max                | Unit | Remark                                                 |

|------------------------------------------|---------------------------------|-----|-----|--------------------|------|--------------------------------------------------------|

| Pull-up resistance for CMD               | $R_{CMD}$                       | 4.7 |     | 100(1)             | Kohm | to prevent bus floating                                |

| Pull-up resistance for DAT0-7            | R <sub>DAT</sub>                | 10  |     | 100 <sup>(1)</sup> | Kohm | to prevent bus floating                                |

| Internal pull up resistance<br>DAT1–DAT7 | R <sub>int</sub>                | 10  |     | 150                | kohm | to prevent unconnected lines floating                  |

| Bus signal line capacitance              | $C_{L}$                         |     |     | 30                 | pF   | Single card                                            |

| Single card capacitance                  | C <sub>MICRO</sub>              |     |     | 12                 | pF   | For MMCmicro                                           |

|                                          | C <sub>MOBILE</sub>             |     |     | 18                 | Ī    | For MMCmobile and MMCplus                              |

|                                          | C <sub>BGA</sub>                |     | 7   | 12                 | Ī    | For BGA                                                |

| Maximum signal line inductance           |                                 |     |     | 16                 | nН   | $f_{pp} \le 52 \text{ MHz}$                            |

| VDDi capacitor value                     | C <sub>REG</sub> <sup>(2)</sup> | 0.1 |     |                    | μF   | to stablize regulator output to controller core logics |

<sup>(1)</sup> Recommanded maximum pull-up is 50Kohm for 1.2V and 1.8V interface supply voltages.A 3V part, may use the whole range up to 100Kohms.

JEDEC Standard No. 84-B51 Page 247

#### 10.3.4 Bus signal line load

The total capacitance  $C_L$  of each line of the e-MMC bus is the sum of the bus master capacitance  $C_{\text{HOST}}$ , the bus capacitance  $C_{\text{BUS}}$  itself, and the capacitance  $C_{\text{DEVICE}}$  of the Device connected to this line,

$$C_L = C_{HOST} + C_{BUS} + C_{DEVICE}$$

and requiring the sum of the host and bus capacitances not to exceed 20 pF, see Table 200Error! Reference source not found. Error! Reference source not found.

Table 200 — Capacitance and Resistors

| Parameter                                                  | Symbol                          | Min | Тур | Max    | Unit | Remark                                                                                                                                                |

|------------------------------------------------------------|---------------------------------|-----|-----|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pull-up resistance for CMD                                 | R <sub>CMD</sub>                | 4.7 |     | 100(1) | kΩ   | to prevent bus floating                                                                                                                               |

| Pull-up resistance for<br>DAT0-7                           | $R_{DAT}$                       | 10  |     | 100(1) | kΩ   | to prevent bus floating                                                                                                                               |

| Internal pull up resistance<br>DAT1-DAT7                   | R <sub>int</sub>                | 10  |     | 150    | kΩ   | to prevent unconnected lines<br>floating                                                                                                              |

| Bus signal line capacitance                                | $C_L$                           |     |     | 30     | рF   | Single Device                                                                                                                                         |

| Single Device capacitance                                  | C <sub>DEVICE</sub>             |     |     | 6      | pF   |                                                                                                                                                       |

| Maximum signal line inductance                             |                                 |     |     | 16     | nН   | $f_{pp} \le 52 \text{ MHz}$                                                                                                                           |

| $V_{\text{DDi}}$ capacitor value                           | C <sub>REG</sub> <sup>(2)</sup> | 0.1 |     |        | uF   | To stabilize regulator output<br>when target device bus speed<br>mode is either backward-<br>compatible, high speed SDR,<br>high speed DDR, or HS200. |

|                                                            |                                 | 1   |     |        | uF   | To stabilize regulator output<br>when target device bus speed<br>mode is HS400.                                                                       |

| V <sub>DDi2</sub> capacitor value<br>(e <sup>2</sup> •MMC) | $C_{REG2}$                      | 1   |     |        | uF   | To stabilize internal regulated voltage                                                                                                               |

JEDEC Standard No. 84-A441

Page 174

12.6 Bus signal levels

<sup>(2)</sup> Recommended value for C<sub>REG</sub> might be different between e\*MMC device vendors. Please confirm the maximum value and the accuracy of the capacitance with e\*MMC vendor because the electrical characteristics of the regulator inside e\*MMC is affected by the fluctuation of the capacitance.

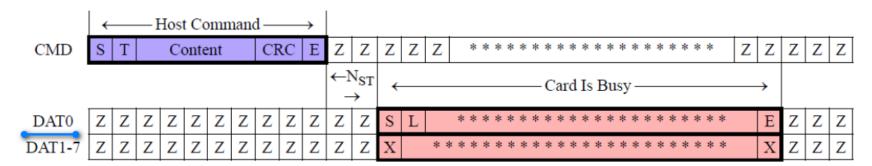

Bootloader of customer's QNX uSDHC driver don't enable i.MX8X IOMUX pull-up in EMMC0\_CMD and EMMC0\_DATA0~7, and customer don't add external pull-up resistors in these eMMC related pads, so DAT0 will become always "Card Is Busy" status as following, i.MX8 uSDHC controller will dead loop in CMD\_INHIBIT and DATA\_INHIBIT.

#### R1b responses

Some commands, like CMD6, may assert the BUSY signal and respond with R1. If the busy signal is asserted, it is done two clock cycles after the end bit of the command. The DAT0 line is driven low, DAT1-DAT7 lines are driven by the Device though their values are not relevant.

Figure 39 — R1b response timing

In i.MX8X Android and Linux, we can find eMMC related pads are configured as IOMUX pull-up as following, so there is no such issue if customer don't add external pull-up resistors in DAT0~7 and CMD when using i.MX8X Android or Linux BSP:

#### In Uboot:

#### In Kernel device tree:

```

pinctrl usdhc1: usdhc1grp {

fsl,pins = <

SC P EMMC0 CLK CONN EMMC0 CLK

0x06000041

SC P EMMC0 CMD CONN EMMC0 CMD

0x00000021

SC P EMMC0 DATA0 CONN EMMC0 DATA0

0x00000021

SC P EMMC0 DATA1 CONN EMMC0 DATA1

0x00000021

SC P EMMC0 DATA2 CONN EMMC0 DATA2

0x00000021

SC P EMMC0 DATA3 CONN EMMC0 DATA3

0x00000021

SC P EMMC0 DATA4 CONN EMMC0 DATA4

0x00000021

SC P EMMC0 DATA5 CONN EMMC0 DATA5

0x00000021

SC P EMMC0 DATA6 CONN EMMC0 DATA6

0x00000021

SC P EMMC0 DATA7 CONN EMMC0 DATA7

0x00000021

SC P EMMC0 STROBE CONN EMMC0 STROBE 0x00000041

>;

```

## Issue Summary

### **Issue Summary**

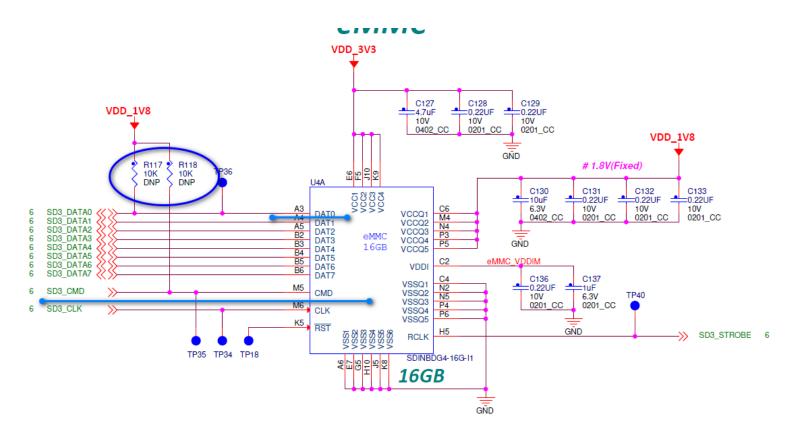

Suggest customer to reserve external pull-up resistors on DAT0~7 and CMD pins to comply with eMMC SPEC, at least DAT0 and CMD as following, but we should care about some eMMC don't have internal pull-up on DAT1~7.

SECURE CONNECTIONS FOR A SMARTER WORLD