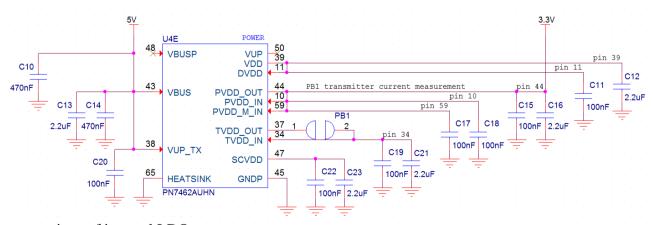

Using contact<u>less</u> interface only with internal RF transmitter power TVDD\_OUT.

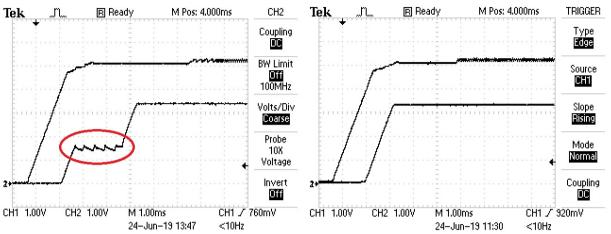

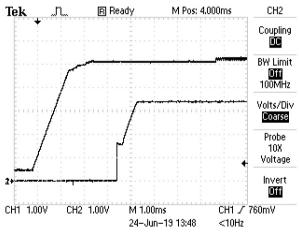

The 3.3V PVDD\_OUT has a 2ms unstable plateau during power up while the PN7462 RESET input is low (active)

1: VBUS 5V, 2: PVDD\_OUT 3.3V

OK if RST\_N is pulled-up to PVDD\_OUT

1: VBUS 5V, 2: RST\_N input

connections of internal LDOs.

Total capacity on PVDD\_OUT 2.2+2.2+0.1+0.1uF. More or less does'nt change anything.

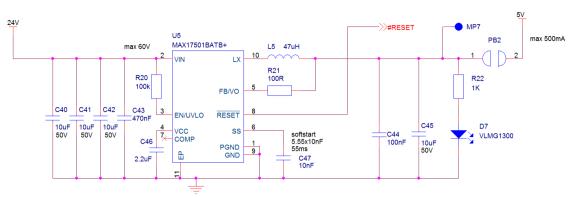

## standard 5V swithmode powersupply

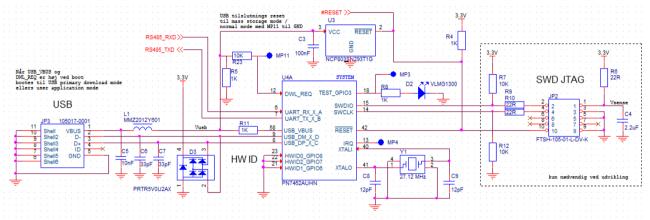

## USB/SWD interface

What is preventing the PVDD\_OUT startup when RST\_N is active?

Why is the RST\_N input pin not listed in the PN7462 family datasheet rev. 4.3, 24 January 2019, chap 8.16.1 table 25 ?