# Generic Timer Module 104 (GTM104) Reference Manual

Document Number: GTM104RM

Rev 1, 3 Feb 2015

#### **Contents**

| Section number |                 | nber Title                                                            | Page |

|----------------|-----------------|-----------------------------------------------------------------------|------|

|                |                 | Chapter 1<br>Introduction                                             |      |

| 1.1            | Overview        | 7                                                                     | 23   |

| 1.2            | Features        |                                                                       | 24   |

| 1.3            | Documen         | t Structure                                                           | 24   |

|                |                 | Chapter 2 GTM Architecture                                            |      |

| 2.1            | GTM Arc         | chitecture Overview                                                   | 27   |

|                | 2.1.1           | GTM Architecture                                                      | 27   |

|                | 2.1.2           | Advanced Routing Unit (ARU) Brief Description                         | 28   |

|                | 2.1.3           | Broadcast Module (BRC) Brief Description                              | 29   |

|                | 2.1.4           | Parameter Storage Module (PSM) Brief Description                      | 29   |

|                | 2.1.5           | Timer Input Modules (TIMs) Brief Description                          | 29   |

|                | 2.1.6           | Clock Management Unit (CMU) Brief Description                         | 30   |

|                | 2.1.7           | Time Base Unit (TBU) Brief Description.                               | 30   |

|                | 2.1.8           | Digital Phase Locked Loop (DPLL) Brief Description                    | 30   |

|                | 2.1.9           | Timer Output Module (TOM) Brief Description                           | 30   |

|                | 2.1.10          | ARU-connected Timer Output Module (ATOM) Brief Description            | 31   |

|                | 2.1.11          | Interrupt Concentrator Module (ICM) Dreif Description                 | 31   |

|                | 2.1.12          | Compare (CMP) Module and Monitor (MON) Module Brief Description       | 32   |

| 2.2            | Signal M        | ultiplex                                                              | 32   |

| 2.3            | Signal Co       | onnectivity Overview                                                  | 33   |

| 2.4            | GTM Interfaces. |                                                                       | 33   |

|                | 2.4.1           | GTM Generic Bus Interface (AEI)                                       | 34   |

|                | 2.4.2           | GTM Multi-master and multi-tasking support                            | 35   |

| 2.5            | ARU Rou         | iting Concept                                                         | 36   |

|                | 2.5.1           | Principle of data routing using ARU                                   | 36   |

|                | 2.5.2           | ARU Round Trip Time                                                   | 39   |

|                |                 | Generic Timer Module 104 (GTM104) Reference Manual, Rev. 1, 3 Feb 201 | 15   |

| Sec  | tion nui | mber Title                                                     | Page |

|------|----------|----------------------------------------------------------------|------|

|      | 2.5.3    | ARU Blocking Mechanism                                         | 39   |

| 2.6  | GTM Cl   | ock and Time Base Management (CTBM)                            | 40   |

| 2.7  | GTM Int  | terrupt Concept                                                | 41   |

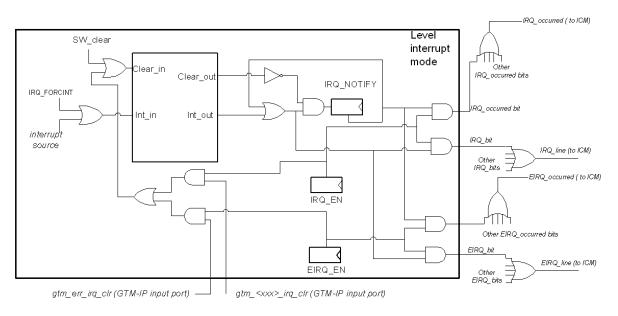

|      | 2.7.1    | Level interrupt mode                                           | 44   |

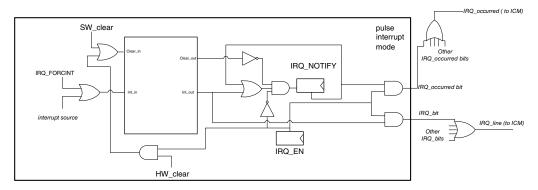

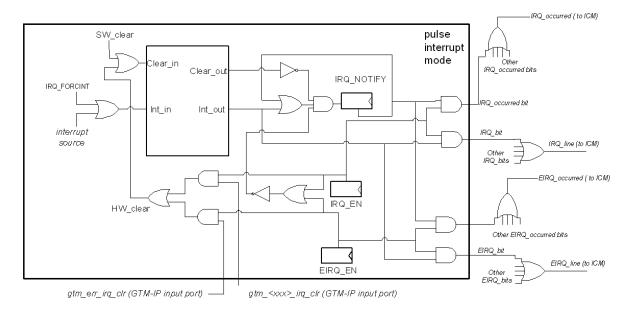

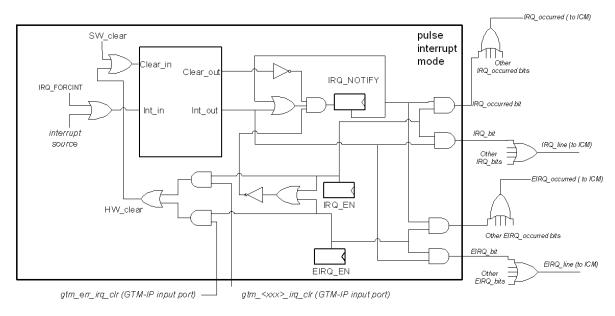

|      | 2.7.2    | Pulse interrupt mode                                           | 46   |

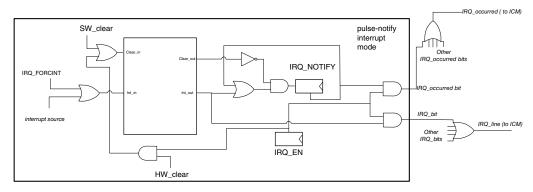

|      | 2.7.3    | Pulse-notify interrupt mode                                    | 47   |

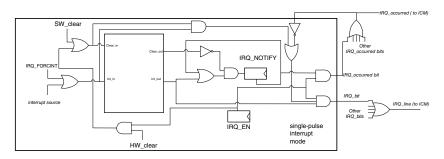

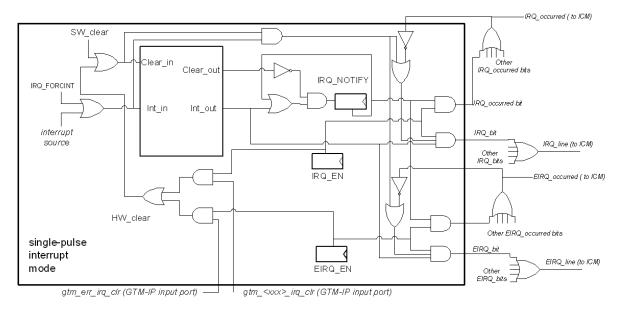

|      | 2.7.4    | Single-pulse interrupt mode                                    | 48   |

|      | 2.7.5    | GTM Interrupt concentration method.                            | 50   |

| 2.8  | GTM So   | ftware Debugger Support                                        | 50   |

| 2.9  | GTM Pro  | ogramming conventions                                          | 51   |

| 2.10 | Memory   | Map and Registers                                              | 51   |

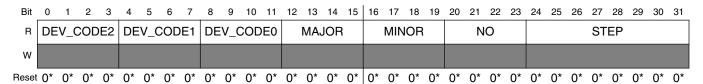

|      | 2.10.1   | GTM Revision Register (GTM_REV)                                | 53   |

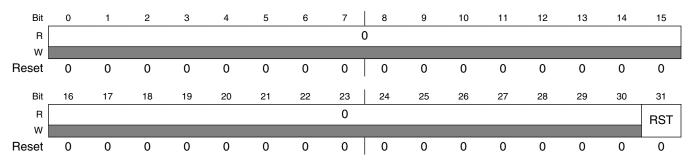

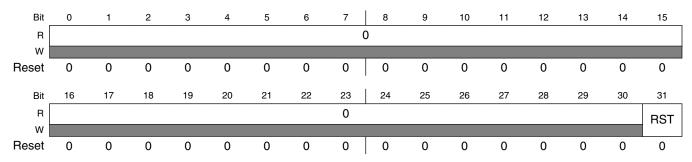

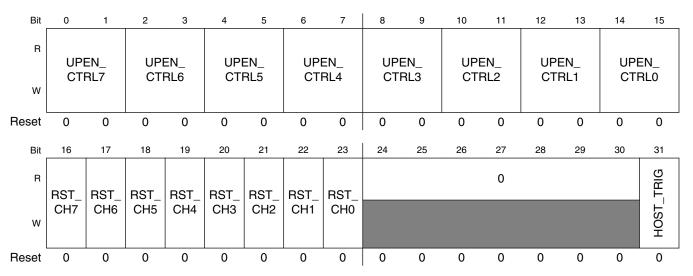

|      | 2.10.2   | GTM Reset Register (GTM_RST)                                   | 54   |

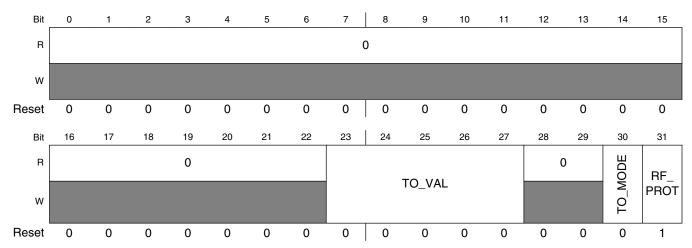

|      | 2.10.3   | GTM Control Register (GTM_CTRL)                                | 54   |

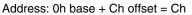

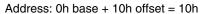

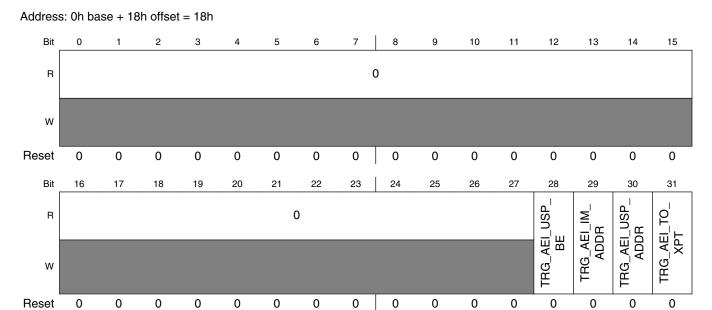

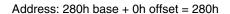

|      | 2.10.4   | GTM AEI Address Pointer Register (GTM_AEI_ADDR_XPT)            | 56   |

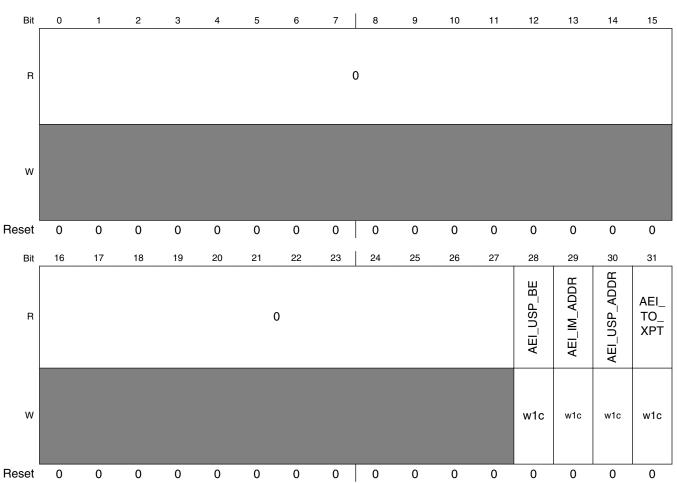

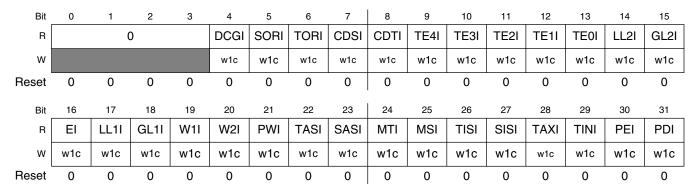

|      | 2.10.5   | GTM Interrupt Request Notification Register (GTM_IRQ_NOTIFY)   | 57   |

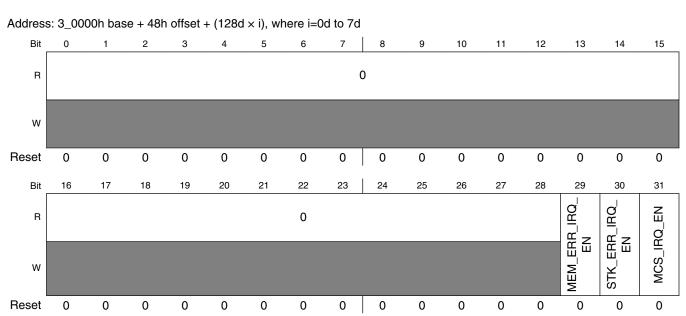

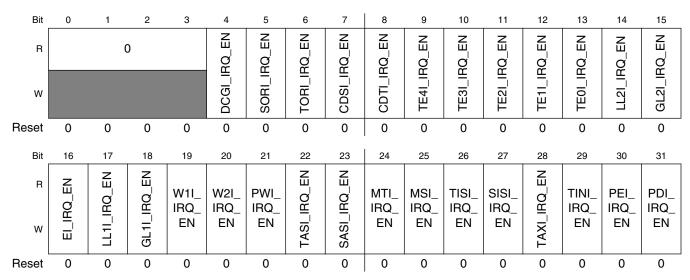

|      | 2.10.6   | GTM Interrupt Request Enable Register (GTM_IRQ_EN)             | 58   |

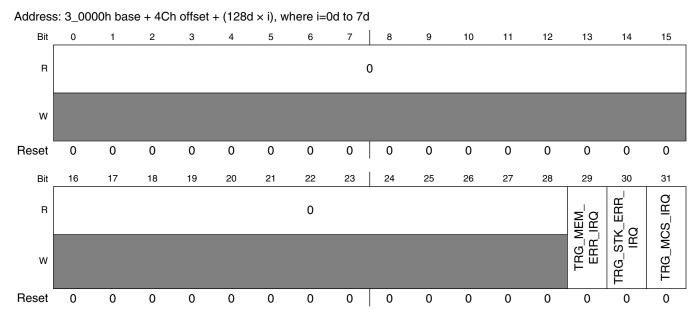

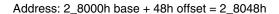

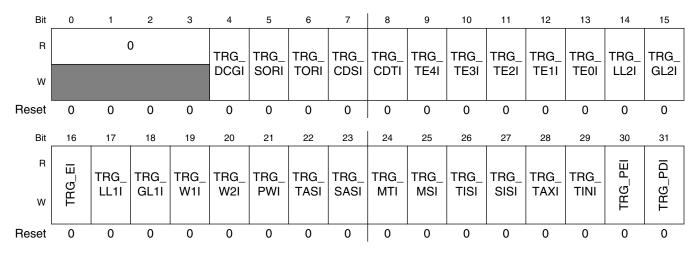

|      | 2.10.7   | GTM Force Interrupt Request Register (GTM_IRQ_FORCINT)         | 59   |

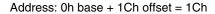

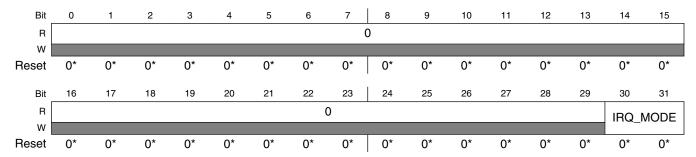

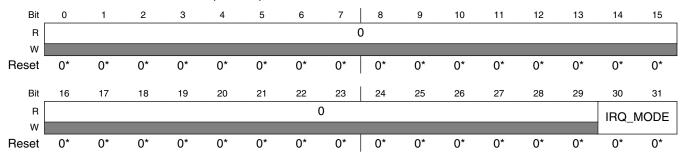

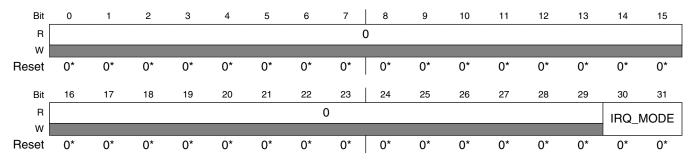

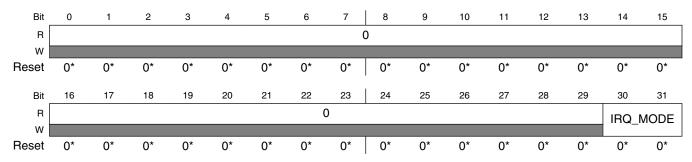

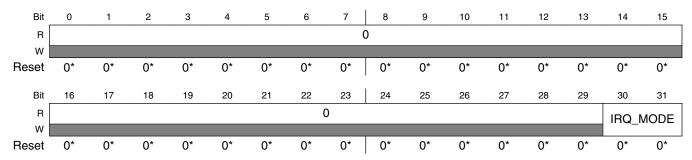

|      | 2.10.8   | GTM Interrupt Request Mode Register (GTM_IRQ_MODE)             | 60   |

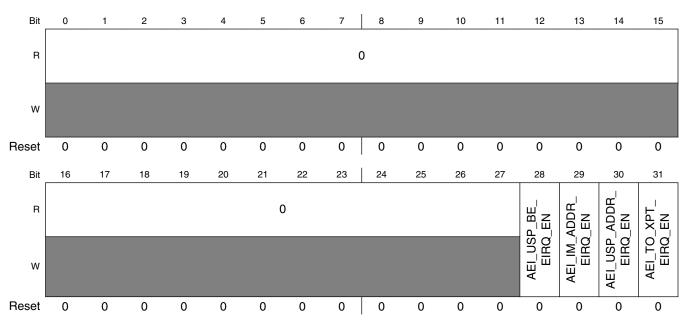

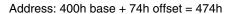

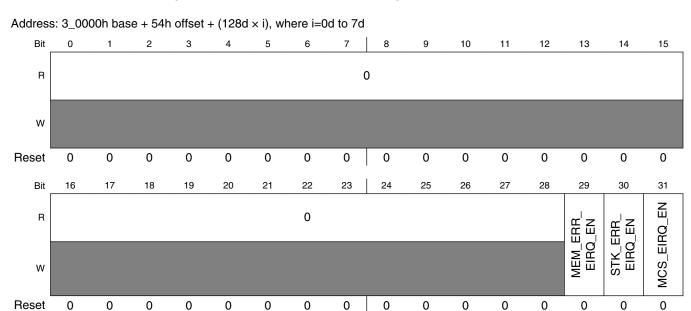

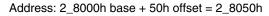

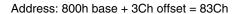

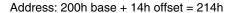

|      | 2.10.9   | GTM Error Interrupt Request Enable register (GTM_EIRQ_EN)      | 61   |

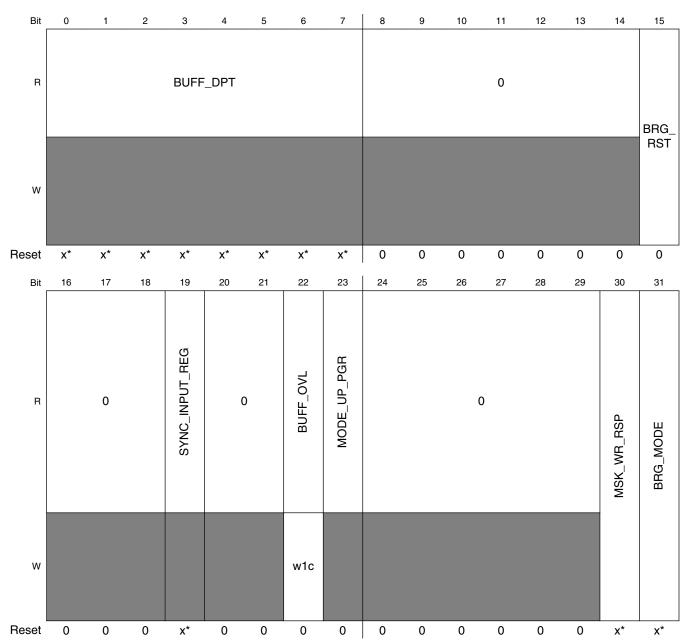

|      | 2.10.10  | GTM Bridge Mode Register (GTM_BRIDGE_MODE)                     | 62   |

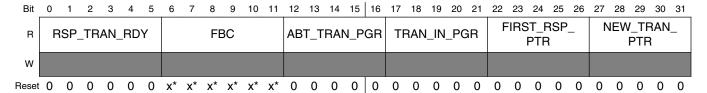

|      | 2.10.11  | GTM Bridge Pointer 1 Register (GTM_BRIDGE_PTR1)                | 64   |

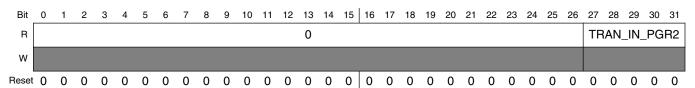

|      | 2.10.12  | GTM Bridge Pointer 2 Register (GTM_BRIDGE_PTR2)                | 65   |

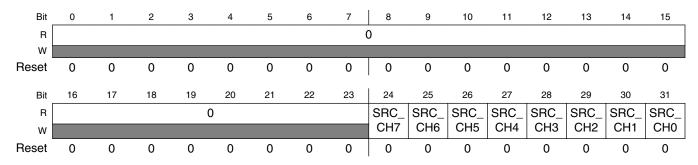

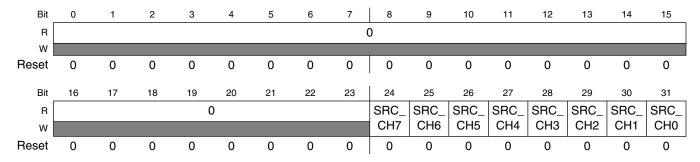

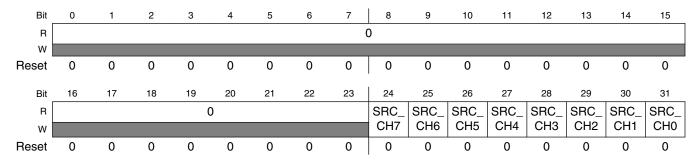

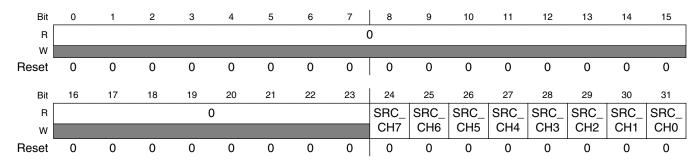

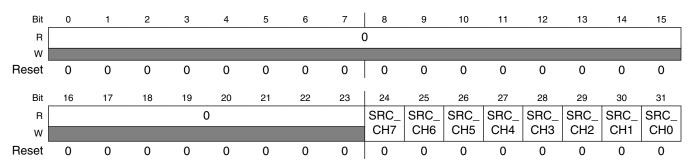

|      | 2.10.13  | GTM TIM0 Auxiliary Input Source register (GTM_TIM0_AUX_IN_SRC) | 65   |

|      | 2.10.14  | GTM TIM1 Auxiliary Input Source register (GTM_TIM1_AUX_IN_SRC) | 66   |

|      | 2.10.15  | GTM TIM2 Auxiliary Input Source register (GTM_TIM2_AUX_IN_SRC) | 67   |

|      | 2.10.16  | GTM TIM3 Auxiliary Input Source register (GTM_TIM3_AUX_IN_SRC) | 69   |

|      | 2.10.17  | GTM TIM4 Auxiliary Input Source register (GTM_TIM4_AUX_IN_SRC) | 70   |

|      | 2.10.18  | GTM TIM5 Auxiliary Input Source register (GTM_TIM5_AUX_IN_SRC) | 71   |

|      |          |                                                                |      |

# Chapter 3 Advanced Routing Unit (ARU)

| 3.1 | ARU O   | verview                                                      | 73 |

|-----|---------|--------------------------------------------------------------|----|

| 3.2 | Special | Data Sources                                                 | 73 |

| 3.3 | ARU A   | ARU Access via AEI                                           |    |

|     | 3.3.1   | Default ARU Access                                           | 74 |

|     | 3.3.2   | Debug Access.                                                | 75 |

| 3.4 | ARU In  | terrupt Signals                                              | 76 |

| 3.5 | Memory  | y Map and Registers                                          | 76 |

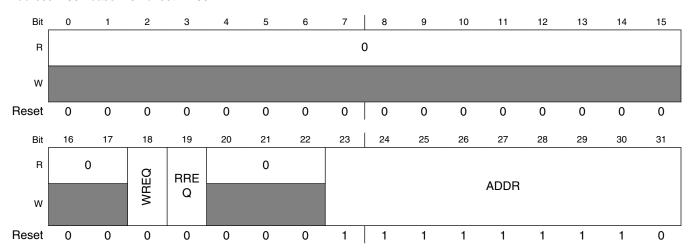

|     | 3.5.1   | ARU Access Register (ARU_ACCESS)                             | 77 |

|     | 3.5.2   | ARU Data High Register (ARU_DATA_H)                          | 78 |

|     | 3.5.3   | ARU Data Low Register (ARU_DATA_L)                           | 78 |

|     | 3.5.4   | ARU Debug Access 0 Register (ARU_DBG_ACCESS0)                | 79 |

|     | 3.5.5   | ARU Debug Data 0 High Register (ARU_DBG_DATA0_H)             | 79 |

|     | 3.5.6   | ARU Debug Data 0 Low Register (ARU_DBG_DATA0_L)              | 80 |

|     | 3.5.7   | ARU Debug Access 1 Register (ARU_DBG_ACCESS1)                | 80 |

|     | 3.5.8   | ARU Debug Data 1 High (ARU_DBG_DATA1_H)                      | 81 |

|     | 3.5.9   | ARU Debug Data 1 Low Register (ARU_DBG_DATA1_L)              | 81 |

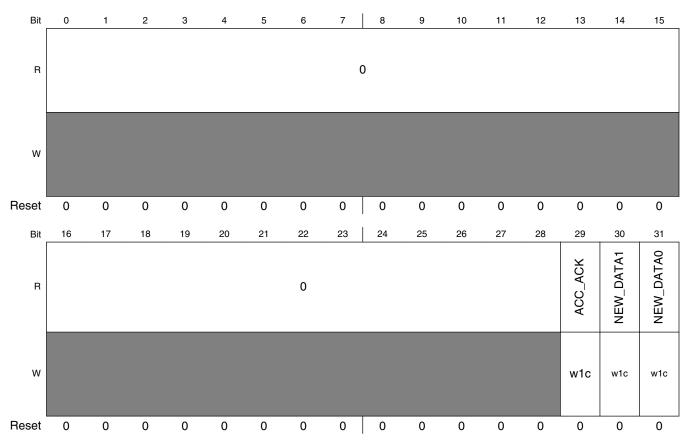

|     | 3.5.10  | ARU Interrupt Request Notification Register (ARU_IRQ_NOTIFY) | 82 |

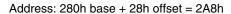

|     | 3.5.11  | ARU Interrupt Request Enable Register (ARU_IRQ_EN)           | 83 |

|     | 3.5.12  | ARU Force Interrupt Request Register (ARU_IRQ_FORCINT)       | 84 |

|     | 3.5.13  | ARU Interrupt Request Mode Register (ARU_IRQ_MODE)           | 85 |

|     |         | Chapter 4 Broadcast (BRC) Module                             |    |

| 4.1 | BRC O   | verview                                                      | 87 |

| 4.2 | BRC Co  | onfiguration                                                 | 87 |

| 4.3 | BRC In  | terrupt Signals                                              | 89 |

| 4.4 | Memory  | y Map and Registers                                          | 89 |

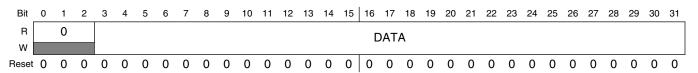

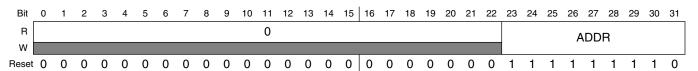

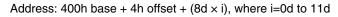

|     | 4.4.1   | BRC Source n Address Register, n[0:11] (BRC_SRCn_ADDR)       | 91 |

|     |         |                                                              |    |

| Sec | tion nun  | nber Title                                                          | Page |  |

|-----|-----------|---------------------------------------------------------------------|------|--|

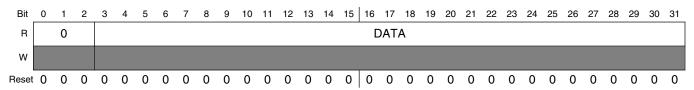

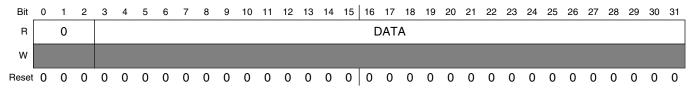

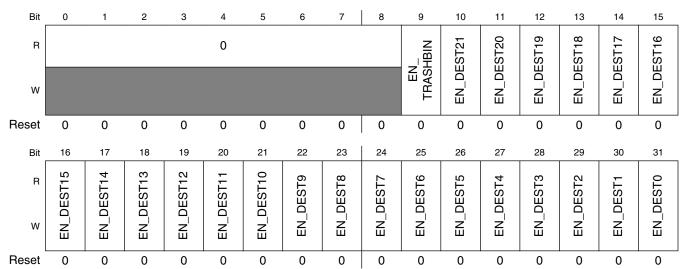

|     | 4.4.2     | BRC Source n to Destination Register, n[0:11] (BRC_SRCn_DEST)       | 92   |  |

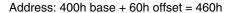

|     | 4.4.3     | BRC Interrupt Request Notification Register (BRC_IRQ_NOTIFY)        | 94   |  |

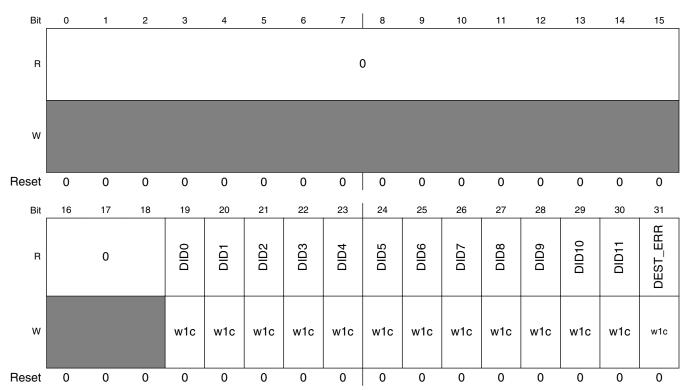

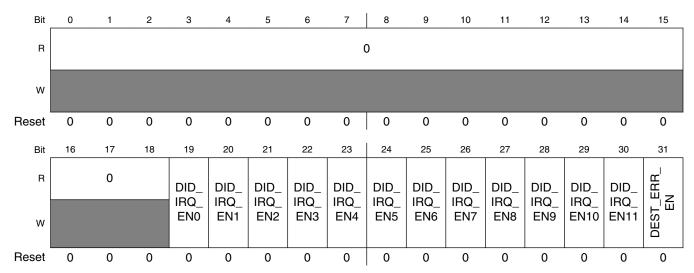

|     | 4.4.4     | BRC Interrupt Request Enable Register (BRC_IRQ_EN)                  | 96   |  |

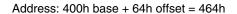

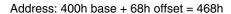

|     | 4.4.5     | BRC Force Interrupt Request Register (BRC_IRQ_FORCINT)              | 98   |  |

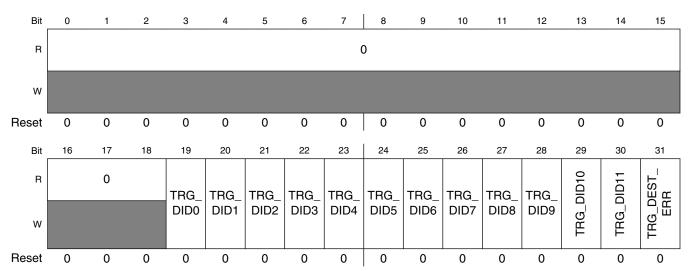

|     | 4.4.6     | BRC Interrupt Request Mode Register (BRC_IRQ_MODE)                  | 100  |  |

|     | 4.4.7     | BRC Software Reset Register (BRC_RST)                               | 101  |  |

|     | 4.4.8     | BRC Error Interrupt Request Enable Register (BRC_EIRQ_EN)           | 102  |  |

|     |           | Chapter 5 First In First Out Module (FIF0)                          |      |  |

| 5.1 | FIFO Ove  | erview                                                              | 105  |  |

| 5.2 | Operation | 1 Modes                                                             | 106  |  |

|     | 5.2.1     | Normal Operation Mode                                               | 106  |  |

|     | 5.2.2     | Ring Buffer Operation Mode                                          | 106  |  |

| 5.3 | FIFO Inte | errupt Signals                                                      | 107  |  |

| 5.4 | Memory 1  | Map and Registers                                                   | 107  |  |

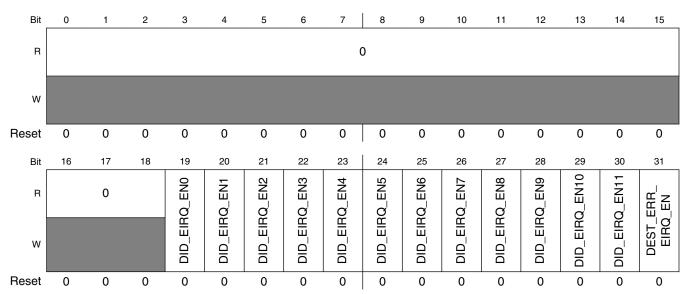

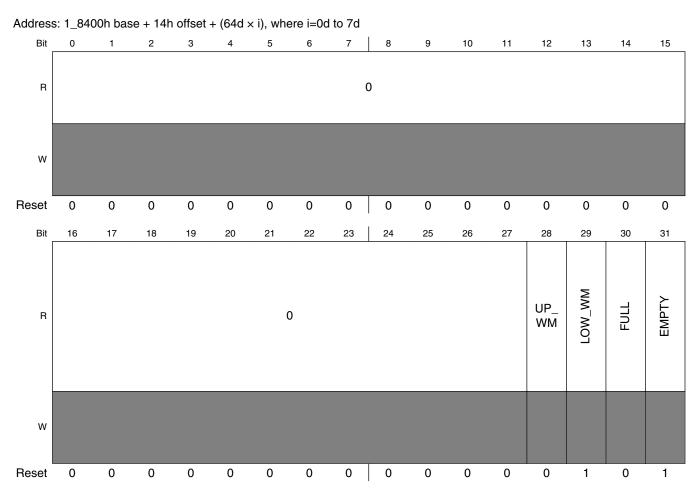

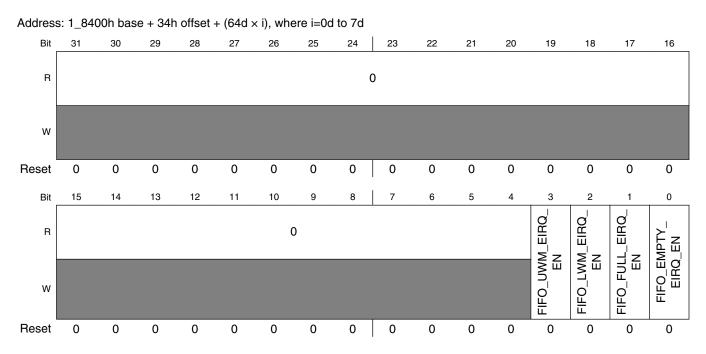

|     | 5.4.1     | FIFO0 Channel Control Register (FIFO_0_CHn_CTRL)                    | 112  |  |

|     | 5.4.2     | FIFO0 Channel End Address Register (FIFO_0_CHn_END_ADDR)            | 113  |  |

|     | 5.4.3     | FIFO0 Channel Start Address Register (FIFO_0_CHn_START_ADDR)        | 114  |  |

|     | 5.4.4     | FIFO0 Channel Upper Watermark Register (FIFO_0_CHn_UPPER_WM)        | 114  |  |

|     | 5.4.5     | FIFO0 Channel Lower Watermark Register (FIFO_0_CHn_LOWER_WM)        | 115  |  |

|     | 5.4.6     | FIFO0 Channel Status Register (FIFO_0_CHn_STATUS)                   | 116  |  |

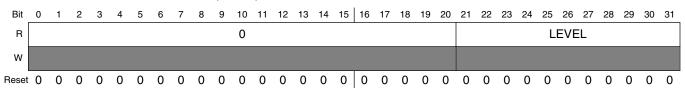

|     | 5.4.7     | FIFO0 Channel Fill Level Register (FIFO_0_CHn_FILL_LEVEL)           | 117  |  |

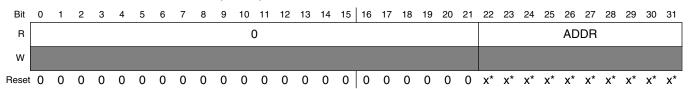

|     | 5.4.8     | FIFO0 Channel Write Pointer Register (FIFO_0_CHn_WR_PTR)            | 117  |  |

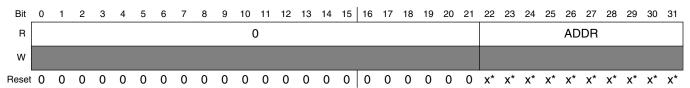

|     | 5.4.9     | FIFO0 Channel Read Pointer (FIFO_0_CHn_RD_PTR)                      | 118  |  |

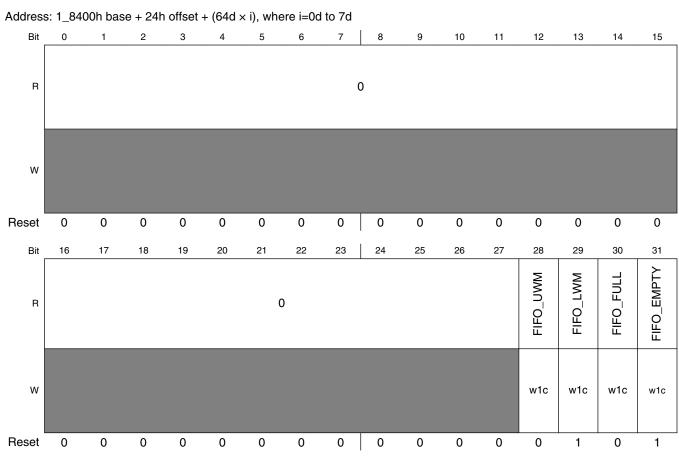

|     | 5.4.10    | FIFO0 Channel IRQ Notification Register (FIFO_0_CHn_IRQ_NOTIFY)     | 119  |  |

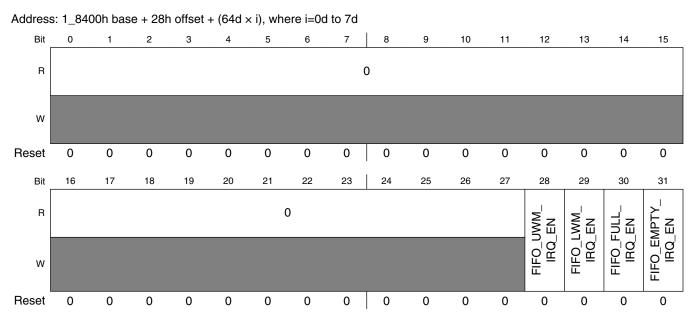

|     | 5.4.11    | FIFO0 Channel IRQ Enable Register (FIFO_0_CHn_IRQ_EN)               | 120  |  |

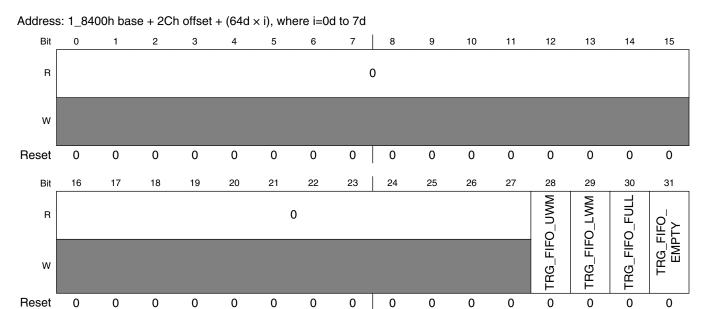

|     | 5.4.12    | FIFO0 Channel Force Interrupt Register (FIFO_0_CHn_IRQ_FORCINT)     | 121  |  |

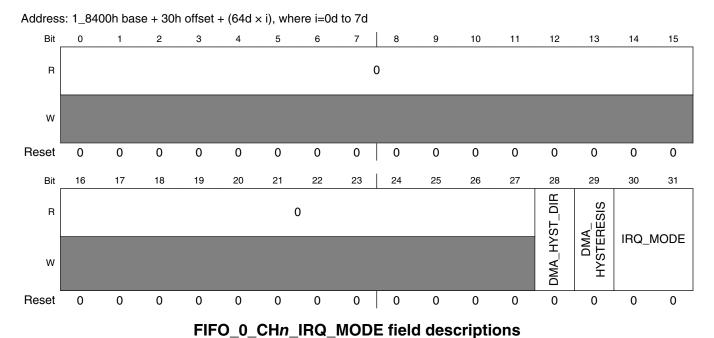

|     | 5.4.13    | FIFO0 Channel IRQ Mode Register (FIFO_0_CHn_IRQ_MODE)               | 122  |  |

|     | 5.4.14    | FIFO0 Channel Error Interrupt Request Register (FIFO_0_CHn_EIRQ_EN) | 123  |  |

|     |           |                                                                     |      |  |

| Section number |         | umber Title                                                             | Page |

|----------------|---------|-------------------------------------------------------------------------|------|

|                |         | Chapter 6 AEI to FIFO Data Interface (AFD)                              |      |

| 6.1            | AFD O   | verview                                                                 | 125  |

| 6.2            | Memor   | y Map and Registers                                                     | 125  |

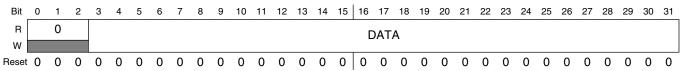

|                | 6.2.1   | AFD0 FIFO Channel n Buffer Access Register, n=0:7 (AFD_0_CHn_BUF_ACC)   | 126  |

|                |         | Chapter 7<br>FIFO-to-ARU (F2A) Unit                                     |      |

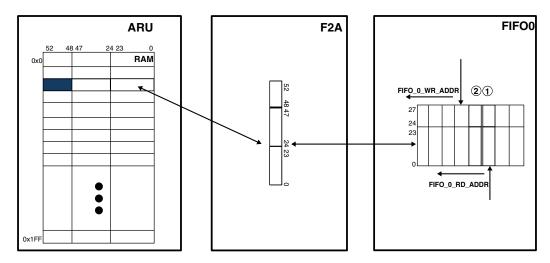

| 7.1            | F2A O   | verview                                                                 | 127  |

| 7.2            | Transfe | er modes                                                                | 127  |

| 7.3            | Memor   | y Map and Registers                                                     | 129  |

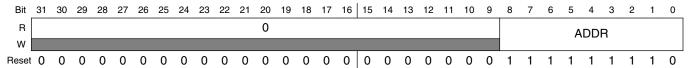

|                | 7.3.1   | F2A0 Read Channel n Address Register, n=0:7 (F2A_0_CHn_ARU_RD_FIFO)     | 130  |

|                | 7.3.2   | F2A0 Channel n Stream Configuration Register, n=0:7 (F2A_0_CHn_STR_CFG) | 130  |

|                | 7.3.3   | F2A0 Stream Activation Register (F2A_0_ENABLE)                          | 131  |

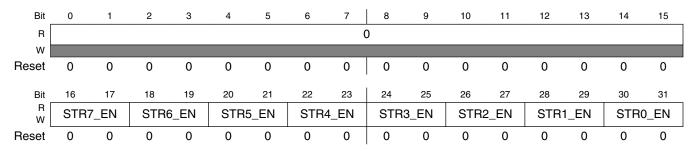

|                |         | Chapter 8 Clock Management Unit (CMU)                                   |      |

| 8.1            | CMU C   | Overview                                                                | 135  |

| 8.2            | Global  | Clock Divider                                                           | 137  |

| 8.3            | Configu | urable Clock Generation Subunit (CFGU)                                  | 138  |

| 8.4            | Wave F  | Form of Generated Clock Signal CMU_CLKn                                 | 139  |

| 8.5            | Fixed C | Clock Generation (FXU)                                                  | 139  |

| 8.6            | Externa | al Generation Unit (EGU)                                                | 140  |

| 8.7            | Memor   | y Map and Registers                                                     | 141  |

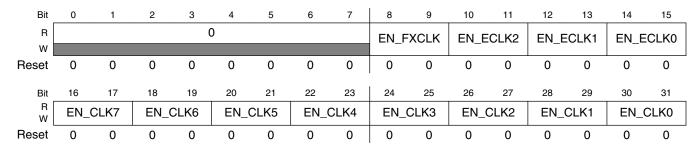

|                | 8.7.1   | CMU Clock Enable Register (CMU_CLK_EN)                                  | 142  |

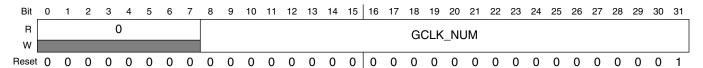

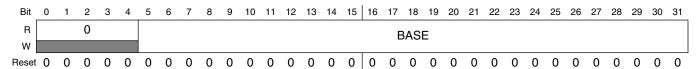

|                | 8.7.2   | Global Clock Control Numerator Register (CMU_GCLK_NUM)                  | 146  |

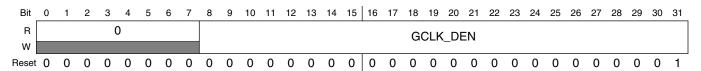

|                | 8.7.3   | Global Clock Control Denominator Register (CMU_GCLK_DEN)                | 146  |

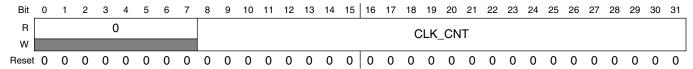

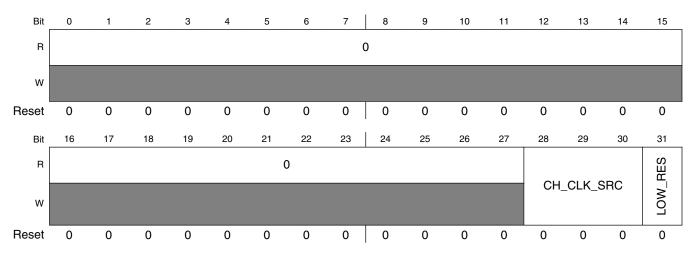

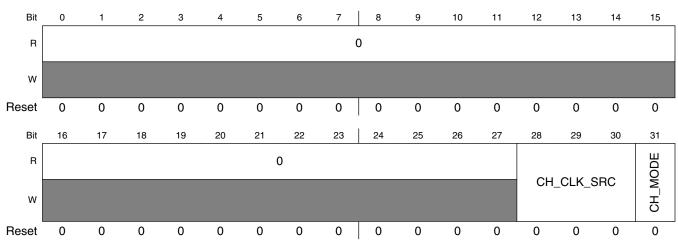

|                | 8.7.4   | Control for Clock Source n register (CMU_CLK_n_CTRL)                    | 147  |

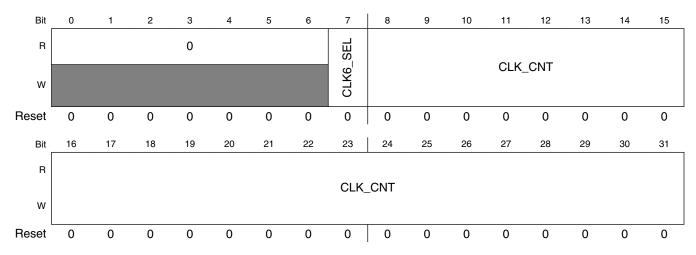

|                | 8.7.5   | Control for Clock Source 6 register (CMU_CLK_6_CTRL)                    | 147  |

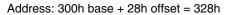

|                | 8.7.6   | Control for Clock Source 7 register (CMU_CLK_7_CTRL)                    | 148  |

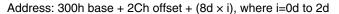

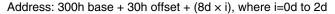

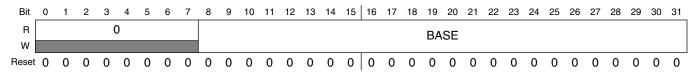

|                | 8.7.7   | CMU External Clock n Numerator Register (CMU_ECLKn_NUM)                 | 149  |

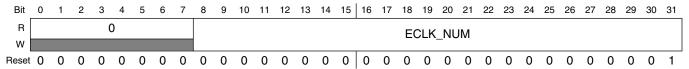

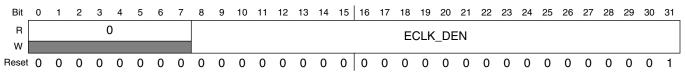

|                | 8.7.8   | CMU External Clock n Denominator Register (CMU_ECLKnDEN)                | 150  |

|                |         | Generic Timer Module 104 (GTM104) Reference Manual, Rev. 1, 3 Feb 2015  |      |

| Sec  | tion nur                 | mber Title                                                        | Page |

|------|--------------------------|-------------------------------------------------------------------|------|

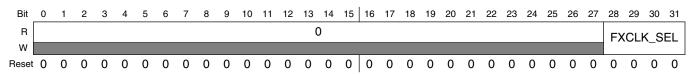

|      | 8.7.9                    | CMU FX Clock Control register (CMU_FXCLK_CTRL)                    | 150  |

|      |                          | Chapter 9 Time Base Unit (TBU)                                    |      |

| 9.1  | TBU Ove                  | erview                                                            | 153  |

| 9.2  | TBU Cha                  | annel Modes                                                       |      |

| 9.3  | Memory                   | 155                                                               |      |

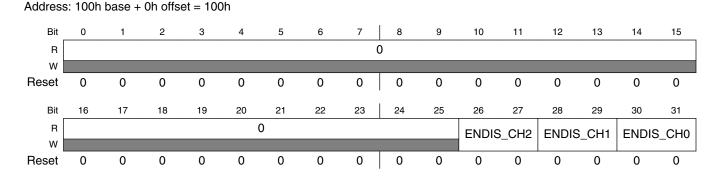

|      | 9.3.1                    | TBU Global Channel Enable Register (TBU_CHEN)                     | 155  |

|      | 9.3.2                    | TBU Channel 0 Control Register (TBU_CH0_CTRL)                     | 157  |

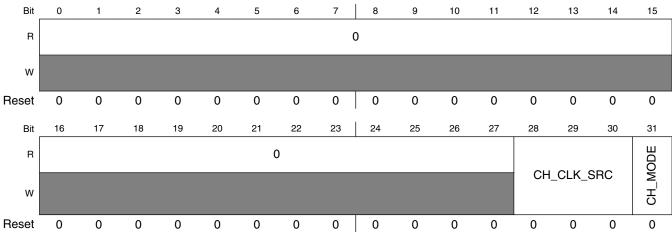

|      | 9.3.3                    | TBU Channel 0 Base Register (TBU_CH0_BASE)                        | 158  |

|      | 9.3.4                    | TBU Channel 1 Control Register (TBU_CH1_CTRL)                     | 158  |

|      | 9.3.5                    | TBU Channel 1 Base Register (TBU_CH1_BASE)                        | 159  |

|      | 9.3.6                    | TBU Channel 2 Control Register (TBU_CH2_CTRL)                     | 160  |

|      | 9.3.7                    | TBU Channel 2 Base Register (TBU_CH2_BASE)                        | 161  |

|      |                          | Chapter 10 Timer Input Module (TIM)                               |      |

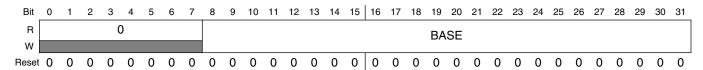

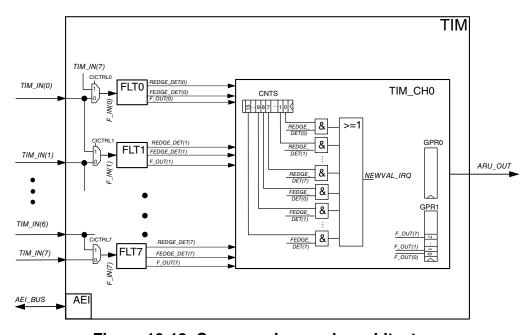

| 10.1 | TIM Ove                  | erview                                                            | 163  |

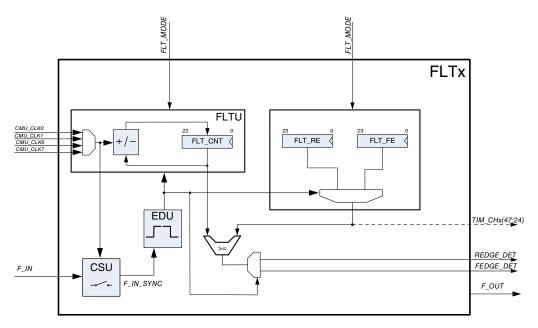

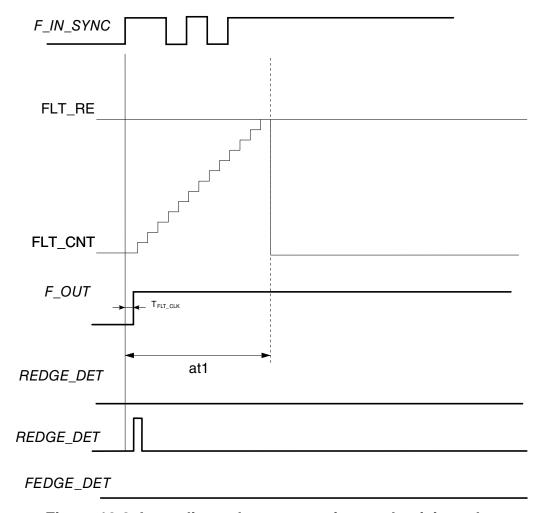

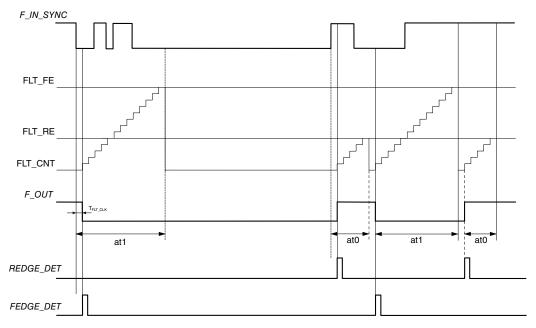

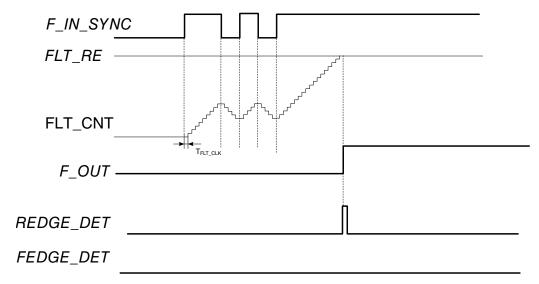

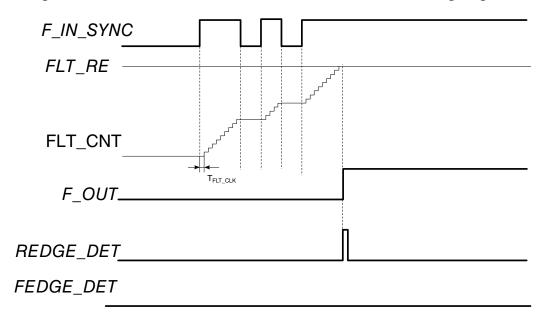

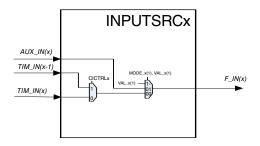

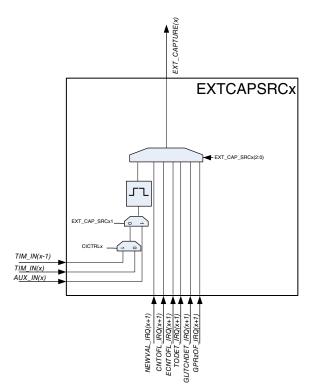

| 10.2 | TIM_Filter_Function_FLT. |                                                                   | 165  |

|      | 10.2.1                   | FLT Overview                                                      | 165  |

|      | 10.2.2                   | TIM Filter Modes                                                  | 167  |

|      | 10.2.3                   | TIM Filter reconfiguration.                                       | 172  |

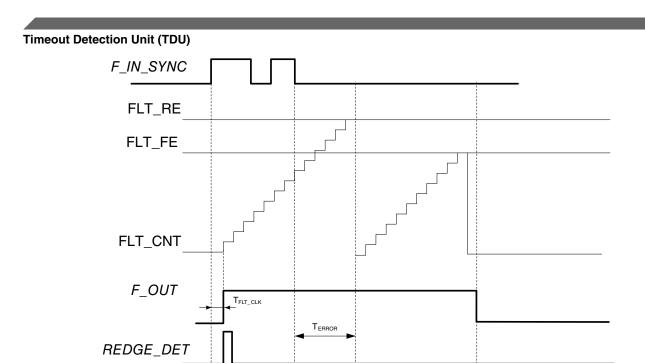

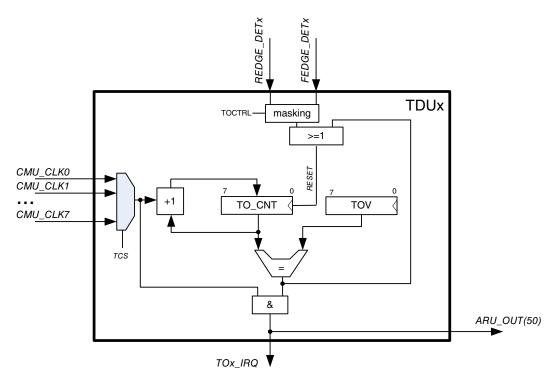

| 10.3 | Timeout                  | Detection Unit (TDU)                                              | 172  |

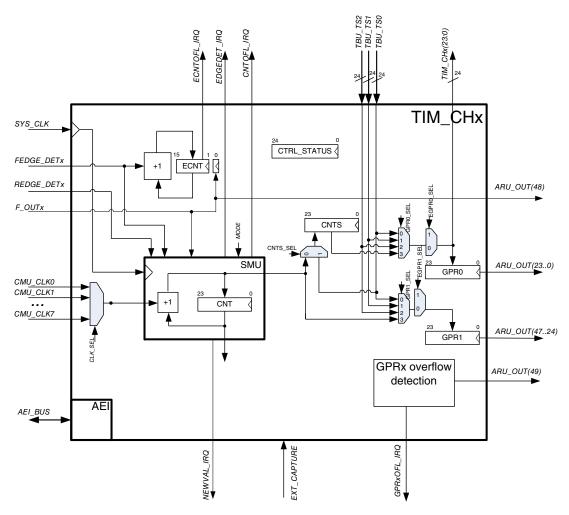

| 10.4 | TIM Cha                  | annel Architecture                                                | 175  |

|      | 10.4.1                   | TIM Channel Overview                                              | 175  |

|      | 10.4.2                   | TIM Channel Modes                                                 | 178  |

| 10.5 | MAP Su                   | bmodule Interface                                                 | 190  |

| 10.6 | TIM Inte                 | errupt Signals                                                    | 191  |

| 10.7 | Memory                   | Map and Registers                                                 | 191  |

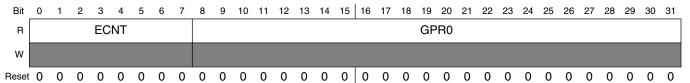

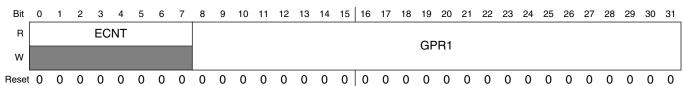

|      | 10.7.1                   | TIM0 Channel n General Purpose Register 0, n=0:7 (TIM_0_CHn_GPR0) | 197  |

|      | 10.7.2                   | TIM0 Channel n General Purpose Register 1, n=0:7 (TIM_0_CHn_GPR1) | 198  |

|      |                          |                                                                   |      |

| Section number Title |         | mber Title                                                                           | Page |

|----------------------|---------|--------------------------------------------------------------------------------------|------|

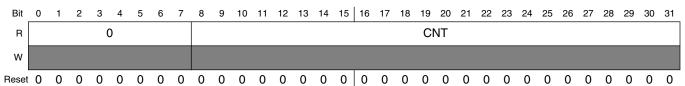

|                      | 10.7.3  | TIM0 Channel n Count Register, n=0:7 (TIM_0_CHn_CNT)                                 | 198  |

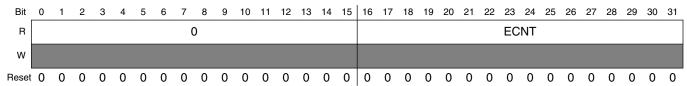

|                      | 10.7.4  | TIM0 Channel n Edge Counter Register, n=0:7 (TIM_0_CHn_ECNT)                         | 199  |

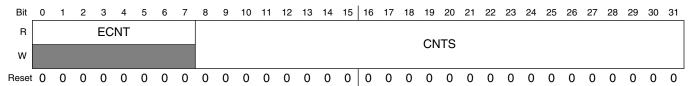

|                      | 10.7.5  | TIM0 Channel n Counter Shadow Register, n=0:7 (TIM_0_CHn_CNTS)                       | 199  |

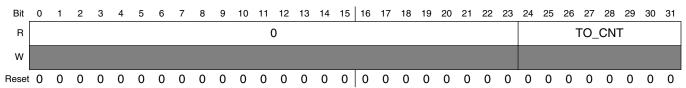

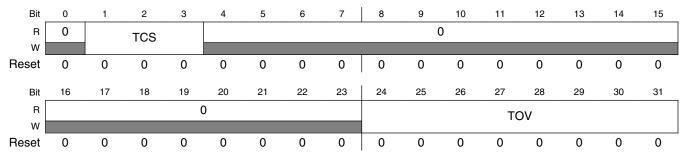

|                      | 10.7.6  | TIM0 Channel n TDUC Register, n=0:7 (TIM_0_CHn_TDUC)                                 | 200  |

|                      | 10.7.7  | TIM0 Channel n TDUV Register, n=0:7 (TIM_0_CHn_TDUV)                                 | 200  |

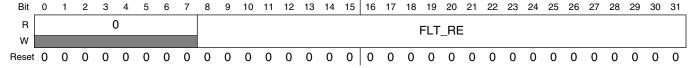

|                      | 10.7.8  | TIM0 Channel n Filter Parameter 0 Register, n=0:7 (TIM_0_CHn_FLT_RE)                 | 201  |

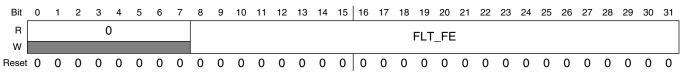

|                      | 10.7.9  | TIM0 Channel n Filter Parameter 1 Register, n=0:7 (TIM_0_CHn_FLT_FE)                 | 201  |

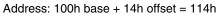

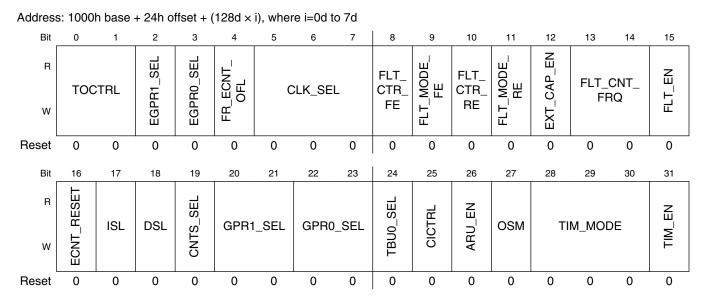

|                      | 10.7.10 | TIM0 Channel n Control Register, n=0:7 (TIM_0_CHn_CTRL)                              | 202  |

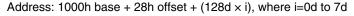

|                      | 10.7.11 | TIM0 Channel n External Control Register, n=0:7 (TIM_0_CHn_ECTRL)                    | 206  |

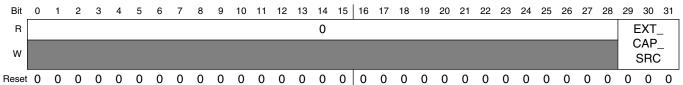

|                      | 10.7.12 | TIM0 Channel n Interrupt Request Notification Register, n=0:7 (TIM_0_CHn_IRQ_NOTIFY) | 207  |

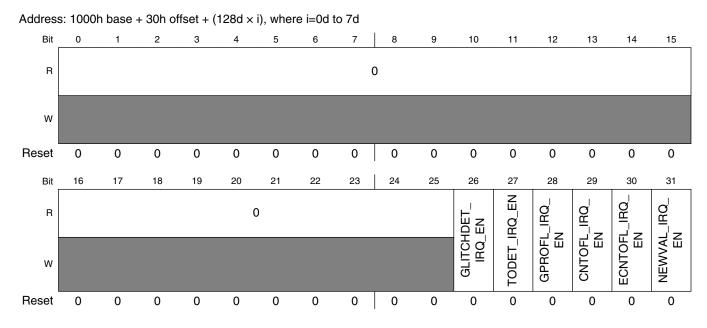

|                      | 10.7.13 | TIM0 Channel n Interrupt Request Enable Register, n=0:7 (TIM_0_CHn_IRQ_EN)           | 208  |

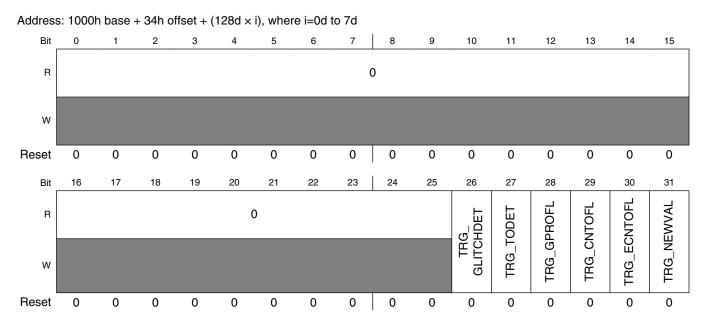

|                      | 10.7.14 | TIM0 Channel n Force Interrupt Request Register, n=0:7 (TIM_0_CHn_IRQ_FORCINT)       | 210  |

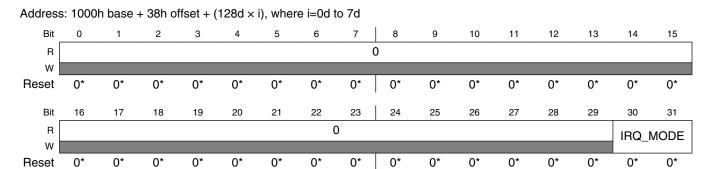

|                      | 10.7.15 | TIM0 Channel n Interrupt Request Mode Register, n=0:7 (TIM_0_CHn_IRQ_MODE)           | 211  |

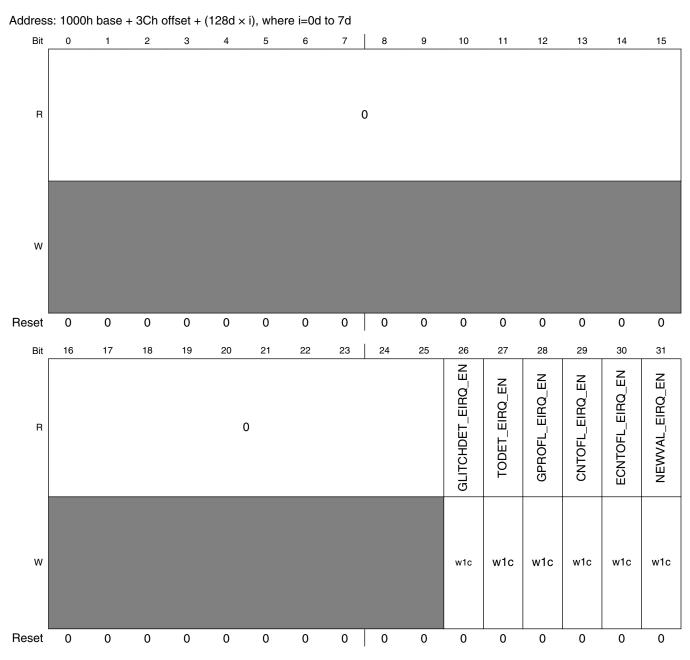

|                      | 10.7.16 | TIM0 Channel Error Interrupt Request Enable Register, n=0:7 (TIM_0_CHn_EIRQ_EN)      | 213  |

|                      | 10.7.17 | TIM0 Input Source Register (TIM_0_IN_SRC)                                            | 214  |

|                      | 10.7.18 | TIM0 Channel Reset Register (TIM_0_RST)                                              | 221  |

|                      |         | Chapter 11 Timer Output Module (TOM)                                                 |      |

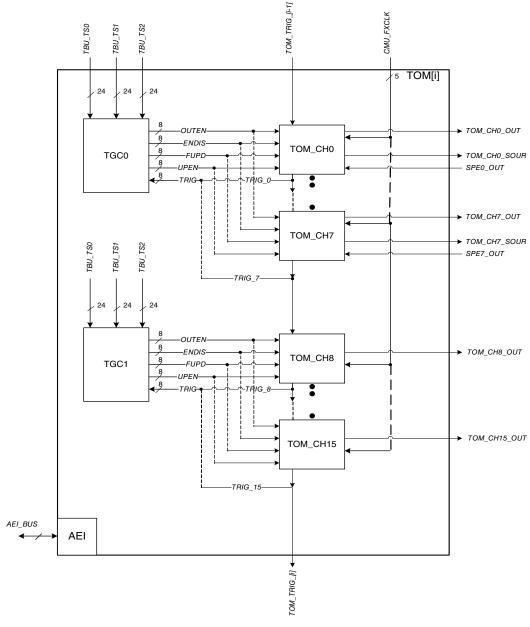

| 11.1                 |         | rerview                                                                              |      |

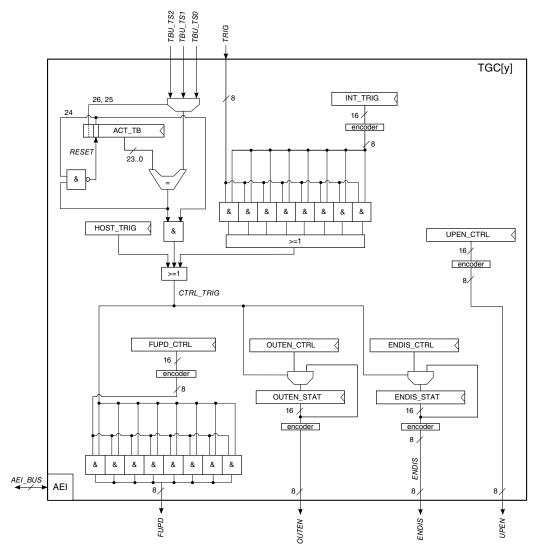

| 11.2                 | TOM GI  | obal Channel Control (TGC0, TGC1)                                                    |      |

|                      | 11.2.1  | TOM Global Channel Control Overview                                                  |      |

|                      | 11.2.2  | TGC Subunit                                                                          |      |

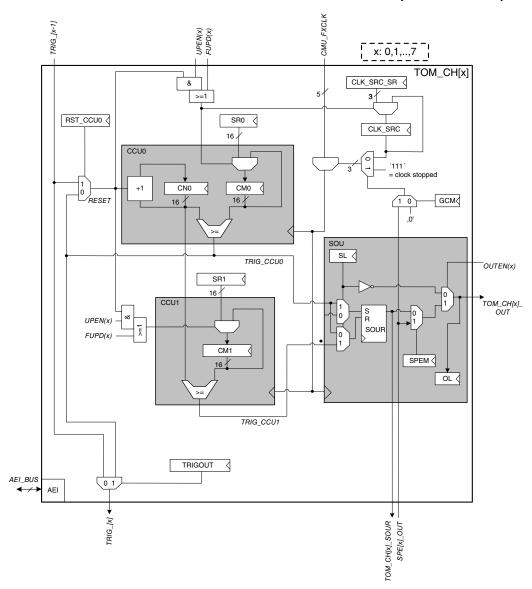

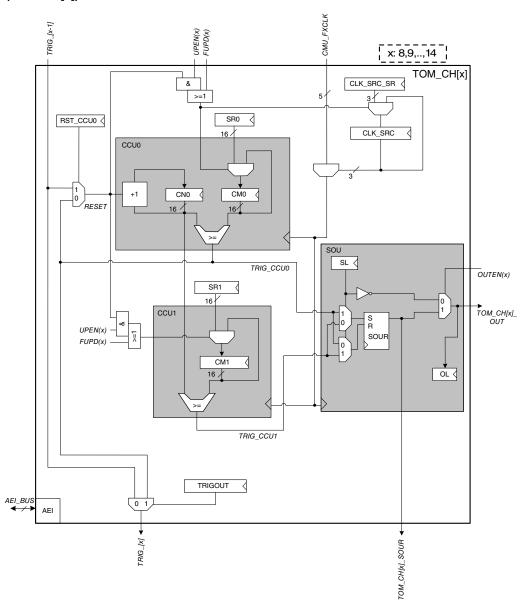

| 11.3                 |         | annel (TOM_CH[x])                                                                    |      |

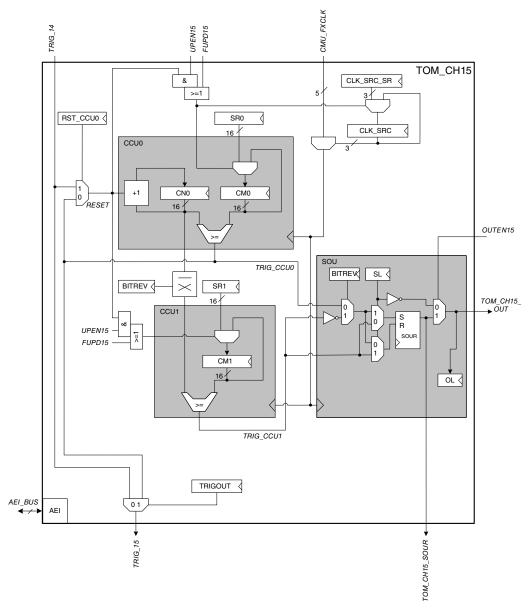

|                      | 11.3.1  | TOM Channel 15 architecture for PCM generation                                       |      |

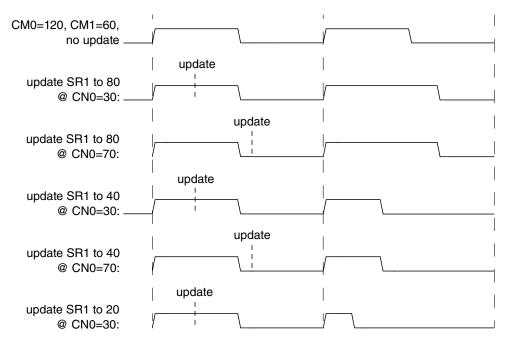

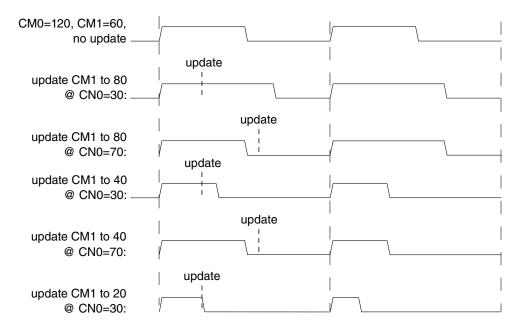

|                      | 11.3.2  | Duty cycle, period and selected counter clock frequency update mechanisms            |      |

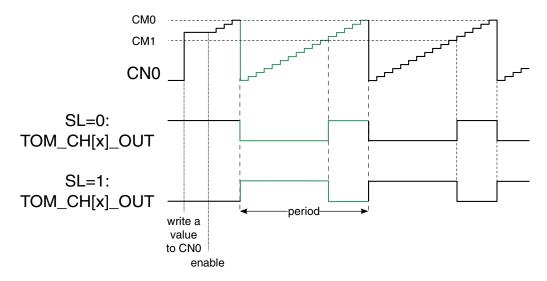

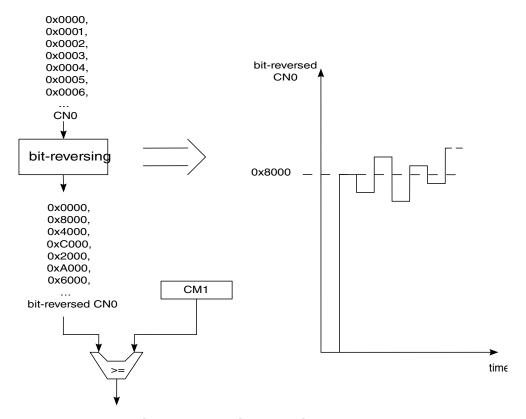

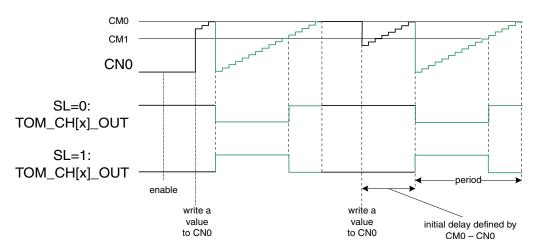

|                      | 11.3.3  | TOM continuous mode                                                                  | 234  |

|                      | 11.3.4  | TOM One shot mode                                                                    | 235  |

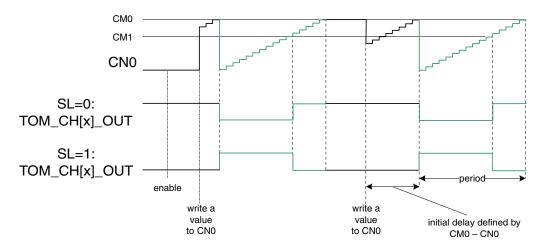

|                      | 11.3.5  | Pulse count modulation                                                               |      |

| 11.4                 | TOM Br  | ush-Less Direct Current (BLDC) Motor Support                                         | 238  |

Generic Timer Module 104 (GTM104) Reference Manual, Rev. 1, 3 Feb 2015

| Section number T |         | nber Title                                                                              | Page |

|------------------|---------|-----------------------------------------------------------------------------------------|------|

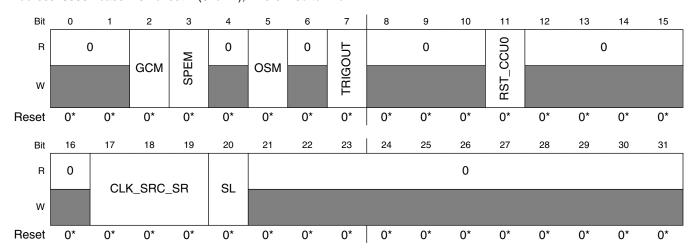

| 11.5             | TOM Ga  | ted Counter Mode                                                                        | 238  |

| 11.6             | TOM Int | errupt signals                                                                          | 239  |

| 11.7             | Memory  | Map and Registers                                                                       | 239  |

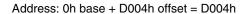

|                  | 11.7.1  | TOM0 Channel n Control Register, n[0:14] (TOM_0_CHn_CTRL)                               | 248  |

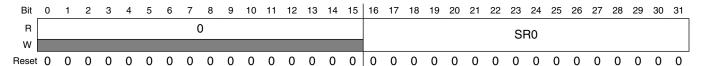

|                  | 11.7.2  | TOM0 Channel n Shadow 0 Register, n[0:15] (TOM_0_CHn_SR0)                               | 250  |

|                  | 11.7.3  | TOM0 Channel n Shadow 1 Register, n[0:15] (TOM_0_CHn_SR1)                               | 250  |

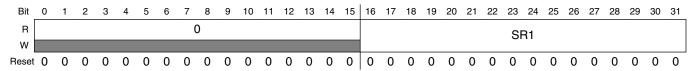

|                  | 11.7.4  | TOM0 Channel n Compare 0 Register, n[0:15] (TOM_0_CHn_CM0)                              | 251  |

|                  | 11.7.5  | TOM0 Channel n Compare 1 Register, n[0:15] (TOM_0_CHn_CM1)                              | 251  |

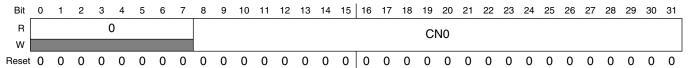

|                  | 11.7.6  | TOM0 Channel n CN0 Register, n[0:15] (TOM_0_CHn_CN0)                                    | 252  |

|                  | 11.7.7  | TOM0 Channel n Status Register, n[0:15] (TOM_0_CHn_STAT)                                | 252  |

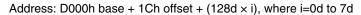

|                  | 11.7.8  | TOM0 Channel n Interrupt Request Notification Register, n[0:15] (TOM_0_CHn_IRQ_NOTIFY). | 253  |

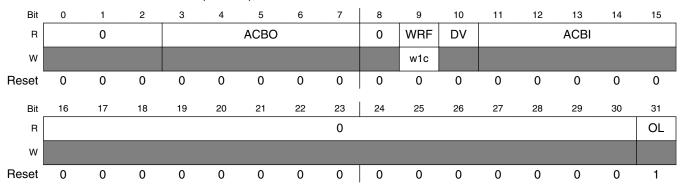

|                  | 11.7.9  | TOM0 Channel n Interrupt Request Enable Register, n[0:15] (TOM_0_CHn_IRQ_EN)            | 254  |

|                  | 11.7.10 | TOM0 Channel n Force Interrupt Request Register, n[0:15] (TOM_0_CHn_IRQ_FORCINT)        | 255  |

|                  | 11.7.11 | TOM0 Channel n Interrupt Request Mode Register, n[0:15] (TOM_0_CHn_IRQ_MODE)            | 256  |

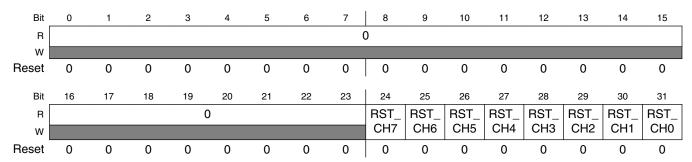

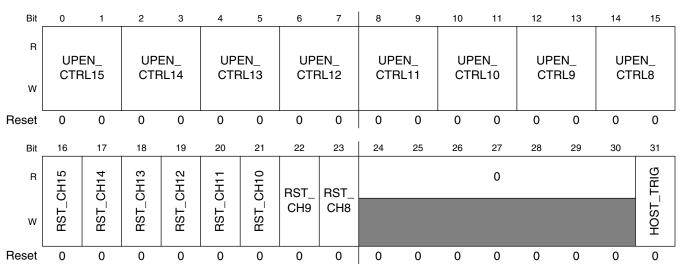

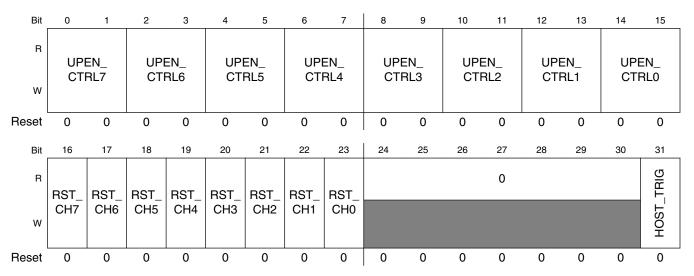

|                  | 11.7.12 | TOM0 TGC0 Global Control Register (TOM_0_TGC0_GLB_CTRL)                                 | 257  |

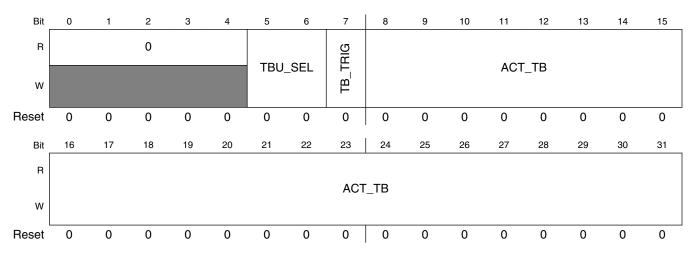

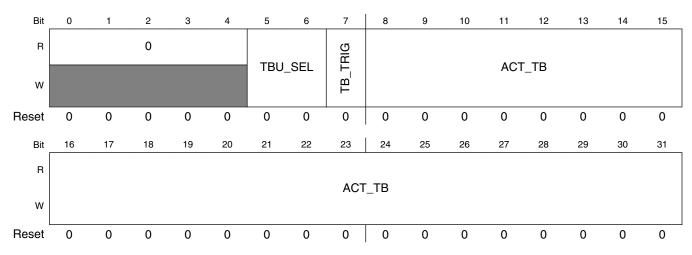

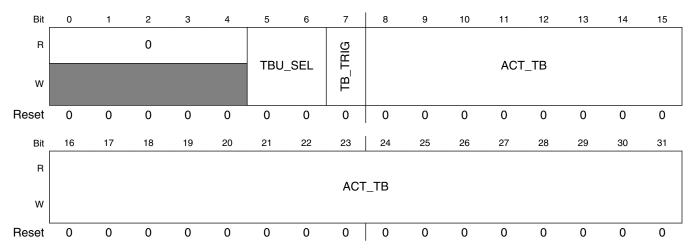

|                  | 11.7.13 | TOM0 TGC0 Action Time Base Register (TOM_0_TGC0_ACT_TB)                                 | 261  |

|                  | 11.7.14 | TOM0 TGC0 Force Update Control Register (TOM_0_TGC0_FUPD_CTRL)                          | 262  |

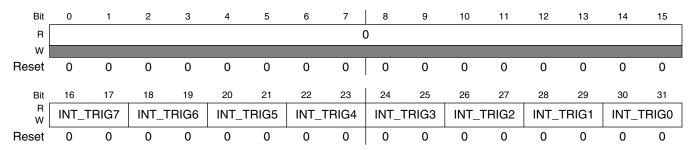

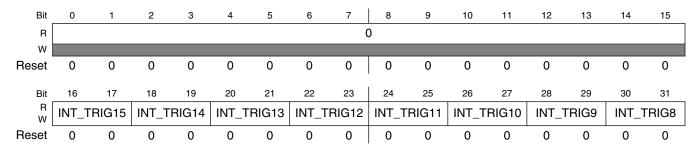

|                  | 11.7.15 | TOM0 TGC0 Interrupt Trigger Register (TOM_0_TGC0_INT_TRIG)                              | 266  |

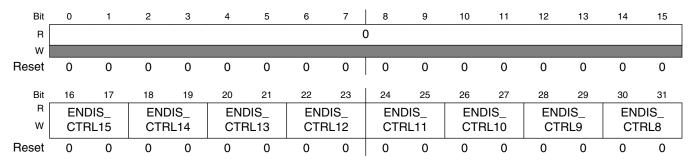

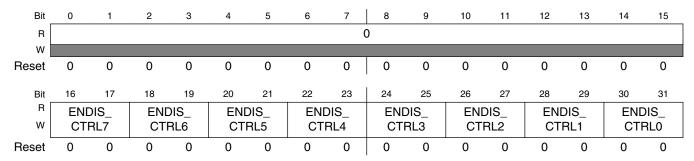

|                  | 11.7.16 | TOM0 TGC0 Enable/Disable Control Register (TOM_0_TGC0_ENDIS_CTRL)                       | 269  |

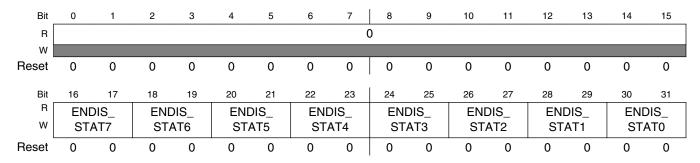

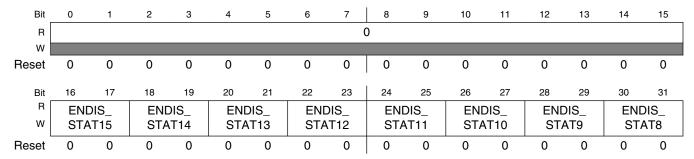

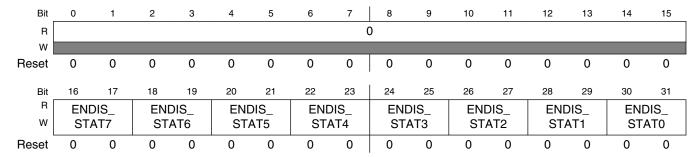

|                  | 11.7.17 | TOM0 TGC0 Enable/Disable Status Register (TOM_0_TGC0_ENDIS_STAT)                        | 271  |

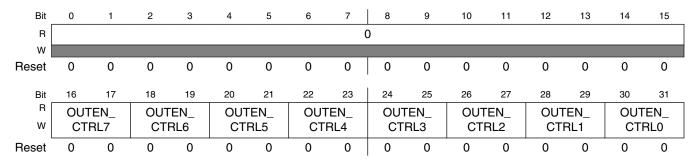

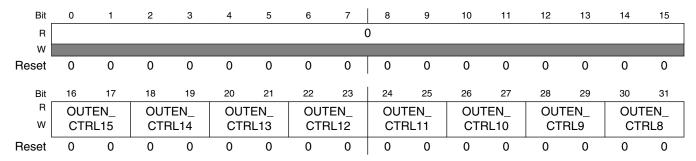

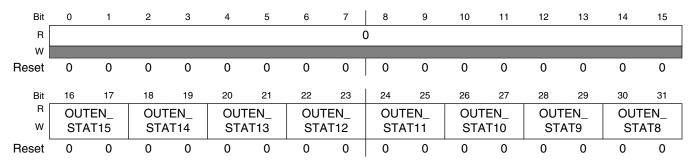

|                  | 11.7.18 | TOM0 TGC0 Out Enable Control Register (TOM_0_TGC0_OUTEN_CTRL)                           | 274  |

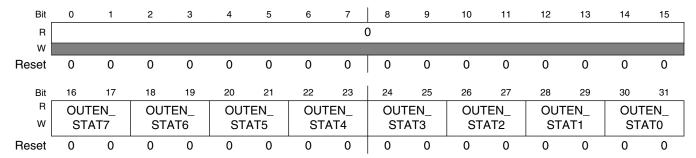

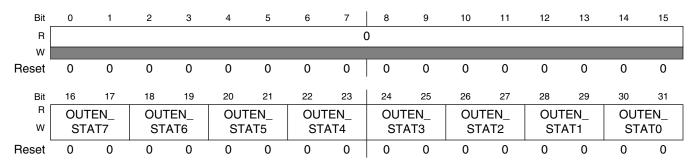

|                  | 11.7.19 | TOM0 TGC0 Out Enable Control/Status Register (TOM_0_TGC0_OUTEN_STAT)                    | 277  |

|                  | 11.7.20 | TOM0 TGC1 Global Control Register (TOM_0_TGC1_GLB_CTRL)                                 | 279  |

|                  | 11.7.21 | TOM0 TGC1 Action Time Base Register (TOM_0_TGC1_ACT_TB)                                 | 283  |

|                  | 11.7.22 | TOM0 TGC1 Force Update Control Register (TOM_0_TGC1_FUPD_CTRL)                          | 284  |

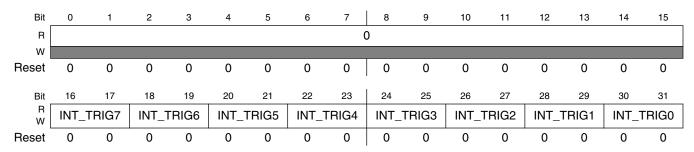

|                  | 11.7.23 | TOM0 TGC1 Interrupt Trigger Register (TOM_0_TGC1_INT_TRIG)                              | 289  |

|                  | 11.7.24 | TOM0 TGC1 Enable/Disable Control Register (TOM_0_TGC1_ENDIS_CTRL)                       | 291  |

|                  | 11.7.25 | TOM0 TGC1 Enable/Disable Status Register (TOM_0_TGC1_ENDIS_STAT)                        | 294  |

|                  | 11.7.26 | TOM0 TGC1 Out Enable Control Register (TOM_0_TGC1_OUTEN_CTRL)                           | 297  |

|                  |         |                                                                                         |      |

| Section number |         | mber Title                                                                            | Page   |  |

|----------------|---------|---------------------------------------------------------------------------------------|--------|--|

|                | 11.7.27 | TOM0 TGC1 Out Enable Control/Status Register (TOM_0_TGC1_OUTEN_STAT)                  | 299    |  |

|                | 11.7.28 | TOM0 Channel 15 Control register (TOM_0_CH15_CTRL)                                    | 302    |  |

|                |         | Chapter 12 ARU-connected Timer Output Module (ATOM)                                   |        |  |

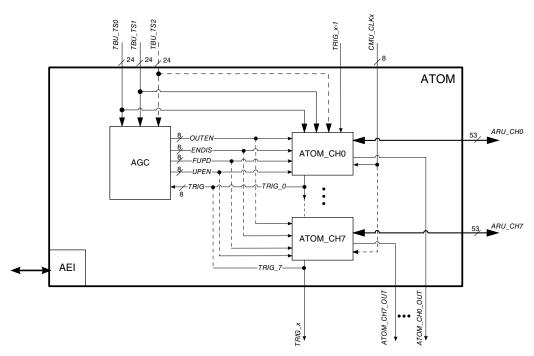

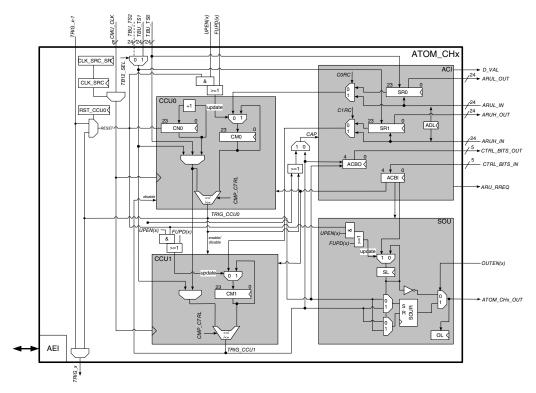

| 12.1           | ATOM (  | Overview                                                                              | 305    |  |

|                | 12.1.1  | ATOM Global control (AGC)                                                             | 307    |  |

| 12.2           | ATOM (  | Channel architecture                                                                  | 307    |  |

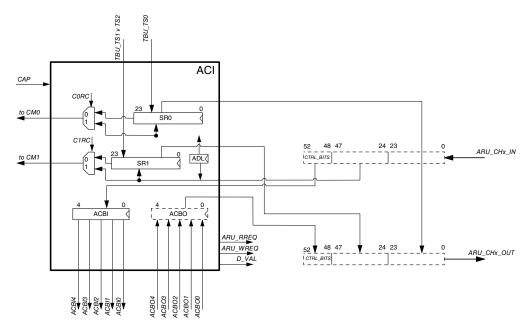

|                | 12.2.1  | ARU Communication Interface                                                           | 309    |  |

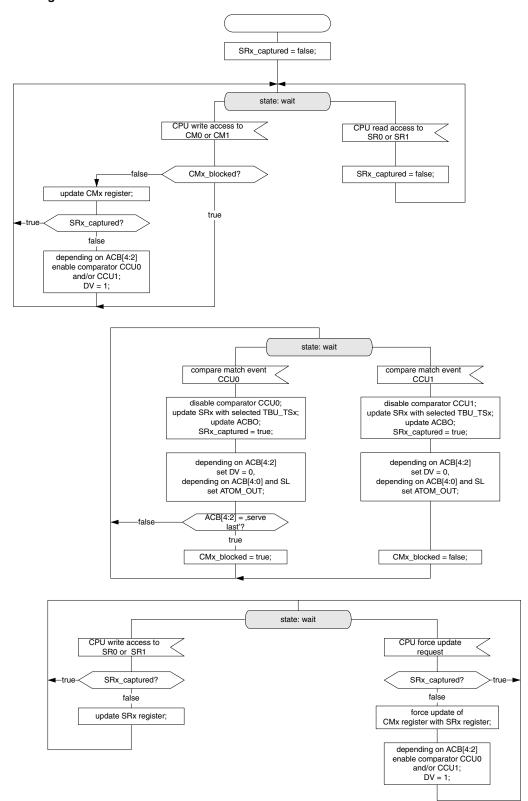

| 12.3           | ATOM (  | Channel modes.                                                                        | 311    |  |

|                | 12.3.1  | ATOM Signal Output Mode Immediate (SOMI)                                              | 312    |  |

|                | 12.3.2  | ATOM Signal Output Mode Compare (SOMC)                                                | 314    |  |

|                | 12.3.3  | ATOM Signal Output Mode PWM (SOMP)                                                    | 334    |  |

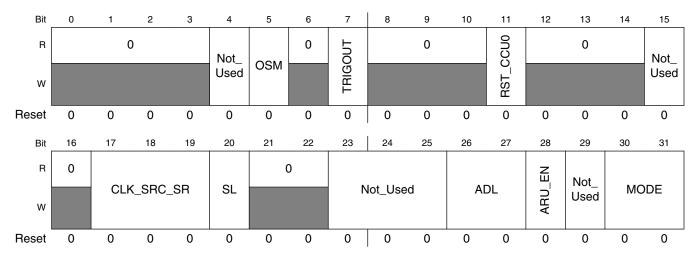

|                | 12.3.4  | ATOM Signal Output Mode Serial (SOMS)                                                 | 343    |  |

| 12.4           | ATOM I  | nterrupt signals                                                                      | 351    |  |

| 12.5           | Memory  | Map and Registers                                                                     | 351    |  |

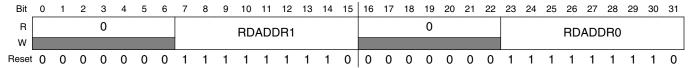

|                | 12.5.1  | ATOM0 Channel n Read Address Register, n=0:7 (ATOM_0_CHn_RDADDR)                      | 356    |  |

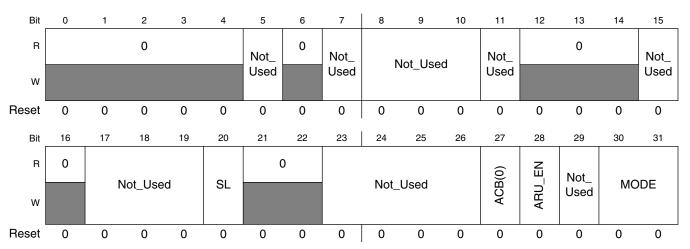

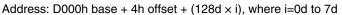

|                | 12.5.2  | ATOM0 Channel n Control Register, n=0:7 (ATOM_0_CHn_CTRL)                             | 357    |  |

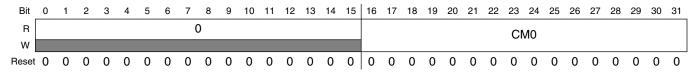

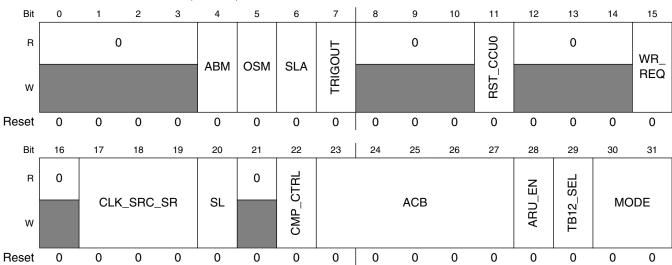

|                | 12.5.3  | ATOM0 Channel n Shadow 0 Register, n=0:7 (ATOM_0_CHn_SR0)                             | 360    |  |

|                | 12.5.4  | ATOM0 Channel n Shadow 1 Register, n=0:7 (ATOM_0_CHn_SR1)                             | 360    |  |

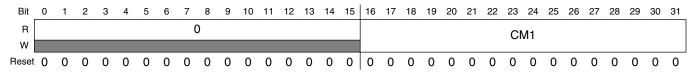

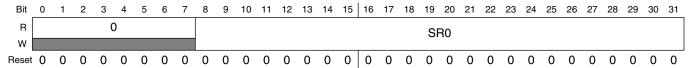

|                | 12.5.5  | ATOM0 Channel n Compare Match 0 Register, n=0:7 (ATOM_0_CHn_CM0)                      | 361    |  |

|                | 12.5.6  | ATOM0 Channel n Compare Match 1 Register, n=0:7 (ATOM_0_CHn_CM1)                      | 362    |  |

|                | 12.5.7  | ATOM0 Channel n Counter 0 Register, n=0:7 (ATOM_0_CHn_CN0)                            | 362    |  |

|                | 12.5.8  | ATOM0 Channel n Status Register, n=0:7 (ATOM_0_CHn_STAT)                              | 363    |  |

|                | 12.5.9  | ATOM0 Channel n Interrupt Request Notification Register, n=0:7 (ATOM_0_CHn_IRQ_NOTIFY | ۲) 364 |  |

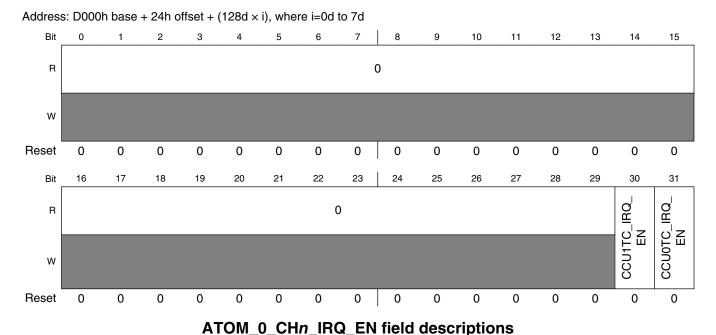

|                | 12.5.10 | ATOM0 Channel n Interrupt Request Enable Register, n=0:7 (ATOM_0_CHn_IRQ_EN)          | 365    |  |

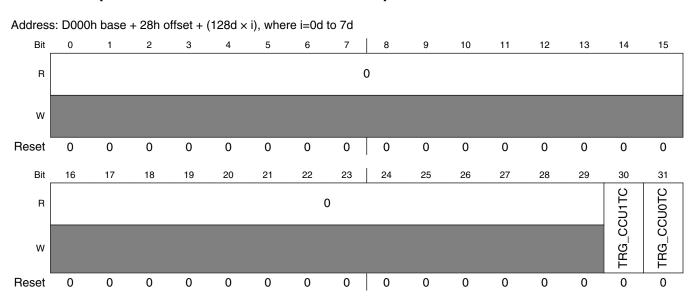

|                | 12.5.11 | ATOM0 Channel n Force Interrupt Request Register, n=0:7 (ATOM_0_CHn_IRQ_FORCINT)      | 366    |  |

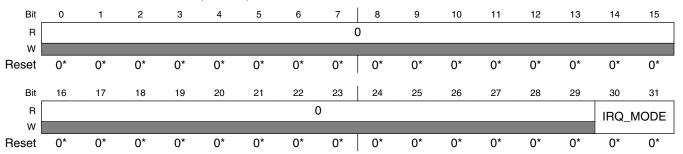

|                | 12.5.12 | ATOM0 Channel n Interrupt Request Mode Register, n=0:7 (ATOM_0_CHn_IRQ_MODE)          | 367    |  |

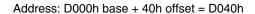

|                | 12.5.13 | ATOM0 AGC Global Control Register (ATOM_0_AGC_GLB_CTRL)                               | 368    |  |

|                | 12.5.14 | ATOM0 TGC0 Enable/Disable Control Register (ATOM_0_AGC_ENDIS_CTRL)                    | 371    |  |

|                |         | Generic Timer Module 104 (GTM104) Reference Manual, Rev. 1, 3 Feb 2015                |        |  |

| Section number Title |             | mber Title                                                            | Page |

|----------------------|-------------|-----------------------------------------------------------------------|------|

|                      | 12.5.15     | ATOM0 TGC0 Enable/Disable Status Register (ATOM_0_AGC_ENDIS_STAT)     | 374  |

|                      | 12.5.16     | ATOM0 TGC0 Action Time Base Register (ATOM_0_AGC_ACT_TB)              | 377  |

|                      | 12.5.17     | ATOM0 TGC0 Out Enable Control Register (ATOM_0_AGC_OUTEN_CTRL)        | 378  |

|                      | 12.5.18     | ATOM0 TGC0 Out Enable Control/Status Register (ATOM_0_AGC_OUTEN_STAT) | 380  |

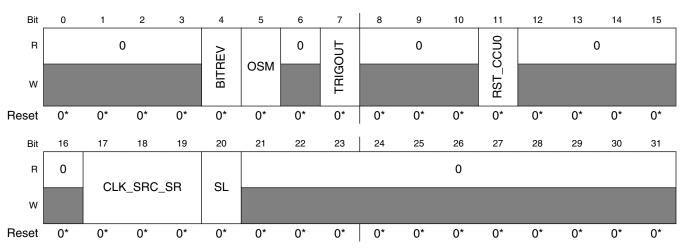

|                      | 12.5.19     | ATOM0 TGC0 Force Update Control Register (ATOM_0_AGC_FUPD_CTRL)       | 383  |

|                      | 12.5.20     | ATOM0 TGC0 Interrupt Trigger Register (ATOM_0_AGC_INT_TRIG)           | 387  |

|                      |             | Chapter 13 Multi Channel Sequencer (MCS)                              |      |

| 13.1                 | MCS Ov      | erview                                                                | 391  |

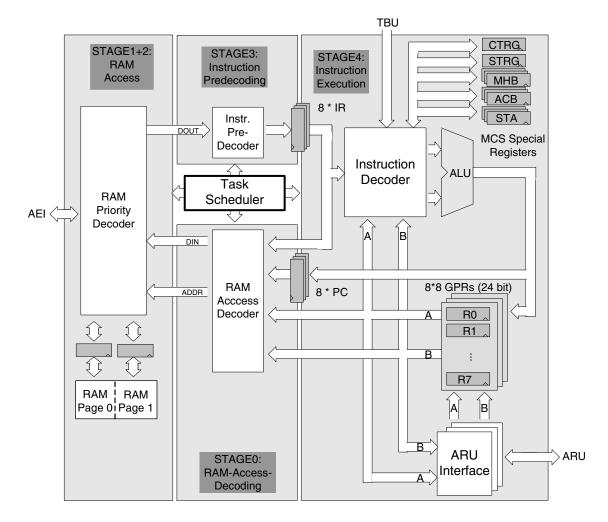

|                      | 13.1.1      | Architecture                                                          | 391  |

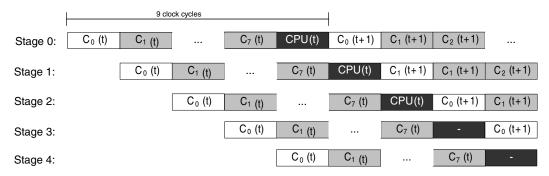

|                      | 13.1.2      | Scheduling                                                            | 394  |

| 13.2                 | Instruction | on Set                                                                | 396  |

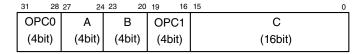

|                      | 13.2.1      | Instruction Format.                                                   | 397  |

|                      | 13.2.2      | Data Transfer Instructions.                                           | 398  |

|                      | 13.2.3      | ARU Instructions                                                      | 404  |

|                      | 13.2.4      | Arithmetic Logic Instructions                                         | 409  |

|                      | 13.2.5      | Test Instructions                                                     | 416  |

|                      | 13.2.6      | Control Flow Instructions                                             | 419  |

|                      | 13.2.7      | Other Instructions                                                    | 422  |

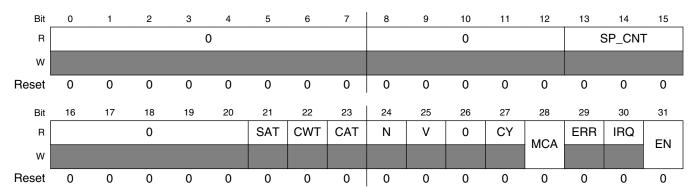

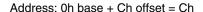

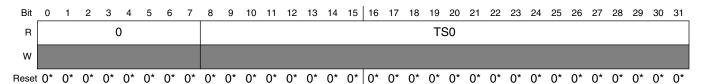

| 13.3                 | MCS Int     | ernal Registers                                                       | 424  |

|                      | 13.3.1      | Memory Map and Registers                                              | 424  |

| 13.4                 | MCS Co      | nfiguration Registers                                                 | 433  |

|                      | 13.4.1      | Memory Map and Registers                                              | 434  |

|                      |             | Chapter 14 Memory Configuration (MCFG)                                |      |

| 14.1                 | MCFG (      | Overview                                                              | 461  |

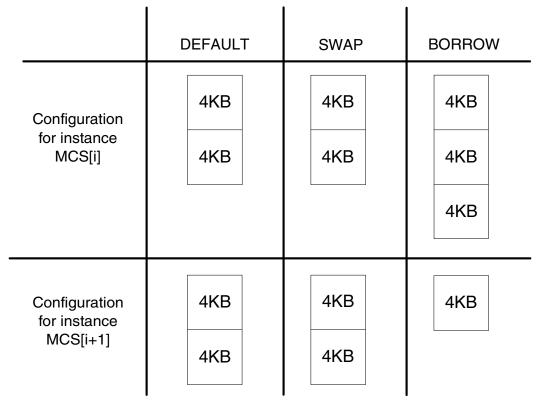

|                      | 14.1.1      | Memory layout configurations (MCS_RAM1_EN_ADDR_MSB = 0)               | 462  |

|                      | 14.1.2      | Memory Layout Parameters (MCS_RAM1_EN_ADDR_MSB = 0)                   | 462  |

|                      | 14.1.3      | Memory Layout Configurations (MCS_RAM1_EN_ADDR_MSB = 1)               | 463  |

| Sec  | tion nu           | mber Title                                           | Page |

|------|-------------------|------------------------------------------------------|------|

|      | 14.1.4            | Memory layout parameters (MCS_RAM1_EN_ADDR_MSB = 1)  | 463  |

| 14.2 | Memory            | Map and Registers                                    | 464  |

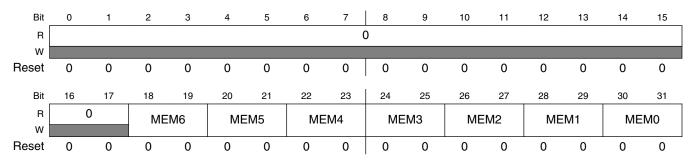

|      | 14.2.1            | Memory Configuration Register (MCFG_CTRL)            | 464  |

|      |                   | Chapter 15 TIM0 Input Mapping Module (MAP)           |      |

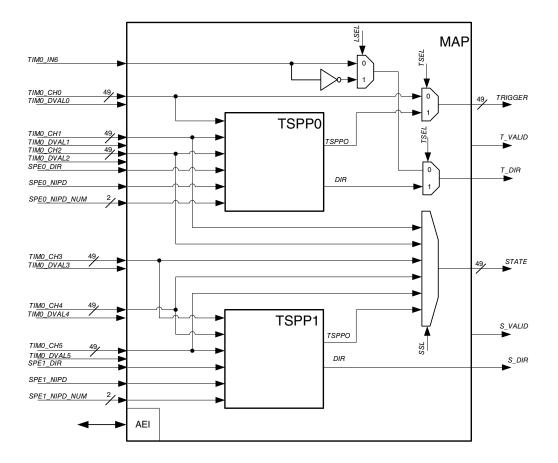

| 15.1 | MAP O             | verview                                              | 467  |

|      | 15.1.1            | MAP Architecture                                     | 467  |

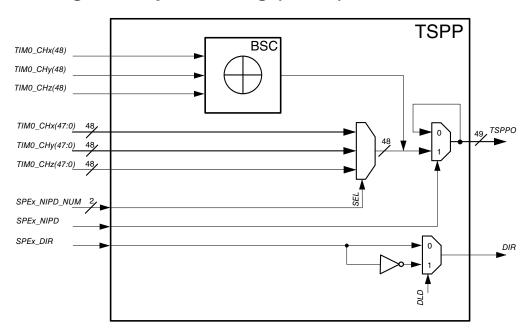

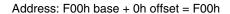

| 15.2 | TIM Sig           | gnal Preprocessing (TSPP)                            | 469  |

|      | 15.2.1            | TIM Signal Preprocessing (TSPP) subunit architecture | 469  |

|      | 15.2.2            | Bit Stream Combination.                              | 470  |

| 15.3 | Memory            | Map and Registers                                    | 471  |

|      | 15.3.1            | TIM0 Input MAP Control Register (MAP_CTRL)           | 472  |

|      |                   | Chapter 16<br>Digital PLL Module (DPLL)              |      |

| 16.1 | DPLL O            | Overview                                             | 475  |

| 16.2 | Require           | ments and demarcation                                | 476  |

| 16.3 | DPLL b            | lock diagram and interface description               | 478  |

| 16.4 | DPLL Architecture |                                                      | 481  |

|      | 16.4.1            | Purpose of the module                                | 481  |

|      | 16.4.2            | Explanation of the prediction methodology            | 482  |

|      | 16.4.3            | Clock topology                                       | 482  |

|      | 16.4.4            | Clock generation.                                    |      |

|      | 16.4.5            | Typical frequencies                                  | 482  |

|      | 16.4.6            | Time stamps and systematic corrections               | 482  |

|      | 16.4.7            | DPLL Architecture overview                           | 484  |

|      | 16.4.8            | DPLL Architecture description                        | 486  |

|      | 16.4.9            | Block diagrams of time stamp processing.             | 488  |

| Section number |                                | mber Title                                                      | Page    |

|----------------|--------------------------------|-----------------------------------------------------------------|---------|

|                | 16.4.10                        | Register and RAM address overview                               | 490     |

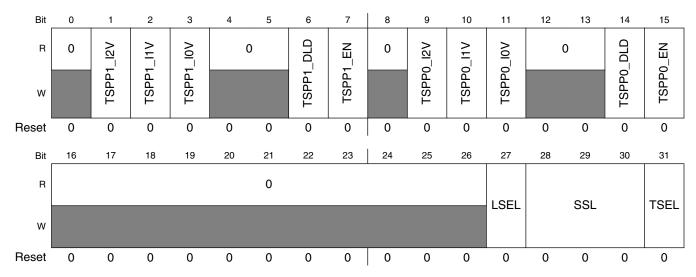

| 16.5           | Predictio                      | n of current increment duration                                 | 495     |

|                | 16.5.1                         | The use of increments in the past                               | 495     |

|                | 16.5.2                         | Increment prediction in Normal Mode forwards (DIR1=0)           | 496     |

|                | 16.5.3                         | Increment prediction in Emergency Mode forward (DIR2=0)         | 500     |

|                | 16.5.4                         | Increment prediction in Normal Mode backward (DIR1=1)           | 503     |

|                | 16.5.5                         | Increment prediction in Emergency Mode backward (DIR2=1)        | 505     |

| 16.6           | Calculati                      | ons for actions                                                 | 507     |

|                | 16.6.1                         | Action calculations for TRIGGER forward                         | 509     |

|                | 16.6.2                         | Action calculations for TRIGGER backward                        | 512     |

|                | 16.6.3                         | Action calculations for STATE forwards                          | 516     |

|                | 16.6.4                         | Action calculations for STATE backwards                         | 519     |

|                | 16.6.5                         | Update of RAM in Normal and Emergency Mode                      | 522     |

|                | 16.6.6                         | Time and position stamps for actions in Normal Mode             | 527     |

|                | 16.6.7                         | The use of the RAM                                              | 531     |

|                | 16.6.8                         | Time and position stamps for actions in Emergency Mode          | 531     |

| 16.7           | Signal processing.             |                                                                 | 534     |

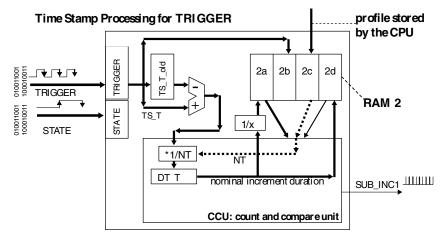

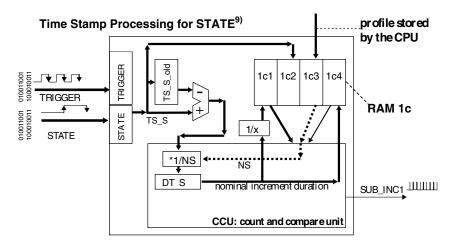

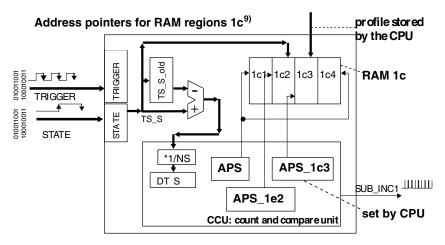

|                | 16.7.1                         | Time stamp processing                                           | 534     |

|                | 16.7.2                         | Count and compare unit                                          | 535     |

|                | 16.7.3                         | Sub pulse generation for SMC=0                                  | 535     |

|                | 16.7.4                         | Sub pulse generation for SMC = 1                                | 541     |

|                | 16.7.5                         | Calculation of Accurate Position Values                         | 545     |

|                | 16.7.6                         | Scheduling of the Calculation                                   | 546     |

| 16.8           | DPLL In                        | terrupt signals                                                 | 568     |

| 16.9           | DPLL Memory Map and Registers. |                                                                 | 570     |

|                | 16.9.1                         | Control Register 0 (DPLL_CTRL_0)                                | 576     |

|                | 16.9.2                         | Control Register 1 (DPLL_CTRL_1)                                | 578     |

|                | 16.9.3                         | Action Enable Register (DPLL_CTRL_2)                            | 583     |

|                | 16.9.4                         | Action Enable Register (DPLL_CTRL_3)                            | 586     |

|                |                                | Generic Timer Module 104 (GTM104) Reference Manual, Rev. 1, 3 F | eb 2015 |

| Section nur | nber Title                                                                                      | Page |

|-------------|-------------------------------------------------------------------------------------------------|------|

| 16.9.5      | Action Enable Register (DPLL_CTRL_4)                                                            | 589  |

| 16.9.6      | Action Enable Register (DPLL_CTRL_5)                                                            | 593  |

| 16.9.7      | Action Status Register including Shadow Register (DPLL_ACT_STA)                                 | 596  |

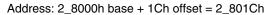

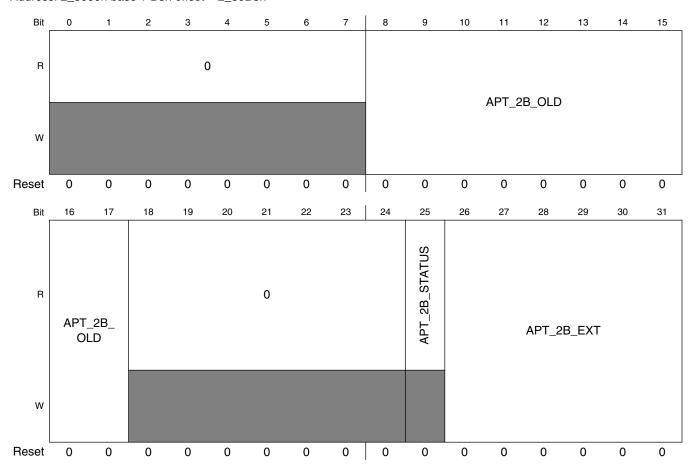

| 16.9.8      | Offset and Switch Old/New Address Register (DPLL_OSW)                                           | 597  |

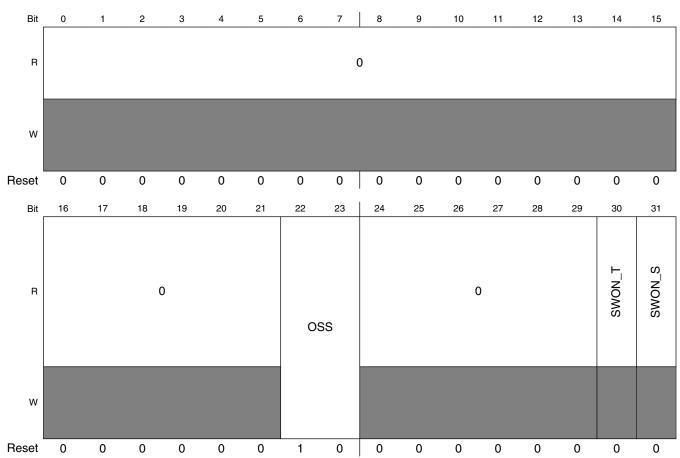

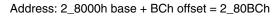

| 16.9.9      | Address Offset Register of RAM2 Regions (DPLL_AOSV_2)                                           | 598  |

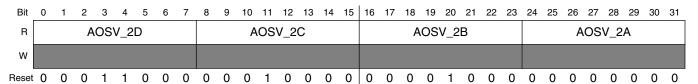

| 16.9.10     | Actual RAM Pointer Address for Trigger (DPLL_APT)                                               | 599  |

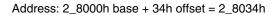

| 16.9.11     | Actual RAM Pointer Address for STATE (DPLL_APS)                                                 | 601  |

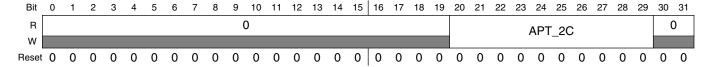

| 16.9.12     | Actual RAM Pointer Address for Region 2C (DPLL_APT_2C)                                          | 602  |

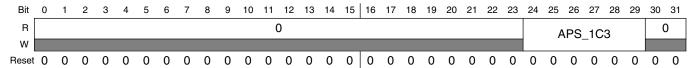

| 16.9.13     | Actual RAM Pointer Address for Region 1C3 (DPLL_APS_1C3)                                        | 603  |

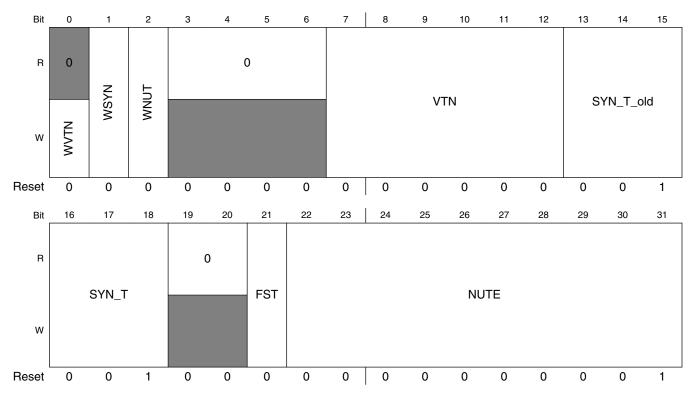

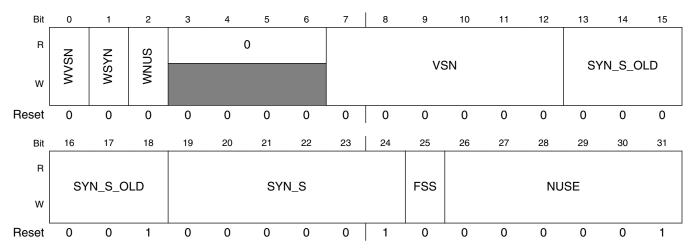

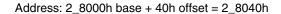

| 16.9.14     | Number of Recent TRIGGER Events used for Calculations (DPLL_NUTC)                               | 604  |

| 16.9.15     | Number of Recent STATE Events used for Calculations (DPLL_NUSC)                                 | 606  |

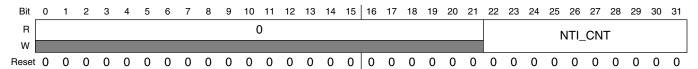

| 16.9.16     | Number of Active TRIGGER Events to Interrupt (DPLL_NTI_CNT)                                     | 607  |

| 16.9.17     | Interrupt Register (DPLL_IRQ_NOTIFY)                                                            | 608  |

| 16.9.18     | Interrupt Enable Register (DPLL_IRQ_EN)                                                         | 611  |

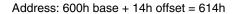

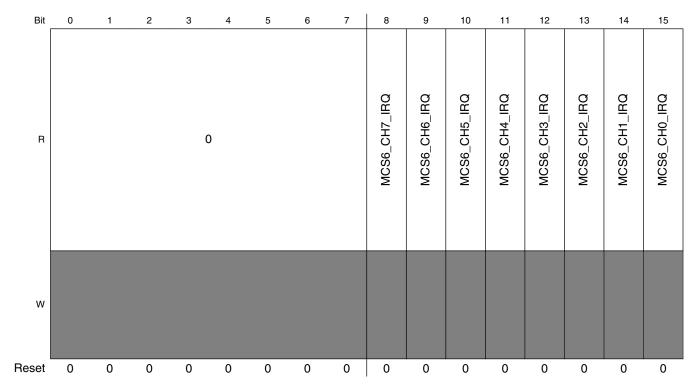

| 16.9.19     | Force Interrupt Register (DPLL_IRQ_FORCINT)                                                     | 614  |

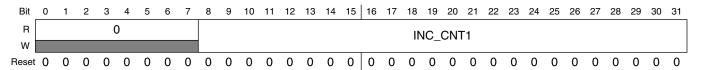

| 16.9.20     | Interrupt Request Mode (DPLL_IRQ_MODE)                                                          | 618  |

| 16.9.21     | Error Interrupt Enable Register (DPLL_EIRQ_EN)                                                  | 619  |

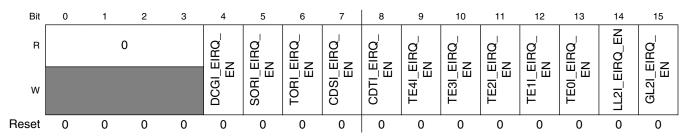

| 16.9.22     | Counter Value of Sent SUB_INC1 Pulses (DPLL_INC_CNT1)                                           | 622  |

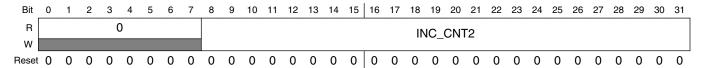

| 16.9.23     | Counter Value of sent SUB_INC2 values (for SMC=1 and RMO=1) (DPLL_INC_CNT2)                     | 623  |

| 16.9.24     | TRIGGER Time Stamp Field Offset at Synchronization Time (DPLL_APT_SYNC)                         | 624  |

| 16.9.25     | STATE Time Stamp Field Offset at Synchronization Time (DPLL_APS_SYNC)                           | 626  |

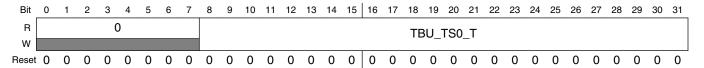

| 16.9.26     | Time Stamp Value for the last valid TRIGGER (DPLL_TBU_TS0_T)                                    | 627  |

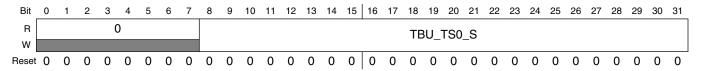

| 16.9.27     | Time Stamp Value for the last valid STATE (DPLL_TBU_TS0_S)                                      | 628  |

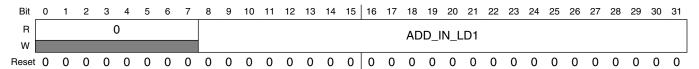

| 16.9.28     | ADD_IN Value in Direct Load Mode for TRIGGER (DPLL_ADD_IN_LD1)                                  | 628  |

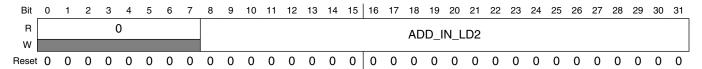

| 16.9.29     | ADD_IN Value in Direct Load Mode for STATE (DPLL_ADD_IN_LD2)                                    | 629  |

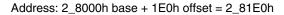

| 16.9.30     | Status Register (DPLL_STATUS)                                                                   | 629  |

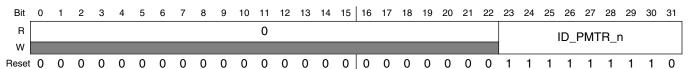

| 16.9.31     | ID Information for In ut Signal PTR x (Position minus Time Request) (DPLL_ID_PMTR_n)            | 635  |

| 16.9.32     | Shadow Register of DPLL_CTRL_0 controlled by a valid TRIGGER Slope (DPLL_CTRL_0_SHADOW_TRIGGER) | 636  |

| Section n | umber Title                                                                                     | Page |

|-----------|-------------------------------------------------------------------------------------------------|------|

| 16.9.3    | Shadow Register of DPLL_CTRL_0 controlled by a valid STATE Slope (DPLL_CTRL_0_SHADOW_STATE)     | 637  |

| 16.9.34   | Shadow Register of DPLL_CTRL_1 controlled by a valid TRIGGER Slope (DPLL_CTRL_1_SHADOW_TRIGGER) | 638  |

| 16.9.3    | 5 Shadow Register of DPLL_CTRL_1 controlled by a valid STATE Slope (DPLL_CTRL_1_SHADOW_STATE)   | 640  |

| 16.9.3    | 6 Register to control the RAM Initialization (DPLL_RAM_INI)                                     | 642  |

| 16.9.3    | 7 Calculated Time Value to start Action i (DPLL_TSAC_n)                                         | 643  |

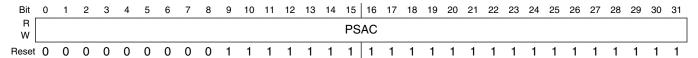

| 16.9.3    | 8 DPLL Calculated Position Value ACTION i (DPLL_PSAC_n)                                         | 644  |

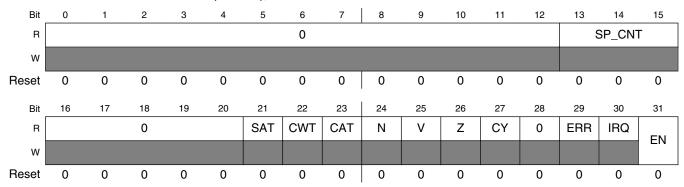

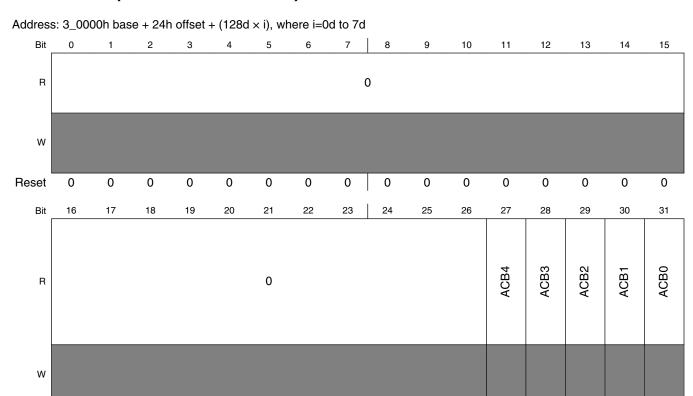

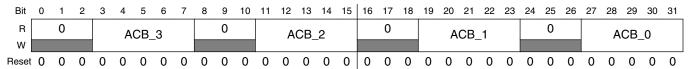

| 16.9.39   | 9 Control Bits for up to 32 Actions (DPLL_ACB_n)                                                | 644  |

| 16.10 RAM | Region 1A Memory Map and Registers                                                              | 645  |

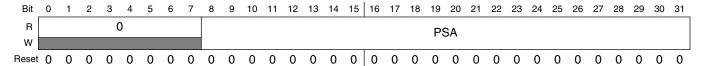

| 16.10.    | Position Action Request for ACTION n (PSAn)                                                     | 645  |

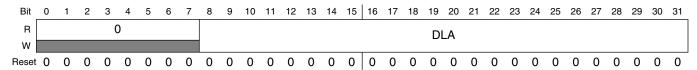

| 16.10.    | 2 Time to React for Action n (DLAn)                                                             | 651  |

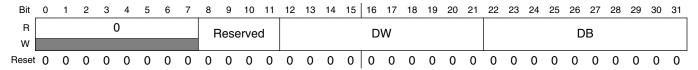

| 16.10.    | 3 Calculated Number of TRIGGER/STATE Increments to Action n (NAn)                               | 651  |

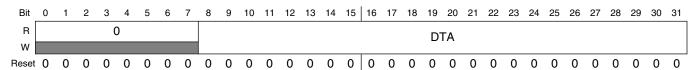

| 16.10.    | 4 Calculated Relative Time to Action n (DTAn)                                                   | 652  |

| 16.11 RAM | Region 1B Memory Map and Registers                                                              | 652  |

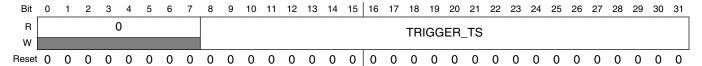

| 16.11.    | 1 Actual TRIGGER Time Stamp Value (TS_T)                                                        | 653  |

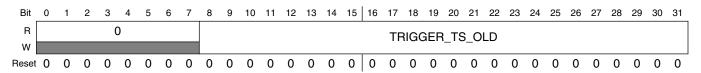

| 16.11.    | 2 Previous TRIGGER Time Stamp Value (TS_T_OLD)                                                  | 657  |

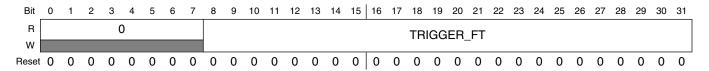

| 16.11.    | 3 Actual TRIGGER Filter Value (FTV_T)                                                           | 657  |

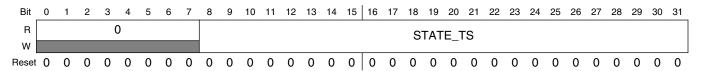

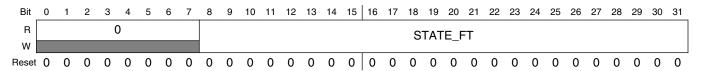

| 16.11.    | 4 Actual STATE Time Stamp Register (TS_S)                                                       | 658  |

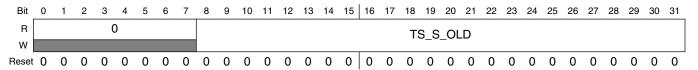

| 16.11.:   | 5 Previous STATE Time Stamp Register (TS_S_OLD)                                                 | 658  |

| 16.11.    | 6 Actual STATE Filter Value (FTV_S)                                                             | 659  |

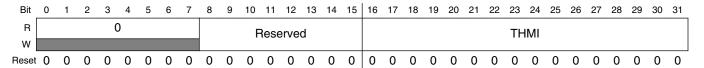

| 16.11.    | 7 TRIGGER Hold Time Minimum Value (THMI)                                                        | 659  |

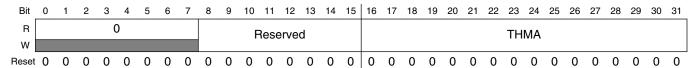

| 16.11.    | 8 TRIGGER Hold Time Maximum Value (THMA)                                                        | 660  |

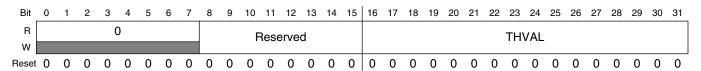

| 16.11.9   | 9 Measured TRIGGER Hold Time Value (THVAL)                                                      | 660  |

| 16.11.    | 10 Time Out Value of Active TRIGGER Slope (for missing TRIGGER generation) (TOV)                | 661  |

| 16.11.    | 11 Time Out Value of Actvie STATE Slope (for missing STATE generation) (TOV_S)                  | 662  |

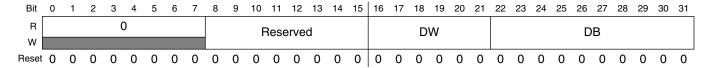

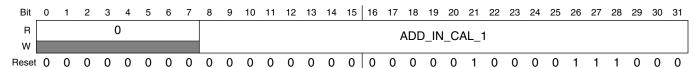

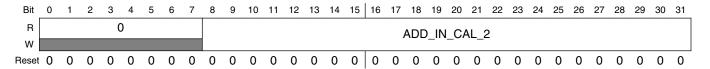

| 16.11.    | 12 Calculated ADD_IN Value for SUB_INC1 Generation (ADD_IN_CAL1)                                | 663  |

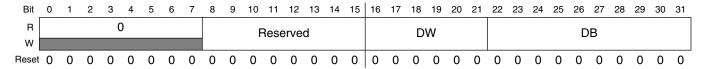

| 16.11.    | 13 Calculated ADD_IN Value for SUB_INC2 Generation (ADD_IN_CAL2)                                | 663  |

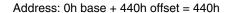

| 16.11.    | 14 Missing Pulses to be Added or Subtracted Directly (MPVAL1)                                   | 664  |

|           | Generic Timer Module 104 (GTM104) Reference Manual, Rev. 1, 3 Feb 2015                          |      |

| Section nun | nber Title                                                                           | Page |

|-------------|--------------------------------------------------------------------------------------|------|

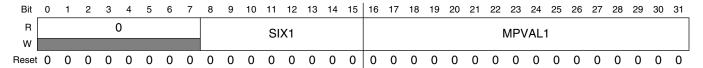

| 16.11.15    | Missing Pulses to be Added or Subtracted Directly (MPVAL2)                           | 664  |

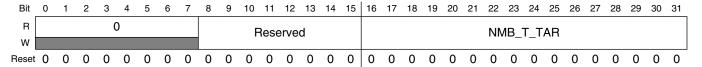

| 16.11.16    | Target Number of Pulses to be Sent in Normal Mode (NMB_T_TAR)                        | 665  |

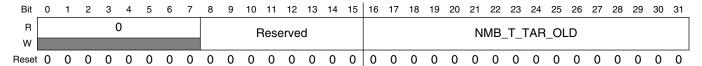

| 16.11.17    | Last but one Target Number of Pulses to be sent in Normal Mode (NMB_T_TAR_OLD)       | 666  |

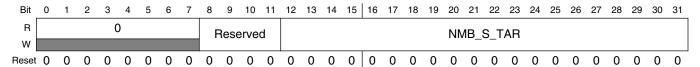

| 16.11.18    | Target Number Of Pulses to be Sent In Emergency Mode (NMB_S_TAR)                     | 666  |

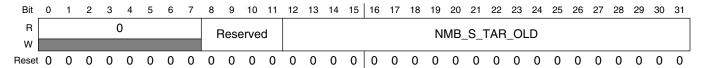

| 16.11.19    | Last but one Target Number Of Pulses to be Sent In Emergency Mode (NMB_S_TAR_OLD)    | 667  |

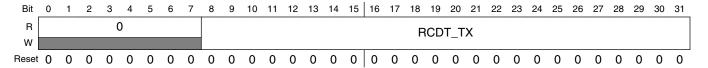

| 16.11.20    | Reciprocal Value of the Expected Increment Duration of TRIGGER (RCDT_TX)             | 667  |

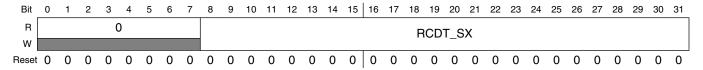

| 16.11.21    | Reciprocal Value of the Expected Increment Duration of STATE (RCDT_SX)               | 668  |

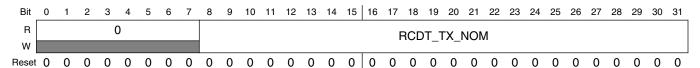

| 16.11.22    | Reciprocal Value of the Expected Nominal Increment Duration of TRIGGER (RCDT_TX_NOM) | 668  |

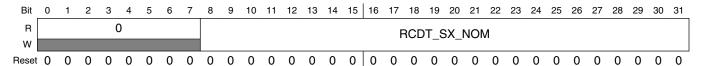

| 16.11.23    | Reciprocal Value of the Expected Nominal Increment Duration of STATE (RCDT_SX_NOM)   | 669  |

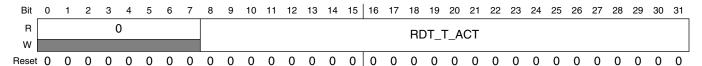

| 16.11.24    | Reciprocal Value of last Increment of TRIGGER (RDT_T_ACT)                            | 669  |

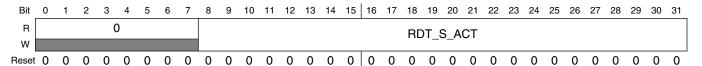

| 16.11.25    | Reciprocal Value of the Last Increment of STATE (RDT_S_ACT)                          | 670  |

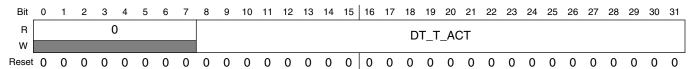

| 16.11.26    | Duration of the Last TRIGGER Increment (DT_T_ACT)                                    | 670  |

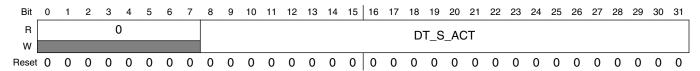

| 16.11.27    | Duration of the Last STATE Increment (DT_S_ACT)                                      | 671  |

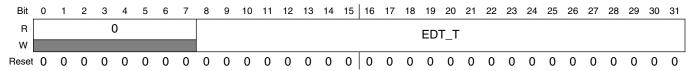

| 16.11.28    | Difference of Prediction to Actual Value of the Last TRIGGER Increment (EDT_T)       | 671  |

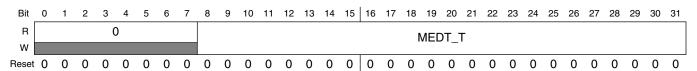

| 16.11.29    | Weighted Difference of Prediction Errors of TRIGGER (MEDT_T)                         | 671  |

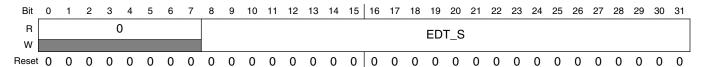

| 16.11.30    | Difference of Prediction to Actual Value of the Last STATE Increment (EDT_S)         | 672  |

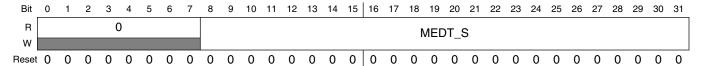

| 16.11.31    | Weighted Difference of Prediction Errors of STATE (MEDT_S)                           | 672  |

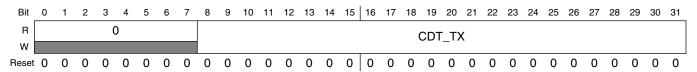

| 16.11.32    | Prediction of the Actual TRIGGER Increment Duration (CDT_TX)                         | 673  |

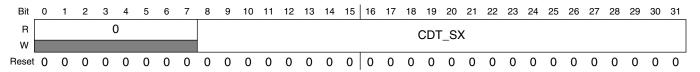

| 16.11.33    | Prediction of the Actual STATE Increment Duration (CDT_SX)                           | 673  |

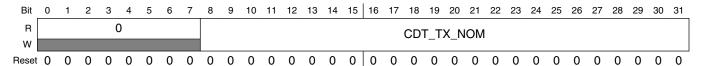

| 16.11.34    | Prediction of the Nominal TRIGGER Increment Duration (CDT_TX_NOM)                    | 674  |

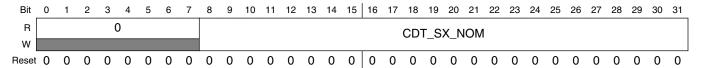

| 16.11.35    | Prediction of the Nominal STATE Increment Duration (CDT_SX_NOM)                      | 674  |

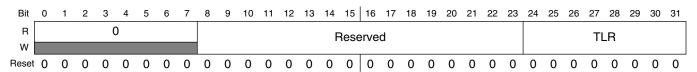

| 16.11.36    | TRIGGER Locking Range (TLR)                                                          | 674  |

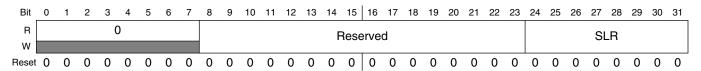

| 16.11.37    | STATE Locking Range (SLR)                                                            | 675  |

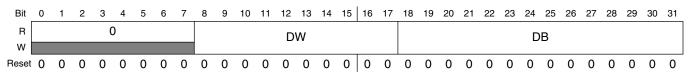

| 16.11.38    | Projected Increment Sum Relations for Action n (PDTn)                                | 675  |

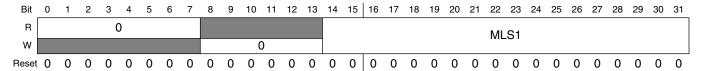

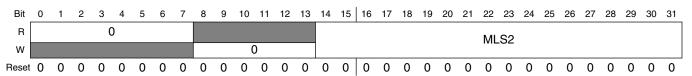

| 16.11.39    | Calculated Number of Sub-Pulses between two STATE Events for SMC=0 (MLS1)            | 676  |

| 16.11.40    | Calculated Number of Sub-pulses between two STATE Events for SMC=1 and RMO=1 (MLS2)  | 676  |

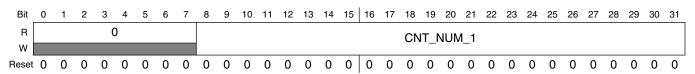

| 16.11.41    | Counter for number of SUB_INC1 pulses (CNT_NUM1)                                     | 677  |

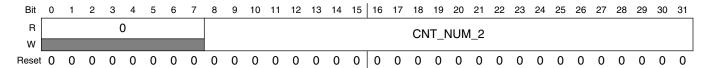

| 16.11.42    | Counter for number of SUB_INC2 pulses (CNT_NUM2)                                     | 677  |

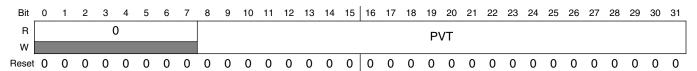

| 16.11.43    | Plausibility Value of Next TRIGGER Slope (PVT)                                       | 678  |

| 13.11.13    | Generic Timer Module 104 (GTM104) Reference Manual, Rev. 1, 3 Feb 2015               | 010  |

| Sect  | ion nun   | nber Title                                                                         | Page |

|-------|-----------|------------------------------------------------------------------------------------|------|

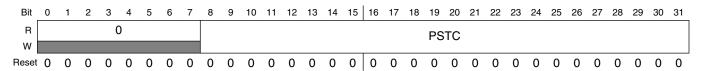

|       | 16.11.44  | Actual Calculated Position Stamp of TRIGGER (PSTC)                                 | 678  |

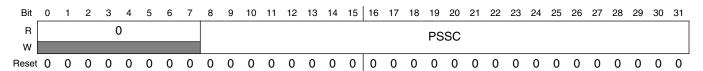

|       | 16.11.45  | Actual Calculated Position Stamp of STATE (PSSC)                                   | 679  |

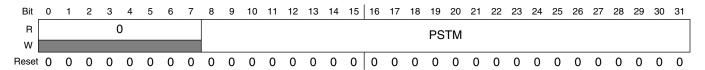

|       | 16.11.46  | Measured Position Stamp at Last TRIGGER Input (PSTM)                               | 679  |

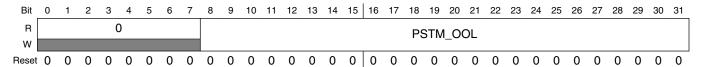

|       | 16.11.47  | Measured Position Stamp at Last But One TRIGGER Input (PSTM_OLD)                   | 680  |

|       | 16.11.48  | Measured Position Stamp at Last STATE Input (PSSM)                                 | 680  |

|       | 16.11.49  | Measured Position Stamp at Last but One STATE Input (PSSM_OLD)                     | 681  |

|       | 16.11.50  | Number of Pulses to be Sent in Normal Mode (NMB_T)                                 | 681  |

|       | 16.11.51  | Number of Pulses to be Sent in Emergency Mode (NMB_S)                              | 682  |

| 16.12 | RAM Re    | gion 1C Memory Map and Registers                                                   | 682  |

|       | 16.12.1   | Reciprocal Values of the Nominal STATE Increment Durations in FULL SCALE (RDT_Sn)  | 682  |

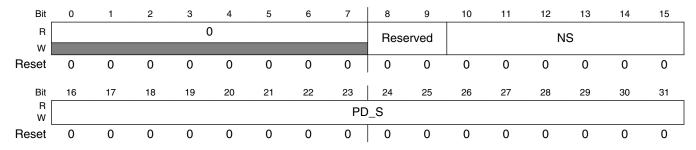

|       | 16.12.2   | Time Stamp Values of the Nominal STATE Events in FULL SCALE (TSF_Sn)               | 695  |

|       | 16.12.3   | Adapt and Profile Values STATE Increments in FULL SCALE (ADT_Sn)                   | 695  |

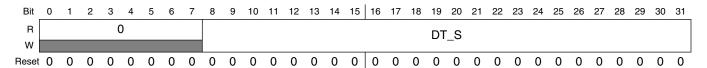

|       | 16.12.4   | Nominal STATE Increment Durations in FULL SCALE (DT_Sn)                            | 696  |

| 16.13 | RAM Re    | gion 2 Memory Map and Registers                                                    | 696  |

|       | 16.13.1   | Reciprocal Values of the Nominal TRIGGER Increment Durations in FULL_SCALE (RDT_T) | 697  |

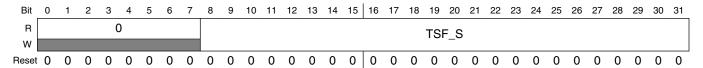

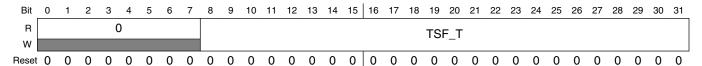

|       | 16.13.2   | Time Stamp Values of the Nominal TRIGGER Increments in FULL_SCALE (TSF_T)          | 698  |

|       | 16.13.3   | Adapt and Profile Values of the TRIGGER Increments in FULL_SCALE (ADT_T)           | 698  |

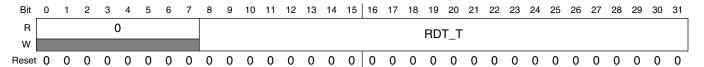

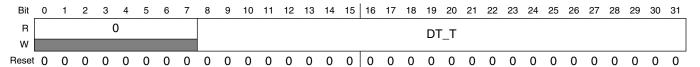

|       | 16.13.4   | Nominal TRIGGER Increment Durations in FULL_SCALE (DT_T)                           | 699  |

|       |           | Chapter 17 Sensor Pattern Evaluation (SPE)                                         |      |

| 17.1  | SPE Over  | rview                                                                              | 701  |

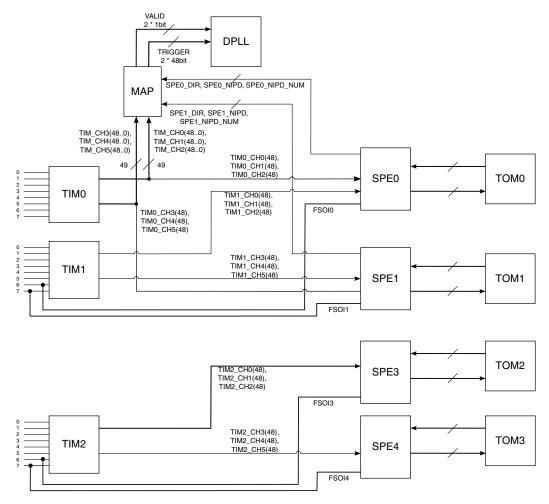

|       | 17.1.1    | SPE Submodule integration concept into GTM                                         | 701  |

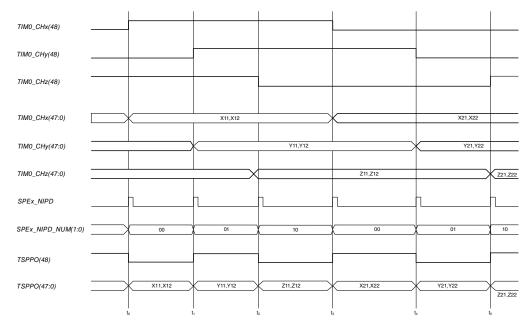

|       | 17.1.2    | SPE Sample input pattern for TIM[i]_CH[x,y,z](48)                                  | 702  |

| 17.2  | SPE Subi  | nodule description                                                                 | 703  |

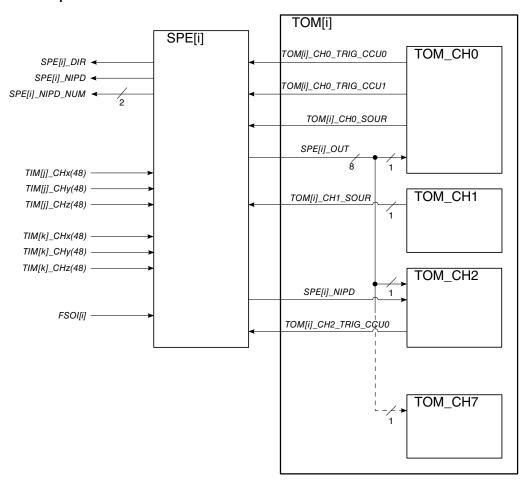

|       | 17.2.1    | SPE to TOM Connections                                                             | 703  |

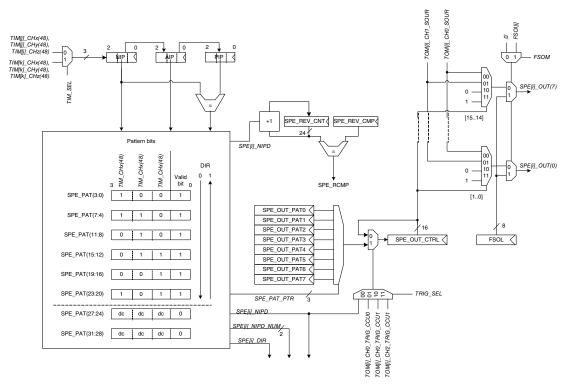

|       | 17.2.2    | SPE Submodule architecture                                                         | 704  |

|       | 17.2.3    | SPE[i]_IN_PAT register representation.                                             | 706  |

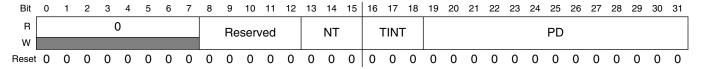

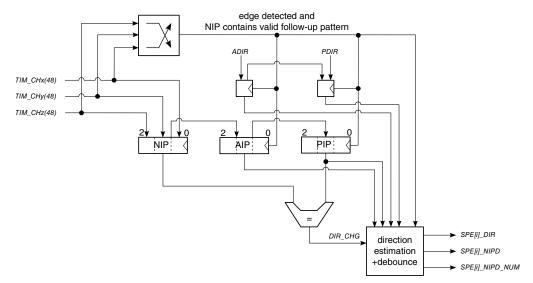

|       | 17.2.4    |                                                                                    | 707  |

| 17.3  | SPE Inter | rupt signals                                                                       | 708  |

|       |           |                                                                                    |      |

| Section number Title |          |                                                                     | Page |  |

|----------------------|----------|---------------------------------------------------------------------|------|--|

| 17.4                 | Memory   | Map and Registers                                                   | 708  |  |

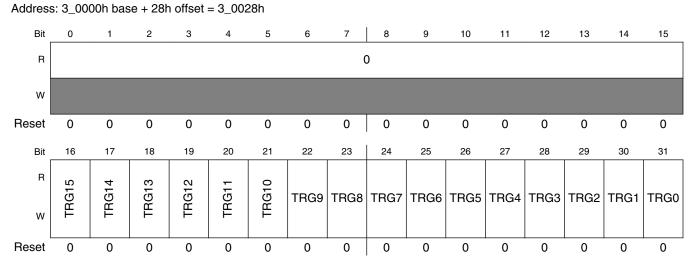

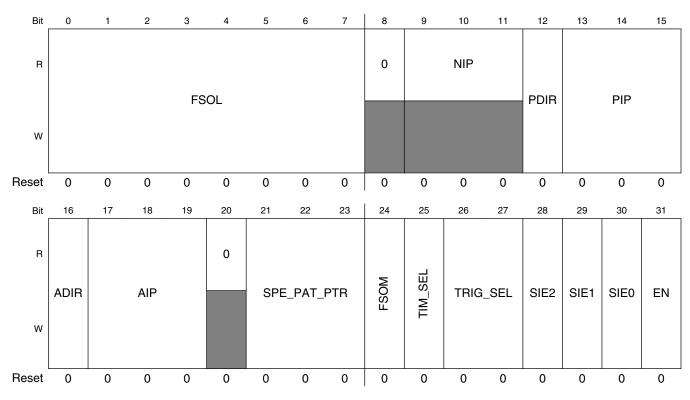

|                      | 17.4.1   | SPE0 Control Status Register (SPE_0_CTRL_STAT)                      | 709  |  |

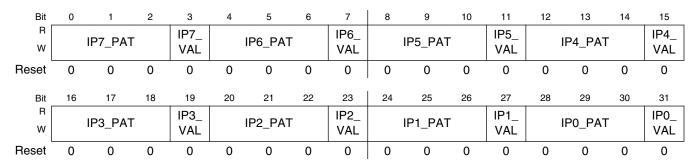

|                      | 17.4.2   | SPE0 Input Pattern Register (SPE_0_PAT)                             | 711  |  |

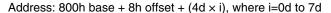

|                      | 17.4.3   | SPE0 Output Pattern n Register (SPE_0_OUT_PATn)                     | 714  |  |

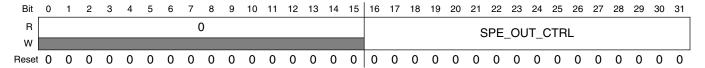

|                      | 17.4.4   | SPE0 Output Control Register (SPE_0_OUT_CTRL)                       | 714  |  |

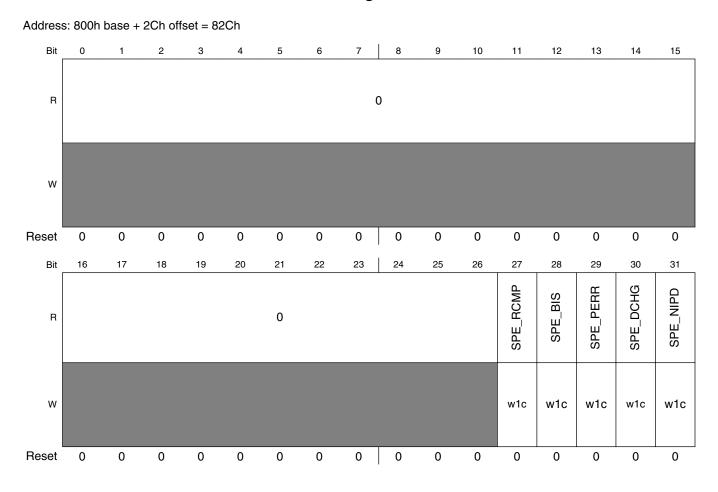

|                      | 17.4.5   | SPE0 Interrupt Request Notify Register (SPE_0_IRQ_NOTIFY)           | 715  |  |

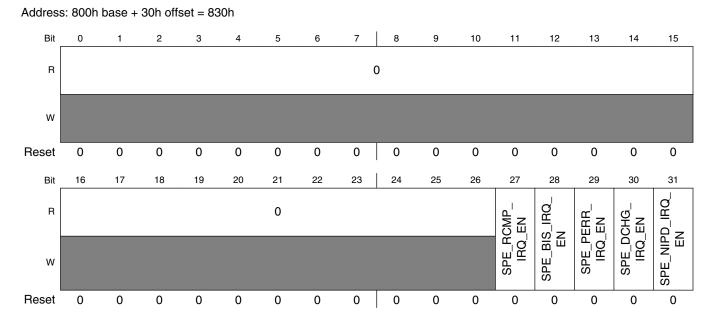

|                      | 17.4.6   | SPE0 Interrupt Request Enable Register (SPE_0_IRQ_EN)               | 716  |  |

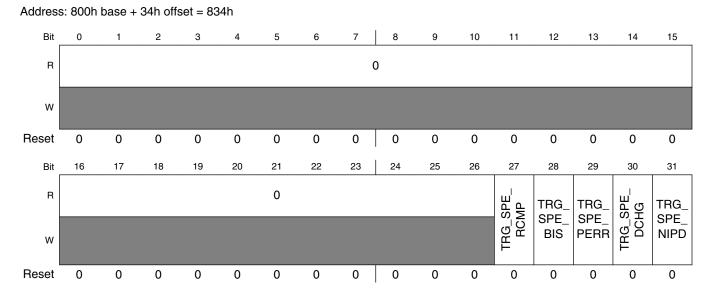

|                      | 17.4.7   | SPE0 Interrupt Request Force Interrupt Register (SPE_0_IRQ_FORCINT) | 718  |  |

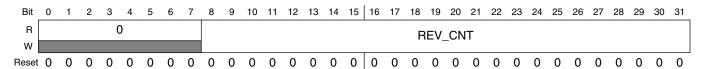

|                      | 17.4.8   | SPE0 Interrupt Request Mode Register (SPE_0_IRQ_MODE)               | 719  |  |

|                      | 17.4.9   | SPE0 Error Interrupt Request Enable register (SPE_0_EIRQ_EN)        | 720  |  |

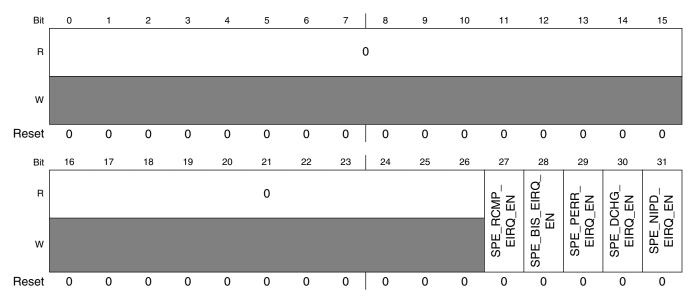

|                      | 17.4.10  | SPE0 Revolution Counter register (SPE_0_REV_CNT)                    | 721  |  |

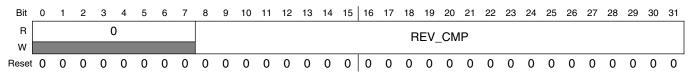

|                      | 17.4.11  | SPE0 Revolution Counter Compare register (SPE_0_REV_CMP)            | 721  |  |

|                      |          | Chapter 18 Interrupt Concentrator Module (ICM)                      |      |  |

| 18.1                 | ICM Ove  | erview                                                              | 723  |  |

| 18.2                 | Bundling | <u> </u>                                                            | 723  |  |

|                      | 18.2.1   | GTM Infrastructure Interrupt Bundling                               | 723  |  |

|                      | 18.2.2   | DPLL Interrupt Bundling                                             | 724  |  |

|                      | 18.2.3   | TIM Interrupt Bundling.                                             | 724  |  |

|                      | 18.2.4   | MCS Interrupt Bundling                                              | 724  |  |

|                      | 18.2.5   | TOM and ATOM Interrupt Bundling                                     | 725  |  |

|                      | 18.2.6   | Module error interrupt bundling                                     | 726  |  |

|                      | 18.2.7   | FIFO channel error interrupt bundling.                              | 726  |  |

|                      | 18.2.8   | TIM channel error interrupt bundling.                               | 726  |  |

|                      | 18.2.9   | MCS channel error interrupt bundling                                | 727  |  |

| 18.3                 | ICM Inte | errupt Signals                                                      | 727  |  |

| 18.4                 | Memory   | Map and Registers                                                   | 729  |  |

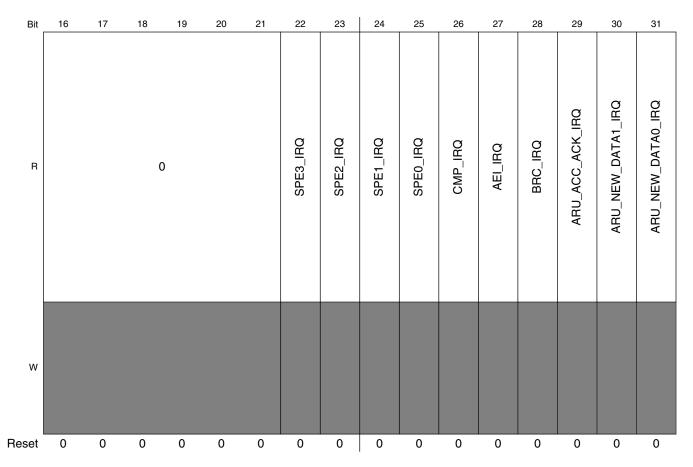

|                      | 18.4.1   | GTM Infrastructure Interrupt Group Register (ICM_IRQG_0)            | 729  |  |

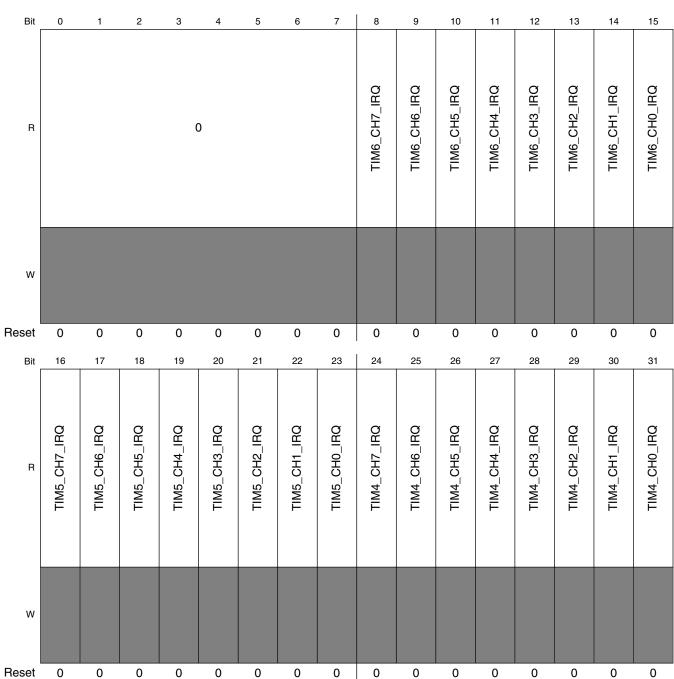

|                      | 18.4.2   | DPLL Interrupt Group Register (ICM_IRQG_1)                          | 735  |  |

| Sec  | tion nui  | mber Title                                                           | Page |

|------|-----------|----------------------------------------------------------------------|------|

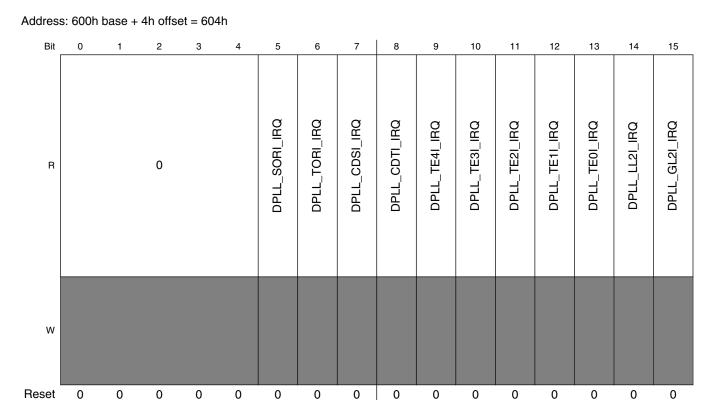

|      | 18.4.3    | TIM Interrupt Group 0 Register (ICM_IRQG_2)                          | 738  |

|      | 18.4.4    | TIM Interrupt Group 1 Register (ICM_IRQG_3)                          | 742  |

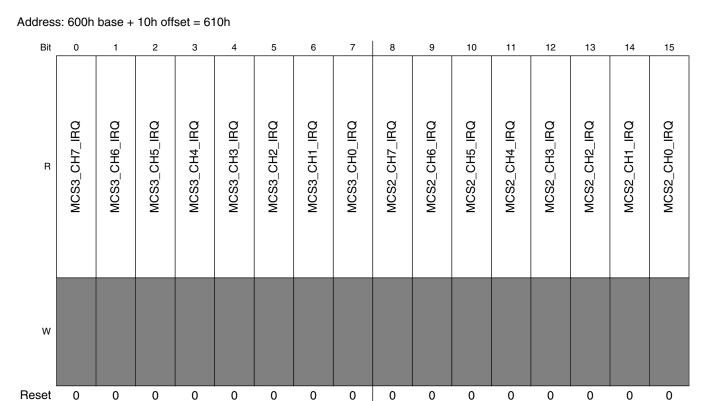

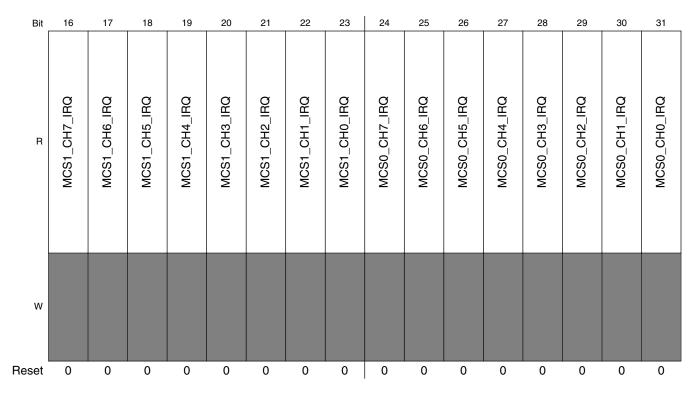

|      | 18.4.5    | MCS Interrupt Group 0 Register (ICM_IRQG_4)                          | 749  |

|      | 18.4.6    | MCS Interrupt Group 1 Register (ICM_IRQG_5)                          | 754  |

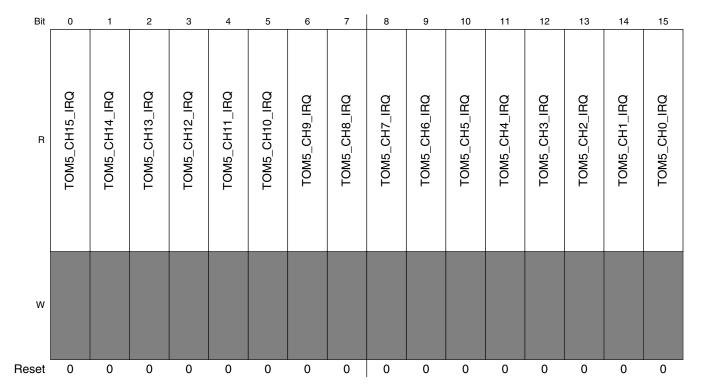

|      | 18.4.7    | TOM Interrupt Group 0 Register (ICM_IRQG_6)                          | 758  |

|      | 18.4.8    | TOM Interrupt Group 1 Register (ICM_IRQG_7)                          | 763  |

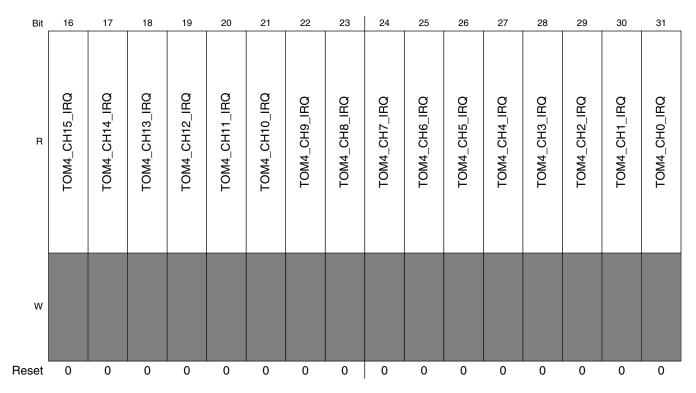

|      | 18.4.9    | TOM Interrupt Group 2 Register (ICM_IRQG_8)                          | 768  |

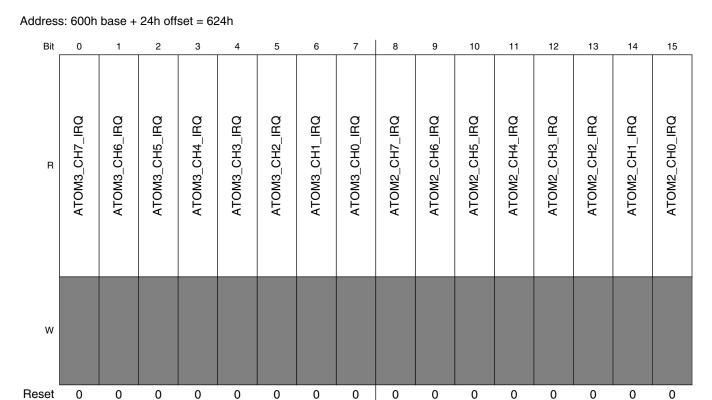

|      | 18.4.10   | ATOM Interrupt Group 0 Register (ICM_IRQG_9)                         | 773  |

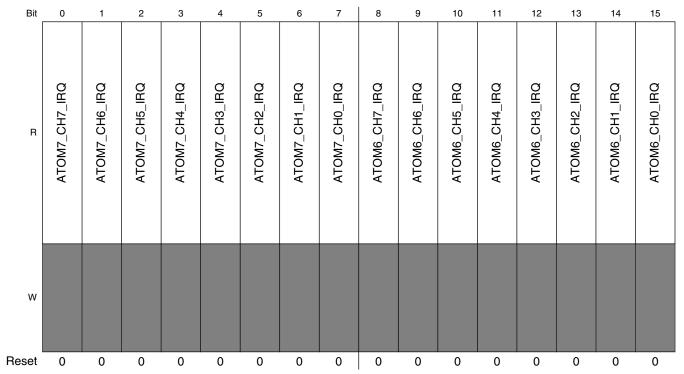

|      | 18.4.11   | ATOM Interrupt Group 1 Register (ICM_IRQG_10)                        | 778  |

|      | 18.4.12   | ATOM Interrupt Group 2 Register (ICM_IRQG_11)                        |      |

|      | 18.4.13   | ICM IRQG Module Error Interrupt register (ICM_IRQG_MEI)              | 788  |

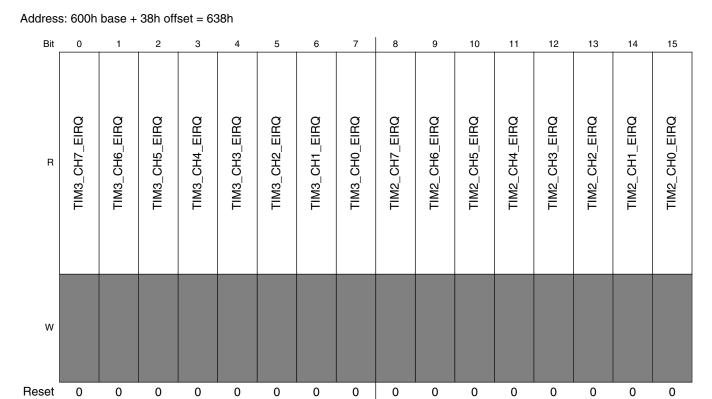

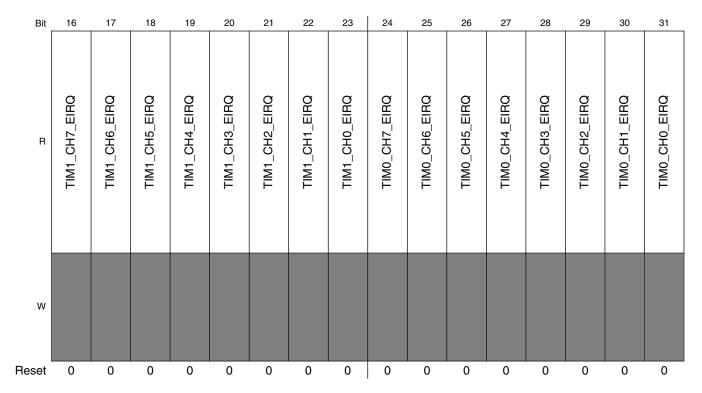

|      | 18.4.14   | ICM Channel Error Interrupt Request Group 0 register (ICM_IRQG_CEI0) | 792  |

|      | 18.4.15   | Channel Error Interrupt Request Group 1 register (ICM_IRQG_CEI1)     | 795  |

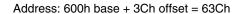

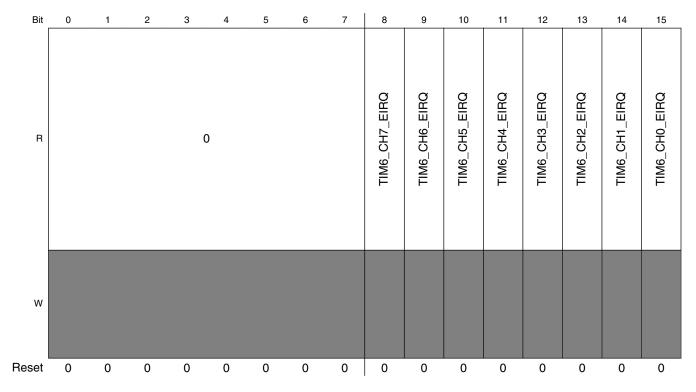

|      | 18.4.16   | Channel Error Interrupt Request Group 2 register (ICM_IRQG_CEI2)     | 800  |

|      | 18.4.17   | Channel Error Interrupt Request Group 3 register (ICM_IRQG_CEI3)     | 804  |

|      | 18.4.18   | Channel Error Interrupt Request Group 4 register (ICM_IRQG_CEI4)     | 809  |

|      |           | Chapter 19 Output Compare Unit (CMP)                                 |      |

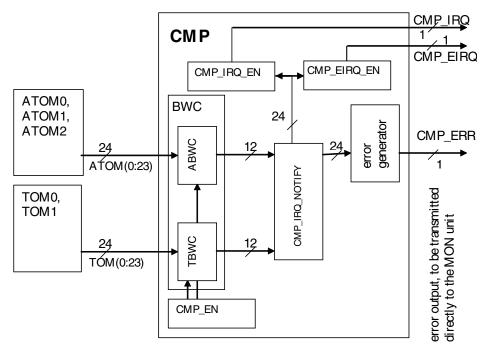

| 19.1 | CMP Ov    | verview                                                              | 813  |

| 19.2 | Bitwise ( | Compare Unit (BWC)                                                   | 814  |

| 19.3 | Configu   | ration of the Compare Unit                                           | 815  |

| 19.4 | Error Ge  | nerator                                                              | 815  |

| 19.5 | CMP Int   | errupt Signal                                                        | 815  |

| 19.6 | Memory    | Map and Registers                                                    | 816  |

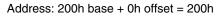

|      | 19.6.1    | Compare Enable Register (CMP_EN)                                     | 816  |

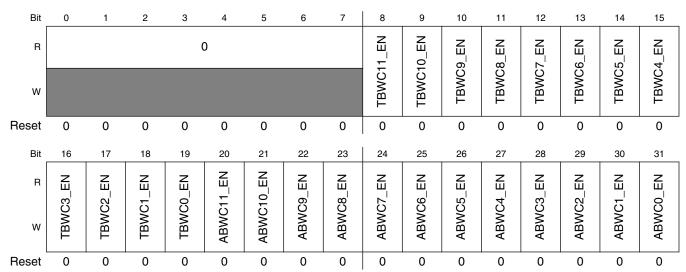

|      | 19.6.2    | Compare Interrupt Request Notification Register (CMP_IRQ_NOTIFY)     | 818  |

|      | 19.6.3    | Compare Interrupt Request Enable Register (CMP_IRQ_EN)               | 820  |

|      | 19.6.4    | Compare Force Interrupt Request Register (CMP_IRQ_FORCINT)           | 822  |

|      | 19.6.5    | Compare Interrupt Request Mode Register (CMP_IRQ_MODE)               | 824  |

|      |           |                                                                      |      |

| Sect | tion num  | ber Title                                                     | Page |

|------|-----------|---------------------------------------------------------------|------|

|      | 19.6.6    | Compare Error Interrupt Request Enable register (CMP_EIRQ_EN) | 825  |

|      |           | Chapter 20<br>Monitor Unit (MON)                              |      |

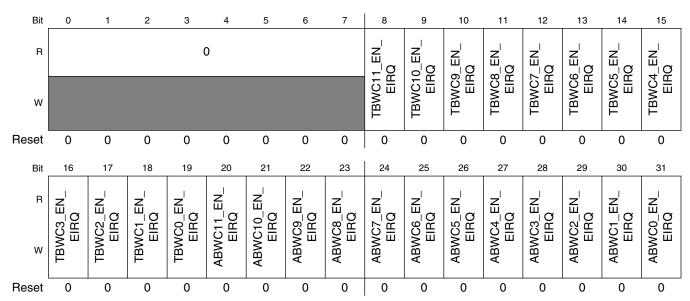

| 20.1 | MON Ove   | rview                                                         | 829  |

|      | 20.1.1    | Realization without Activity Checker for the clock signals    | 830  |

| 20.2 | Clock Mon | nitoring                                                      | 830  |

| 20.3 | CMP error | r Monitoring                                                  | 831  |

| 20.4 | MCS Chec  | cking for Characteristics of Signals                          | 831  |

| 20.5 | Checking  | ARU Cycle Time                                                | 832  |

| 20.6 | MON Inte  | rrupt Signals                                                 | 832  |

| 20.7 | Memory N  | Map and Registers                                             | 832  |

|      | 20.7.1    | Monitor Status Register (MON_STATUS)                          | 833  |

|      | 20.7.2    | Monitor Acitivity 0 (MON_ACTIVITY_0)                          | 835  |

|      | 20.7.3    | Monitor Acitivity 1 (MON_ACTIVITY_1)                          | 838  |

# Chapter 1 Introduction

#### 1.1 Overview

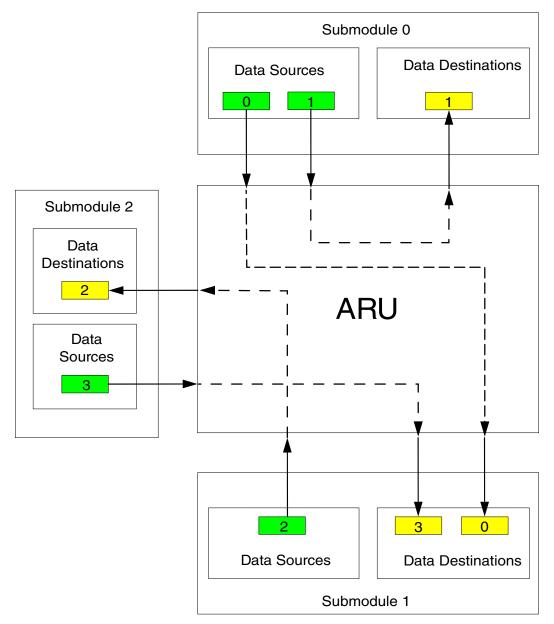

The Generic Timer Module (GTM) is composed of several submodules of different functionality. These submodules can be combined in a configurable manner to form a complex timer module that serves different application domains and different classes within one application domain. Because of this scalability and configurability the timer is called generic. The scalability and configurability is reached with an architecture philosophy where dedicated hardware submodules are located around a central routing unit called Advanced Routing Unit (ARU). The ARU can connect the submodules in a flexible manner. The connectivity is software programmable and can be configured during runtime.

Nevertheless, the GTM is designed to unload the CPU or a peripheral core from a high interrupt load. Most of the tasks inside the GTM can run (once set up by an external CPU) independent and in parallel to the software. There may be special situations, where the CPU has to take action but the goal of the GTM design was to reduce these situations to a minimum. In addition, the timer section of GTM runs at a fixed clock frequency (80 MHz) to allow real time period counting, but the interface to CPU can work with a frequency variable clock.

The GTM is designed to unload the CPU or a peripheral core from a high interrupt load. Most of the tasks inside the GTM can run, after setup by an external CPU, independently and in parallel to the software. There may be special situations, where the CPUhas to take action, but the goal of the GTM design is to reduce these situations to a minimum.

The hardware submodules have dedicated functionalities. By combining the functionality of several submodules through the ARU, complex functions can be established. For example, signals at an input module can be routed to a signal processing unit where intermediate values for the frequencies of the incoming signals can be calculated.

There are five groups of submodules:

#### **Features**

- 1. Submodules that help to implement complex functionalities are called *infrastructural components*. These components are present in all GTM variants. However, the number of these components may vary from one GTM implementation to another.

- 2. Submodules that have general architectures that can fulfil typical timer functions, such as PWM generation units.

- 3. Submodules that fulfil a dedicated functionality for a certain application domain. For example, the DPLL serves engine management applications.

- 4. Submodules that are responsible for supporting the implementation of safety functions to fulfil a defined safety level.

- 5. The ICM module is responsible for interrupt services.

Each GTM implementation is built with submodules from those four groups. An application class is defined by which and how many of those submodules are integrated into the GTM implementation.

#### 1.2 Features

The Generic Timer Module (GTM) has these general features:

- Time base generators

- Advanced data signal / time base router

- Input signal processors (up to 48 inputs)

- Simple output signal generators (up to 80 outputs)

- Microprocessed output signal generators (up to 72 outputs)

- Digital PLL

- BLDC support

- Safety features GTM is a non-safety relevant module

- Output compare unit

- Monitoring unit

- CPU bus interface clock operates asynchronously to timer section clock, allowing CPU low power operation.

#### 1.3 Document Structure

GTM Architecture Overview describes the dedicated GTM implementation for which this specification is written. It gives an overview of the implemented submodules, and their quantity, within this dedicated GTM implementation.

ARU Overview through TBU Overview deal with infrastructural components for routing, clock management, and common time base functions. TIM Overview through ATOM Overview describe the signal input and output modules.

MCS Overview explains the signal processing and generation submodule. MCFG Overview outlines a memory configuration module for the described signal processing and generation submodule.

The next sections provide detailed descriptions of application specific and safety related modules like the MAP, DPLL, SPE, CMP and MON submodules. ICM Overview describes a module that bundles several interrupts coming from other submodules, how they are bundled, and how the bundled result is externally connected.

The submodules are shown in Table 1-1.

Table 1-1. GTM submodules

| Chapter | Submodule                                                   | Group                             |

|---------|-------------------------------------------------------------|-----------------------------------|

| 3       | Advanced Routing Unit (ARU), see ARU Overview               | Infrastructural components        |

| 4       | Broadcast Module (BRC), see BRC Overview                    | Infrastructural components        |

| 5       | First In First Out Module (FIFO), see FIFO Overview         | Infrastructural components        |

| 6       | AEI-to-FIFO Data Interface (AFD), see AFD Overview          | Infrastructural components        |

| 7       | FIFO-to-ARU Interface (F2A), see F2A Overview               | Infrastructural components        |

| 8       | Clock Management Unit (CMU), see CMU Overview               | Infrastructural components        |

| 9       | Time Base Unit (TBU), see TBU Overview                      | Infrastructural components        |

| 10      | Timer Input Module (TIM), see TIM Overview                  | IO Modules                        |

| 11      | Timer Output Module (TOM), see TOM Overview                 | IO Modules                        |

| 12      | ARU-connected Timer Output Module (ATOM), see ATOM Overview | IO Modules                        |

| 13      | Multi Channel Sequencer (MCS), see MCS Overview             | Signal generation and processing  |

| 14      | Memory Configuration Module (MCFG), see MCFG Overview       | Infrastructural component for MCS |

| 15      | TIM0 Input Mapping Module (MAP), see MAP Overview           | Dedicated                         |

| 16      | Digital PLL (DPLL), see DPLL Overview                       | Dedicated                         |

| 17      | Sensor Pattern Evaluation Module (SPE), see SPE Overview    | BLDC support                      |

| 18      | Interrupt Concentrator Module (ICM), see ICM Overview       | Interrupt services                |

| 19      | Output Compare Unit (CMP), see CMP Overview                 | Safety features                   |

| 20      | Monitoring Unit (MON), see MON Overview                     | Safety features                   |

**Document Structure**

# Chapter 2 GTM Architecture

#### 2.1 GTM Architecture Overview

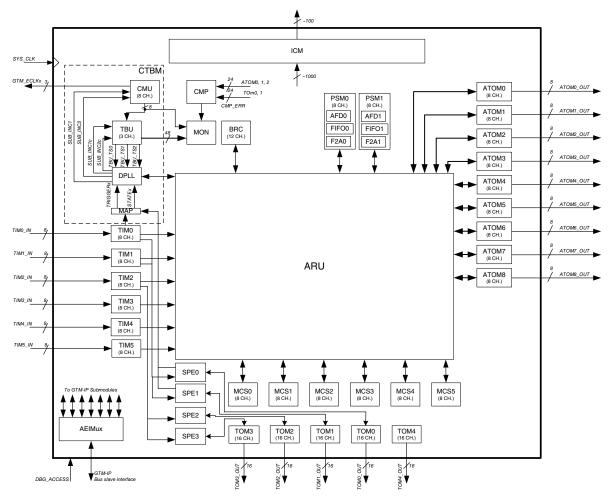

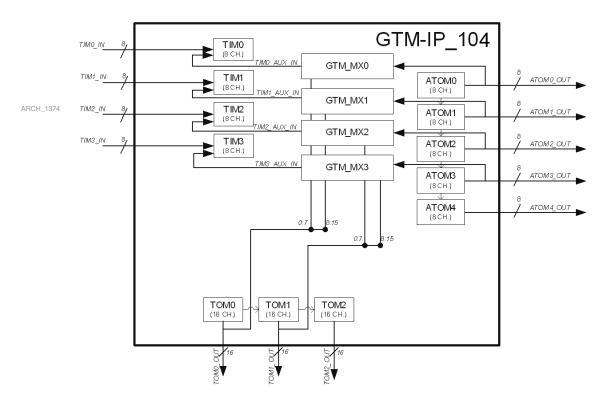

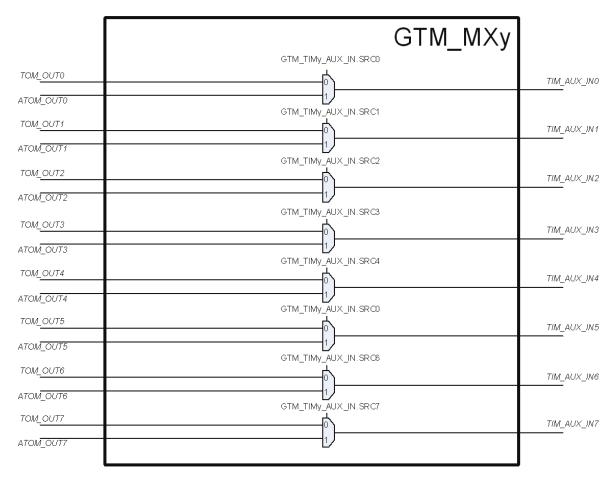

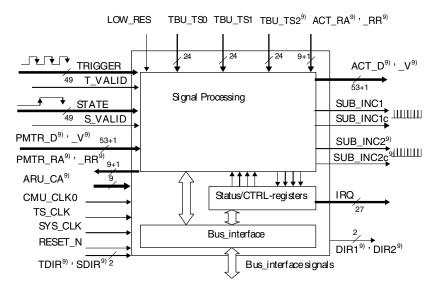

The GTM forms a generic timer platform that serves different application domains and different classes within those application domains. Depending on these multiple requirements of application domains, multiple device configurations with different quantities of submodules (i.e. ATOM, BRC, MCS, PSM, SPE, TIM, TOM) and a different count of channels per submodule (if applicable) are possible. In this document, an example of possible device configurations for the GTM realization is outlined. The architecture of the GTM is depicted in Figure 2-1. Please note, that the size of the submodules in the figure does not reflect the die size of the modules in the final RTL implementation. The device dependent configuration (i.e the count of submodules) is listed in the device specific Appendix B of this document.

#### 2.1.1 GTM Architecture

As an example of a possible device configuration, the GTM104 realization is shown in the figure below.

The device dependent configuration (i.e. the count of submodules and channels per submodule) is listed in the device specific Appendix B of this document.

Figure 2-1. GTM104 architecture block diagram

### 2.1.2 Advanced Routing Unit (ARU) Brief Description

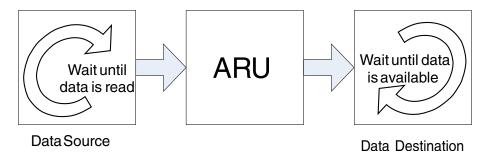

The Advanced Routing Unit (ARU) is the central component of the GTM. Most of the submodules are located around, and connected to, the ARU. The ARU forms, together with the Broadcast (BRC) module and the Parameter Storage Module (PSM), the infrastructural part of the GTM. The ARU uses a round-robin scheduling scheme of connected channels to route data from a connected source submodule to a connected destination submodule. The routing is done in a deterministic manner with a worst case round-trip time.

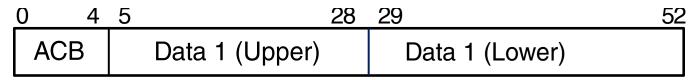

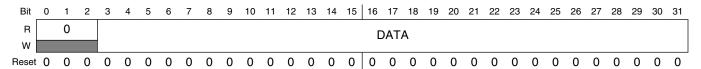

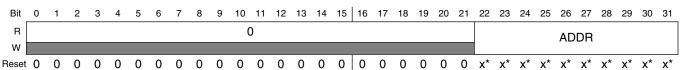

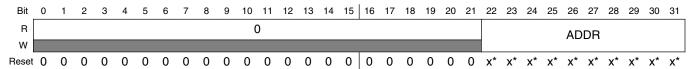

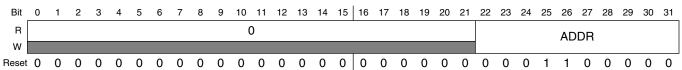

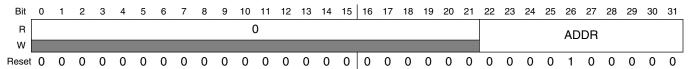

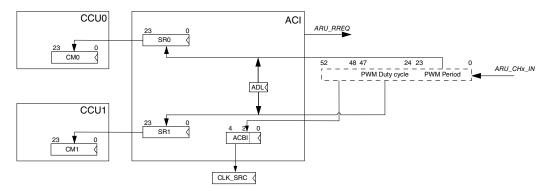

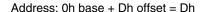

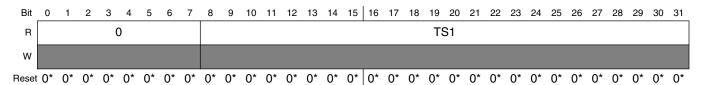

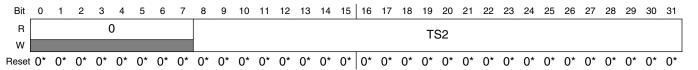

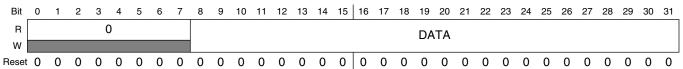

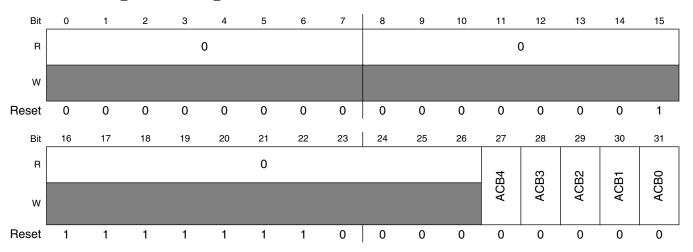

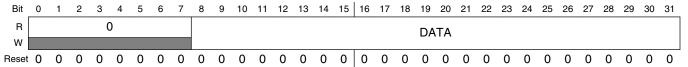

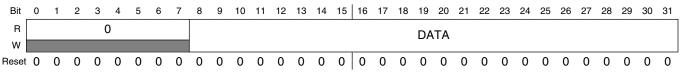

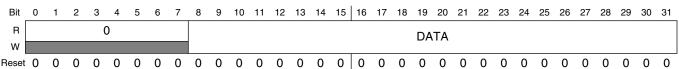

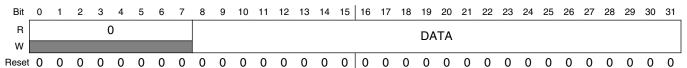

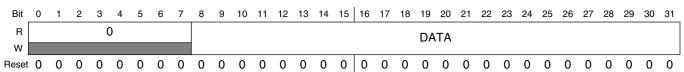

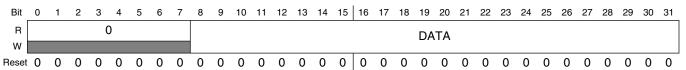

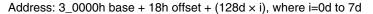

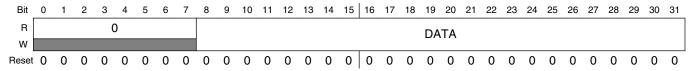

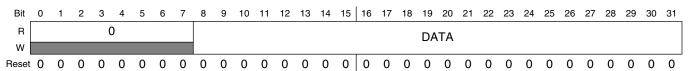

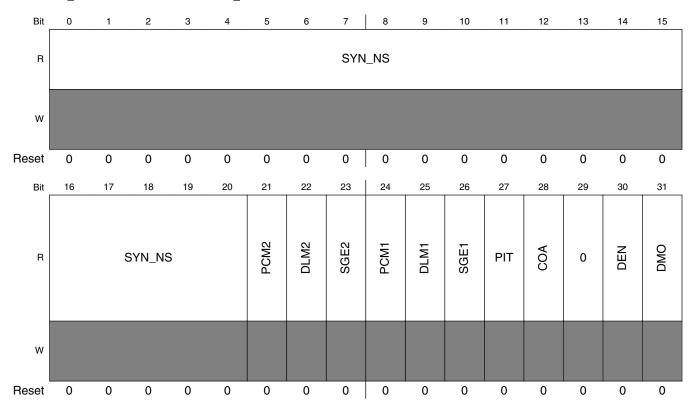

The routed data word size from the ARU is 53 bits. The data word, shown in the figure below, can be logically split into three parts.

- 1. ACB,

- 2. Data1, and

- 3. Data0.

The ACB part contains control bits to send control information from one submodule to another. The ARU Control Bits (ACB) can have a different meaning for different submodules.

The DATA0 and DATA1 parts typically hold data for the operation registers of the GTM. This data can be, for example, the duty cycle and period duration of a measured PWM input signal or the characteristic of an output PWM that is to be generated. Other possible content for Data0 and Data1 is two 24-bit values of the GTM time bases: TBU\_TS0, TBU\_TS1 and TBU\_TS2.

It is possible to route data from a source to a destination, and later, that destination can act as a source for another destination. Routes through the GTM are called 'data streams'. For a detailed description of the ARU submodule, please refer to Chapter 3.

Figure 2-2. ARU data word

#### 2.1.3 Broadcast Module (BRC) Brief Description

The Broadcast Module (BRC) can distribute data from one source submodule to more than one destination submodule, provided that the submodules are connected to the ARU.

#### 2.1.4 Parameter Storage Module (PSM) Brief Description

The Parameter Storage Module (PSM) consists of three subunits:

- 1. AEI-to-FIFO Data Interface (AFD),

- 2. FIFO-to-ARU Interface (F2A), and

- 3. the FIFO itself.

The PSM can serve as a data storage for incoming data characteristics or as parameter storage for outgoing data. The data is stored in a RAM that is logically located inside the FIFO subunit, but physically implemented and integrated outside of the GTM. Accordingly, the GTM provides the interface to the RAM at its module boundary.

#### 2.1.5 Timer Input Modules (TIMs) Brief Description

Signals are received into the GTM via the TIMs. The TIM s can filter the input signals and extrapolate additional information from them. Each channel is, for example, able to measure pulse high or low times and the period of a PWM signal in parallel and route the values to the ARU for further processing. The internal operation registers of the TIM submodule are 24 bits wide.

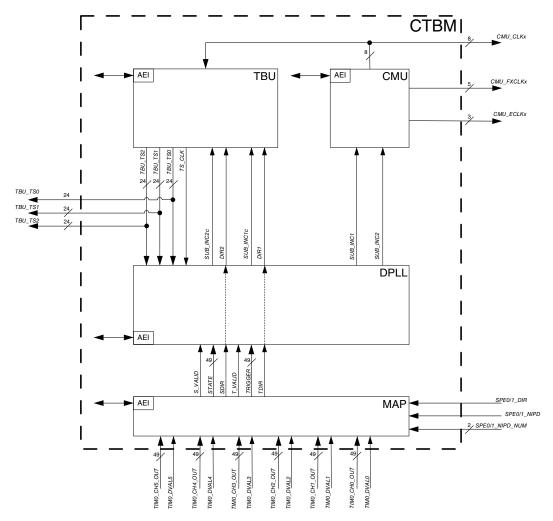

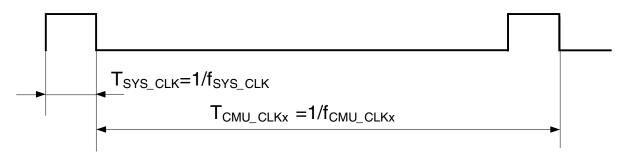

### 2.1.6 Clock Management Unit (CMU) Brief Description

The CMU provides up to 13 different clocks, and it can source up to three external clock pins, GTM\_ECLK[0:2]. It acts as a clock divider for the system clock. The counters implemented inside other submodules are typically driven from the CMU.

#### **NOTE**

The CMU clocks are implemented as enable signals for the counters while the whole system runs with the GTM global clock, SYS\_CLK.

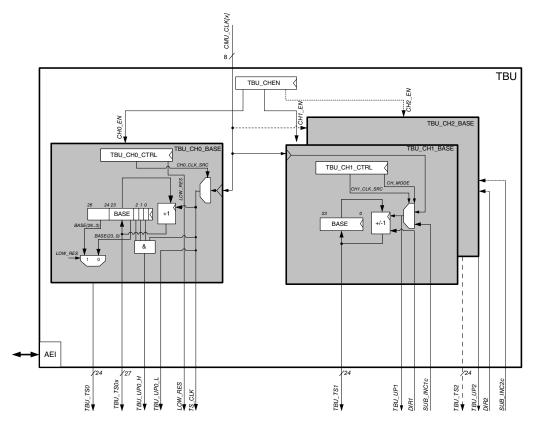

#### 2.1.7 Time Base Unit (TBU) Brief Description

The Time Base Unit (TBU) submodule provides three independent, common time bases for the GTM. In general, the number of time bases depends on the needs of the implemented device. If three time bases are implemented, two of the time bases can also be clocked with the sub\_inc1c and sub\_inc2c outputs from the Digital Phased Locked Loop (DPLL) submodule.

#### 2.1.8 Digital Phase Locked Loop (DPLL) Brief Description

The DPLL generates higher frequency clock signals, sub\_inc1, sub\_inc2, sub\_inc1c and sub\_inc2c, based on the frequencies of up to two input signals. Input signals are filtered in the TIM0 submodule and then transferred to the MAP submodule, where two of six input signals are routed to the DPLL for further processing.

### 2.1.9 Timer Output Module (TOM) Brief Description

The TOM submodules and the ATOM submodules generate signal outputs. Each TOM is able to generate a PWM signal at its output. With the use of an integrated shadow register, multiple TOM channels can be used to generate complex PWM outputs, with the

parameters being serviced by the CPU. It is possible to trigger TOM channels for a successor TOM submodule through a trigger line between  $TOM(x)_CH(15)$  and  $TOM(x+1)_CH(0)$ . However, to avoid long trigger paths, the trigger signal is saved in a register at the TOM submodule output, resulting in one SYS\_CLK cycle delay of the trigger signal.

In addition, each TOM submodule can integrate functions to drive one Brushless Direct Current (BLDC) engine. BLDC support is established with a TOM, a TIM, and the Sensor Pattern Evaluation (SPE) submodule.

# 2.1.10 ARU-connected Timer Output Module (ATOM) Brief Description

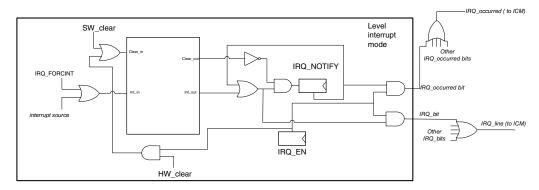

ATOM submodules and TOM submodules generate output signals.