## NXP Semiconductors Application Note

Document Number: AN0 Rev. 1, 11/2021

# MPC57xx - DCF (Device Configuration Format) records

By: Peter VIna and Petr Stancik

# 1. Introduction

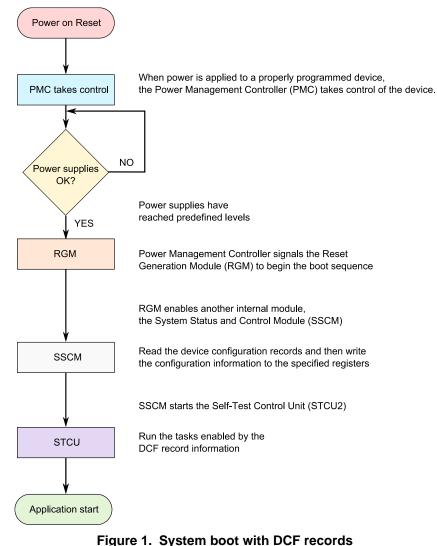

Before MPC57xx devices can be used by application they must pass a complex system reset sequence. During system reset sequence device initialization is done. Various self-test mechanism, configuration and trimming is executed during this time.

In order to prepare correct device operation, it is necessary to configure device during reset phase. For this purpose, MPC57xx implements DCF records located in special one-time programable flash memory (UTEST).

#### NOTE

Pay attention when programming DCF records as it can lead to permanent lock of the device.

#### Contents

| 1. | Intr | oduction                         | 1 |

|----|------|----------------------------------|---|

| 2. | DC   | F records                        | 2 |

|    | 2.1. | DCF records execution process    |   |

| 3. | DC   | F records general implementation |   |

|    | 3.1. | DCF records structure            |   |

|    | 3.2. | DCF clients                      |   |

|    | 3.3. | Safety features of DCF clients   |   |

|    | 3.4. | DCF records sequence             | 7 |

|    | 3.5. | Overwriting existing record      | 8 |

| 4. | DC   | F records fault reports          |   |

|    |      | FCCU monitoring                  |   |

|    | 4.2. | SSCM monitoring                  | 9 |

| 5  |      | F record calculator              |   |

# 2. DCF records

The MPC57xx devices implements one type of DCF records mechanism. However, the DCF records handling, special strategies and various use cases brings differences into the DCF records implementation. Aim of this document is to described usage, differences and implementation if DCF record mechanism.

## 2.1. DCF records execution process

System boot is a complex process requiring a considerable amount of initialization to take place before releasing reset. Before the device can be used in an application, the user application code, reset vectors for all of the CPUs and the DCF records must be properly programmed into their respective flash memories.

# **3. DCF records general implementation**

DCF records are stored in UTEST flash memory block. System Status and Control Module (SSCM) reads the DCF records from flash and writes the configuration information to the specified DCF clients.

For location of UTEST memory area refer to device specific reference manual or reference manual attachment.

DCF records are:

- a. Factory programmed (TEST) These DCF records are programmed in NXP factory to configure necessary device initialization. For example, offline BIST (build-in self-test), ADC calibration values, trimming oscillator frequencies, etc.... The TEST DCF Records are programmed into TEST flash during production and cannot be modified. TEST flash is not visible to the user.

- b. User programmed (UTEST) There DCF records are intended to be programmed by user and contain various configurations for device start conditions. For example, software watchdog (SWT) enable, oscillator enable, Build-in self-test configuration, etc..... Some UTEST DCF records are written by the factory and programmed during production testing. Others are written by the end user and programmed at the same time application code is programmed into the flash memory.

## 3.1. DCF records structure

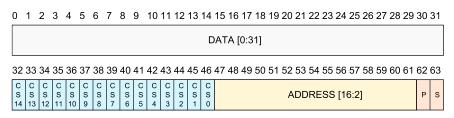

A DCF record is a contiguous double-word (64-bit) entry consisting of the following:

Figure 2. DCF record structure

DCF record consist of:

- Data 32 bits of data to be written to the DCF client

- Chip Select For each DCF record, one Chip Select bit is asserted

- Address Address of the DCF client within the selected module.

- Parity Parity Bit for the DCF Record.

- Stop Stop bit. Indicates the end of the list of DCF Records.

#### NOTE

Address decoding for DCF clients may not match the standard software address map decoding. Details of DCF Client addresses are defined in each module chapter.

MPC57xx - DCF (Device Configuration Format) records, Application Note, Rev. 1, 11/2021

## 3.2. DCF clients

DCF clients are 32-bit wide hardware registers inside a module, that receive and store the data from a DCF record. This stored data is used to initialize registers and to configure features. DCF Clients have a default value before any DCF Records are written, and may have special writing constraints, such as, 'Write Once' or allowing bits to be written from '1' to '0' only or vice versa.

DCF clients may be designated 'TEST DCF record only', which means that only DCF Records stored in TEST flash can write to the DCF Client. The DCF Records select the 'target' DCF client by a 30-bit field in the DCF Record consisting of a 15-bit 'Chip Select' field and a 15-bit Address field. Each module that includes DCF clients is assigned a Chip Select during chip definition. The address field is only relevant to the address decoding within that module and may not necessarily relate to the address of a register visible to software.

## 3.3. Safety features of DCF clients

Implementation of safety clients differs from device to device. Some MPC57xx implements safety features by HW and some need to be applied by user. Following table shows the implementation of DCF safety features:

| Implemented in Hardware | Implemented in Software |

|-------------------------|-------------------------|

| MPC5777M                | MPC5744P                |

| MPC5777C                | MPC5746R                |

| MPC574xG                |                         |

| MPC5746C                |                         |

|                         | MPC577xK                |

|                         | S32R274                 |

Table 1. Safety features implementation

#### 3.3.1. Parity

If a DCF client implements parity checking, then it will receive a parity bit additionally to its data in the DCF record. During device operation, it will continuously monitor whether the data it stores matches the parity and report errors to the SSCM. Parity is calculated also for triple voting and spread address.

#### 3.3.2. Triple voting

DCF clients that use the triple voting have three copies of the register. The SSCM will write to all three registers in a single write cycle. During device operation, the DCF client continuously monitors whether all three copies match and reports errors to the SSCM. The device will use the majority result, so single errors will not affect device operation.

| Address in UTEST                                      | Register Value | C               | Chip select   | Register Address                        | Parity | Stop |  |  |  |

|-------------------------------------------------------|----------------|-----------------|---------------|-----------------------------------------|--------|------|--|--|--|

| 0x00400308                                            | 0x00028500     | 0b00            | 0000010000000 | 0b00000000001000                        | 0      | 0    |  |  |  |

| Triple Voting on Register Value - Inverted record     |                |                 |               |                                         |        |      |  |  |  |

| 0x00400310 0x0057AFF                                  |                |                 | 0000010000000 | 060000000000000000000000000000000000000 | 0      | 0    |  |  |  |

| Triple Voting on Register Value - Rotate right record |                |                 |               |                                         |        |      |  |  |  |

| 0x00400318                                            | 0x00014280     | 060000001000000 |               | 060000000000000000000000000000000000000 | 0      | 0    |  |  |  |

| Figure 3. Triple voting                               |                |                 |               |                                         |        |      |  |  |  |

| DCF records                                           |                |                 |               |                                         |        |      |  |  |  |

| 0x00400308 0x0002850001000020                         |                |                 |               |                                         |        |      |  |  |  |

| 0x00400310                                            |                | 00310           | 0x00057AFF01  | 000020                                  |        |      |  |  |  |

| 0x00400318 0x0001428001000020                         |                |                 |               |                                         |        |      |  |  |  |

|                                                       | Figure 4       | Triple vo       | ting DCF reco | rd example                              |        |      |  |  |  |

Figure 4. Triple voting DCF record example

#### 3.3.3. Spread address

DCF clients that use spread triple voting have three copies of the register which are individually addressed and where the data is stored in three different formats. The SSCM will fetch these records independently. During device operation, the DCF client continuously monitors whether all three copies can be resolved from the stored format to the value and reports errors to the SSCM. The device will use the majority result, so single errors will not affect device operation. This parameter is only available on safety critical DCF clients.

DCF record with spread address implements 3 writes to address adjusted from base address. You can see example on the figure below.

| Address in UTEST                | Register Value        | Chip Select              | Register Address                        | Pari       | ty Stop |

|---------------------------------|-----------------------|--------------------------|-----------------------------------------|------------|---------|

|                                 |                       |                          | Spread address = base a                 | ddress + ( | 0x4     |

| 0x00400308                      | 0x00028500            | 060000001000000          | 060000000000000000000000000000000000000 | 0          | 0       |

|                                 |                       |                          | Spread address = base a                 | ddress + ( | 0x8     |

| 0x00400310                      | 0x00028500            | 0b0000001000000          | 0b00000000001010                        | 0          | 0       |

| Triple Voting on Register Value | - Rotate right record |                          | Spread address = base a                 | ddress + ( | Ox10    |

| 0x00400318                      | 0x00028500            | 060000001000000          | 0b00000000001100                        | 0          | 0       |

|                                 |                       | Figure 5. Spread address | S                                       |            |         |

MPC57xx - DCF (Device Configuration Format) records, Application Note, Rev. 1, 11/2021

| DCF records          |                         |

|----------------------|-------------------------|

| 0x00400308           | 0x0002850001000024      |

| 0x00400310           | 0x0002850001000028      |

| 0x00400318           | 0x0002850001000030      |

| Figure 6. Spread add | ress DCF record example |

# 3.3.4. Spread address + triple voting + parity

Safety critical DCF records combine multiple safety features. Below is the example of spread address + triple voting + parity.

| Address in UTEST                                  | Register Value                 | Chip Select     | Register Address         | Parity                   | Stop |  |  |

|---------------------------------------------------|--------------------------------|-----------------|--------------------------|--------------------------|------|--|--|

|                                                   |                                |                 | Spread address = base ac | ldress + 0x4             |      |  |  |

| 0x00400308                                        | 0x00028500                     | 060000001000000 | 060000000000000001001    | 0                        | 0    |  |  |

| Triple Voting on Registe                          | er Value - Inverted record     |                 | Spread address = base ac | ldress + 0x8             |      |  |  |

| 0x00400310                                        | 0x00057AFF                     | 0b0000001000000 | 0b00000000001010         | 1                        | 0    |  |  |

| Triple Voting on Registe                          | er Value - Rotate right record |                 | Spread address = base ac | ss = base address + 0x10 |      |  |  |

| 0x00400318                                        | 0x00014280                     | 0b0000001000000 | 0b00000000001100         | 0                        | 0    |  |  |

| Figure 7. Spread address + triple voting + parity |                                |                 |                          |                          |      |  |  |

| DCF records                                       |                                |                 |                          |                          |      |  |  |

|                                                   | 0x00400308                     | 8 0x00028500010 | 000024                   |                          |      |  |  |

|                                                   | 0x00400310                     | 0 0x00057AFF01  | 00002A                   |                          |      |  |  |

|                                                   | 0x00400318                     | 8 0x00014280010 | 000030                   |                          |      |  |  |

Figure 8. Spread address + triple voting + parity DCF record example

#### 3.3.5. Second write check

This feature is used by DCF clients which receive their records twice - e.g. once before and once after BIST for clients which retain their value during self-test. They will monitor whether the second write matches the first and report deviations to the SSCM.

#### 3.3.6. Write Once

A DCF client using the Write Once rule can only be written with a single DCF record. Records appended later in the list will be ignored and not change the value of the client.

#### 3.3.7. Write 0 only

A bit in a DCF client can only be written from a 1 to a 0. So, if an earlier DCF record has set a bit to 0, then an attempt by a later record to set this bit to a 1 will be ignored.

#### 3.3.8. Write 1 only

A bit in a DCF client can only be written from a 0 to a 1. So, if an earlier DCF record has set a bit to 1, then an attempt by a later record to set this bit to a 0 will be ignored.

#### 3.4. DCF records sequence

An individual DCF record consists of information to locate the corresponding DCF client internal to the device (control word) and the data to be written to that client (data word).

DCF records appear as contiguous series of entries programmed at a specific address within flash memory (UTEST flash memory).

The following structure must be present:

| Record type  | ADDR offset | DATA                                |  |      |   |                 |  |

|--------------|-------------|-------------------------------------|--|------|---|-----------------|--|

| Start record | 0x00        | 0x05AA_55AF                         |  |      |   |                 |  |

|              | 0x04        | 0x0000_0000 STOP = 0                |  |      |   |                 |  |

| DATA records | 0x8         | WDATA[31:0]                         |  |      |   |                 |  |

|              | 0xC         | CS[14:0] ADDR[16:2] PARITY STOP = 0 |  |      |   | $\Gamma OP = 0$ |  |

|              | 0x10        | WDATA[31:0]                         |  |      |   |                 |  |

|              | 0x14        | CS[14:0] ADDR[16:2] PARITY          |  |      | S | TOP = 0         |  |

|              |             |                                     |  | •••• |   |                 |  |

| STOP record  | 8(n-1)+0x0  | 0xFFFF_FFFF                         |  |      |   |                 |  |

|              | 8(n-1)+0x4  | 0xFFFF_FFFF STOP = 1                |  |      |   |                 |  |

Table 2. DCF records sequence

#### 3.4.1. Start record

The first DCF record must be a start record. This record must be placed at DCF Start Record position of a DCF area in UTEST flash memory to indicate to the device that the following records must be processed. Always refer to reference manual UTEST Memory Map chapter for location of DCF start record.

#### 3.4.2. Data records

DCF records containing configuration data must immediately follow the start record with no blank records between-an unprogrammed record is interpreted as a stop record and no DCF records following

MPC57xx - DCF (Device Configuration Format) records, Application Note, Rev. 1, 11/2021

that record are processed. This allows one to program the records in several sessions, each time appending new records at the end of the list.

#### 3.4.3. STOP record

The end of the configuration records are indicated by the presence of a stop record indicated by the stop bit being set. Normally, the stop bit is never set in a valid UTEST DCF record programmed during production, since this would prevent appending additional UTEST records. The flash memory location following the last UTEST DCF record programmed at the factory is an unprogrammed location.

Therefore, that location's contents will be 0xFFFF\_FFF. Thus, the stop bit location in this unprogrammed flash memory location will be a logic 1, signifying that this is the last DCF record and it is not to be acted upon.

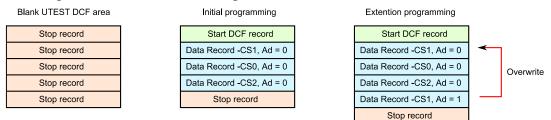

#### 3.5. Overwriting existing record

As the UTEST flash memory is OTP (one time programable) user cannot simply rewrite already programmed data. For this purpose, device implements overwrite function.

It is possible for more than one DCF Record to write to the same DCF client. In this case the later record usually overrides a DCF client value set by a previous record. However, not all DCF clients allow overwrites; this depends on the DCF client implementation.

Figure 9. Appending DCF records

# 4. DCF records fault reports

Correct implementation of DCF records is monitored by FCCU and SSCM peripherals.

## 4.1. FCCU monitoring

If SSCM detects the invalid DCF record programmed in UTEST flash memory it will inform FCCU about this event. FCCU will rise non-critical fault flag in FCCU[NCF\_Sx] register. Refer to reference manual of your device for exact DCF record non-critical fault implementation.

## 4.2. SSCM monitoring

When SSCM detects invalid DCF records it will set CER and flags in CERS SSCM[SSCM\_STATUS] register.

#### NOTE

Not all MPC57xx devices implements CERS reporting bit in SSCM module.

#### 4.2.1. CER - Configuration Error

This bit indicates that the SSCM has detected a configuration error during reset while loading initial device configuration. See the reference manual chip-specific SSCM information for details about sources of the error. If a non-permanent error is detected, this bit can be cleared by writing a 1.

## 4.2.2. CERS - Configuration Error for Safe DCF Clients

This field indicates that the SSCM has detected a configuration error during reset while loading the Safe DCF Clients (Triple Voting Enabled). If a non-permanent error is detected, this bit can be cleared by writing a 1.

# 5. DCF record calculator

DCF record calculators have been developed to ease the work with DCF records. The calculators are attached to this document.

MPC5746R: https://community.nxp.com/docs/DOC-334130 MPC5777C: https://community.nxp.com/docs/DOC-335523 MPC5744P: https://community.nxp.com/docs/DOC-341538 MPC5746C: https://community.nxp.com/docs/DOC-341539 MPC5748G: https://community.nxp.com/docs/DOC-341540 MPC5775K: https://community.nxp.com/docs/DOC-341541 MPC5777M: https://community.nxp.com/docs/DOC-341542 S32R274: https://community.nxp.com/docs/DOC-341633

#### How to Reach Us:

Home Page: nxp.com

Web Support: nxp.com/support Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

Registered trademarks: NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE,

JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners.

ARM, the ARM logo, and Cortex are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. mbed is a trademark of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved.

IEEE nnn, nnn, and nnn are registered trademarks of the Institute of Electrical and Electronics Engineers, Inc. (IEEE). This product is not endorsed or approved by the IEEE. Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. (Add contract language here, as necessary.)

© 2016 NXP B.V.

Document Number: AN0 Rev. 1 11/2021

PRELIMINARY