# Generating interrupt in NON-security world

For the CM33 of LPC55S6x family, the trust zone module is integrated, the memory space and peripherals are classified as security and non-security space. In order to generate interrupt in non-security mode, the NVIC module especially the NVIC\_ITNSx register must be initialized in security mode so that interrupt module can generate interrupt in non-security mode.

The example demos that MRTO module generates interrupt in non-security mode, the NVIC module is initialized at security mode, MRTO is initialized at non-security mode.

The project is based on MCUXpresso IDE ver11.1 tools, LPC55S69-EVK board and SDK\_2.x\_LPCXpresso55S69 SDK package version 2.7.1.

#### 1) security and non-security mode introduction

The SDK package for LPC55S6x has an example:

The lpcxpresso55s69\_hello\_world\_s is the code that the LPC55S69 runs in the security mode.

The lpcxpresso55s69\_hello\_world\_ns is the code that the lpc55S69 runs in non-security mode.

Users can compile the two project, then download ONLY the lpcxpresso55s69\_hello\_world\_s project, the lpcxpresso55s69\_hello\_world\_ns is loaded to flash automatically by the lpcxpresso55s69\_hello\_world\_s project.

The lpcxpresso55s69\_hello\_world\_s is loaded into PROGRAM\_FLASH (rx) : ORIGIN = 0x10000000, so the LPC55S69 runs in security mode after Reset.

### 2) NVIC-ITNSx registers introduction

For the CM33 core, there is additional NVIC-ITNSx registers,

Reset value Description Address Name Type Required privilege 0xE000E100-0xE000E13C NVIC ISER0-Privileged 4.4.2 Interrupt Set Enable Registers 0x00000000 on page 4-305 NVIC ISER15 NVIC ICER0-Privileged 4.4.3 Interrupt Clear Enable 0XE000E180- 0XE000E1BC 0x00000000 NVIC\_ICER15 Registers on page 4-306 NVIC ISPR0-4.4.4 Interrupt Set Pending 0XE000E200- 0xE000E23C RW Privileged 0x00000000 NVIC ISPR15 Registers on page 4-307 NVIC ICPR0-Privileged 4.4.5 Interrupt Clear Pending 0XE000E280- 0XE000E2BC 0x00000000 NVIC ICPR15 Registers on page 4-307 NVIC IABR0-RW 4.4.6 Interrupt Active Bit Registers 0xE000E300-0xE000E33C Privileged 0×00000000 NVIC IABR15 on page 4-308 NVIC ITNS0-4.4.7 Interrupt Target Non-secure 0×E000E380-0×E000E3BC RWV Privileged ахаааааааа NVIC\_ITNS15 Registers on page 4-308. NVIC IPR0-4.4.8 Interrupt Priority Registers 0×F000F400-0×F000F5DC Privileged 0×00000000 NVIC IPR119 on page 4-309 0xE000EF00 STIR WO Configurablew 0x00000000 4.4.9 Software Trigger Interrupt

Table 4-35 NVIC registers summary

Table 4-42 NVIC\_ITNSn bit assignments

Register on page 4-310

| Bits   | Name | Function                                                                                                                                                     |

|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:0] | ITNS | Interrupt Targets Non-secure bits. For ITNS[m] in NVIC_ITNSn, this field indicates and allows modification of the target Security state for interrupt 32n+m. |

|        |      | <ul> <li>The interrupt targets Secure state.</li> <li>The interrupt targets Non-secure state.</li> </ul>                                                     |

The CM33 core has two interrupt vector table located at different memory space, one is for security mode, another is for non-security mode. In other words, each interrupt source has two interrupt vector, one is located in security interrupt vector table, another is located at non-security interrupt vector table.

If user wants to generate interrupt in non-security mode, user has to set the interrupt source bit in NVIC\_ITNSx register in the secure project. In this way, the security project can control whether the interrupt source is allowed or not allowed in non-security project.

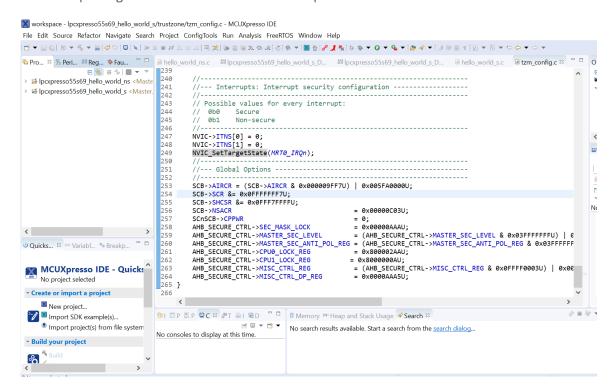

Generally, the code to initialize the NVIC\_ITNSx register is located in the tzm\_config.c to initialize the trust zone in the security project.

```

NVIC->ITNS[0] = 0;

NVIC->ITNS[1] = 0;

NVIC SetTargetState(MRT0 IRQn);

```

## 3) MRTO and NVIC code

3.1 The code required to be located at the lpcxpresso55s69\_hello\_world\_s

project:

The NVIC module initialization must be located at the security side so

that the security side can determine what resource is open to non-security side. User can use NVIC module or NVIC\_NS module, either of them is okay, because security can access non-security peripherals.

```

void MRT0_InterruptInit(void)

NVIC \rightarrow IPR[9] = 0 \times 00;

NVIC->ISER[0]|=1<<9;

NVIC->ICPR[0]|=1<<9;

}

0r

void MRT0 NS InterruptInit(void)

NVIC NS->IPR[9]=0\times00;

NVIC NS->ISER[0]|=1<<9;

NVIC_NS->ICPR[0]|=1<<9;

}

The NVIC->ITNSx register must be initialized in security side.

NVIC \rightarrow ITNS[0] = 0;

NVIC \rightarrow ITNS[1] = 0;

NVIC SetTargetState(MRT0 IRQn);

3.2 The code required to be located at the lpcxpresso55s69 hello world ns

project:

void Init_MRTO_NS(void)

SYSCON_NS->AHBCLKCTRL.AHBCLKCTRL1 | =1<<0;

//set up PIT0

MRT0 NS->CHANNEL[0].INTVAL=12000000;

//repeated interrupt mode

MRT0 NS->CHANNEL[0].CTRL=0x00;

//enable MRT channel0

MRT0 NS->CHANNEL[0].CTRL=1<<0;}</pre>

void MRT0 IRQHandler(void)

{

//toggle LED

//clear flag

MRTO_NS->CHANNEL[0].STAT=1<<0;</pre>

GPIO_NS->NOT[1]|=1<<7;</pre>

//LEDG PIO1_7 as GPIO output mode

void Init PIO1 7 NS(void)

```

```

{

//enable gated GPIOP1 clock

SYSCON_NS->AHBCLKCTRL.AHBCLKCTRL0|=1<<15;

//set the mux

//set GPIO direction reg

GPIO_NS->DIR[1]|=1<<7;

//toggle the PIO1_4

GPIO_NS->NOT[1]=1<<7;

__asm("nop");

}</pre>

```

### 4. conclusion

In order to generate interrupt in non-security side, the NVIC module must be initialized in security side, which includes the initialization of the registers: ISER,ICPR,IPR and ITNS of NVIC. The module which generate interrupt can be initialized in the non-security side.