# Image: Non LPC-Link2 Debug Probe Firmware Programming Rev. 1.8.2 – 19 June, 2017

**User Guide**

19 June, 2017

Copyright © 2015 NXP Semiconductors

All rights reserved.

| 1. Revision History                                                | . 1 |

|--------------------------------------------------------------------|-----|

| 1.1. v1.8.2                                                        |     |

| 1.2. v1.5.2                                                        | . 1 |

| 1.3. v1.5                                                          | . 1 |

| 2. Introduction                                                    |     |

| 3. Quick Start                                                     |     |

| 4. Debug Firmware Variants and Drivers                             | . 4 |

| 4.1. Firmware Variants                                             |     |

| 4.1.1. CMSIS-DAP                                                   | . 4 |

| 4.1.2. Segger J-Link                                               | . 4 |

| 4.2. Drivers                                                       |     |

| 5. Programming (LPC-Link2)                                         |     |

| 6. Programming (LPCXpressoV2/V3)                                   | . 7 |

| 7. Advanced                                                        | . 9 |

| 7.1. Script steps                                                  | . 9 |

| 7.2. Script Options                                                |     |

| 8. Trouble Shooting                                                |     |

| 8.1. My device fails to DFU boot                                   |     |

| 8.2. My device DFU boots but then just prints ''                   | 11  |

| 8.3. My newly programmed debug probe is not recognised by the Host | 11  |

| 9. Legal Information                                               |     |

| 9.1. Definitions                                                   | 12  |

| 9.2. Disclaimers                                                   | 12  |

| 9.3. Trademarks                                                    | 13  |

# **1. Revision History**

## 1.1 v1.8.2

• Minor additions to reference compatibility with MCUXpresso IDE

## 1.2 v1.5.2

• Minor additions to reflect product and script improvements.

## 1.3 v1.5

• First release of this document detailing the programming of CMSIS-DAP and J-Link firmware added to LPCScrypt version 1.5 release.

# **2. Introduction**

LPCScrypt is a fast flash and security programming tool for the LPC18xx and LPC43xx series of microcontrollers. It can be used on Windows, Linux and Mac OSX.

This document describes the use of scripts provide within LPCScrypt to simplify the programming of debug probe firmware into the standalone LPC-Link2 debug probe, as well as the variant built into the LPCXpresso V2/V3 boards.

For more details of these boards/probes, please visit:

http://www.nxp.com/pages/:LPCXPRESSO-BOARDS

For more details of using LPCScrypt, please read the LPCScrypt User Guide supplied within the product.

#### Important Note

You may need to install additional Windows drivers in order to make use of your debug probe.

For CMSIS-DAP, the Windows driver package if not already installed – for example by LPCXpresso IDE – can be found at:

http://www.lpcware.com/content/nxpfile/lpcxpresso-link2-usb-driver-package

In addition, there is a small possibility that an incompatible driver may be selected. For more details of this issue and fix, please see the FAQ below:

https://community.nxp.com/message/630660

For J-Link, please check the Segger website for more information.

# 3. Quick Start

LPCScrypt is supplied with scripts to enable the programming of CMSIS-DAP and J-Link firmware images into LPC-Link2 and LPCXpresso V2/V3 boards.

To make use of this functionality, configure the selected board to DFU Boot, then connect to the host computer via USB.

To install CMSIS-DAP debug firmware, open a command shell and call the program\_CMSIS script:

```

<LPCScrypt Install Dir>\scripts\program_CMSIS

```

To install J-Link debug firmware, open a command shell and call the program\_JLINK script:

<LPCScrypt Install Dir>\scripts\program\_JLINK

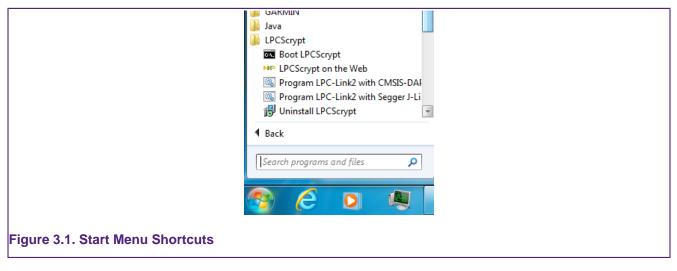

For Windows users, shortcuts to these scripts are available from the LPCScrypt entry on the Start menu.

#### Note

File paths in this document use Windows directory separators, on Linux or Mac OSX these must be replaced with '/'

These scripts will boot the LPCScrypt firmware on the selected board and then choose the appropriate firmware image and program it into flash.

Once completed, follow the onscreen instructions to make use of the programmed debug probe.

For more information, please read the following sections for a detailed explanation of this procedure.

#### Note

The scripts offer the option to repeat the programming sequence to enable multiple debug probes to be programmed in sequence.

# 4. Debug Firmware Variants and Drivers

### 4.1 Firmware Variants

Separate firmware images are available for each LPC-Link2 variant for the following debug probe protocol implementations:

#### 4.1.1 CMSIS-DAP

The CMSIS-DAP debug probe images allow debugging from any compatible toolchain, including IAR EWARM, Keil MDK, as well as NXP's LPCXpresso and MCUXpresso IDE.

As well as providing debug probe functionality, the default CMSIS-DAP image also provides:

- Support for SWO Trace capture from the LPCXpresso IDE and MCUXpresso IDE

- Support for Power Measurement from the LPCXpresso IDE and MCUXpresso IDE

- UART bridge connected to the target processor (LPCXpresso V2/V3 boards only),

- LPCSIO bridge that provides communication to I2C and SPI slave devices (LPCXpresso V3 boards only).

For more information please see:

http://www.lpcware.com/content/project/lpc-usb-serial-io-library

#### Note

If these additional features are not required, a version supporting debug features only is also provided. For information on script options, see Section 7.2.

#### Note

MCUXpresso IDE and LPCXpresso IDE do not require a CMSIS-DAP image to be programmed into the debug probe flash, as it will normally be downloaded directly into the probe after power up. However it can use a pre-programmed version if one is present.

## 4.1.2 Segger J-Link

J-Link is a trademark of Segger Embedded Software Solutions. More information about J-Link can be found at:

http://www.segger.com

#### **Important Note**

Please ensure that you read Segger's licensing terms for these debug probe firmware images before using them.

For information on the use of J-Link with LPC-Link2 and LPCXpresso V2/V3, please see:

https://www.segger.com/lpc-link-2.html

https://www.segger.com/jlink-lpcxpresso-ob.html

The J-Link debug probe images allow the LPC-Link2/LPCXpressoV2/V3 board to operate as a J-Link debug probe that works with tool chains that support the J-Link protocol such

as MCUXpresso IDE, IAR EWARM, Keil MDK, Rowley CrossWorks, Atollic TrueSTUDIO, OpenOCD compatible tools as well as GDB-based tool chains such as emIDE.

J-Link can also be used with LPCXpresso IDE. For details see:

https://www.segger.com/nxp-lpcxpresso.html

## 4.2 Drivers

You may need to install additional Windows drivers in order to make use of your debug probe.

For CMSIS-DAP, the Windows driver package if not already installed – for example by LPCXpresso IDE – can be found at:

http://www.lpcware.com/content/nxpfile/lpcxpresso-link2-usb-driver-package

For J-Link, please check the Segger website for more information.

# 5. Programming (LPC-Link2)

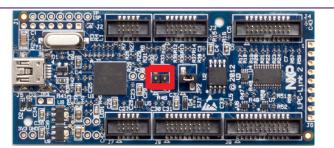

To program a standalone LPC-Link2, first of all ensure that jumper JP1 is NOT fitted so that the probe will be DFU bootable at power on.

#### Figure 5.1. LPCLink2 DFU Boot

Then connect the board to your host computer over the debug link USB connector and in a command shell run either:

<LPCScrypt Install Dir>\scripts\program\_CMSIS

or

```

<LPCScrypt Install Dir>\scripts\program_JLINK

```

Note: For Windows users, shortcuts to these scripts are available from the LPCScrypt entry on the Start menu.

The output will be similar to that below:

```

LPCScrypt - CMSIS-DAP firmware programming script v1.5.2 June 2015.

.

Connect an LPC-Link2 or LPCXpresso V2/V3 Board via USB then press Space.

Booting LPCScrypt

.

CMSIS-DAP firmware successfully programmed to flash.

.

LPC-Link2 programmed with LPC432x_CMSIS_DAP_V5_112.bin.hdr

- To use: make link JP1 (nearest USB) and reboot the board

.

Connect next board then press Space (or <return> to Quit)

```

Note: The script will automatically detect the debug probe type and select the appropriate firmware version.

Once programming is complete, disconnect the board from the host, fit JP1, then reconnect the board to the host computer. You should see the debug probe enumerate on the host's USB system.

# 6. Programming (LPCXpressoV2/V3)

To program an LPCXpressoV2/V3 board, first of all ensure that the DFULink jumper **IS** fitted. Normally DFULink can be found between the two USB ports on the left hand side of the board, but please check the information for your actual board to confirm.

- for the LPCXpresso11U68, it is JP3

- for the LPCXpresso54102, it is JP5

- for the LPCXpresso4337, it is JP6

#### Figure 6.1. LPCXpresso V2 DFU Boot

Then connect the board to your host computer over the debug link USB connector and in a command shell run either:

<LPCScrypt Install Dir>\scripts\program\_CMSIS

or

<LPCScrypt Install Dir>\scripts\program\_JLINK

Note: For Windows users, shortcuts to these scripts are available from the LPCScrypt entry on the Start menu.

The output will be similar to that below:

```

LPCScrypt - CMSIS-DAP firmware programming script v1.5.2 June 2015.

.

Connect an LPC-Link2 or LPCXpresso V2/V3 Board via USB then press Space.

Booting LPCScrypt

.

CMSIS-DAP firmware successfully programmed to flash.

.

LPCXpresso V2/V3 programmed with LPC432x_IAP_CMSIS_DAP_V5_112.bin

- To use: remove DFU link and reboot the board

.

Connect next board then press Space (or <return> to Quit)

```

Note: The script will automatically detect the debug probe type and select the appropriate firmware version.

LPC-Link2 Debug Probe Firmware Programming -User Guide Once programming is complete, disconnect the board from the host, remove the DFULink jumper, then reconnect the board to the host computer. You should see the probe enumerate on the host's USB system.

# 7. Advanced

LPC-Link2 is a dual purpose debug probe and test board. The board contains a single LPC4370 MCU and 1MB of SPIFI flash memory. Where as, LPCXpresso V2/V3 boards, contain a dedicated 43xx debug MCU (connected via the lower left USB port) with internal Flash memory in addition to the target MCU. Since the debug firmware is stored in the flash memory of the debug MCU, different images are required for these board.

# 7.1 Script steps

This section describes the operations carried out by the  $\tt program\_CMSIS$  and  $\tt program\_JLINK$  scripts.

The scripts perform the following steps:

- 1. Boots the debug probe with the LPCScrypt firmware.

- this is performed by calling the script LPCScrypt install dir>\scripts

- if this operation succeeds, then the script will continue, otherwise, the script will terminate with an error

- 2. Tests for successful communication between the host and LPCScrypt

- <LPCScrypt install dir>\bin\LPCScrypt print 0x1234 is repeatedly called until sucessful communication is achieved.

- a '.' is printed for each attempt

- 3. Identify the debug probe MCU.

- <LPCScrypt install dir>\bin\LPCScrypt querypart is called to return the part name

- based on the result, the flash type SPIFI or BANKA is selected

- 4. The appropriate image file is located in the LPCScrypt firmware directory based on the identified debug probe MCU.

- if this cannot be found an error will be generated and the script will terminate

- 5. LPCScrypt is called to program the image onto the chosen board.

- <LPCScrypt install dir>\bin\LPCScrypt program <path to image> <Flash Device>

- if the program operation should fail, an error will be generated and the script will terminate

- 6. If no error has been generated, the steps will be repeated for the next device to be connected.

#### Note:

- for LPC-Link2, the firmware is stored in the SPIFI flash memory at 0x14000000, so the board must be configured to boot from SPIFI memory for the CMSIS-DAP or J-Link firmware to be used after programming (by connecting the jumper JP1)

- for LPCXpresso V2/V3 boards, the firmware is stored in flash BankA at 0x1A000000, so the board must be re-configured to boot from BankA for the CMSIS-DAP or J-Link firmware to be used after programming (by removing DFU Link jumper)

# 7.2 Script Options

The program\_CMSIS script can be called with the argument 'NB'. If this argument is used, the 'Non Bridged' variant of CMSIS-DAP is programmed. This version of firmware provides debug features only – removing the bridged channels such as trace, power measurement and VCOM. The use of this firmware is only recommended if USB bandwidth issues are encountered on your host.

The program\_CMSIS script can also be called with an argument consisting of a path to a binary file. This option is intended for use when a number of boards require programming with a particular image. This feature can be used with any LPC18xx/LPC43xx MCU but note that if internal flash is available, this will be programmed in preference to SPIFI.

# 8. Trouble Shooting

Some potential issues and their solutions are listed below:

## 8.1 My device fails to DFU boot

For the DFU boot to work, your device should appear as a 'NXP Semiconductors LPC' device when connected to the host.

The following FAQ describes this in more detail:

https://community.nxp.com/message/630577

#### Note

Due to restrictions with the dfu-util utility used by  $boot_lpcscrypt$ , only one unbooted MCU may be connected. Additionally the supplied script expects a single LPC USB serial (VCOM) port to be connected to the host.

## 8.2 My device DFU boots but then just prints '.....'

```

Booting LPCScrypt target with "LPCScrypt_77.bin.hdr"

LPCScrypt target booted

```

This indicates that the host is unable to establish successful communication with the LPCScrypt Firmware.

- If using Windows, ensure that you have installed the VCOM driver. Refer to the LPCScryptGuide section 'Installing host drivers' for details.

- If using a Linux host, ensure you have installed the correct drivers. Refer to the LPCScryptGuide section 'Installing host drivers' for details.

- Check that you only have a single VCOM device connected to the host via USB.

- If you are using a Virtual Machine (VM), check that the VM has routed the newly enumerated VCOM device to the OS in use.

# 8.3 My newly programmed debug probe is not recognised by the Host

You may need to install additional Windows drivers in order to make use of your debug probe.

For CMSIS-DAP, the Windows driver package if not already installed – for example by LPCXpresso IDE – can be found at:

http://www.lpcware.com/content/nxpfile/lpcxpresso-link2-usb-driver-package

In addition, there is a small possibility that an incompatable driver may be selected. For more details of this issue and fix, please see the FAQ below:

https://community.nxp.com/message/630660

For J-Link, please check the Segger website for more information.

# 9. Legal Information

## 9.1 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

## 9.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including – without limitation – lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Suitability for use** — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or

products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Evaluation products** — This product is provided on an **"as is"** and **"with all faults"** basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non- infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer.

In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages.

Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

## 9.3 Trademarks

**Notice:** All referenced brands, product names, service names and trademarks are property of their respective owners.