Author: Dawei You

Customer may meet Kinetis chips lock issue during software debug, prototype production, mass-production phase. This document will try to list the potential root causes and how to figure out.

- 1. Kinetis locked behaviors

- 1.1 During IDE debug phase, it couldn't find the device and debug processing halted.

- 1.2 Pop-up device is secured panel:

| Confirm |                                      |

|---------|--------------------------------------|

| ?       | Device is secure. Erase to unsecure? |

|         | Yes <u>N</u> o                       |

## 1.3 No connection for J-Flash tool

|                                  | Registers                        |                                  | t system has unexpected ·                      |              |

|----------------------------------|----------------------------------|----------------------------------|------------------------------------------------|--------------|

| -<br>R3 = 0000B800<br>= 20000133 | R2 = 00008000,<br>= 000000FF, R7 | R1 = 08000000,<br>= 0000B7FC, R6 | = FFFFFFFE<br>R0 = 0000B800,<br>= 20000000, R5 |              |

|                                  |                                  |                                  |                                                | Failed to re |

|                                  |                                  |                                  | ead back target memory                         | Failed to re |

1.4 Even connected, it will report "RAM check failed" error and no operation available

1.5 Using J-Link commander tool, could not find MCU core

```

C:\Windows\system32\cmd.exe - JLink.exe -device MKV58F1M0xx22 -if swd

Selecting JTAG as current target interface.

Setting target interface speed to 1MHz. Use "Speed" to change.

Sleep(100)

Info: TotalIRLen = ?, IRPrint = 0x..00000000000000000000000

Reset delay: 0 ms

Reset type UNKNOWN: ???

Info: TotalIRLen = ?, IRPrint = 0x..000000000000000000000000

Script processing completed.

C:\Program Files\SEGGER\JLink_U502f>JLink.exe -device MKU58F1M0xxx22 -if swd

SEGGER J-Link Commander V5.02f ('?' for help)

Compiled Oct 2 2015 20:52:00

Info: Device "MKV58F1M0XXX22" selected.

DLL version V5.02f, compiled Oct 2 2015 20:51:34

Firmware: J-Link V9 compiled Sep 18 2015 19:53:12

Hardware: V9.20

S∕N: -1

Feature(s): GDB, RDI, FlashBP, FlashDL, JFlash

Emulator has Trace capability

VTarget = 3.325V

Can not connect to target.

Failed to identify target. Trying again with slow (4 kHz) speed.

Can not connect to target.

No device found at all. Selecting JTAG as default target interface.

J-Link>_

```

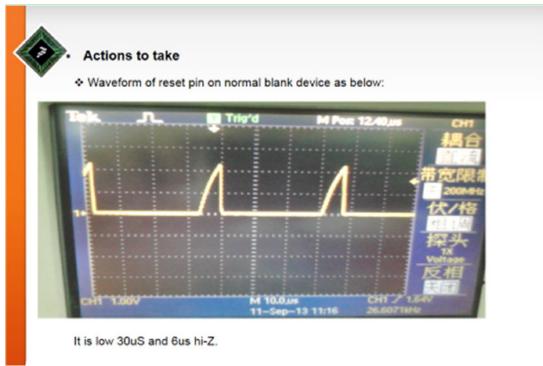

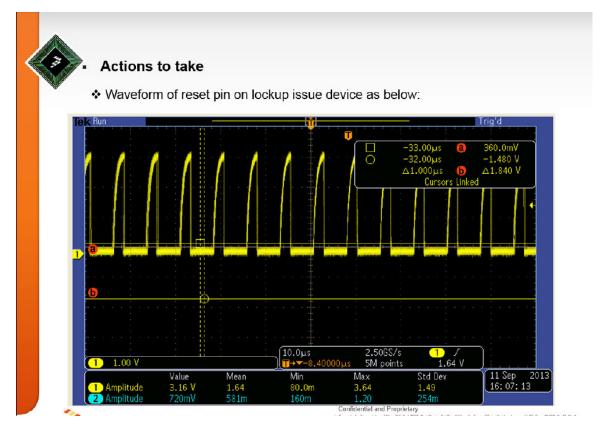

1.6 With power up, Reset pin will always with low voltage, or output oscillated signals (different with blanked chip), for example, KL chip without programmed, the reset pin output normal signal period is 36us and low voltage about 30us:

Locked KL chip the reset pin output signal with higher frequency, the signal may be different. And if the external circuit exists capacitive reactance, the signal period maybe changed.

Above behaviors most meet during software debug and production phase.

2. What's could be the root cause? It belongs to inevitable reasons and possible causes.

2.1 Inevitable reasons

<1> Welding problem: This problem with the highest probability during production phase. There with requirement the solder package peak temperature is 260° C, while during prototype production phase, there with problem to control the soldering temperature and the chip locked. That issue is hard to recover and maybe the chip is damaged. Even if there with temperature controlled (within 260° C) soldering station, the soldering time also be a consideration factor. The long soldering time also could cause chip locked. It must control the package peak temperature below 260° C with using SMT machine.

## 4.1 Thermal handling ratings

| Symbol           | Description                   | Min. | Max. | Unit | Notes |

|------------------|-------------------------------|------|------|------|-------|

| T <sub>STG</sub> | Storage temperature           | -55  | 150  | °C   | 1     |

| T <sub>SDR</sub> | Solder temperature, lead-free | _    | 260  | °C   | 2     |

|                  | Solder temperature, leaded    | —    | 245  |      |       |

1. Determined according to JEDEC Standard JESD22-A103, High Temperature Storage Life.

2. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

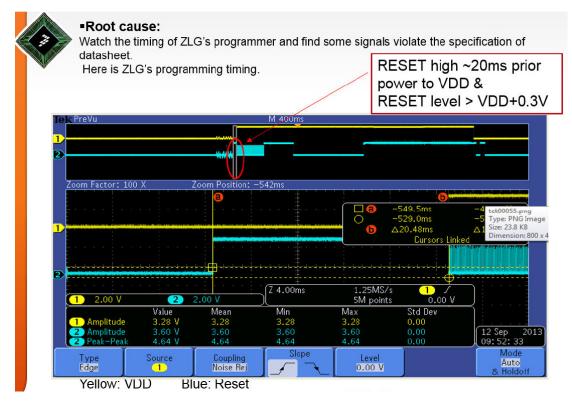

<2> Power up sequence: if reset pin power up earlier than VDD, it will lock the chip and hard to recover. It must be careful to check the power up sequence with power circuit or programmer tool.

<3> Add high voltage to Reset pin to modify the chip internal NVM/IFR setting, which was confirmed a manufactory operation, in order to change the chip ID configuration.

The mode of operation is latched on the rising edge of the reset pin. The monitor mode is selected by connecting two port lines to  $V_{ss}$  and applying an over-voltage of approximately 2 x  $V_{DD}$  to the IRQ1 pin concurrent with the rising edge of reset (see Table 3-1). Port allocation varies from part to part.

| IRQ1 Pin            | Port x | Port y | Mode    |

|---------------------|--------|--------|---------|

| ≤ V <sub>DD</sub>   | х      | x      | User    |

| 2 x V <sub>DD</sub> | 1      | 0      | Monitor |

Table 3-1. Mode Selection

<4> Too long debugger cable (such as 40~50cm) can lock the chip and make the debugger working unstable.

<5> Set chip in secured state, could be unsecured with external mass erased.

<6> Using fake J-Link tool can damage the debug port and cause chip lock.

Testing on the ATE revealed that four of the devices failed for leakage on various pins including the RESET pin. Unpowered curve trace analysis showed the RESET pin was open on Device 1 and normal on the remaining four units. The TCLK pin had no positive diode on Device 1 and leakage on Devices 2, 3, and 4. Devices 2, 3, and 4 exhibited leakage between Vdd and ground. Device 2 was selected for further analysis and decapsulated. OBIRCH (Optical Beam Induced Resistance Change) revealed a unique site near the JTAG TCLK pin. A visual inspection found evidence of EOS. Deprocessing and visual inspections found damage indicative of EOS.

2.2 Possible causes

<1> Hot plug.

<2> Software code: for example: enable LVD detection, program Flash to record this case and cause Flash content was modified; Frequently Erase-Program-Read cycling test trigger Flash self-protection mechanism. <3> Unstable power.

<4> Unstable debugger signals or glitch.

3. Unlock way (from easy to complex)

<1> It could check the reset pin signal, for the blanked chip will output the saw wave. Using the IDE software download the program will unlock the chip. If the chip was locked, it would pop up "chip secured" notification. Just using external mass erase will unlock the chip.

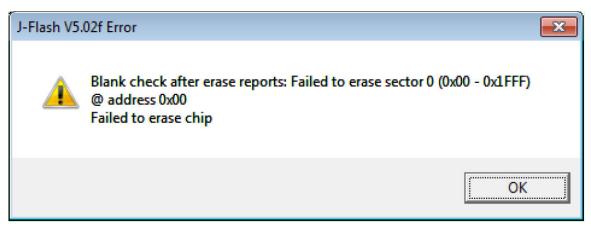

<2> Using J-Flash software and select chip part number and click [Check core ID], then connect the chip. The J-Flash tool try to find the device and compare with the core ID. If core ID isn't match or could not find the device, the connection will be failed.

| Project settings          |               |              |                                                            | ? <mark>- x</mark> |

|---------------------------|---------------|--------------|------------------------------------------------------------|--------------------|

| General Target Interfac   | e CPU   Flash | n Productio  | n                                                          |                    |

| 🗖 Use J-Link script file  |               |              |                                                            |                    |

| C <u>C</u> ore            |               |              | Chec <u>k</u> core ID<br>ID 3BA02477<br>Mask 0F000FFF      |                    |

|                           |               |              | ✓ Use target <u>B</u> AM (fa<br>Addr <mark>3F000000</mark> | aster)<br>256 KB ▼ |

| Init steps                | -             |              |                                                            |                    |

| # Action                  | Value0        | Value1       | Comment                                                    |                    |

| <u>A</u> dd <u>Insert</u> | Delete        | <u>E</u> dit | Шр                                                         | D <u>o</u> wn      |

|                           |               | ОК           | Cancel                                                     | Apply              |

<3> If connection done, then using [Target] menu's [Erase chip] command to unlock the chip.

| Project - Defa                 | Disconnect                                                    |       | scale\K   |       | .2.0\    | exam     |          |           |          | drive    | er_exa   | ampl    | es\gp    | oio\ia   | r\rele   | ease\   | gpio_   | exan    | nple.bii | n (=     |          |     | × |

|--------------------------------|---------------------------------------------------------------|-------|-----------|-------|----------|----------|----------|-----------|----------|----------|----------|---------|----------|----------|----------|---------|---------|---------|----------|----------|----------|-----|---|

| Connection                     | Show CFI info                                                 |       | : 0x120   |       |          | -        | ×1       |           | ×4       | -        | -        |         |          | -        |          |         | -       | -       |          | -        |          |     |   |

| Target interface               | Test                                                          | ,     | s 0<br>00 | 1 00  | 2        | 3<br>20  | 4<br>69  | 5<br>1F   | 6<br>00  | 7        | 8<br>97  | 9<br>1E | A<br>00  | B<br>00  | C<br>65  | D<br>1F | E<br>00 | F<br>00 | ASCI     | -        | e        |     | - |

| nit JTAG speed<br>JTAG speed   |                                                               |       | A3        | 1F    | 00       | 00       | AF       | <b>1F</b> | 00       | 00       | 2D       | 20      | 00       | 00       | 00       | 00      | 00      | 00      |          |          |          |     |   |

| TAP number                     | Secure chip                                                   |       | 00        | 00    | 00       | 00       | 00       | 00        | 00       | 00       | 00       | 00      | 00       | 00       | 2F       | 20      | 00      | 00      |          |          | /        |     |   |

| RPre                           | Unsecure chip                                                 |       | 31        |       | 00       | 00       | 00       | 00        | 00       | 00       | 33       | 20      | 00       | 00       | 35       | 20      | 00      | 00      | 1        |          | 35       |     |   |

| MCU                            | Check blank                                                   | F2    | 29        | 20    | 00       | 00       | 29       | 20        | 00       | 00       | 29       | 20      | 00       | 00       | 29       | 20      | 00      | 00      |          | >        |          | ••• |   |

| Endian                         | Fill with zero                                                | 12    | 29        |       | 00       | 00       | 29       | 20        | 00       | 00       | 29       | 20      | 00       | 00       | 29       | 20      |         |         |          | 0.000    | >>       |     |   |

| Check core Id<br>Core Id       |                                                               | 10000 | 29        |       | 00       | 00       | 29       | 20        | 00       | 00       | 29       | 20      | 00       |          | _        |         |         |         |          |          | >>       |     |   |

| Use target RAM                 | Erase sectors                                                 | F3    | 29        |       | 00<br>00 | 00<br>00 | 29<br>29 | 20        | 00<br>00 | 00<br>00 | 29<br>29 | 20      | 00<br>00 | 00<br>00 | 29<br>29 | 20      |         |         |          |          | ››       |     |   |

| RAM address<br>RAM size        | Erase chip                                                    | F4    | 29        |       | NN       | NN       | 29       | 20        | 00<br>NN | NN       | 29       | 20      | 00<br>NN | 00       | 29       | 20      |         |         |          |          | ;;       |     |   |

| HAM SIZE                       | Program                                                       | F5    | 29        |       | RN NO    | AN N     | 29       | 20        | RR NR    | 00       | 29       | 20      | 00       | 00       | 29       | 20      |         |         |          |          | ››       |     |   |

| Flash memory                   | Program & Verify                                              | F6    | 29        | 20    | 00       | 00       | 29       | 20        | 00       | 00       | 29       | 20      | 00       | 00       | 29       | 20      | 00      |         |          |          | >>       |     |   |

| Manufacturer<br>Size           |                                                               |       | 29        | 20    | 00       | 00       | 29       | 20        | 00       | 00       | 29       | 20      | 00       | 00       | 29       | 20      | 00      | 00      | >        | >        | ))       |     |   |

| Flash Id                       | Auto                                                          | F7    | 29        | 20    | 00       | 00       | 29       | 20        | 00       | 00       | 29       | 20      | 00       | 00       | 29       | 20      | 00      | 00      | >        | >        | ))       |     |   |

| Check flash Id<br>Base address | Verify                                                        | F8    | 29        | 20    | 00       | 00       | 29       | 20        | 00       | 00       | 29       | 20      | 00       | 00       | 29       | 20      | 00      | 00      | >        | >        | ))       |     |   |

| Organization                   | Verify CRC                                                    |       | 29        | 20    | 00       | 00       | 29       | 20        | 00       | 00       | 29       | 20      | 00       | 00       | 29       | 20      | 00      |         |          |          | ›>       |     |   |

|                                | Read back                                                     |       | _ 29      |       | 00       | 00       | 29       | 20        | 00       | 00       | 29       | 20      | 00       | 00       |          | 20      |         |         |          |          | ›)       |     |   |

| •                              | neud boek                                                     |       | 29        |       | 00       | 00       | 29       | 20        | 00       | 00       | 29       | 20      | 00       | 00       | 29       |         |         |         |          | ›        | >>       |     | - |

|                                | Start application                                             | F9    | 194       | -714  | LALA     | ININ     | .74      | -714      | ININ     | LAILA    | .74      | 714     |          | LALA     | 74       | -714    | LALA    | INIA    | · ·      | <u>'</u> | <u> </u> | _   | _ |

| LOG                            |                                                               |       |           |       |          |          |          |           |          |          |          |         |          |          |          |         |         |         |          |          | -        |     | 8 |

|                                | list [C:\Program Files\SEGGI<br>s read successfully (4934 Dev |       | V502f\E   | TC\JF | lash\l   | MCU.     | csv]     |           |          |          |          |         |          |          |          |         |         |         |          |          |          |     |   |

<4> If above steps don't work, keep the reset pin low and using [erase chip] command again.

<5> If still not work, please use J-Link software command window and using "unlock Kinetis" command to unlock the chip. Using this way, the chip's reset pin should connect with debugger's reset pin.

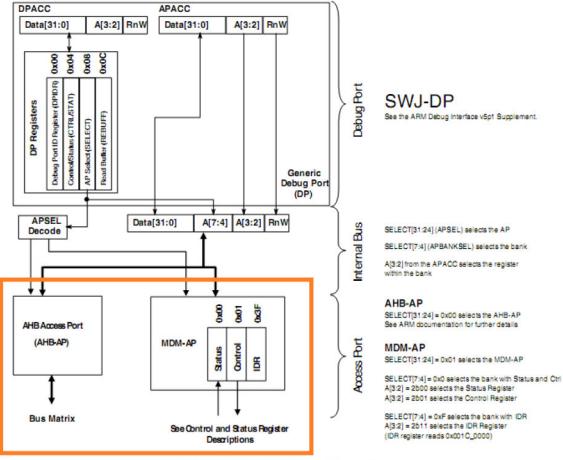

<6> Using Erase\_all\_pin.jlk script with J-Link tool. In J-Link software command window call "Jlink.exe erase\_all\_pin.jlk" and check the log, which will indicate if find the "Debug Access Port" and if using this port find MCU core. If it could find the AHB-AP, then it can use this interface to access MDM-AP and to check MCU status & ID.

## Figure 9-3. MDM AP Addressing

<7> If the SWD-DP interface could not be found, the debug port may be damaged or could not accept connecting or could not find the MCU core. Then the way left was to keep the reset pin in low voltage and run this script many times. There exist using this script more time could unlock the chip. After the chip unlocked, the chip will work normally.

```

J-Link Commander

SEGGER J-Link Commander V4.24 ('?' for help)

Compiled Feb 17 2011 16:01:04

DLL version V4.24, compiled Feb 17 2011 16:00:51

Firmware: J-Link ARM V7 compiled Feb 15 2011 11:03:33

Hardware: V7.00

S/N: 11111117

Feature(s): RDI, FlashBP, FlashDL, JFlash, GDBFull

VTarget = 3.326V

Info: TotalIRLen = 4, IRPrint = 0x01

Info: ARM AP[0]: 0x24770011, AHB-AP

Info: ARM AP[1]: 0x001C0000, JTAG-AP

***** Error: No APB-AP found.

o devices found on JTAG chain. Trying to find device on SWD.

nfo: Found SWD-DP with ID 0x2BA01477

WARNING: ROM table: Two components occupy the same memory space.

Info:

FPUnit: 1 code (BP) slots and 0 literal slots

WARNING: CPU core not found.

No device found on SWD.

Did not find any core.

Info: TotalIRLen = 4, IRPrint = 0x01

Info: ARM AP[0]: 0x24770011, AHB-AP

Info: ARM AP[1]: 0x001C0000, JTAG-AP

***** Error: No APB-AP found.

No devices found on JTAG chain. Trying to find device on SWD.

Info: Found SWD-DP with ID 0x2BA01477

WARNING: ROM table: Two components occupy the same memory space.

FPUnit: 1 code (BP) slots and 0 literal slots

Info:

WARNING: CPU core not found.

No device found on SWD.

Did not find any core.

J-Link≻

```

<8> If above ways do not work, please update J-Link hardware firmware and related J-Link software, or using P&E USB Multilink tool. There with successfully unlock examples with that suggestion.