### **EzPort K64 Hardware Configuration**

### Introduction

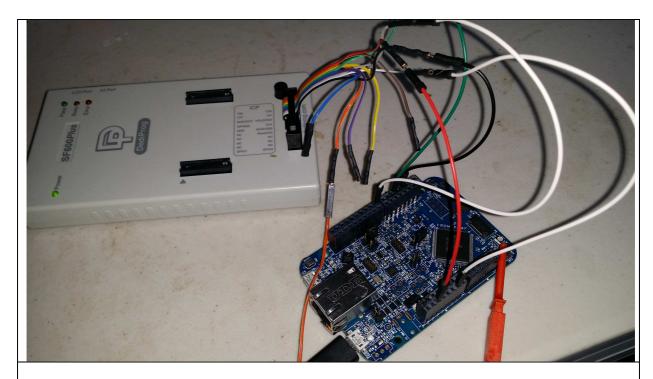

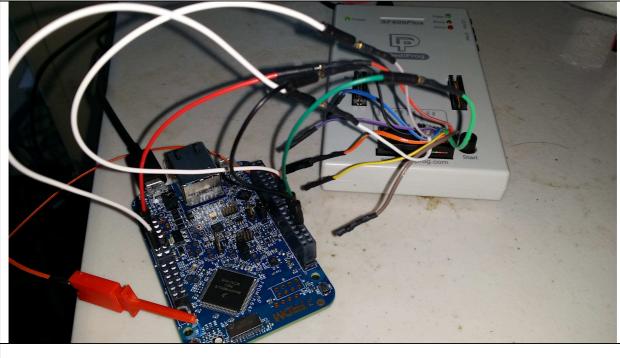

This document describes installing and testing of SF600 Plus DediProgrammer with Freescale K64 processor on FRDM K64 evaluation board.

The purpose of this document is to determine if the SF600 Plus is compatible with EzPort feature of the MK64FN1M0VLL12 processor as claimed by the manufacturer.

I've purchased a SF600 Plus programmer and below are my notes on setting up the hardware and software. I'm following the directions provided by DediProg on setting up EzPort in the EzPortsupport.pdf document. Unfortunately, the directions are not clear and I've been unable to get the programmer to work.

# **Installing Dediport Driver**

Follow directions provided in DediProg SF software user manual. Installation requires manually installing driver. Must tell operating system where inf file on CD or drive.

# Installing SF600 desktop software

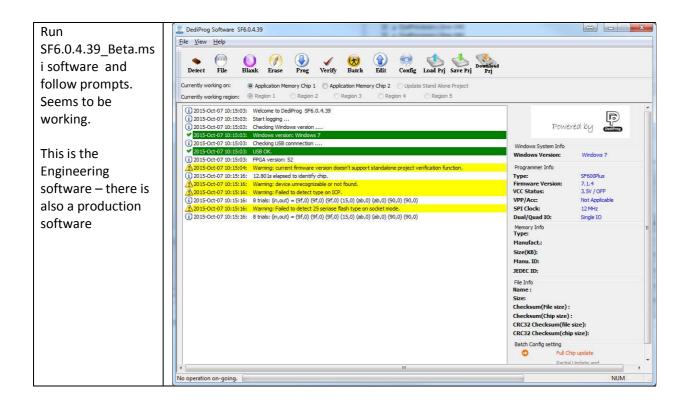

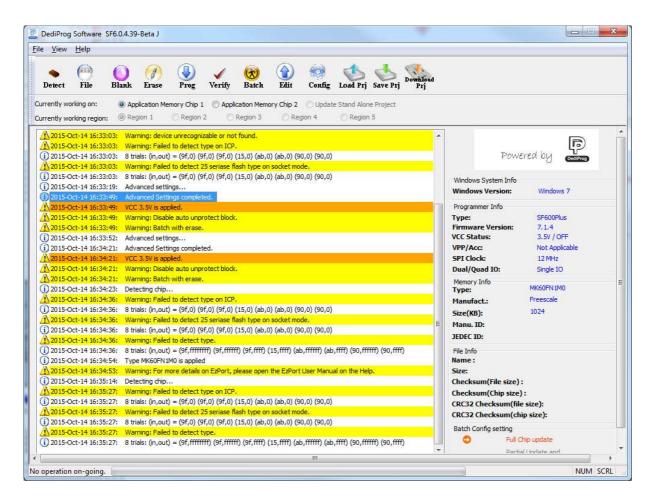

So the desktop software seems to be working – its trying to identify the device – but I don't have any hardware connected.

Note: Warning current firmware version doesn't support standalone project verification function – what does that mean?

#### **Hardware Connection Table**

Connecting SF600 to K64 chip via SWD connector on my board. Below are connection details

Table 2 from DediProg EzPort user manual for SF600

| Pin Number | SF600 | Freescale MCU |

|------------|-------|---------------|

| 2          | CS2   | #RSTI         |

| 3          | CS1   | #EZPCS        |

| 5          | MISO  | EZPQ          |

| 8          | CLK   | EZPK          |

| 9          | GND   | GND           |

| 10         | MOSI  | EZPD          |

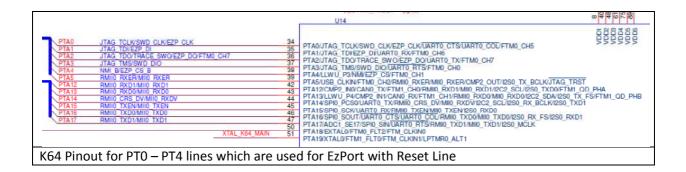

K64 pins vs SWD header on board vs SF600 DediProgammer pinout

| K64  | K64 | K64 EZP  | K64 SWD  | K64 JTAG | Header | SF600 | SF600 | SF600 | Comment |

|------|-----|----------|----------|----------|--------|-------|-------|-------|---------|

| Pin  | Pin | Pin Name | Pin Name | Pin Name | PIN on | Pin   | Pin # | Cable |         |

| Name | #   |          |          |          | Board  | Name  |       | Color |         |

| PTA3              | 37 |                    | SWD_DIO                | JTAG TMS  | 2              |      |    |        |                                                                       |

|-------------------|----|--------------------|------------------------|-----------|----------------|------|----|--------|-----------------------------------------------------------------------|

| PTA0              | 34 | EZP_CLK<br>EZP_CK? | SWD<br>CLK             | JTAG TCLK | 4              | CLK  | 8  | Gray   |                                                                       |

| PTA2              | 36 | EZP_D0<br>EZP_Q?   | SWO /EXTa<br>/TRACECTL | JTAG TDO  | 6              | MISO | 5  | green  |                                                                       |

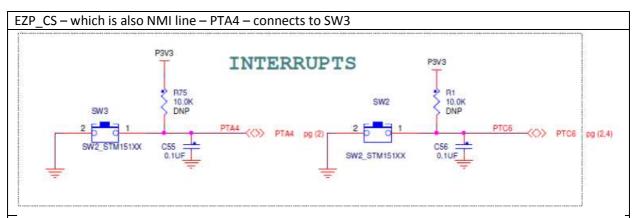

| PTA4<br>or<br>NMI | 38 | EZP_CS             | N/A                    |           | 7?<br>Key Pin  | CS 1 | 3  | orange | 10K pull up<br>on line. Will<br>programmer<br>be able to<br>pull low? |

| PTA1              | 35 | EZP_DI<br>EZP_D?   | NC/EXTb                | JTAG TDI  | 8?             | MOSI | 10 | black  | Unconnected – no trace on Rev F green wire                            |

|                   |    |                    |                        |           | 3 and 5<br>GND | GND  | 9  | white  |                                                                       |

| Reset             | 52 |                    |                        | nRESET    | 10             | CS 2 | 2  | red    |                                                                       |

## **Connecting Dediport to Target FRDM-K64**

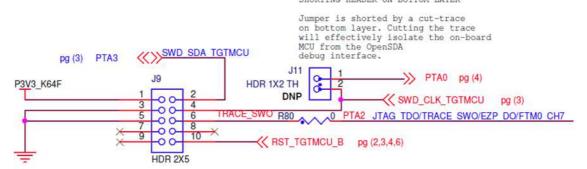

Most of the connection points required for EzPort on the FRDM-K64 board are exposed on the Serial Wire Debug (SWD) connector. This connector is used a segger j-link to load and debug software.

The purpose of this document is to see if the SF600 plus DediProg can access the K64 processor's EzPort.

Before connecting the programmer to the FRDM-K64, scratch out the trace jumper at J11 and install a two pin header. Leave the jumper J11 open. This cuts the clock signal from the OpenSDA circuit to PTAO (SWD\_CLK/EZP\_CLK).

SHORTING HEADER ON BOTTOM LAYER

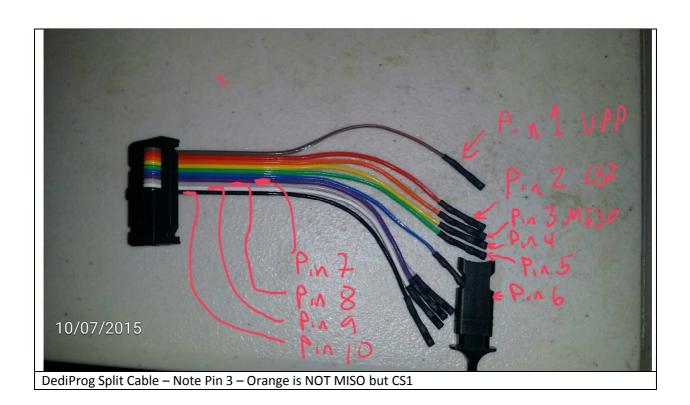

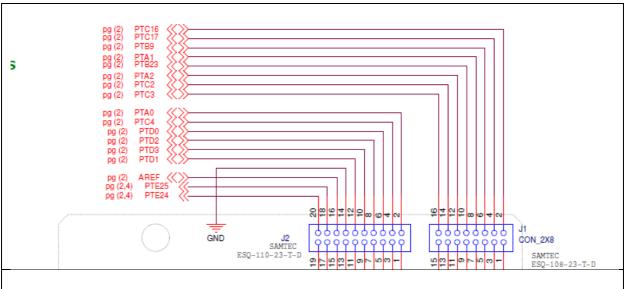

PTA0 (EZP\_CLK) (pin 34 k64) is on pin 2 of J2 (2x10) - Gray Wire on DediProg Split Cable PTA1 (EZP\_DI) (pin 35 k64) is on pin 8 of J1 (2x8) Black Wire on DediProg Split Cable PTA2 (EZP\_DO) (pin 36 K64) is pin 12 j1 (2x8) and on pin 6 of SWD connector - GREEN Wire on DediProg Split Cable

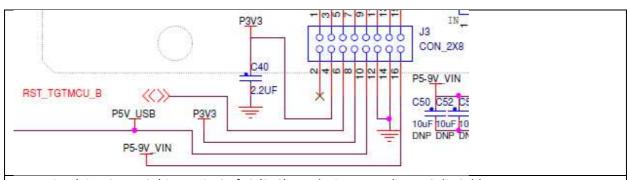

Reset Line (pin 52 on K64) is on pin 6 of J3 (2x8) - red wire on DediProg Split Cable Gnd are pins 12 and 14 on J3 (2x8) White on DediProg Split Cable

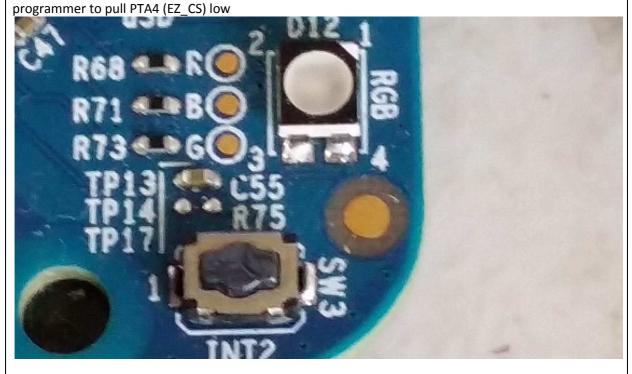

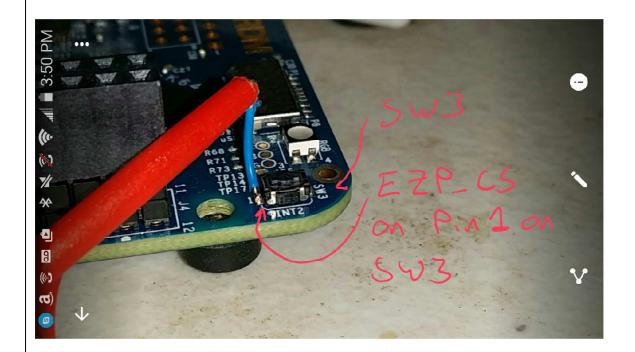

PTA4 (EZP\_CS\_B) (pin 38) is connected to SW3 - Orange Wire on DediProg Split Cable

Note: on rev D1 board/schematic – R75 is DNP (do not populate) – so should not be hard for

Note: I've installed a wire on pin 1 of SW3 that connects to the Orange Wire on Split Cable – CS1

Below is what final wiring looks like

### DediProg Engineer Software Set up

These are the directions for EzPort Set up document. I've followed them and tried various alternatives. No option seems able to detect the part type – nor read the part's memory.

- 1.) Open DediProg Engineering software.

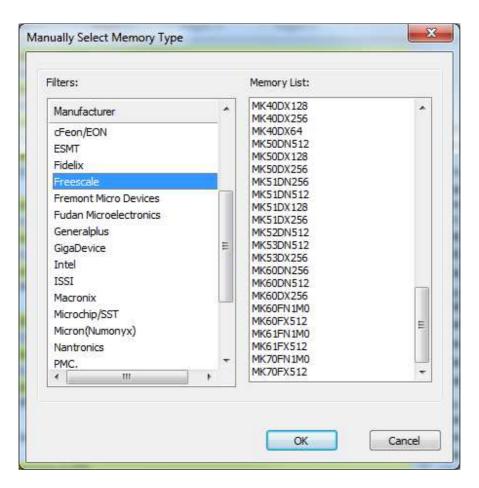

- a. Click on Detect and select Freescale part number Note: No K64 part number but K61, K60 and K70 part numbers

Do I pick K61FN1M0 or MK64FN1M0 or K70FN1MO – which all seem to have 1M of flash?

I picked MK61FN1MO - DediProg has indicated this is a valid choice.

"Config->Miscellaneous Setting->SPI Clock Setting" to select SPI clock frequency according to your application system frequency.

Really don't have an SPI clock – but I'll pick 12MHZ – DediProg has indicated this choice is valid

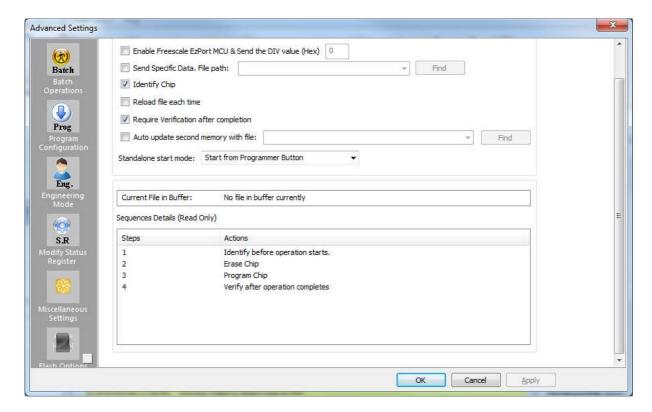

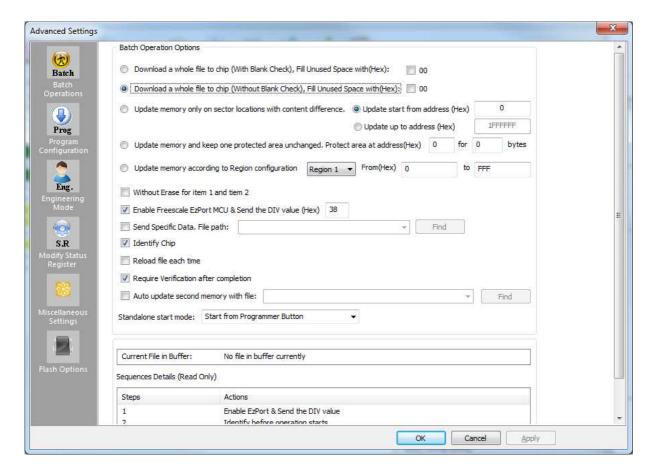

3. Enable "Config->Batch Operations->Enable Freescale EzPort MCU & Send the DIV value".

- 4. Set the flash machine clock (FCLK) by the following procedure:

- A. If Fsys is greater than 25.6 MHz, PRDIV8 equals 1; otherwise, PRDIV8 equals 0.

- B. Determine DIV[5:0] by using the following equation. Keep only the integer portion of the result and discard any fraction. Do not round the result.

$$DIV = \frac{Fsys}{2 \times 200kHz \times (1 + (PRDIV8 \times 7))}$$

For proper program and erase operations, it is critical to set FCLK between 150 kHz and 200 kHz. Array damage due to overstress can occur when FCLK is less than 150 kHz. Incomplete programming and erasure can occur when FCLK is greater than 200 kHz.

So lets try 22.5mhz (default internal clock of K64) / 400000 = 56 = 0x38 - DediProg did not confirm this value - it assumes the K64's internal clock is running the part at reset before any code initializes the clock registers.

Enable DediProg Engineering software "Config->Batch Operations->Enable Freescale EzPort MCU & Send the DIV value" and fill out the DIV value.

- 5. Load file and then click on "Batch", EzPort will be enabled and software will program the Freescale MCU according to Batch options.

- 6. For Read command to return the correct data, the EzPort Clock (EZPCK) must run at no more than divide by eight of the internal system clock.

#### **Results**

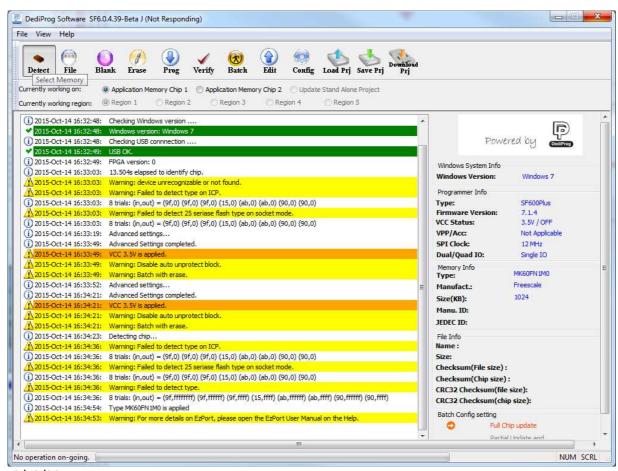

When I hit detect button in software, DediProg does NOT detect part type. It seems to try to reset board, but it doesn't seem to recognize K64 part. When I manually input K61, K60 or K70 part, I still can't read K64 memory.

10/13/2015

Installed new beta software - no change really

All attempts to identify the chip fail.

I've also tried the edit button (read the chip) but they also fail.

If anybody has had any luck getting this DediProg SP600 (or any other DediProg product) working with a Kinetis processor, please advise.