NXP Semiconductors Application Notes

# **Enhanced Features in i.MX RT1060**

## 1. Introduction

The i.MX RT1060 is the latest addition to the industry's first crossover processor series, The i.MX RT1060 doubles the On-Chip SRAM to 1 MB while keeping pin-to-pin compatibility with i.MX RT1050. This new series introduces additional features ideal for real-time applications such as High-Speed GPIO, CAN-FD, and synchronous parallel NAND/NOR/PSRAM controller. The i.MX RT1060 runs on the Arm® Cortex®-M7 core at 600 MHz.

The document intends to introduce these enhanced features comparing i.MX RT1050.

#### Contents

| 1. | Introd | uction          | 1  |

|----|--------|-----------------|----|

| 2. | Overv  | iew             | 2  |

| 3. | Enhan  | ced Features    | 3  |

|    | 3.1.   | On-Chip RAM     | 3  |

|    | 3.2.   | Platform        | 3  |

|    | 3.3.   | External memory | 6  |

|    | 3.4.   | Connectivity    | 7  |

|    | 3.5.   | ROM             | 11 |

| 4. | Concl  | usion           | 14 |

| 5. | Revisi | on history      | 14 |

|    |        |                 |    |

# 2. Overview

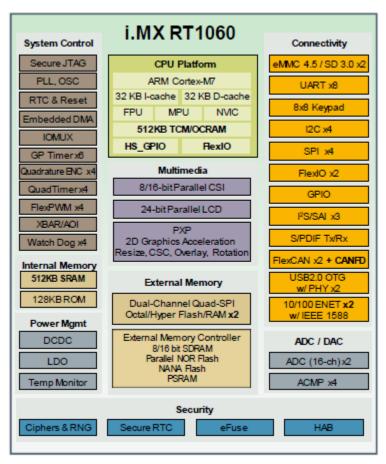

i.MX RT1060 keeps pin to pin compatibility with i.MX RT1050, and add some features to improve its performance over i.MX RT1050. Below is the block diagram of i.MX RT1060:

Figure 1. i.MX RT1060 block diagram

Table1 lists the enhanced features of i.MX RT1060 in comparison of i.MXRT1050:

| Items            | Enchanced features on i.MX RT1060                             |  |  |  |  |

|------------------|---------------------------------------------------------------|--|--|--|--|

| On-chip RAM(1MB) | 512 KB OCRAM shared between ITCM/DTCM and OCRAM               |  |  |  |  |

|                  | Dedicate 512 KB OCRAM                                         |  |  |  |  |

|                  | Support flash remapping address setting                       |  |  |  |  |

| latform          | Tightly coupled GPIOs, operating at the same frequency as ARM |  |  |  |  |

| External memory  | Two Single/Dual channel Quad SPI FLASH with XIP support       |  |  |  |  |

Table 1. Enhanced features on I.MXRT1060

|                    | Small size SDRAM support with 8 column or 2 bank                                |

|--------------------|---------------------------------------------------------------------------------|

|                    | Add synchronous function on parallel NAND<br>flash/PNOR/PSRAM by SEMC interface |

| O serve a the iter | Two 10M/100M Ethernet controller with support for IEEE1588                      |

| Connectivity       | Add one CANFD module                                                            |

|                    | Three FlexIO modules                                                            |

| ROM                | Support auto-probe                                                              |

|                    | Support flash remapping setting                                                 |

These features enables i.MXRT1060 to be fully compatible with i.MXRT1050 to improve the performance. Below sections provide the details of the new features and how they improve the performance.

# 3. Enhanced Features

## 3.1. On-Chip RAM

i.MX RT1050 provides the 512 KB FlexRAM, it can flexibly configure to ITCM, DTCM and OCRAM. Users can locate the application code to ITCM, and data to DTCM to get high performance. It can get higher performance for DMA accessing OCRAM, so FlexRAM provides the capacity of flexibly configuring RAM type base on the different applications, which benefit to improve the performance.

i.MX RT1060, not only has the same FlexRAM feature, but also add the dedicated 512 KB OCRAM, so it has 1 MB RAM space for users to locate the key code/data to TCM or OCRAM.

Memory map for On-Chip RAM is as below:

| Memory Type | Start Address | End Address | Allocation      |  |  |  |

|-------------|---------------|-------------|-----------------|--|--|--|

|             | 2020_0000     | 2027_FFFF   | OCRAM           |  |  |  |

| OCRAM       | 2028_0000     | 202F_FFFF   | FlexRAM (OCRAM) |  |  |  |

| DTCM        | 2000_0000     | 2007_FFFF   | DTCM            |  |  |  |

| ITCM        | 0000_0000     | 0007_FFFF   | ITCM            |  |  |  |

Table 2. Memory map for on-chip memory

## 3.2. Platform

i.MX RT1060 also improve the platform to get the high performance.

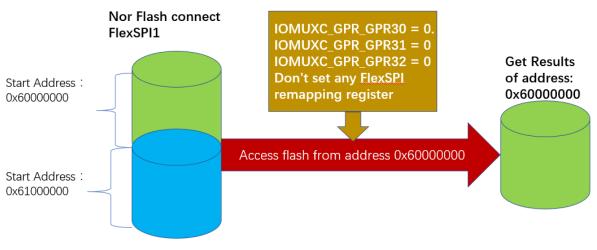

## 3.2.1. Flash Address Remapping Setting

i.MXRT1060 provides one feature to remap FlexSPI1 and FlexSPI2 address, that means it can use the same address map to different flash physical address, which is interfaced by FlexSPI1 and FlexSP2. Enhanced Features in i.MX RT1060, Application Notes, Rev. 0, 09/2018 To implement this, it provide three registers.

#### • IOMUXC\_GPR\_GPR30

Specified start address of flexspi1 and flexspi2

#### • IOMUXC\_GPR\_GPR31

Specified end address of flexspi1 and flexspi2

#### • IOMUXC\_GPR\_GPR32

Specified offset address of flexspi1 and flexspi2, When ADDR\_START[31:12]  $\leq$  Addr\_i[31:12], remapped address Addr\_o = Addr\_i[31:12] + {OFFSET[31:12],12'h0}; Otherwise Addr\_o = Addr\_i, where Addr i: original access address

Addr\_o: remapped address

For example:

Don't set any FlexSPI remapping register, it will get flash contents of corresponding accessing address, don't do any remapping.

Figure 2. Access FlexSPI without any remapped setting

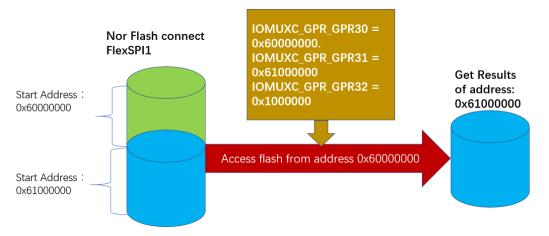

After setting reampping register, when try to access the same flash address, it will get the remapping address contents.

Figure 3. Access FlexSPI with remapped address setting

With this feature, user can easily switch the firmware located in different flash space, and multiple firmware can share the same linker file, which benefit OTA application. it is available to receive the firmware and save to different flash address, after the received firmware to be verified, easily switch to new firmware to run by this flash remapping feature, it is easy for use and keep high reliability during firmware upgrade, user don't need to build the firmware with different linker file, reduce the operation complexity and avoid the issue happen.

The embedded ROM of i.MXRT1060 also support flash remapping, which allow to program the multiple firmware to flash, and switch firmware by provided API function, for detail information please refer to below chapter" 3.5.2"

#### 3.2.2. Tightly coupled GPIOs access

i.MX RT provides the tightly coupled GPIO, enable to be accessed with high frequency.

It provides two set of GPIOs registers to control pads output. GPIO1 to GPIO3 is general GPIO, and GPIO6 to GPIO8 is tightly GPIO, but they share the same pad, that means the gpio pin can select from GPIO1/2/3 to GPIO6/7/8.

The registers IOMUXC\_GPR\_GPR26, IOMUXC\_GPR\_GPR27, and IOMUXC\_GPR\_GPR28 are for GPIO selection.

Below is the description of IOMUXC\_GPR\_GPR26 register:

Table 3.

IOMUXC\_GPR\_GPR26 descriptions

| Field                  | Description                                                                                                                                                   |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO_MUX1_<br>GPIO_SEL | GPIO1 and GPIO6 share same IO MUX function, GPIO_MUX1 selects one GPIO function.                                                                              |

|                        | <ul> <li>This register controls GPIO_MUX1 to select GPIO1 or GPIO6. For bit n,</li> <li>0: GPIO1[n] is selected;</li> <li>1: GPIO6[n] is selected.</li> </ul> |

With this register, it is available for user to select generally GPIO(slow) or fast GPIO routing to corresponding pad, when GPIO6/7/8 is selected, the corresponding pad can be up to 150Mhz when toggle this GPIOs to output waveform.

### 3.3. External memory

#### 3.3.1. Two same FlexSPI interface

i.MX RT1060 add one FlexSPI interface, which provides the capacity of interfacing with multiple flash or SRAM device. One typical use case is to use one flexspi interface to connect serial nor flash for code location, and the other interface is to connect hyper RAM. It saves pins comparing SDRAM, only about 11 pins is needed.

#### 3.3.2. SDRAM enhanced features

As i.MXRT1050 limit the column address width to 9 bit or more, fail to support less address width, but for some small size SDRAM, which require the column address width to be 8bit, so it fail to support these small size SDRAM

To implement this, it add two bit field in register SEMC\_SDRAMCR0, and detail description as below:

Add bit field BANK2 for 2 bank and 4 bank selectable.

0 - SDRAM device has 4 banks.

1 - SDRAM device has 2 banks.

There are two register for column address definition one is bit field COL, it is same with i.MX RT1050.

00b - 12 bit

01b - 11 bit

10b - 10 bit

11b - 9 bit

The other register field(CLO8) is new for i.MX RT1060.

0b - Column address bit number is decided by COL field.

1b - Column address bit number is 8. COL field is ignored.

#### 3.3.3. SEMC support PNOR/PSRAM/NAND with sync mode

i.MX RT1060 improves the SEMC IP to support sync mode, which can support NAND flash, Nor flash and SRAM by sync mode, which can further improve the performance.

## 3.4. Connectivity

i.MX RT1060 enhanced features on connectivity include Ethernet interface, Flexible Data-rate Controller Area Network and Flexible I/O.

### 3.4.1. Two 10M/100M Ethernet controller

Two 10M/100M ethernet controller are added to support two ethernet interfaces, that benefit to connectivity application.

And new adder ethernet interface pinmux as below:

| Instance | Port         | Pad           | Mode |  |  |

|----------|--------------|---------------|------|--|--|

| Instance | Port         |               |      |  |  |

|          | ENET2_MDC    | GPIO_EMC_38   | ALT8 |  |  |

|          |              | GPIO_B0_00    | ALT8 |  |  |

|          | ENET2_MDIO   | GPIO_EMC_39   | ALT8 |  |  |

|          |              | GPIO_B0_01    | ALT8 |  |  |

|          |              | GPIO_EMC_30   | ALT8 |  |  |

|          | ENET2_TDATA0 | GPIO_B0_12    | ALT8 |  |  |

|          |              | GPIO_B1_14    | ALT8 |  |  |

|          |              | GPIO_EMC_31   | ALT8 |  |  |

|          | ENET2_TDATA1 | GPIO_B0_13    | ALT8 |  |  |

|          |              | GPIO_B1_15    | ALT8 |  |  |

|          | ENET2_TDATA2 | GPIO_B0_05    | ALT8 |  |  |

|          | ENET2_TDATA3 | GPIO_B0_04    | ALT8 |  |  |

|          | ENET2_TX_CLK | GPIO_EMC_33   | ALT8 |  |  |

|          |              | GPIO_B0_15    | ALT8 |  |  |

| ENET2    |              | GPIO_SD_B0_01 | ALT8 |  |  |

|          | ENET2_TX_EN  | GPIO_EMC_32   | ALT8 |  |  |

|          |              | GPIO_B0_14    | ALT8 |  |  |

|          |              | GPIO_SD_B0_00 | ALT8 |  |  |

|          | ENET2_TX_ER  | GPIO_B0_07    | ALT8 |  |  |

|          |              | GPIO_EMC_35   | ALT8 |  |  |

|          | ENET2_RDATA0 | GPIO_B1_01    | ALT8 |  |  |

|          |              | GPIO_SD_B0_03 | ALT8 |  |  |

|          |              | GPIO_EMC_36   | ALT8 |  |  |

|          | ENET2_RDATA1 | GPIO_B1_02    | ALT8 |  |  |

|          |              | GPIO_SD_B0_04 | ALT8 |  |  |

|          | ENET2_RDATA2 | GPIO_B0_09    | ALT8 |  |  |

|          | ENET2_RDATA3 | GPIO_B0_08    | ALT8 |  |  |

|          | ENET2_RX_CLK | GPIO_B0_06    | ALT8 |  |  |

|          | ENET2_RX_EN  | GPIO_EMC_37   | ALT8 |  |  |

Table 4.

Muxing options for ethernet 2

#### Enhanced Features

|                       | GPIO_B1_03                                                                                                                                                                                                          | ALT8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | GPIO_SD_B0_05                                                                                                                                                                                                       | ALT8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                       | GPIO_EMC_34                                                                                                                                                                                                         | ALT8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ENET2_RX_ER           | GPIO_B1_00                                                                                                                                                                                                          | ALT8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                       | GPIO_SD_B0_02                                                                                                                                                                                                       | ALT8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                       | GPIO_EMC_33                                                                                                                                                                                                         | ALT9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ENET2_REF_CLK2        | GPIO_B0_15                                                                                                                                                                                                          | ALT9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                       | GPIO_SD_B0_01                                                                                                                                                                                                       | ALT9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                       | GPIO_AD_B1_01                                                                                                                                                                                                       | ALT8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ENETZ_1000_EVENTU_IN  | GPIO_B0_03                                                                                                                                                                                                          | ALT8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ENET2_COL             | GPIO_B0_11                                                                                                                                                                                                          | ALT8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ENET2_CRS             | GPIO_B0_10                                                                                                                                                                                                          | ALT8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ENET2_1588_EVENT1_IN  | GPIO_AD_B1_11                                                                                                                                                                                                       | ALT8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ENET2_1588_EVENT2_IN  | GPIO_AD_B1_13                                                                                                                                                                                                       | ALT8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ENET2_1588_EVENT3_IN  | GPIO_AD_B1_15                                                                                                                                                                                                       | ALT8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                       | GPIO_AD_B1_00                                                                                                                                                                                                       | ALT8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ENET2_1300_EVENT0_001 | GPIO_B0_02                                                                                                                                                                                                          | ALT8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ENET2_1588_EVENT1_OUT | GPIO_AD_B1_10                                                                                                                                                                                                       | ALT8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ENET2_1588_EVENT2_OUT | GPIO_AD_B1_12                                                                                                                                                                                                       | ALT8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ENET2_1588_EVENT3_OUT | GPIO_AD_B1_14                                                                                                                                                                                                       | ALT8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                       | ENET2_REF_CLK2<br>ENET2_1588_EVENT0_IN<br>ENET2_COL<br>ENET2_CRS<br>ENET2_1588_EVENT1_IN<br>ENET2_1588_EVENT2_IN<br>ENET2_1588_EVENT3_IN<br>ENET2_1588_EVENT0_OUT<br>ENET2_1588_EVENT1_OUT<br>ENET2_1588_EVENT2_OUT | GPIO_SD_B0_05           ENET2_RX_ER         GPIO_EMC_34           GPIO_B1_00         GPIO_SD_B0_02           GPIO_EMC_33         GPIO_EMC_33           ENET2_REF_CLK2         GPIO_B0_15           GPIO_SD_B0_01         GPIO_SD_B0_01           ENET2_1588_EVENT0_IN         GPIO_B0_13           ENET2_COL         GPIO_B0_11           ENET2_CCL         GPIO_B0_11           ENET2_CRS         GPIO_B0_10           ENET2_1588_EVENT1_IN         GPIO_AD_B1_13           ENET2_1588_EVENT2_IN         GPIO_AD_B1_13           ENET2_1588_EVENT3_IN         GPIO_AD_B1_00           ENET2_1588_EVENT1_OUT         GPIO_AD_B1_00           ENET2_1588_EVENT1_OUT         GPIO_AD_B1_10           ENET2_1588_EVENT1_OUT         GPIO_AD_B1_10           ENET2_1588_EVENT1_OUT         GPIO_AD_B1_12 |

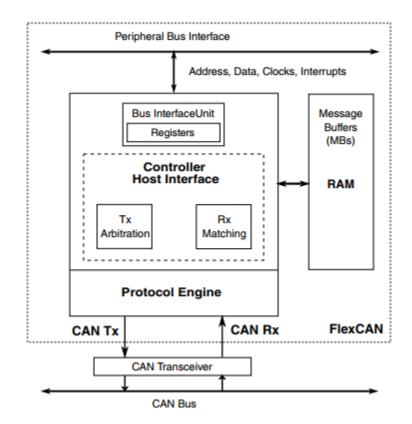

#### 3.4.2. Flexible Data-rate Controller Area Network

i.MXRT1060 add one new module "flexible Data-rate Controller Area Network (CANFD/FlexCAN), which is used for that application required high speed and reliability industry control bus,CANFD is a full implementation of the CAN protocol specification, which supports both standard and extended message frames and long payloads up to 64 bytes transferred at faster rates up to 8 Mbps. The message buffers are stored in an embedded RAM dedicated to the CANFD/FlexCAN module.

The block diagram as below:

Figure 4. CANFD/FlexCAN Block Diagram

The CANFD/FlexCAN module includes these distinctive features:

- Full implementation of the CAN with Flexible Data- Rate (CAN FD) protocol specification and CAN protocol specification, Version 2.0 B

- Standard data frames

- Extended data frames

- Zero to sixty four bytes data length

• Programmable bit rate (see the chip-specific FlexCAN information for the specific maximum rate configuration)

- Content-related addressing

- Compliant with the ISO 11898-1 standard

- Flexible mailboxes configurable to store 0 to 8, 16, 32 or 64 bytes data length

- Each mailbox configurable as receive or transmit, all supporting standard and extended messages

- Individual Rx Mask registers per mailbox

- Full-featured legacy Rx FIFO with storage capacity for up to six frames and automatic internal pointer handling with DMA support Full-featured enhanced Rx FIFO with storage capacity for up to 32 CAN FD frames and automatic internal pointer handling with DMA support.

- Transmission abort capability

• Flexible message buffers (MBs), totaling 64 message buffers of 8 bytes data length each, configurable as Rx or Tx

- Programmable clock source to the CAN Protocol Interface, either peripheral clock or oscillator clock

- RAM not used by reception or transmission structures can be used as general purpose RAM space

#### Enhanced Features

- Listen-Only mode capability

- Programmable Loop-Back mode supporting self-test operation

- Programmable transmission priority scheme: lowest ID, lowest buffer number, or highest priority

- Time stamp based on 32-bit free-running timer, with an optional external time tick

- Global network time, synchronized by a specific message

- Maskable interrupts

- Independence from the transmission medium (an external transceiver is assumed)

- Short latency time due to an arbitration scheme for high-priority messages

- Low power modes, with programmable wake up on bus activity

- Transceiver Delay Compensation feature when transmitting CAN FD messages at faster data rates

- Remote request frames may be handled automatically or by software

- CAN bit time settings and configuration bits can only be written in Freeze mode

- Tx mailbox status (Lowest priority buffer or empty buffer)

- Identifier Acceptance Filter Hit Indicator (IDHIT) register for received frames

• SYNCH bit available in Error in Status 1 register to inform that the module is synchronous with CAN bus

- CRC status for transmitted message

- Legacy Rx FIFO Global Mask register

- Selectable priority between mailboxes and Rx FIFO during matching process

• Powerful legacy Rx FIFO ID filtering, capable of matching incoming IDs against either 128 extended, 256 standard, or 512 partial (8 bit) IDs, with up to 32 individual masking capability

• Powerful Enhanced Rx FIFO ID filtering, capable of matching incoming IDs against either 64 extended or 128 standard ID filter elements with three filtering schemes: mask + filter, range, and two filters without mask.

• 100% backward compatibility with previous FlexCAN version

#### 3.4.3. Flexible I/O

i.MX RT1060 supports up to three Flexible I/O(FlexIO) instances, while i.MX RT1050 only supports two instances, FlexIO3 instance can support fast clock soure which is clocked from ahb\_clock\_root, same to core clock, while other two FlexIO instance clocked by ipg\_clk\_root, limit frequency to 120MHz.

See below clock tree for FlexIO modules.

| Table 5. | FlexIO | clock | options |

|----------|--------|-------|---------|

|----------|--------|-------|---------|

| Module  | Module Clock       | Clock Root       | Module Clock Gating Enable      |  |  |  |

|---------|--------------------|------------------|---------------------------------|--|--|--|

|         | flexio1_ipg_clk    | ipg_clk_root     | CCGR5[CG1] (flexio1_clk_enable) |  |  |  |

|         | flexio1_ipg_clk_s  | ipg_clk_root     | CCGR5[CG1] (flexio1_clk_enable) |  |  |  |

| FLEXIOn | flexio1_flexio_clk | flexio1_clk_root | CCGR5[CG1] (flexio1_clk_enable) |  |  |  |

|         | flexio2_ipg_clk    | ipg_clk_root     | CCGR3[CG0] (flexio2_clk_enable) |  |  |  |

| flexio2_ipg_clk_s  | ipg_clk_root     | CCGR3[CG0] (flexio2_clk_enable) |

|--------------------|------------------|---------------------------------|

| flexio2_flexio_clk | flexio2_clk_root | CCGR3[CG0] (flexio2_clk_enable) |

| flexio3_ipg_clk    | ahb_clk_root     | CCGR7[CG6] (flexio3_clk_enable) |

| flexio3_ipg_clk_s  | ipg_clk_root     | CCGR7[CG6] (flexio3_clk_enable) |

| flexio3_flexio_clk | flexio2_clk_root | CCGR7[CG6] (flexio3_clk_enable) |

#### 3.5. ROM

i.MX RT1060 increased the ROM size to 128 KB, while RT1050 only supports 96 KB. Also, it implements the auto probe and flash remapping functions on RT1060, see detailed introduction below.

#### 3.5.1. Auto Probe

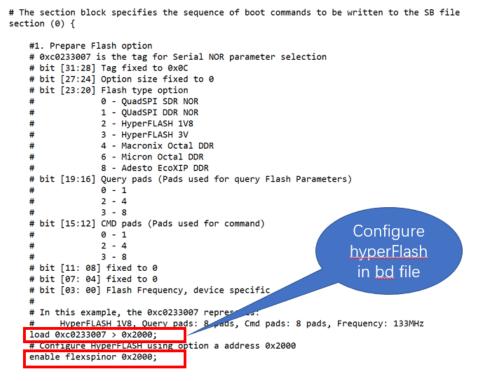

Usually, to enable external flash working well in flashless parts, it need to get the flash configuration information by reading flash configuration block specified by user. For example, RT1050 asks customer to input flash configure bit field (32bit) so that generate the flash configure block, and ROM can initialize the flash by these configure block information, so it requires to fill the flash configuration information in bd file, for example:

Figure 5. Hyperflash configure in bd file Enhanced Features in i.MX RT1060, Application Notes, Rev. 0, 09/2018 While RT1060 ROM implement the auto-probe function, which can automatically probe the flash type and get the parameters without above configure information in bd file, and configure flash without user's input once enable the auto-probe function.

Auto probe function can be enabled with below two ways.

• Program eFUSE

Program the bit fuse "FLASH\_AUTO\_PROBE\_EN" to enable eFUSE, and also need to program eFUSE bit "BT\_FUSE\_SEL" to enable boot mode configuration by fuses.

Also it determine the flash type by BOOT\_CFG1[3:2].

- ➢ 00 QuadSPI NOR

- ➢ 01 Macronix Octal FLASH

- > 10 Micron Octal FLASH

- 11 Adesto Octal FLASH

- Enable it by level of configure pins.

When eFUSE bit "BT\_FUSE\_SEL" is 0, keep the pin "GPIO\_B0\_04" to high to enable auto-probe function.

Similarly, it determine flash type by status of GPIO "GPIO\_B0\_6" and "GPIO\_B0\_7".

#### 3.5.2. Flash Remapping Setting

The ROM of i.MXRT1060 support the flash remapping feature and allow user to download two firmware to flash, also provide the API for user to switch firmware easily.

To enable flash remapping function, need to blow the below fuse bit..

| Module                   | Address          | 7                                                                                                                        | 6                                                    | 5                                                   | 4                                                                        | 3                                              | 2                                                                                                | 1                                                                              | 0 |

|--------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---|

| FlexSPI<br>1 -<br>Serial | 0x6E0[7:0]       | FLEXSPI_RESET_PIN_E<br>N<br>0 - Disabled<br>1 - Enabled                                                                  | JEDEC_HW_RESET_E<br>N<br>0 - Disabled<br>1 - Enabled | FLA<br>HC<br>TII<br>0<br>500<br>1 -<br>2 - 3<br>/ 3 | SPI<br>ASH<br>PLD<br>ME<br>-<br>Juss /<br>1ms<br>3ms<br>3ms<br>3 -<br>ms | FRE<br>0 -<br>1 -<br>2 -<br>3 -1<br>- F<br>5 - | BOOT<br>100M<br>120M<br>133M<br>66MH<br>Reserv                                                   | UENCY<br>0MHz /<br>0MHz / SIP_TEST<br>3MHz / N<br>MHz / 4<br>served<br>MHz / 6 |   |

| NOR                      | 0x6E0[15:8]      | <b>xSPI FLASH IMAGE SIZE</b><br>0-FLEXSPI_NOR_SEC_IMAGE_OFFSET*256KB<br>1-12: 1MB-12MB<br>13 - 256KB, 14-512KB, 15-768KB |                                                      |                                                     |                                                                          |                                                | xSPI FLASH DUMMY CYCLE<br>0 - Auto probe<br>Others - Dummy cycles (for<br>example, 8 - 8 cycles) |                                                                                |   |

|                          | 0x6E0[23:1<br>6] | FLEXSPI_NOR_SEC_IMAGE_OFFSET[7:0]<br>Actual offset = 256KB * fuse value                                                  |                                                      |                                                     |                                                                          |                                                |                                                                                                  |                                                                                |   |

Table 6. Fuse definition of FlexSPI1

0x6E0[23:16] specify the offset value of flash remap, when it is not 0, flash remapping is enable. For example, if image size is about 512 KB, fuse setting as below:

• 0x6E0[23:16] set to 2, 0x6E0[15:12] to 0.

User can switch firmware in their application code by calling API function, ROM open the API function for easy to use.

Below is bootloader API entry structure for reference:

```

typedef struct

ł

const uint32 t version;

//!< Bootloader version

number

//!< Bootloader Copyright

const char *copyright;

//!< Function to start the

void (*runBootloader)(void *arg);

bootloader executing

const uint32 t *reserved0;

//!< Reserved

const flexspi_nor_driver_interface_t *flexSpiNorDriver; //!< FlexSPI NOR Flash API</pre>

const uint32 t *reserved1;

//!< Reserved

const clock driver interface t *clockDriver;

const rtwdog driver interface t *rtwdogDriver;

const wdog driver interface t *wdogDriver;

const uint32 t *reserved2;

} bootloader_api_entry_t;

```

User can call these API functions by API entry address 0x0020001c.

One example as below:

g bootloaderTree = (bootloader api entry t \*)\*(uint32 t \*)0x0020001c;

and also bootloader argument parameter as below:

#### Revision history

```

typedef union

{

struct

{

uint32_t imageIndex : 4;

uint32_t reserved : 12;

uint32_t serialBootInterface : 4;

uint32_t bootMode : 4;

uint32_t tag : 8;

} B;

uint32_t U;

} run_bootloader_ctx_t;

```

"imageIndex" define which image is be remapping to run.

One example as below:

user can easily change firmware to run by specified firmware index.

# 4. Conclusion

This document introduces the enhanced features of RT1060 and also discusses the difference with RT1050. It also provide the guidelines on how to use these new features. The objective of this document is to help customers in learning i.MX RT1060 to use it well.

# 5. Revision history

| Revision number | Date    | Substantive changes |

|-----------------|---------|---------------------|

| 0               | 09/2018 | Initial release     |

|                 |         |                     |

Revision history

#### How to Reach Us:

Home Page: nxp.com

Web Support: nxp.com/support Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals", must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer's applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners, AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big,LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamIQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2018 NXP B.V.

Document Number: AN12240 Rev. 0 09/2018

# arm