## i.MX53 EVK Linux

Reference Manual

Part Number: 924-76374

Rev.10.10.01

10/2010

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc.

Technical Information Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

1-800-521-6274 or

+1-480-768-2130

www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd.

Exchange Building 23F

No. 118 Jianguo Road

Chaoyang District

Beijing 100022

China

+86 10 5879 8000

support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor

Literature Distribution Center

1-800 441-2447 or

+1-303-675-2140

Fax: +1-303-675-2150

LDCForFreescaleSemiconductor

@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale and the Freescale logo are trademarks or registered trademarks of Freescale Semiconductor, Inc. in the U.S. and other countries. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc., 2004-2010. All rights reserved.

## **Contents**

|  | Δ | ha | tuc | Th | is | Bo | οk |

|--|---|----|-----|----|----|----|----|

|--|---|----|-----|----|----|----|----|

|                | Audience                                                            |     |

|----------------|---------------------------------------------------------------------|-----|

|                | Definitions, Acronyms, and Abbreviations                            | ix  |

| Chap<br>Introd | ter 1<br>duction                                                    |     |

| 1.1<br>1.2     | Software Base                                                       |     |

| Chap<br>Archi  | ter 2<br>tecture                                                    |     |

| 2.1            | Linux BSP Block Diagram                                             |     |

| 2.2<br>2.2.1   | Kernel2Kernel Configuration2                                        |     |

| 2.2.1          | Machine Specific Layer (MSL)                                        |     |

| 2.2.2.1        |                                                                     |     |

| 2.2.2.2        |                                                                     |     |

| 2.2.2.3        | ±                                                                   |     |

| 2.2.2.4        |                                                                     |     |

| 2.2.2.5        | Callback mechanism at the end of script executionInput/Output (I/O) | -4  |

| 2.2.2.6        | Shared Peripheral Bus Arbiter (SPBA)                                | -5  |

| 2.3            | Drivers                                                             |     |

| 2.3.1          | Universal Asynchronous Receiver/Transmitter (UART) Driver           | 5   |

| 2.3.1.1        |                                                                     |     |

| 2.3.2          | Real-Time Clock (RTC) Driver                                        |     |

| 2.3.3          | Watchdog Timer (WDOG) Driver                                        |     |

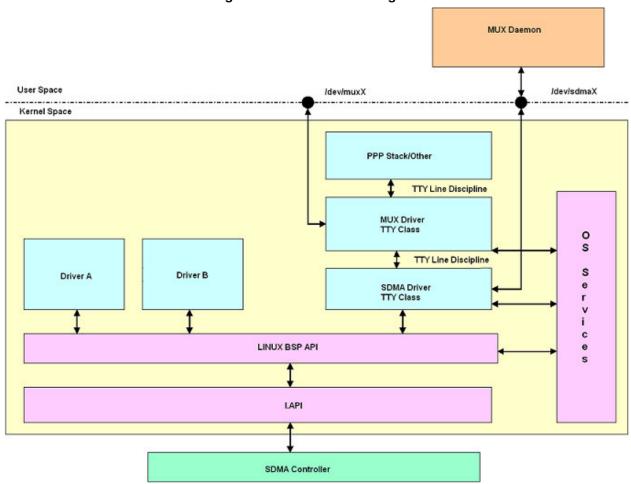

| 2.3.4          | SDMA API Driver                                                     |     |

| 2.3.5          | Image Processing Unit (IPU) Driver                                  |     |

| 2.3.6          | Video for Linux 2 (V4L2) Driver                                     |     |

| 2.3.7          | Figure 2-2Figure 2-2 Sound Driver                                   |     |

| 2.3.8          | Memory Technology Device (MTD) Driver                               |     |

| 2.3.8.1        | NAND MTD Driver                                                     |     |

| 2.3.8.2        | SPI-NOR MTD driver                                                  | ,-9 |

| 2.3.9    | Networking Drivers                                     | 2-9    |

|----------|--------------------------------------------------------|--------|

| 2.3.9.1  | FEC driver                                             | 2-9    |

| 2.3.10   | USB Driver                                             | 2-9    |

| 2.3.10.1 | USB Host-Side API Model                                | 2-9    |

| 2.3.10.2 | $\boldsymbol{\mathcal{C}}$                             |        |

| 2.3.10.3 | USB OTG Framework                                      | . 2-10 |

| 2.3.11   | General Drivers                                        |        |

| 2.3.11.  | MMC/SD Host Driver                                     | . 2-11 |

| 2.3.11.2 | Inter-IC (I2C) Bus Driver                              | . 2-11 |

| 2.3.11.3 | Configurable Serial Peripheral Interface (CSPI) Driver | . 2-12 |

| 2.3.11.4 | Dynamic Power Management (DPM) Driver                  | . 2-12 |

| 2.3.11.5 | Low-Level Power Management Driver                      | . 2-14 |

| 2.3.11.6 | Dynamic Voltage and Frequency Scaling (DVFS) Driver    | . 2-14 |

| 2.4      | Boot Loaders                                           | . 2-14 |

| Chapt    | er 3<br>ine Specific Layer (MSL)                       |        |

|          |                                                        |        |

|          | Interrupts                                             |        |

| 3.1.1    | Interrupt Hardware Operation                           |        |

| 3.1.2    | Interrupt Software Operation                           |        |

| 3.1.3    | Interrupt Features                                     |        |

| 3.1.4    | Interrupt Source Code Structure                        |        |

| 3.1.5    | Interrupt Programming Interface                        |        |

|          | Timer                                                  |        |

| 3.2.1    | Timer Hardware Operation                               |        |

| 3.2.2    | Timer Software Operation                               |        |

| 3.2.3    | Timer Features                                         |        |

| 3.2.4    | Timer Source Code Structure                            |        |

|          | Memory Map                                             |        |

| 3.3.1    | Memory Map Hardware Operation                          |        |

| 3.3.2    | Memory Map Software Operation                          |        |

| 3.3.3    | Memory Map Features                                    |        |

| 3.3.4    | Memory Map Source Code Structure                       |        |

| 3.3.5    | Memory Map Programming Interface                       |        |

|          | IOMUX                                                  |        |

| 3.4.1    | IOMUX Hardware Operation                               |        |

| 3.4.2    | IOMUX Software Operation                               |        |

| 3.4.3    | IOMUX Features                                         |        |

| 3.4.4    | IOMUX Source Code Structure                            |        |

| 3.4.5    | IOMUX Programming Interface                            |        |

|          | General Purpose Input/Output(GPIO)                     |        |

| 3.5.1    | GPIO Software Operation                                |        |

| 3.5.1.1  | API for GPIO                                           |        |

| 3.5.2    | GPIO Features                                          | 1-7    |

| 3.5.3<br>3.5.4                                       | GPIO Source Code Structure                                                                                                                                                |                                 |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Chap<br>Smar                                         | ter 4<br>t Direct Memory Access (SDMA) API                                                                                                                                |                                 |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7        | Overview. Hardware Operation Software Operation. Source Code Structure Menu Configuration Options Programming Interface Usage Example.                                    | 2-1<br>2-1<br>2-3<br>2-3<br>2-4 |

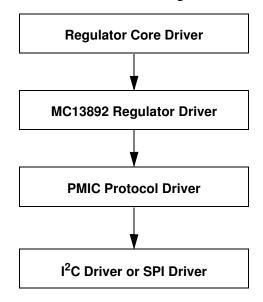

| Chap                                                 | ter 3<br>8892 Regulator Driver                                                                                                                                            |                                 |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8 | Hardware Operation  Driver Features  Software Operation  Regulator APIs  Driver Architecture  Driver Interface Details  Source Code Structure  Menu Configuration Options | 3-1<br>3-2<br>3-3<br>3-3<br>3-4 |

| Chap<br>MC13                                         | ter 4<br>8892 RTC Driver                                                                                                                                                  |                                 |

| 4.1<br>4.2<br>4.3<br>4.3.1<br>4.4<br>4.5             | Driver Features Software Operation Driver Implementation Details Driver Access and Control Source Code Structure Menu Configuration Options                               | 4-1<br>4-1<br>4-1<br>4-2        |

| Chap <sup>1</sup><br>MC13                            | ter 5<br>892 Digitizer Driver                                                                                                                                             |                                 |

| 5.1<br>5.2<br>5.3<br>5.4                             | Driver Features                                                                                                                                                           | 5-2<br>5-3                      |

| Chap<br>CPU                                             | ter 6<br>Frequency Scaling (CPUFREQ) Driver                                                                                                                                                                              |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.1<br>6.2<br>6.3<br>6.3.1                              | Software Operation 6-1 Source Code Structure 6-1 Menu Configuration Options 6-2 Board Configuration Options 6-2                                                                                                          |

| Chap<br>Low-l                                           | ter 7<br>evel Power Management (PM) Driver                                                                                                                                                                               |

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5                         | Hardware Operation7-1Software Operation7-1Source Code Structure7-2Menu Configuration Options7-2Programming Interface7-2                                                                                                  |

| Chap<br>Dyna                                            | ter 8<br>mic Voltage Frequency Scaling (DVFS) Driver                                                                                                                                                                     |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.4.1                       | Hardware Operation 8-1 Software Operation 8-1 Source Code Structure 8-1 Menu Configuration Options 8-2 Board Configuration Options 8-2                                                                                   |

| Chap<br>Softw                                           | ter 9<br>vare Based Peripheral Domain Frequency Scaling                                                                                                                                                                  |

| 9.1<br>9.1.1<br>9.1.2<br>9.1.3<br>9.2<br>9.3<br>9.3.1   | Software based Bus Frequency Scaling9-1Low Power Audio Playback Mode (LPAPM)9-1Medium Frequency setpoint9-2High Frequency setpoint9-2Source Code Structure9-2Menu Configuration Options9-2Board Configuration Options9-2 |

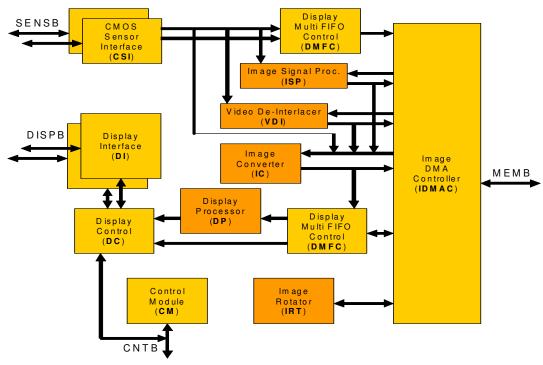

|                                                         | ter 10<br>e Processing Unit (IPU) Drivers                                                                                                                                                                                |

| 10.1<br>10.2<br>10.2.1<br>10.2.1.<br>10.2.1.<br>10.2.1. | 2 IPU Frame Buffer Software Operation                                                                                                                                                                                    |

vi i.MX53 EVK Linux Reference Manual

Freescale Semiconductor

| 10.4<br>10.5                                                                 | Menu Configuration Options                                                                                                           |                                              |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

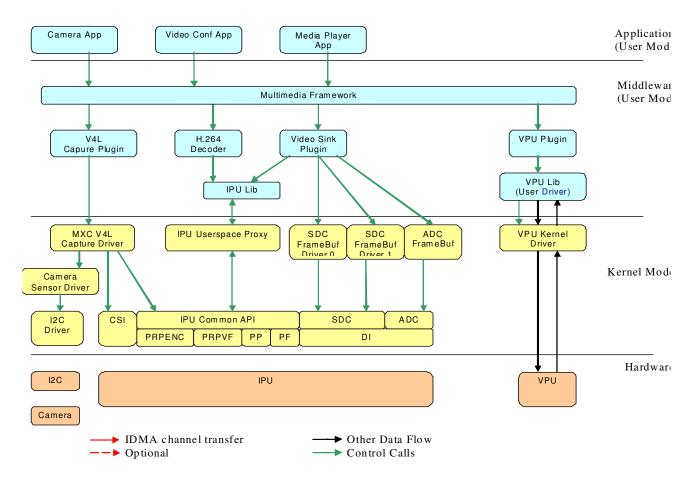

|                                                                              | eter 11<br>o for Linux Two (V4L2) Driver                                                                                             |                                              |

| 11.1<br>11.1.1<br>11.1.2<br>11.2<br>11.2.1<br>11.2.2<br>11.3<br>11.4<br>11.5 | V4L2 Capture IOCTLs Use of the V4L2 Capture APIs  V4L2 Output Device.  V4L2 Output IOCTLs.                                           | 11-2<br>11-4<br>11-5<br>11-5<br>11-6<br>11-6 |

|                                                                              | rter 12<br>6 Display Bridge(LDB) Driver                                                                                              |                                              |

| 12.1<br>12.2<br>12.3<br>12.4<br>12.5                                         | Hardware Operation Software Operation Source Code Structure Menu Configuration Options Programming Interface                         | 12-1<br>12-2<br>12-2                         |

| Chap<br>i.MX5                                                                | ter 13<br>5 Dual Display                                                                                                             |                                              |

| 13.1<br>13.2<br>13.3                                                         | Hardware Operation                                                                                                                   | 13-1                                         |

| Chap<br>Video                                                                | ter 14<br>Deprocessing Unit (VPU) Driver                                                                                             |                                              |

| 14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.6                                 | Hardware Operation Software Operation Source Code Structure Menu Configuration Options Programming Interface Defining an Application | 14-2<br>14-3<br>14-4<br>14-4                 |

| Chap<br>Grapl                                                                | ter 15<br>hics Processing Unit (GPU)                                                                                                 |                                              |

| 15.1<br>15.2                                                                 | Driver Features                                                                                                                      |                                              |

|                                                                              | i.MX53 EVK Linux Reference Manual                                                                                                    |                                              |

Freescale Semiconductor vii

| 15.3<br>15.4<br>15.5<br>15.6                                                           | Software Operation                                                                                                                                                                                                                              | 15-2<br>15-2                                         |

|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|                                                                                        | ter 16<br>ecoder (TV-In) Driver                                                                                                                                                                                                                 |                                                      |

| 16.1<br>16.2<br>16.3<br>16.4                                                           | Hardware Operation                                                                                                                                                                                                                              | 16-1<br>16-1                                         |

| Adva                                                                                   | ter 17<br>nced Linux Sound Architecture (ALSA)<br>em on a Chip (ASoC) Sound Driver                                                                                                                                                              |                                                      |

| 17.1<br>17.1.1<br>17.1.2<br>17.1.3<br>17.2<br>17.3<br>17.4<br>17.4.1<br>17.5<br>17.5.1 | SoC Sound Card Stereo Codec Features Multi-channel Codec Feature Sound Card Information ASoC Driver Source Architecture Menu Configuration Options Hardware Operation Stereo Audio Codec Software Operation Sound Card Registration Device Open | 17-2<br>17-3<br>17-3<br>17-5<br>17-6<br>17-6<br>17-7 |

|                                                                                        | ter 18<br>Sony/Philips Digital Interface (S/PDIF) Tx Driver                                                                                                                                                                                     |                                                      |

| 18.1<br>18.1.1<br>18.1.2<br>18.2<br>18.2.1<br>18.2.2<br>18.3<br>18.4                   | S/PDIF Overview  Hardware Overview  Software Overview  S/PDIF Tx Driver  Driver Design  Provided User Interface  Source Code Structure  Menu Configuration Options                                                                              | 18-2<br>18-2<br>18-3<br>18-3<br>18-4                 |

|                                                                                        | ter 19<br>IOR Flash Memory Technology Device (MTD) Driver                                                                                                                                                                                       |                                                      |

| 19.1<br>19.2<br>19.3                                                                   | Hardware Operation Software Operation Driver Features                                                                                                                                                                                           | 19-1                                                 |

|                                                                                        | i.MX53 EVK Linux Reference Manual                                                                                                                                                                                                               |                                                      |

Freescale Semiconductor

viii

| 19.4<br>19.5                                                         | Source Code Structure                                                                                                                                                                                                          |                                                      |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|                                                                      | ter 20<br>D Flash Memory Technology Device (MTD) Driver                                                                                                                                                                        |                                                      |

| 20.1<br>20.1.1<br>20.1.2<br>20.2<br>20.3<br>20.4<br>20.5             | Overview.  Hardware Operation  Software Operation.  Requirements  Source Code Structure  Linux Menu Configuration Options  Programming Interface  ter 21                                                                       | 20-1<br>20-2<br>20-2<br>20-2<br>20-2                 |

| SATA                                                                 | Driver                                                                                                                                                                                                                         |                                                      |

| 21.1<br>21.2<br>21.3<br>21.4<br>21.5<br>21.6<br>21.7<br>21.8         | Hardware Operation Software Operation Source Code Structure Configuration Linux Menu Configuration Options Board Configuration Options Programming Interface Usage Example Usage Example                                       | 21-1<br>21-1<br>21-1<br>21-1<br>21-2<br>21-2         |

| Chap <sup>e</sup><br>Low-l                                           | ter 22<br>Level Keypad Driver                                                                                                                                                                                                  |                                                      |

| 22.1<br>22.2<br>22.3<br>22.4<br>22.5<br>22.6<br>22.7<br>22.8<br>22.9 | Hardware Operation Software Operation Reassigning Keycodes Driver Features Implemented as a standard input deviceMX53 EVK Keypad Source Code Structure Menu Configuration Options Programming Interface Interrupt Requirements | 22-1<br>22-3<br>22-3<br>22-3<br>22-5<br>22-5<br>22-6 |

|                                                                      | ter 23<br>Ethernet Controller (FEC) Driver                                                                                                                                                                                     |                                                      |

| 23.1<br>23.2<br>23.3<br>23.4                                         | Hardware Operation                                                                                                                                                                                                             | 23-3<br>23-3                                         |

ix

Freescale Semiconductor

| 23.5<br>23.5.1<br>23.5.2                                                                     | Programming Interface                                                                                                                                                                                                                                      | 23-4                                                         |

|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Chap                                                                                         | ter 24<br>IC (I2C) Driver                                                                                                                                                                                                                                  |                                                              |

| 24.1<br>24.2<br>24.3                                                                         | I2C Bus Driver Overview                                                                                                                                                                                                                                    | 24-1                                                         |

| 24.4<br>24.4.1<br>24.4.2                                                                     | Software Operation                                                                                                                                                                                                                                         | 24-2                                                         |

| 24.5<br>24.6<br>24.7                                                                         | Driver Features                                                                                                                                                                                                                                            | 24-3<br>24-3                                                 |

| 24.8<br>24.9                                                                                 | Programming Interface                                                                                                                                                                                                                                      |                                                              |

| Confi                                                                                        | ter 25<br>gurable Serial Peripheral Interface (CSPI) Driver                                                                                                                                                                                                |                                                              |

| 25.1<br>25.2<br>25.2.1<br>25.2.2<br>25.2.3<br>25.2.4<br>25.3<br>25.4<br>25.5<br>25.6<br>25.7 | Hardware Operation  Software Operation  SPI Sub-System in Linux  Software Limitations.  Standard Operations  CSPI Synchronous Operation  Driver Features  Source Code Structure  Menu Configuration Options  Programming Interface  Interrupt Requirements | 25-1<br>25-3<br>25-3<br>25-4<br>25-4<br>25-4<br>25-4<br>25-5 |

| Chap<br>MMC                                                                                  | ter 26<br>/SD/SDIO Host Driver                                                                                                                                                                                                                             |                                                              |

| 26.1<br>26.2<br>26.3<br>26.4<br>26.5<br>26.6                                                 | Hardware Operation Software Operation Driver Features Source Code Structure Menu Configuration Options Programming Interface                                                                                                                               | 26-2<br>26-3<br>26-4<br>26-4                                 |

## Chapter 27 Universal Asynchronous Receiver/Transmitter (UART) Driver

| 27.1          | Hardware Operation                         | 27-1 |

|---------------|--------------------------------------------|------|

| 27.2          | Software Operation                         | 27-2 |

| 27.3          | Driver Features                            | 27-2 |

| 27.4          | Source Code Structure                      | 27-3 |

| 27.5          | Configuration                              | 27-3 |

| 27.5.1        | Menu Configuration Options                 | 27-3 |

| 27.5.2        | Source Code Configuration Options          | 27-4 |

| 27.5.2.       | 1 Chip Configuration Options               | 27-4 |

| 27.5.2.       | Board Configuration Options                | 27-4 |

| 27.6          | Programming Interface                      |      |

| 27.7          | Interrupt Requirements                     |      |

| 27.8          | Device Specific Information                | 27-5 |

| 27.8.1        | UART Ports                                 |      |

| 27.8.2        | Board Setup Configuration                  | 27-5 |

| 27.9          | Early UART Support                         | 27-7 |

| Chap<br>ARC   | ter 28<br>USB Driver                       |      |

| 28.1          | Architectural Overview                     | 28-2 |

| 28.2          | Hardware Operation                         | 28-2 |

| 28.3          | Software Operation                         | 28-2 |

| 28.4          | Driver Features                            |      |

| 28.5          | Source Code Structure                      | 28-4 |

| 28.6          | Menu Configuration Options                 | 28-5 |

| 28.7          | Programming Interface                      |      |

| 28.8          | Default USB Settings                       |      |

| 28.9          | Remote WakeUp                              |      |

| 28.10         | System WakeUp                              |      |

|               | USB Wakeup usage                           |      |

| 28.11.1       | , , , , , , , , , , , , , , , , , , ,      |      |

| 28.11.2       | 1 11                                       |      |

| 28.11.3       | How to close the usb child device power    | 28-9 |

| Chap<br>Secui | ter 29<br>re Real Time Clock (SRTC) Driver |      |

| 29.1          | Hardware Operation                         | 29-1 |

| 29.2          | Software Operation                         |      |

| 29.2.1        | IOCTL                                      |      |

| 29.2.2        | Keep Alive in the Power Off State          |      |

| 29.3          | Driver Features                            |      |

| 29.4          | Source Code Structure                      |      |

|               |                                            |      |

| 29.5                                                                                    | Menu Configuration Options                                                                                                                             | 29-2                                                         |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

|                                                                                         | ter 30<br>hdog (WDOG) Driver                                                                                                                           |                                                              |

| 30.1<br>30.2<br>30.3<br>30.3.1<br>30.3.2<br>30.3.3<br>30.3.4                            | Hardware Operation  Software Operation  Generic WDOG Driver  Driver Features  Menu Configuration Options  Source Code Structure  Programming Interface | 30-1<br>30-1<br>30-1<br>30-1<br>30-2                         |

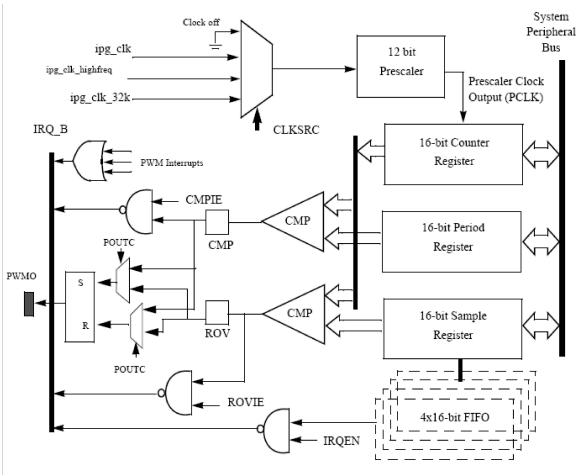

| Chap<br>Pulse                                                                           | ter 31<br>-Width Modulator (PWM) Driver                                                                                                                |                                                              |

| 31.1<br>31.2<br>31.3<br>31.4<br>31.5<br>31.6                                            | Hardware Operation  Clocks  Software Operation  Driver Features  Source Code Structure  Menu Configuration Options                                     | 31-2<br>31-2<br>31-3<br>31-3                                 |

|                                                                                         | ter 32<br>CAN Driver                                                                                                                                   |                                                              |

| 32.1<br>32.2<br>32.3<br>32.4<br>32.5                                                    | Driver Overview                                                                                                                                        | 32-1<br>32-1<br>32-2                                         |

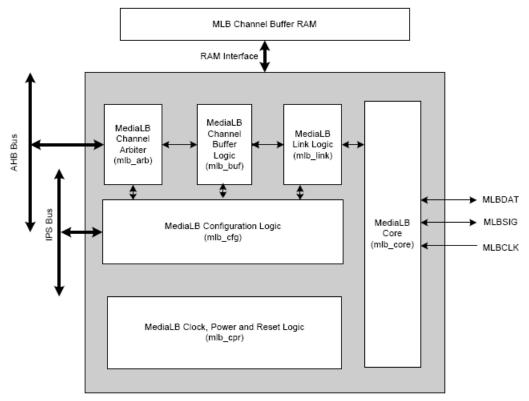

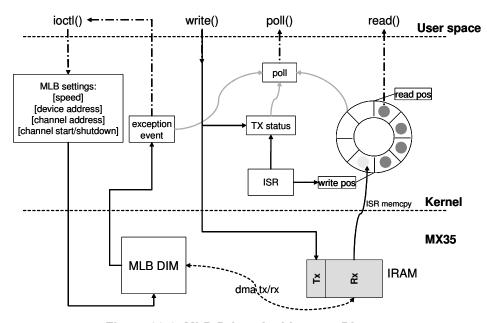

| Chap<br>Media                                                                           | ter 33<br>a Local Bus Driver                                                                                                                           |                                                              |

| 33.1<br>33.1.1<br>33.1.1.<br>33.1.2<br>33.2<br>33.2.1<br>33.2.2<br>33.2.3<br>33.3<br>33 | Tr                                                                                                                                                     | 33-1<br>33-2<br>33-2<br>33-2<br>33-2<br>33-3<br>33-4<br>33-5 |

xii Freescale Semiconductor

# Chapter 34 OProfile

| 34.1   | Overview                                            | 34-1 |

|--------|-----------------------------------------------------|------|

| 34.2   | Features                                            | 34-1 |

| 34.3   | Hardware Operation                                  | 34-1 |

| 34.4   | Software Operation                                  | 34-2 |

| 34.4.1 | Architecture Specific Components                    | 34-2 |

| 34.4.2 | oprofilefs Pseudo Filesystem                        | 34-2 |

| 34.4.3 | Generic Kernel Driver                               | 34-2 |

| 34.4.4 | OProfile Daemon                                     | 34-3 |

| 34.4.5 | Post Profiling Tools                                | 34-3 |

| 34.5   | Requirements                                        | 34-3 |

| 34.6   | Source Code Structure                               | 34-3 |

| 34.7   | Menu Configuration Options                          | 34-4 |

| 34.8   | Programming Interface                               | 34-4 |

| 34.9   | Interrupt Requirements                              | 34-4 |

| 34.10  | Example Software Configuration                      | 34-4 |

|        | ter 35<br>Jently Asked Questions                    |      |

| 35.1   | Downloading a File                                  | 35-1 |

| 35.2   | Creating a JFFS2 Mount Point                        | 35-1 |

| 35.3   | NFS Mounting Root File System                       | 35-2 |

| 35.4   | Error: NAND MTD Driver Flash Erase Failure          | 35-3 |

| 35.5   | Error: NAND MTD Driver Attempt to Erase a Bad Block | 35-3 |

| 35.6   | Using the Memory Access Tool                        | 35-3 |

| 35.7   | How to Make Software Workable when JTAG is Attached | 35-4 |

Freescale Semiconductor xiii

i.MX53 EVK Linux Reference Manual

xiv Freescale Semiconductor

## **Tables**

| 1-1  | Linux BSP Supported Features          | 1-2  |

|------|---------------------------------------|------|

| 2-1  | MSL Directories                       | 2-3  |

| 3-1  | Interrupt Files                       | 1-2  |

| 3-2  | Memory Map Files                      | 1-4  |

| 3-3  | IOMUX Files                           | 1-6  |

| 3-4  | GPIO Files                            | 1-7  |

| 4-1  | SDMA Channel Usage                    | 2-3  |

| 4-2  | SDMA API Source Files                 | 2-3  |

| 4-3  | SDMA Script Files                     | 2-3  |

| 3-1  | MC13892 Power Management Driver Files | 3-4  |

| 4-1  | MC9S08DZ60 RTC Driver Files           |      |

| 5-1  | MC13892 Digitizer Driver Files        | 5-3  |

| 6-1  | CPUFREQ Driver Files                  | 6-2  |

| 7-1  | Low Power Modes                       | 7-1  |

| 7-2  | PM Driver Files                       | 7-2  |

| 8-1  | DVFS Driver Files                     | 8-1  |

| 9-1  | Bus Frequency Scaling Driver Files    | 9-2  |

| 10-1 | IPU Driver Files                      |      |

| 10-2 | IPU Global Header Files               | 10-6 |

| 11-1 | V2L2 Driver Files                     | 11-6 |

| 13-1 |                                       | 13-1 |

| 14-1 | VPU Driver Files                      | 14-3 |

| 14-2 | VPU Library Files                     | 14-4 |

| 14-3 | VPU firmware Files                    | 14-4 |

| 15-1 | GPU Driver Files                      | 15-2 |

| 16-1 | TV-In Driver Source File              | 16-1 |

| 17-1 | Stereo Codec SoC Driver Files         | 17-5 |

| 17-2 | CS42888 ASoC Driver Source File       | 17-5 |

| 18-1 | S/PDIF Driver Files                   | 18-4 |

| 19-1 | SPI NOR MTD Driver Files              | 19-2 |

| 20-1 | NAND MTD Driver Files                 | 20-2 |

| 22-1 | Keypad Driver Files                   | 22-5 |

| 22-2 | Keypad Interrupt Timer Requirements   | 22-6 |

| 23-1 | Pin Usage in MIIRMII and SNI Modes    | 23-1 |

| 23-2 | FEC Driver Files                      |      |

| 24-1 | I2C Bus Driver Files                  | 24-3 |

| 24-2 | I2C Interrupt Requirements            | 24-3 |

| 25-1 | CSPI Driver Files                     |      |

|      |                                       |      |

| 25-2  | CSPI Interrupt Requirements              | 25-5 |

|-------|------------------------------------------|------|

| 26-1  | eSDHC Driver FilesMMC/SD Driver Files    |      |

| 27-1  | UART Driver Files                        | 27-3 |

| 27-2  | UART Global Header Files                 | 27-3 |

| 27-3  | UART Interrupt Requirements              | 27-5 |

| 27-4  | UART General Configuration               | 27-5 |

| 27-5  | UART Active/Inactive Configuration       | 27-5 |

| 27-6  | UART IRDA Configuration                  | 27-5 |

| 27-8  | UART Shared Peripheral Configuration     | 27-6 |

| 27-9  | UART Hardware Flow Control Configuration |      |

| 27-10 | UART DMA Configuration                   | 27-6 |

| 27-11 | UART DMA RX Buffer Size Configuration    | 27-6 |

| 27-12 | UART UCR4_CTSTL Configuration            |      |

| 27-13 | UART UFCR_RXTL Configuration             | 27-6 |

| 27-7  | UART Mode Configuration                  | 27-6 |

| 27-14 | UART UFCR_TXTL Configuration             | 27-7 |

| 27-15 | UART Interrupt Mux Configuration         | 27-7 |

| 27-16 | UART Interrupt 1 Configuration           |      |

| 27-17 | UART Interrupt 2 Configuration           | 27-7 |

| 27-18 | UART interrupt 3 Configuration           | 27-7 |

| 28-1  | USB Driver Files                         | 28-4 |

| 28-2  | USB Platform Source Files                | 28-4 |

| 28-3  | USB Platform Header Files                | 28-4 |

| 28-4  | USB Common Platform Files                | 28-5 |

| 28-5  | Default USB Settings                     | 28-7 |

| 29-1  | RTC Driver Files                         | 29-2 |

| 30-1  | WDOG Driver Files                        | 30-2 |

| 31-1  | PWM Driver Summary                       | 31-2 |

| 31-2  | PWM Driver Files                         | 31-3 |

| 32-1  | FlexCAN Driver Files                     | 32-2 |

| 33-1  | MLB Driver Source File List              | 33-5 |

| 34-1  | OProfile Source Files                    | 34-3 |

## **Figures**

| 2-1  | BSP Block Diagram                               | 2-1  |

|------|-------------------------------------------------|------|

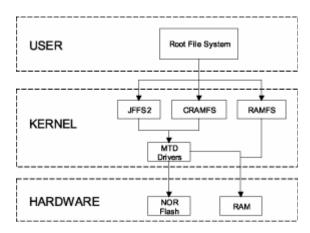

| 2-2  | MTD Architecture                                | 2-8  |

| 2-3  | DPM High Level Design                           | 2-13 |

| 2-4  | DPM Architecture Block Diagram                  | 2-13 |

| 4-1  | SDMA Block Diagram                              |      |

| 3-1  | MC13892 Regulator Driver Architecture           | 3-3  |

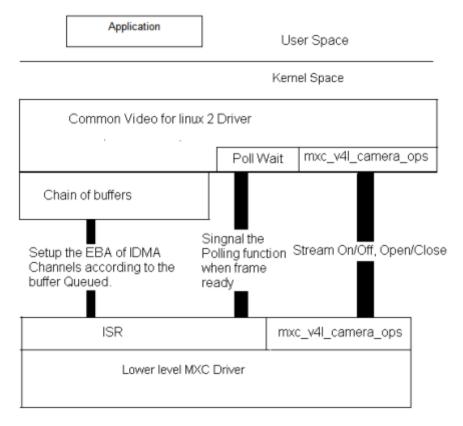

| 11-1 | Video4Linux2 Capture API Interaction            | 11-4 |

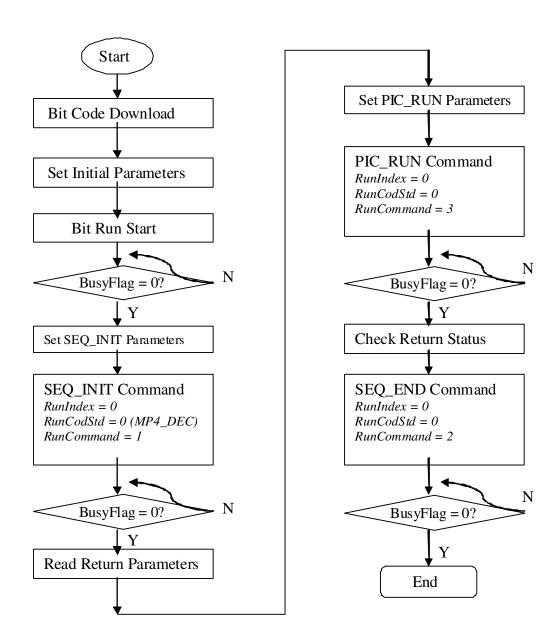

| 14-1 | VPU Hardware Data Flow                          |      |

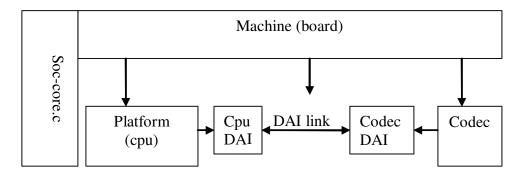

| 17-1 | ALSA SoC Software Architecture                  | 17-1 |

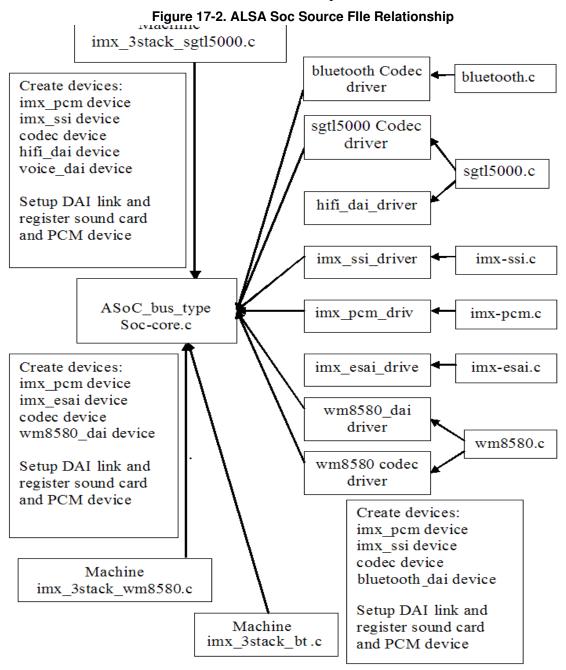

| 17-2 | ALSA Soc Source File Relationship               | 17-4 |

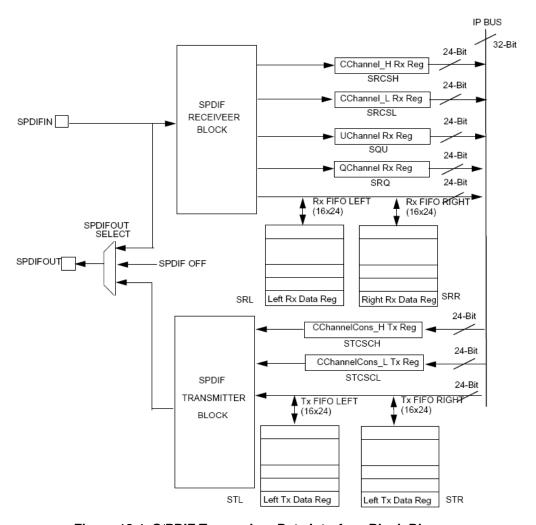

| 18-1 | S/PDIF Transceiver Data Interface Block Diagram | 18-1 |

| 19-1 | Components of a Flash-Based File System         | 19-1 |

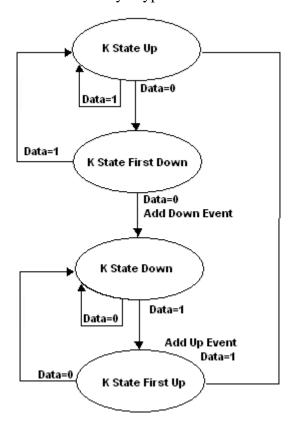

| 22-1 | Keypad Driver State Machine                     |      |

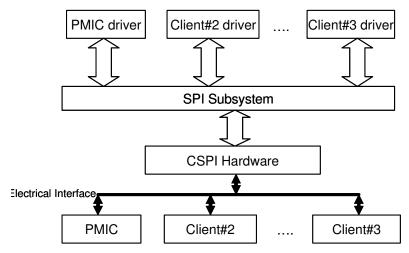

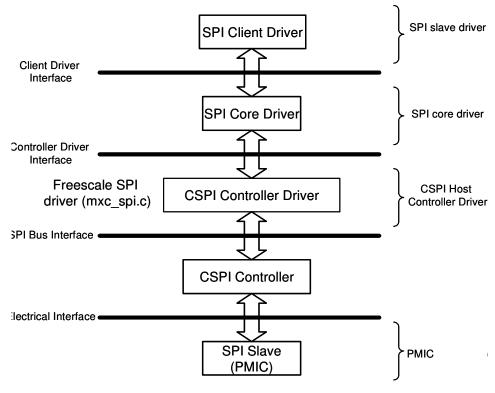

| 25-1 | SPI Subsystem                                   |      |

| 25-2 | Layering of SPI Drivers in SPI Subsystem        | 25-2 |

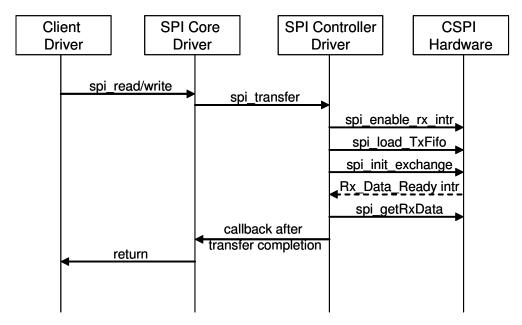

| 25-3 | CSPI Synchronous Operation                      |      |

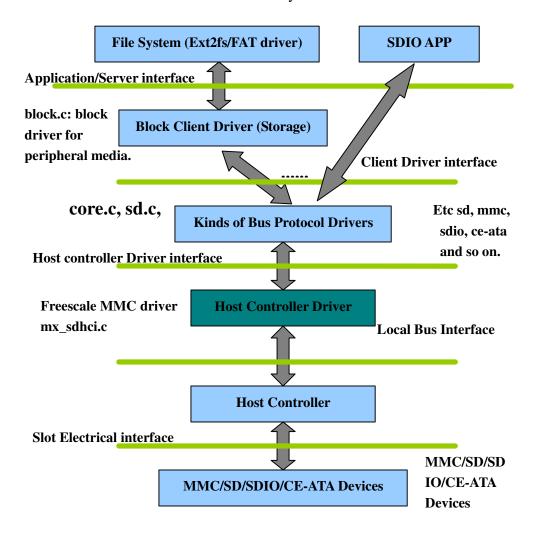

| 26-1 | MMC Drivers Layering                            |      |

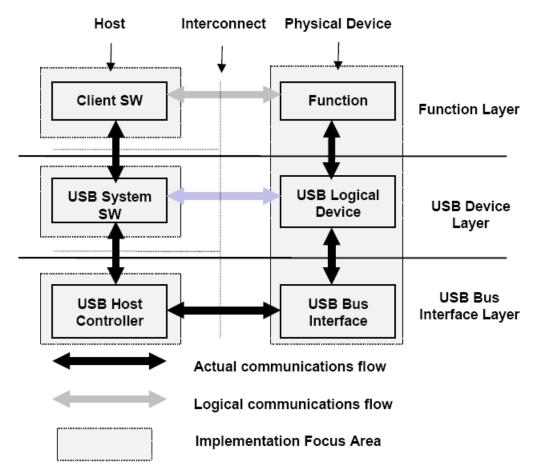

| 28-1 | USB Block Diagram                               |      |

| 31-1 | PWM Block Diagram                               | 31-1 |

| 33-1 | MLB Device Top-Level Block Diagram              | 33-1 |

| 33-2 | MLB Driver Architecture Diagram                 |      |

i.MX53 EVK Linux Reference Manual

xviii Freescale Semiconductor

## **About This Book**

The Linux Board Support Package (BSP) represents a porting of the Linux Operating System (OS) to the i.MX processors and its associated reference boards. The BSP supports many hardware features on the platforms and most of the Linux OS features that are not dependent on any specific hardware feature.

#### **Audience**

This document is targeted to individuals who will port the i.MX Linux BSP to customer-specific products. The audience is expected to have a working knowledge of the Linux 2.6 kernel internals, driver models, and i.MX processors.

## Conventions

This document uses the following notational conventions:

- Courier monospaced type indicate commands, command parameters, code examples, and file and directory names.

- *Italic* type indicates replaceable command or function parameters.

- **Bold** type indicates function names.

## **Definitions, Acronyms, and Abbreviations**

The following table defines the acronyms and abbreviations used in this document.

#### **Definitions and Acronyms**

| Term                   | Definition                                                                                                                                                               |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ADC                    | Asynchronous Display Controller                                                                                                                                          |  |

| address<br>translation | Address conversion from virtual domain to physical domain                                                                                                                |  |

| API                    | Application Programming Interface                                                                                                                                        |  |

| ARM <sup>®</sup>       | Advanced RISC Machines processor architecture                                                                                                                            |  |

| AUDMUX                 | Digital audio MUX—provides a programmable interconnection for voice, audio, and synchronous data routing between host serial interfaces and peripheral serial interfaces |  |

| BCD                    | Binary Coded Decimal                                                                                                                                                     |  |

| bus                    | A path between several devices through data lines                                                                                                                        |  |

| bus load               | The percentage of time a bus is busy                                                                                                                                     |  |

| CODEC                  | Coder/decoder or compression/decompression algorithm—used to encode and decode (or compress and decompress) various types of data                                        |  |

| CPU                    | Central Processing Unit—generic term used to describe a processing core                                                                                                  |  |

#### i.MX53 EVK Linux Reference Manual

Freescale Semiconductor xix

## **Definitions and Acronyms (continued)**

| Term       | Definition                                                                                                                                                                                                                                                                                                                                     |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CRC        | Cyclic Redundancy Check—Bit error protection method for data communication                                                                                                                                                                                                                                                                     |  |

| CSI        | Camera Sensor Interface                                                                                                                                                                                                                                                                                                                        |  |

| DFS        | Dynamic Frequency Scaling                                                                                                                                                                                                                                                                                                                      |  |

| DMA        | Direct Memory Access—an independent block that can initiate memory-to-memory data transfers                                                                                                                                                                                                                                                    |  |

| DPM        | Dynamic Power Management                                                                                                                                                                                                                                                                                                                       |  |

| DRAM       | Dynamic Random Access Memory                                                                                                                                                                                                                                                                                                                   |  |

| DVFS       | Dynamic Voltage Frequency Scaling                                                                                                                                                                                                                                                                                                              |  |

| EMI        | External Memory Interface—controls all IC external memory accesses (read/write/erase/program) from all the masters in the system                                                                                                                                                                                                               |  |

| Endian     | Refers to byte ordering of data in memory. Little endian means that the least significant byte of the data is stored in a lower address than the most significant byte. In big endian, the order of the bytes is reversed                                                                                                                      |  |

| EPIT       | Enhanced Periodic Interrupt Timer—a 32-bit set and forget timer capable of providing precise interrupts at regular intervals with minimal processor intervention                                                                                                                                                                               |  |

| FCS        | Frame Checker Sequence                                                                                                                                                                                                                                                                                                                         |  |

| FIFO       | First In First Out                                                                                                                                                                                                                                                                                                                             |  |

| FIPS       | Federal Information Processing Standards—United States Government technical standards published by the National Institute of Standards and Technology (NIST). NIST develops FIPS when there are compelling Federal government requirements such as for security and interoperability but no acceptable industry standards                      |  |

| FIPS-140   | Security requirements for cryptographic modules—Federal Information Processing Standard 140-2(FIPS 140-2) is a standard that describes US Federal government requirements that IT products should meet for Sensitive, but Unclassified (SBU) use                                                                                               |  |

| Flash      | A non-volatile storage device similar to EEPROM, where erasing can be done only in blocks or the entire chip.                                                                                                                                                                                                                                  |  |

| Flash path | Path within ROM bootstrap pointing to an executable Flash application                                                                                                                                                                                                                                                                          |  |

| Flush      | Procedure to reach cache coherency. Refers to removing a data line from cache. This process includes cleaning the line, invalidating its VBR and resetting the tag valid indicator. The flush is triggered by a software command                                                                                                               |  |

| GPIO       | General Purpose Input/Output                                                                                                                                                                                                                                                                                                                   |  |

| hash       | Hash values are produced to access secure data. A hash value (or simply hash), also called a message digest, is a number generated from a string of text. The hash is substantially smaller than the text itself, and is generated by a formula in such a way that it is extremely unlikely that some other text produces the same hash value. |  |

| I/O        | Input/Output                                                                                                                                                                                                                                                                                                                                   |  |

| ICE        | In-Circuit Emulation                                                                                                                                                                                                                                                                                                                           |  |

| IP         | Intellectual Property                                                                                                                                                                                                                                                                                                                          |  |

| IPU        | Image Processing Unit —supports video and graphics processing functions and provides an interface to video/still image sensors and displays                                                                                                                                                                                                    |  |

| IrDA       | Infrared Data Association—a nonprofit organization whose goal is to develop globally adopted specifications for infrared wireless communication                                                                                                                                                                                                |  |

| ISR        | Interrupt Service Routine                                                                                                                                                                                                                                                                                                                      |  |

## i.MX53 EVK Linux Reference Manual

xx Freescale Semiconductor

## **Definitions and Acronyms (continued)**

| Term                | Definition                                                                                                                                                                                                                                                                                                                                                              |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| JTAG                | JTAG (IEEE Standard 1149.1) A standard specifying how to control and monitor the pins of compliant devices on a printed circuit board                                                                                                                                                                                                                                   |  |

| Kill                | Abort a memory access                                                                                                                                                                                                                                                                                                                                                   |  |

| KPP                 | KeyPad Port—16-bit peripheral used as a keypad matrix interface or as general purpose input/output (I/O)                                                                                                                                                                                                                                                                |  |

| line                | Refers to a unit of information in the cache that is associated with a tag                                                                                                                                                                                                                                                                                              |  |

| LRU                 | Least Recently Used—a policy for line replacement in the cache                                                                                                                                                                                                                                                                                                          |  |

| MMU                 | Memory Management Unit—a component responsible for memory protection and address translation                                                                                                                                                                                                                                                                            |  |

| MPEG                | Moving Picture Experts Group—an ISO committee that generates standards for digital video compression and audio. It is also the name of the algorithms used to compress moving pictures and video                                                                                                                                                                        |  |

| MPEG<br>standards   | Several standards of compression for moving pictures and video:  • MPEG-1 is optimized for CD-ROM and is the basis for MP3  • MPEG-2 is defined for broadcast video in applications such as digital television set-top boxes and DVD  • MPEG-3 was merged into MPEG-2  • MPEG-4 is a standard for low-bandwidth video telephony and multimedia on the World-Wide Web    |  |

| MQSPI               | Multiple Queue Serial Peripheral Interface—used to perform serial programming operations necessary to configure radio subsystems and selected peripherals                                                                                                                                                                                                               |  |

| MSHC                | Memory Stick Host Controller                                                                                                                                                                                                                                                                                                                                            |  |

| NAND Flash          | Flash ROM technology—NAND Flash architecture is one of two flash technologies (the other being NOR) used in memory cards such as the Compact Flash cards. NAND is best suited to flash devices requiring high capacity data storage. NAND flash devices offer storage space up to 512-Mbyte and offers faster erase, write, and read capabilities over NOR architecture |  |

| NOR Flash           | See NAND Flash                                                                                                                                                                                                                                                                                                                                                          |  |

| PCMCIA              | Personal Computer Memory Card International Association—a multi-company organization that has developed a standard for small, credit card-sized devices, called PC Cards. There are three types of PCMCIA cards that have the same rectangular size (85.6 by 54 millimeters), but different widths                                                                      |  |

| physical<br>address | The address by which the memory in the system is physically accessed                                                                                                                                                                                                                                                                                                    |  |

| PLL                 | Phase Locked Loop—an electronic circuit controlling an oscillator so that it maintains a constant phase angle (a lock) on the frequency of an input, or reference, signal                                                                                                                                                                                               |  |

| RAM                 | Random Access Memory                                                                                                                                                                                                                                                                                                                                                    |  |

| RAM path            | Path within ROM bootstrap leading to the downloading and the execution of a RAM application                                                                                                                                                                                                                                                                             |  |

| RGB                 | The RGB color model is based on the additive model in which Red, Green, and Blue light are combined to create other colors. The abbreviation RGB comes from the three primary colors in additive light models                                                                                                                                                           |  |

| RGBA                | RGBA color space stands for Red Green Blue Alpha. The alpha channel is the transparency channel, and is unique to this color space. RGBA, like RGB, is an additive color space, so the more of a color placed, the lighter the picture gets. PNG is the best known image format that uses the RGBA color space                                                          |  |

| RNGA                | Random Number Generator Accelerator—a security hardware module that produces 32-bit pseudo random numbers as part of the security module                                                                                                                                                                                                                                |  |

| ROM                 | Read Only Memory                                                                                                                                                                                                                                                                                                                                                        |  |

#### i.MX53 EVK Linux Reference Manual

Freescale Semiconductor xxi

#### **Definitions and Acronyms (continued)**

| Term             | Definition                                                                                                                                                                                                                                                                                                                                                                                    |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ROM<br>bootstrap | Internal boot code encompassing the main boot flow as well as exception vectors                                                                                                                                                                                                                                                                                                               |  |

| RTIC             | Real-Time Integrity Checker—a security hardware module                                                                                                                                                                                                                                                                                                                                        |  |

| SCC              | SeCurity Controller—a security hardware module                                                                                                                                                                                                                                                                                                                                                |  |

| SDMA             | Smart Direct Memory Access                                                                                                                                                                                                                                                                                                                                                                    |  |

| SDRAM            | Synchronous Dynamic Random Access Memory                                                                                                                                                                                                                                                                                                                                                      |  |

| SoC              | System on a Chip                                                                                                                                                                                                                                                                                                                                                                              |  |

| SPBA             | Shared Peripheral Bus Arbiter—a three-to-one IP-Bus arbiter, with a resource-locking mechanism                                                                                                                                                                                                                                                                                                |  |

| SPI              | Serial Peripheral Interface—a full-duplex synchronous serial interface for connecting low-/medium-bandwidth external devices using four wires. SPI devices communicate using a master/slave relationship over two data lines and two control lines: Also see SS, SCLK, MISO, and MOSI                                                                                                         |  |

| SRAM             | Static Random Access Memory                                                                                                                                                                                                                                                                                                                                                                   |  |

| SSI              | Synchronous-Serial Interface—standardized interface for serial data transfer                                                                                                                                                                                                                                                                                                                  |  |

| TBD              | To Be Determined                                                                                                                                                                                                                                                                                                                                                                              |  |

| UART             | Universal Asynchronous Receiver/Transmitter—asynchronous serial communication to external devices                                                                                                                                                                                                                                                                                             |  |

| UID              | Unique ID-a field in the processor and CSF identifying a device or group of devices                                                                                                                                                                                                                                                                                                           |  |

| USB              | Universal Serial Bus—an external bus standard that supports high speed data transfers. The USB 1.1 specification supports data transfer rates of up to 12 Mb/s and USB 2.0 has a maximum transfer rate of 480 Mbps. A single USB port can be used to connect up to 127 peripheral devices, such as mice, modems, and keyboards. USB also supports Plug-and-Play installation and hot plugging |  |

| USBOTG           | USB On The Go—an extension of the USB 2.0 specification for connecting peripheral devices to each other. USBOTG devices, also known as dual-role peripherals, can act as limited hosts or peripherals themselves depending on how the cables are connected to the devices, and they also can connect to a host PC                                                                             |  |

| word             | A group of bits comprising 32-bits                                                                                                                                                                                                                                                                                                                                                            |  |

## **Suggested Reading**

The following documents contain information that supplements this guide:

- i.MX50\_RDP\_Linux\_BSP\_UserGuide.pdf

- MCIMX50 Multimedia Applications Processor Reference Manual (MCIMX50RM)

xxii Freescale Semiconductor

# Chapter 1 Introduction

The i.MX family Linux Board Support Package (BSP) supports the Linux Operating System (OS) on the following processor:

• i.MX53 Applications Processor

The purpose of this software package is to support Linux on the i.MX family of Integrated Circuits (ICs) and their associated platforms (EVK). It provides the necessary software to interface the standard open-source Linux kernel to the i.MX hardware. The goal is to enable Freescale customers to rapidly build products based on i.MX devices that use the Linux OS.

The BSP is not a platform or product reference implementation. It does not contain all of the product-specific drivers, hardware-independent software stacks, Graphical User Interface (GUI) components, Java Virtual Machine (JVM), and applications required for a product. Some of these are made available in their original open-source form as part of the base kernel.

The BSP is not intended to be used for silicon verification. While it can play a role in this, the BSP functionality and the tests run on the BSP do not have sufficient coverage to replace traditional silicon verification test suites.

#### 1.1 Software Base

The i.MX BSP is based on version 2.6.35.3 of the Linux kernel from the official Linux kernel web site (<a href="http://www.kernel.org">http://www.kernel.org</a>). It is enhanced with the features provided by Freescale.

Freescale Semiconductor

#### Introduction

## 1.2 Features

Table 1-1 describes the features supported by the Linux BSP for specific platforms.

**Table 1-1. Linux BSP Supported Features**