## **i.MX23 EVK 10.05 Linux**

Reference Manual

Document Number: 924-76389

Rev. 2010.05

05/2010

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc.

Technical Information Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

1-800-521-6274 or

+1-480-768-2130

www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor

Literature Distribution Center

1-800 441-2447 or

+1-303-675-2140

Fax: +1-303-675-2150

LDCForFreescaleSemiconductor

@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale and the Freescale logo are trademarks or registered trademarks of Freescale Semiconductor, Inc. in the U.S. and other countries. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc., 2010. All rights reserved.

## **Contents**

## **About This Book**

|                | Audience Conventions Definitions, Acronyms, and Abbreviations Suggested Reading | . vii<br>. vii |

|----------------|---------------------------------------------------------------------------------|----------------|

| Chap<br>Introd | ter 1<br>duction                                                                |                |

| 1.1<br>1.2     | Software Base                                                                   |                |

| Chap<br>Archi  | ter 2<br>tecture                                                                |                |

| 2.1            | Linux BSP Block Diagram                                                         | . 2-1          |

| 2.2            | Kernel                                                                          | . 2-2          |

| 2.2.1          | Kernel Configuration                                                            | . 2-2          |

| 2.2.2          | Machine Specific Layer (MSL)                                                    | . 2-3          |

| 2.2.2.1        | J 1                                                                             |                |

| 2.2.2.2        | 1                                                                               |                |

| 2.2.2.3        | , , , , , , , , , , , , , , , , , , ,                                           |                |

| 2.2.2.4        |                                                                                 |                |

| 2.2.2.5        | Input/Output (I/O)                                                              | . 2-4          |

| 2.2.2.6        | 5 · · · · · · · · · · · · · · · · · · ·                                         |                |

| 2.2.2.7        | 1 /                                                                             |                |

| 2.3            | Drivers                                                                         |                |

| 2.3.1          | Universal Asynchronous Receiver/Transmitter (UART) Driver                       |                |

| 2.3.1.1        | ~ · · · · · · · · · · · · · · · · · · ·                                         |                |

| 2.3.1.2        | Application Asynchronous Receiver/Transmitter (UART)                            | . 2-6          |

| 2.3.2          | Real-Time Clock (RTC) Driver                                                    | . 2-6          |

| 2.3.3          | Watchdog Timer (WDOG) Driver                                                    | . 2-6          |

| 2.3.4          | DCP                                                                             | . 2-7          |

| 2.3.5          | i.MX23 Graphics                                                                 | . 2-7          |

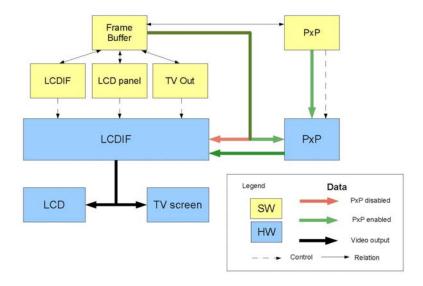

| 2.3.5.1        | LCDIF Driver                                                                    | . 2-8          |

| 2.3.5.2        | LCD Panel Drivers                                                               | . 2-8          |

| 2.3.5.3        | Frame Buffer Driver                                                             | . 2-8          |

| 2.3.5.4        | Pixel Pipeline (PXP) Driver                                                     | . 2-8          |

| 2.3.6          | Sound Driver                                                                    | . 2-8          |

| 2.3.7          | Keypad                                                                          | . 2-8          |

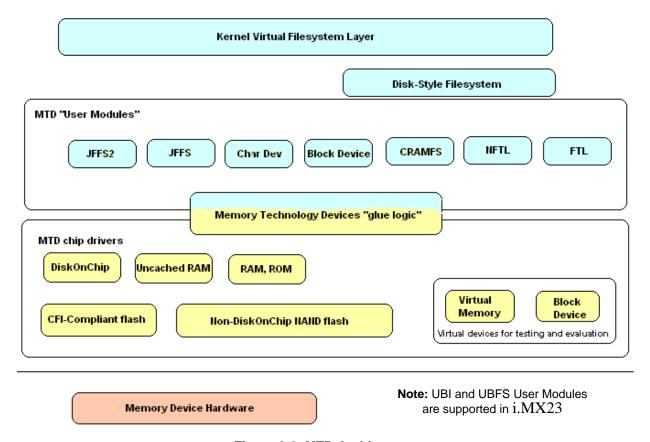

| 2.3.8          | Memory Technology Device (MTD) Driver                                           | . 2-9          |

| 2.3.8.1        | GPMI/NAND                                                                       | 2-10           |

| 2.3.9          | USB Driver                                                                      | 2-10           |

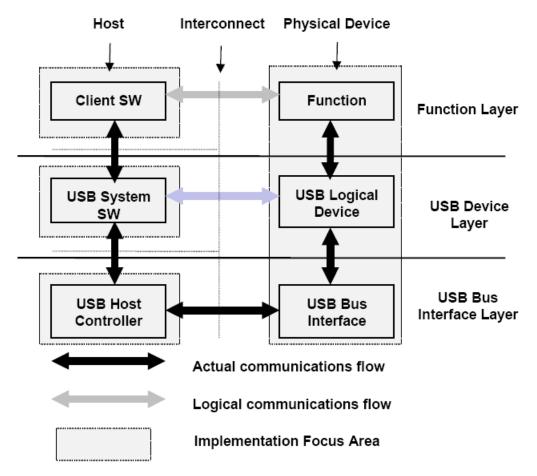

| 2.3.9.1        | USB Host-Side API Model                                                         | 2-10           |

| 2.3.9.2        | USB Device-Side Gadget Framework                                                | 2-11           |

| 2.3.9.3   | USB OTG Framework                                   | 2-11  |

|-----------|-----------------------------------------------------|-------|

| 2.3.10    | General Drivers                                     |       |

| 2.3.10.1  | MMC/SD Host Driver                                  | 2-12  |

| 2.3.10.2  | Inter-IC (I2C) Bus Driver                           | 2-12  |

| 2.3.10.3  | SPI Bus Driver                                      | 2-13  |

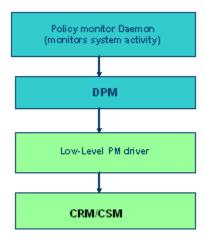

| 2.3.10.4  | Dynamic Power Management (DPM) Driver               | 2-13  |

| 2.3.10.5  | Low-Level Power Management Driver                   | 2-14  |

| 2.3.10.6  | Dynamic Voltage and Frequency Scaling (DVFS) Driver | 2-15  |

| 2.3.10.7  | Backlight Driver                                    | 2-15  |

| 2.3.10.8  | LED Driver                                          | 2-15  |

| 2.3.10.9  | Power Source Manager and Battery Charger            | 2-15  |

| 2.3.10.10 | CPUFreq Driver                                      | 2-16  |

| 2.4 Bo    | ot Loaders                                          | 2-16  |

| 2.4.1     | i.MX23 Boot Loader                                  | 2-16  |

| 2.4.1.1   | Boot Prep                                           | 2-17  |

| 2.4.1.2   | Linux Prep                                          | 2-17  |

| 2.4.1.3   | U-boot                                              | 2-17  |

|           |                                                     |       |

| Chapter   |                                                     |       |

| Machine   | Specific Layer (MSL)                                |       |

| 21 1      |                                                     | 2 1   |

|           | errupts                                             |       |

| 3.1.1     | Interrupt Hardware Operation.                       |       |

| 3.1.2     | Interrupt Software Operation                        |       |

| 3.1.3     | Interrupt Source Code Structure                     |       |

| 3.1.4     | Interrupt Programming Interface                     |       |

|           | mer                                                 |       |

| 3.2.1     | Timer Hardware Operation                            |       |

| 3.2.2     | Timer Software Operation                            |       |

| 3.2.3     | Timer Features                                      |       |

| 3.2.4     | Timer Source Code Structure                         |       |

| 3.2.5     | Timer Programming Interface                         |       |

|           | emory Map                                           |       |

| 3.3.1     | Memory Map Hardware Operation                       |       |

| 3.3.2     | Memory Map Software Operation                       |       |

| 3.3.3     | Memory Map Features                                 |       |

| 3.3.4     | Memory Map Source Code Structure                    |       |

| 3.3.5     | Memory Map Programming Interface                    |       |

|           | Multiplexing                                        |       |

| 3.4.1     | Pin Multiplexing Hardware Operation                 |       |

| 3.4.2     | Pin Multiplexing Software Operation                 |       |

| 3.4.3     | Pin Multiplexing Source Code Structure              |       |

| 3.4.4     | Pin Multiplexing Programming Interface              |       |

| 3.4.5     | GPIO With Pin Multiplexing                          | . 3-6 |

|           |                                                     |       |

-iv Freescale Semiconductor

| Chap<br>Direc                   | ter 4<br>t Memory Access Controller (DMAC) API                                                                          |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 4.1<br>4.2<br>4.3<br>4.4        | Hardware Operation 4-1 Software Operation 4-2 Source Code Structure 4-2 Programming Interface 4-2                       |

| Chap<br>Persi                   | ter 5<br>stent Bits Driver                                                                                              |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5 | Hardware Operation5-1Software Operation5-1Source Code Structure5-2Menu Configuration Options5-2Programming Interface5-2 |

| Chap<br>Uniqu                   | iter 6<br>ue ID on Boot Media                                                                                           |

| 6.1<br>6.2<br>6.3<br>6.4        | Software Operation6-1Programming Interface6-1Source Code Structure6-1Menu Configuration Options6-2                      |

| Chap<br>CPU                     | ter 7 Frequency Scaling (CPUFREQ) Driver                                                                                |

| 7.1<br>7.2<br>7.3<br>7.3.1      | Software Operation7-1Source Code Structure7-1Menu Configuration Options7-2Board Configuration Options7-2                |

| Chap<br>i.MX2                   | ter 8<br>23/I.MX28 Static Power Management Driver                                                                       |

| 8.1<br>8.2<br>8.3<br>8.4        | Hardware Operation                                                                                                      |

| Chap<br>Fram                    | ter 9<br>e Buffer Driver                                                                                                |

Software Operation9-1Menu Configuration Options9-2

9.19.2

9.3

| 9.4                                                                                                        | Source Code Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -2                               |

|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|                                                                                                            | ter 10<br>Interface (LCDIF) Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |

| 10.1<br>10.2<br>10.3<br>10.4<br>10.5                                                                       | Hardware Operation10-Software Operation10-Source Code Structure10-Menu Configuration Options10-Programming Interface10-                                                                                                                                                                                                                                                                                                                                                                          | -1<br>-1<br>-2                   |

| Chap<br>Back                                                                                               | ter 11<br>light Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                  |

| 11.1<br>11.2<br>11.3<br>11.4                                                                               | Hardware Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -1<br>-1                         |

| Adva                                                                                                       | ter 12<br>nced Linux Sound Architecture (ALSA)<br>em on a Chip (ASoC) Sound Driver                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |

| 12.1<br>12.1.1<br>12.1.2<br>12.1.3<br>12.2<br>12.3<br>12.4<br>12.4.1<br>12.4.2<br>12.5<br>12.5.1<br>12.5.2 | SoC Sound Card       12-         Stereo Codec Features       12-         Built-in ADC/DAC Audio Codec Features       12-         Sound Card Information       12-         ASoC Driver Source Architecture       12-         Menu Configuration Options       12-         Hardware Operation       12-         Stereo Audio Codec       12-         Built-in ADC/DAC Codec       12-         Software Operation       12-         Sound Card Registration       12-         Device Open       12- | -2<br>-3<br>-5<br>-5<br>-6<br>-6 |

|                                                                                                            | ter 13<br>Pipeline (PxP) Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                  |

| 13.1<br>13.2<br>13.3<br>13.4                                                                               | Hardware Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -1<br>-2                         |

-vi Freescale Semiconductor

## Chapter 14 NAND Flash Driver

| 14.1                                                                                | Hardware Operation                                                                                                                                                         | 14-1                                                                 |

|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 14.2                                                                                | Software Operation                                                                                                                                                         | 14-1                                                                 |

| 14.2.1                                                                              | Basic Operations: Read/Write                                                                                                                                               | 14-1                                                                 |

| 14.2.2                                                                              | Error Correction                                                                                                                                                           | 14-2                                                                 |

| 14.2.3                                                                              | Boot Control Block Management                                                                                                                                              | 14-2                                                                 |

| 14.2.4                                                                              | Bad Block Handling                                                                                                                                                         | 14-2                                                                 |

| 14.3                                                                                | Source Code Structure                                                                                                                                                      | 14-3                                                                 |

| 14.4                                                                                | Menu Configuration Options                                                                                                                                                 | 14-3                                                                 |

| Chap<br>ENET                                                                        | ter 15<br>· IEEE-1588 Driver                                                                                                                                               |                                                                      |

|                                                                                     |                                                                                                                                                                            | 15 1                                                                 |

| 15.1<br>15.1.1                                                                      | Hardware Operation                                                                                                                                                         |                                                                      |

| 15.1.1                                                                              | Transmit Timestamping                                                                                                                                                      |                                                                      |

| 15.1.2                                                                              | Receive Timestamping                                                                                                                                                       |                                                                      |

| 15.2                                                                                | Software Operation                                                                                                                                                         |                                                                      |

| 15.4                                                                                | Linux Menu Configuration Options                                                                                                                                           |                                                                      |

| 15.4                                                                                | Programming Interface                                                                                                                                                      |                                                                      |

| 15.5.1                                                                              | IXXAT Specific Data structure Defines                                                                                                                                      |                                                                      |

| 15.5.2                                                                              | IXXAT IOCTL Commands Defines.                                                                                                                                              |                                                                      |

|                                                                                     |                                                                                                                                                                            |                                                                      |

| Progi                                                                               | ter 16<br>rammable 3-Port Ethernet Switch Driver                                                                                                                           |                                                                      |

| <b>Prog</b> i<br>16.1                                                               | Tammable 3-Port Ethernet Switch Driver  Hardware Operation                                                                                                                 |                                                                      |

| <b>Prog</b> i<br>16.1<br>16.1.1                                                     | Hardware Operation                                                                                                                                                         | 16-3                                                                 |

| Progi<br>16.1<br>16.1.1<br>16.1.2                                                   | Hardware Operation                                                                                                                                                         | 16-3<br>16-3                                                         |

| Progr<br>16.1<br>16.1.1<br>16.1.2<br>16.2                                           | Hardware Operation                                                                                                                                                         | 16-3<br>16-3<br>16-4                                                 |

| 16.1<br>16.1.1<br>16.1.2<br>16.2<br>16.3                                            | Hardware Operation Passthrough Mode. Switch Mode. Software Operation. Source Code Structure                                                                                | 16-3<br>16-3<br>16-4<br>16-4                                         |

| Progr<br>16.1<br>16.1.1<br>16.1.2<br>16.2<br>16.3<br>16.4                           | Hardware Operation Passthrough Mode. Switch Mode Software Operation Source Code Structure Linux Menu Configuration Options                                                 | 16-3<br>16-3<br>16-4<br>16-4<br>16-5                                 |

| Progr<br>16.1<br>16.1.1<br>16.1.2<br>16.2<br>16.3<br>16.4<br>16.5                   | Hardware Operation Passthrough Mode. Switch Mode. Software Operation. Source Code Structure Linux Menu Configuration Options Programming Interface.                        | 16-3<br>16-4<br>16-4<br>16-5<br>16-5                                 |

| Progr<br>16.1<br>16.1.1<br>16.1.2<br>16.2<br>16.3<br>16.4<br>16.5<br>16.5.1         | Hardware Operation Passthrough Mode. Switch Mode Software Operation Source Code Structure Linux Menu Configuration Options Programming Interface Device Specific Defines   | 16-3<br>16-4<br>16-4<br>16-5<br>16-5                                 |

| Progr<br>16.1<br>16.1.1<br>16.1.2<br>16.2<br>16.3<br>16.4<br>16.5<br>16.5.1<br>Chap | Hardware Operation Passthrough Mode. Switch Mode. Software Operation. Source Code Structure Linux Menu Configuration Options Programming Interface.                        | 16-3<br>16-4<br>16-4<br>16-5<br>16-5                                 |

| Progr<br>16.1<br>16.1.1<br>16.1.2<br>16.2<br>16.3<br>16.4<br>16.5<br>16.5.1<br>Chap | Hardware Operation Passthrough Mode. Switch Mode. Software Operation. Source Code Structure Linux Menu Configuration Options Programming Interface Device Specific Defines | 16-3<br>16-4<br>16-4<br>16-5<br>16-5<br>17-1<br>17-1<br>17-1<br>17-2 |

Freescale Semiconductor -vii

| 17.7<br>17.8                                                                             | Programming Interface                                                                                                                                                                                                                                                         |                                                      |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|                                                                                          | ter 18<br>h Screen and ADC Drivers                                                                                                                                                                                                                                            |                                                      |

| 18.1<br>18.2<br>18.3<br>18.4<br>18.5<br>18.6<br>18.7                                     | Driver Overview .  Hardware Operation .  Software Operation .  Source Code Structure .  Menu Configuration Options .  Programming Interface (Exported API) .  Interrupt Requirements .                                                                                        | 18-1<br>18-2<br>18-2<br>18-2<br>18-2                 |

| Chap<br>Inter-                                                                           | ter 19<br>IC (I2C) Driver                                                                                                                                                                                                                                                     |                                                      |

| 19.1<br>19.2<br>19.3<br>19.4<br>19.4.1<br>19.4.2<br>19.5<br>19.6<br>19.7<br>19.8<br>19.9 | I2C Bus Driver Overview I2C Device Driver Overview Hardware Operation Software Operation I2C Bus Driver Software Operation I2C Device Driver Software Operation Driver Features Source Code Structure Menu Configuration Options Programming Interface Interrupt Requirements | 19-1<br>19-2<br>19-2<br>19-2<br>19-3<br>19-3<br>19-3 |

|                                                                                          | ter 20<br>Co-Processor (DCP) Driver                                                                                                                                                                                                                                           |                                                      |

| 20.1<br>20.2<br>20.3<br>20.4<br>20.5                                                     | Hardware Operation Software Operation Source Code Structure Menu Configuration Options Programming Interface                                                                                                                                                                  | 20-1<br>20-2<br>20-2                                 |

|                                                                                          | ter 21<br>Bus Driver                                                                                                                                                                                                                                                          |                                                      |

| 21.1<br>21.2<br>21.2.1<br>21.2.2<br>21.3                                                 | Hardware Operation Software Operation Transmitting Data Receiving Data Source Code Structure                                                                                                                                                                                  | 21-1<br>21-1<br>21-2                                 |

i.MX23 EVK Linux Reference Manual

| 21.4                                                                             | Menu Configuration Options                                                                                                                                                                   | 21-2                                                 |

|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|                                                                                  | ter 22<br>/SD/SDIO Host Driver                                                                                                                                                               |                                                      |

| 22.1<br>22.2<br>22.3<br>22.4<br>22.5<br>22.6<br>Chap<br>Unive                    | Hardware Operation Software Operation Driver Features Source Code Structure Menu Configuration Options Programming Interface  Ster 23 Persal Asynchronous Receiver-Transmitter (UART) Driver | 22-1<br>22-2<br>22-2<br>22-2                         |

| 23.1<br>23.1.1<br>23.1.2<br>23.1.3<br>23.2<br>23.2.1<br>23.2.2<br>23.2.3<br>23.3 | Source Code Structure                                                                                                                                                                        | 23-1<br>23-2<br>23-2<br>23-2<br>23-2<br>23-2<br>23-2 |

| Chap<br>ARC                                                                      | ter 24<br>USB Driver                                                                                                                                                                         |                                                      |

| 24.1<br>24.2<br>24.3<br>24.4<br>24.5<br>24.6<br>24.7<br>24.8                     | Architectural Overview. Hardware Operation Software Operation Driver Features Source Code Structure Menu Configuration Options Programming Interface Default USB Settings                    | 24-2<br>24-3<br>24-4<br>24-4<br>24-6                 |

|                                                                                  | ter 25<br>Time Clock (RTC) Driver                                                                                                                                                            |                                                      |

| 25.1<br>25.2<br>25.3<br>25.4<br>25.5                                             | Hardware Operation Software Operation Source Code Structure Programming Interface Menu Configuration Options                                                                                 | 25-1<br>25-1<br>25-2                                 |

|                                                                                  |                                                                                                                                                                                              |                                                      |

Freescale Semiconductor -ix

## Chapter 26 Watchdog (WDOG) Driver

| 26.1<br>26.2<br>26.3<br>26.4<br>26.5 | Hardware Operation                                                                     | 26-1<br>26-1<br>26-1 |

|--------------------------------------|----------------------------------------------------------------------------------------|----------------------|

| Chap                                 | pter 27<br>ery Charger and Power Source Manager (PSM) Driver                           |                      |

| 27.1<br>27.2<br>27.3<br>27.4         | Hardware Operation Software Operation Source Code Structure Menu Configuration Options | 27-1                 |

|                                      | pter 28<br>Pulse Width Modulator (PWM) Driver                                          |                      |

| 28.1<br>28.2<br>28.3<br>28.4         | Hardware Operation                                                                     | 28-1<br>28-1         |

|                                      | pter 29<br> uently Asked Questions                                                     |                      |

| 29.1<br>29.2                         | NFS Mounting Root File System                                                          |                      |

-x Freescale Semiconductor

## **Tables**

| 1-1  | Linux BSP Supported Features                   | 1-2  |

|------|------------------------------------------------|------|

| 2-1  | MSL Directories                                | 2-3  |

| 3-1  | Interrupt Files List                           | 3-2  |

| 3-2  | Memory Map Files                               | 3-5  |

| 3-3  | Pin Multiplexing Source Files                  | 3-6  |

| 4-1  | DMA API Files                                  | 4-2  |

| 5-1  | Persistent Bits Driver Files                   | 5-2  |

| 6-1  | Unique ID Files                                | 6-2  |

| 7-1  | CPUFREQ Driver Files                           | 7-2  |

| 8-1  | Power Management Driver Files                  | 8-2  |

| 9-1  | Frame Buffer Driver Files                      | 9-2  |

| 10-1 | LCDIF Driver Files                             | 10-1 |

| 11-1 | Backlight Driver Files                         | 11-2 |

| 12-1 | Built-in ADC/DAC Codec ASoC Driver Source File | 12-5 |

| 15-1 | ENET 1588 File List                            | 15-2 |

| 16-1 | Port Assignment                                | 16-2 |

| 16-2 | Ethernet File List                             | 16-5 |

| 17-1 | Keypad Driver Files                            | 17-2 |

| 17-2 | Keypad Interrupt Timer Requirements            | 17-3 |

| 18-1 | Touch Screen Driver Files                      |      |

| 19-1 | I2C Interrupt Requirements                     | 19-3 |

| 24-1 | USB Driver Files                               | 24-4 |

| 24-2 | Default USB Settings                           | 24-6 |

| 25-1 | RTC Driver File List                           | 25-1 |

| 25-2 | RTC IOCTLs                                     | 25-2 |

| 27-1 | Battery Charger Driver Structure Fields        | 27-2 |

| 27-2 | Battery Charger Driver Files                   | 27-3 |

i.MX23 EVK Linux Reference Manual

Freescale Semiconductor -v

## **Figures**

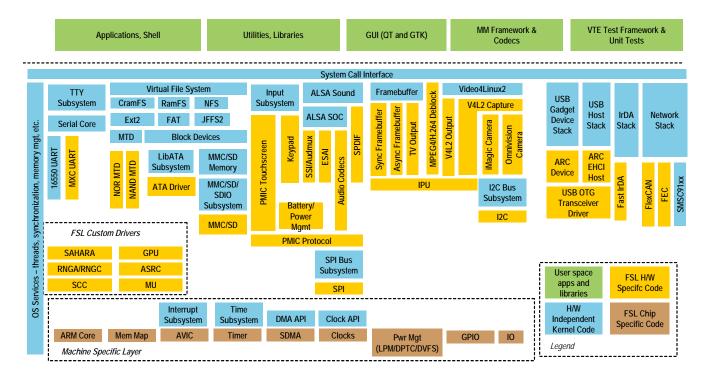

| 2-1  | BSP Block Diagram                       | 2-1  |

|------|-----------------------------------------|------|

| 2-2  | i.MX23 Kernel Graphic Components        | 2-7  |

| 2-3  | MTD Architecture                        | 2-9  |

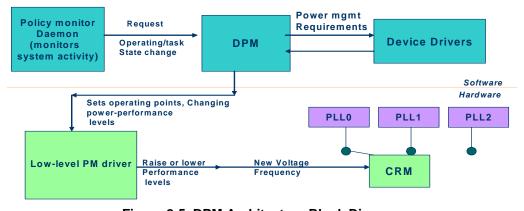

| 2-4  | DPM High Level Design                   | 2-14 |

| 2-5  | DPM Architecture Block Diagram          |      |

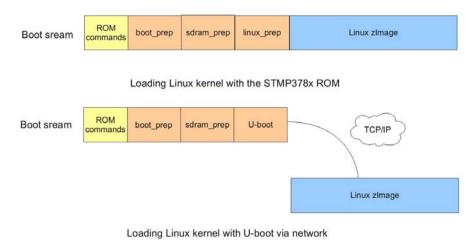

| 2-6  | i.MX23 Boot Stream                      |      |

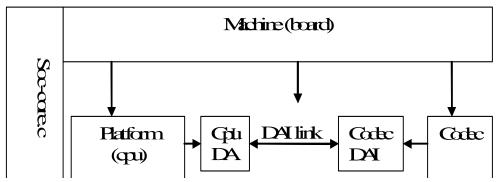

| 12-1 | ALSA SoC Software Architecture          |      |

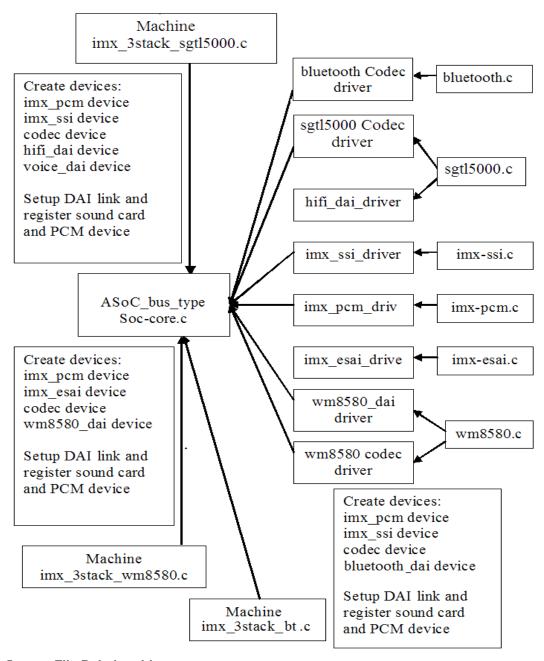

| 12-2 | ALSA SoC Source File Relationship       |      |

| 15-1 | IEEE 1588 Functions Overview            |      |

| 16-1 | Switch Interface                        | 16-2 |

| 16-2 | Passthrough Mode Configuration Overview | 16-3 |

| 16-3 | Switch Mode Configuration Overview      |      |

| 24-1 | USB Block Diagram                       |      |

### **About This Book**

The Linux board support package (BSP) represents a porting of the Linux operating system (OS) to the i.MX processors and its associated reference boards. The BSP supports many hardware features on the platforms and most of the Linux OS features that are not dependent on any specific hardware feature.

### **Audience**

This document is targeted to individuals who will port the i.MX Linux BSP to customer-specific products. The audience is expected to have a working knowledge of the Linux 2.6 kernel internals, driver models, and i.MX processors.

#### **Conventions**

This document uses the following notational conventions:

- Courier monospaced type indicate commands, command parameters, code examples, and file and directory names.

- *Italic* type indicates replaceable command or function parameters.

- **Bold** type indicates function names.

## **Definitions, Acronyms, and Abbreviations**

The following table defines the acronyms and abbreviations used in this document.

#### **Definitions and Acronyms**

| Term                   | Definition                                                                                                                                                               |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ADC                    | DC Asynchronous Display Controller                                                                                                                                       |  |

| address<br>translation |                                                                                                                                                                          |  |

| API                    | Application Programming Interface                                                                                                                                        |  |

| ARM <sup>®</sup>       | Advanced RISC Machines processor architecture                                                                                                                            |  |

| AUDMUX                 | Digital audio MUX—provides a programmable interconnection for voice, audio, and synchronous data routing between host serial interfaces and peripheral serial interfaces |  |

| BCD                    | Binary Coded Decimal                                                                                                                                                     |  |

| bus                    | A path between several devices through data lines                                                                                                                        |  |

| bus load               | The percentage of time a bus is busy                                                                                                                                     |  |

| CODEC                  | Coder/decoder or compression/decompression algorithm—used to encode and decode (or compress and decompress) various types of data                                        |  |

#### i.MX23 EVK Linux Reference Manual

Freescale Semiconductor vii

## **Definitions and Acronyms (continued)**

| Term       | Definition                                                                                                                                                                                                                                                                                                                                     |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CPU        | Central Processing Unit—generic term used to describe a processing core                                                                                                                                                                                                                                                                        |  |

| CRC        | Cyclic Redundancy Check—Bit error protection method for data communication                                                                                                                                                                                                                                                                     |  |

| CSI        | Camera Sensor Interface                                                                                                                                                                                                                                                                                                                        |  |

| DFS        | Dynamic Frequency Scaling                                                                                                                                                                                                                                                                                                                      |  |

| DMA        | Direct Memory Access—an independent block that can initiate memory-to-memory data transfers                                                                                                                                                                                                                                                    |  |

| DPM        | Dynamic Power Management                                                                                                                                                                                                                                                                                                                       |  |

| DRAM       | Dynamic Random Access Memory                                                                                                                                                                                                                                                                                                                   |  |

| DVFS       | Dynamic Voltage Frequency Scaling                                                                                                                                                                                                                                                                                                              |  |

| EMI        | External Memory Interface—controls all IC external memory accesses (read/write/erase/program) from all the masters in the system                                                                                                                                                                                                               |  |

| Endian     | Refers to byte ordering of data in memory. Little endian means that the least significant byte of the data is stored in a lower address than the most significant byte. In big endian, the order of the bytes is reversed                                                                                                                      |  |

| EPIT       | Enhanced Periodic Interrupt Timer—a 32-bit set and forget timer capable of providing precise interrupts at regular intervals with minimal processor intervention                                                                                                                                                                               |  |

| FCS        | Frame Checker Sequence                                                                                                                                                                                                                                                                                                                         |  |

| FIFO       | First In First Out                                                                                                                                                                                                                                                                                                                             |  |

| FIPS       | Federal Information Processing Standards—United States Government technical standards published by the National Institute of Standards and Technology (NIST). NIST develops FIPS when there are compelling Federal government requirements such as for security and interoperability but no acceptable industry standards                      |  |

| FIPS-140   | Security requirements for cryptographic modules—Federal Information Processing Standard 140-2(FIPS 140-2) is a standard that describes US Federal government requirements that IT products should meet for Sensitive, but Unclassified (SBU) use                                                                                               |  |

| Flash      | A non-volatile storage device similar to EEPROM, where erasing can be done only in blocks or the entire chip.                                                                                                                                                                                                                                  |  |

| Flash path | Path within ROM bootstrap pointing to an executable Flash application                                                                                                                                                                                                                                                                          |  |

| Flush      | Procedure to reach cache coherency. Refers to removing a data line from cache. This process includes cleaning the line, invalidating its VBR and resetting the tag valid indicator. The flush is triggered by a software command                                                                                                               |  |

| GPIO       | General Purpose Input/Output                                                                                                                                                                                                                                                                                                                   |  |

| hash       | Hash values are produced to access secure data. A hash value (or simply hash), also called a message digest, is a number generated from a string of text. The hash is substantially smaller than the text itself, and is generated by a formula in such a way that it is extremely unlikely that some other text produces the same hash value. |  |

| I/O        | Input/Output                                                                                                                                                                                                                                                                                                                                   |  |

| ICE        | In-Circuit Emulation                                                                                                                                                                                                                                                                                                                           |  |

| IP         | Intellectual Property                                                                                                                                                                                                                                                                                                                          |  |

| IPU        | Image Processing Unit —supports video and graphics processing functions and provides an interface to video/still image sensors and displays                                                                                                                                                                                                    |  |

| IrDA       | Infrared Data Association—a nonprofit organization whose goal is to develop globally adopted specifications for infrared wireless communication                                                                                                                                                                                                |  |

#### i.MX23 EVK Linux Reference Manual

viii Freescale Semiconductor

## **Definitions and Acronyms (continued)**

| Term                | Definition                                                                                                                                                                                                                                                                                                                                                                    |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ISR                 | Interrupt Service Routine                                                                                                                                                                                                                                                                                                                                                     |  |

| JTAG                | JTAG (IEEE Standard 1149.1) A standard specifying how to control and monitor the pins of compliant devices on a printed circuit board                                                                                                                                                                                                                                         |  |

| Kill                | Abort a memory access                                                                                                                                                                                                                                                                                                                                                         |  |

| KPP                 | KeyPad Port—16-bit peripheral used as a keypad matrix interface or as general purpose input/output (I/O)                                                                                                                                                                                                                                                                      |  |

| line                | Refers to a unit of information in the cache that is associated with a tag                                                                                                                                                                                                                                                                                                    |  |

| LRU                 | Least Recently Used—a policy for line replacement in the cache                                                                                                                                                                                                                                                                                                                |  |

| MMU                 | Memory Management Unit—a component responsible for memory protection and address translation                                                                                                                                                                                                                                                                                  |  |

| MPEG                | Moving Picture Experts Group—an ISO committee that generates standards for digital video compression and audio. It is also the name of the algorithms used to compress moving pictures and video                                                                                                                                                                              |  |

| MPEG<br>standards   | There are several standards of compression for moving pictures and video  • MPEG-1 is optimized for CD-ROM and is the basis for MP3  • MPEG-2 is defined for broadcast video in applications such as digital television set-top boxes and DVD  • MPEG-3 was merged into MPEG-2  • MPEG-4 is a standard for low-bandwidth video telephony and multimedia on the World-Wide Web |  |

| MQSPI               | Multiple Queue Serial Peripheral Interface—used to perform serial programming operations necessary to configure radio subsystems and selected peripherals                                                                                                                                                                                                                     |  |

| MSHC                | Memory Stick Host Controller                                                                                                                                                                                                                                                                                                                                                  |  |

| NAND Flash          | Flash ROM technology—NAND Flash architecture is one of two flash technologies (the other being NOR) used in memory cards such as the Compact Flash cards. NAND is best suited to flash devices requiring high capacity data storage. NAND flash devices offer storage space up to 512-Mbyte and offers faster erase, write, and read capabilities over NOR architecture       |  |

| NOR Flash           | See NAND Flash                                                                                                                                                                                                                                                                                                                                                                |  |

| PCMCIA              | Personal Computer Memory Card International Association—a multi-company organization that has developed a standard for small, credit card-sized devices, called PC Cards. There are three types of PCMCIA cards that have the same rectangular size (85.6 by 54 millimeters), but different widths                                                                            |  |

| physical<br>address | The address by which the memory in the system is physically accessed                                                                                                                                                                                                                                                                                                          |  |

| PLL                 | Phase Locked Loop—an electronic circuit controlling an oscillator so that it maintains a constant phase angle (a lock) on the frequency of an input, or reference, signal                                                                                                                                                                                                     |  |

| RAM                 | Random Access Memory                                                                                                                                                                                                                                                                                                                                                          |  |

| RAM path            | Path within ROM bootstrap leading to the downloading and the execution of a RAM application                                                                                                                                                                                                                                                                                   |  |

| RGB                 | The RGB color model is based on the additive model in which Red, Green, and Blue light are combined to create other colors. The abbreviation RGB comes from the three primary colors in additive light models                                                                                                                                                                 |  |

| RGBA                | RGBA color space stands for Red Green Blue Alpha. The alpha channel is the transparency channel, and is unique to this color space. RGBA, like RGB, is an additive color space, so the more of a color placed, the lighter the picture gets. PNG is the best known image format that uses the RGBA color space                                                                |  |

| RNGA                | Random Number Generator Accelerator—a security hardware module that produces 32-bit pseudo random numbers as part of the security module                                                                                                                                                                                                                                      |  |

| ROM                 | Read Only Memory                                                                                                                                                                                                                                                                                                                                                              |  |

#### i.MX23 EVK Linux Reference Manual

Freescale Semiconductor ix

#### **Definitions and Acronyms (continued)**

| Term             | Definition                                                                                                                                                                                                                                                                                                                                                                                   |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ROM<br>bootstrap | Internal boot code encompassing the main boot flow as well as exception vectors                                                                                                                                                                                                                                                                                                              |  |

| RTIC             | Real-time integrity checker—a security hardware module                                                                                                                                                                                                                                                                                                                                       |  |

| SCC              | SeCurity Controller—a security hardware module                                                                                                                                                                                                                                                                                                                                               |  |

| SDMA             | Smart Direct Memory Access                                                                                                                                                                                                                                                                                                                                                                   |  |

| SDRAM            | Synchronous Dynamic Random Access Memory                                                                                                                                                                                                                                                                                                                                                     |  |

| SoC              | System on a Chip                                                                                                                                                                                                                                                                                                                                                                             |  |

| SPBA             | Shared Peripheral Bus Arbiter—a three-to-one IP-Bus arbiter, with a resource-locking mechanism                                                                                                                                                                                                                                                                                               |  |

| SPI              | Serial Peripheral Interface—a full-duplex synchronous serial interface for connecting low-/medium-bandwidth external devices using four wires. SPI devices communicate using a master/slave relationship over two data lines and two control lines: Also see SS, SCLK, MISO, and MOSI                                                                                                        |  |

| SRAM             | Static Random Access Memory                                                                                                                                                                                                                                                                                                                                                                  |  |

| SSI              | Synchronous-Serial Interface—standardized interface for serial data transfer                                                                                                                                                                                                                                                                                                                 |  |

| TBD              | To Be Determined                                                                                                                                                                                                                                                                                                                                                                             |  |

| UART             | Universal Asynchronous Receiver/Transmitter—asynchronous serial communication to external devices                                                                                                                                                                                                                                                                                            |  |

| UID              | Unique ID-a field in the processor and CSF identifying a device or group of devices                                                                                                                                                                                                                                                                                                          |  |

| USB              | Universal Serial Bus—an external bus standard that supports high speed data transfers. The USB 1.1 specification supports data transfer rates of up to 12Mb/s and USB 2.0 has a maximum transfer rate of 480 Mbps. A single USB port can be used to connect up to 127 peripheral devices, such as mice, modems, and keyboards. USB also supports Plug-and-Play installation and hot plugging |  |

| USBOTG           | USB On The Go—an extension of the USB 2.0 specification for connecting peripheral devices to each other. USBOTG devices, also known as dual-role peripherals, can act as limited hosts or peripherals themselves depending on how the cables are connected to the devices, and they also can connect to a host PC                                                                            |  |

| word             | A group of bits comprising 32-bits                                                                                                                                                                                                                                                                                                                                                           |  |

## **Suggested Reading**

The following documents contain information that supplements this guide:

- i.MX23 PDK Linux Quick Start Guide

- BSP API Document (BSP Doxygen Code Documentation)

- i.MX23 PDK Linux User's Guide

- i.MX23 PDK Hardware User's Guide

- i.MX23 Multimedia Applications Processor Reference Manual (IMX23RM)

- [KERN] *Linux kernel coding style*. This is included in Linux distributions as the file Documentation/CodingStyle

- [WSAS] WSAS Coding Conventions, version 0.4

- [ASM] WSAS Assembly Code Conventions

- [DOXY] WSAS Guidelines for Writing Doxygen Comments

#### i.MX23 EVK Linux Reference Manual

x Freescale Semiconductor

# Chapter 1 Introduction

The i.MX family Linux board support package (BSP) supports the Linux operating system (OS) on the following processor:

• i.MX23 Applications Processor

The purpose of this software package is to support Linux on the i.MX family of integrated circuits (ICs) and their associated platforms (EVK). It provides the necessary software to interface the standard open-source Linux kernel to the i.MX hardware. The goal is to enable Freescale customers to rapidly build products based on i.MX devices that use the Linux OS.

The BSP is not a platform or product reference implementation. It does not contain all of the product-specific drivers, hardware-independent software stacks, graphical user interface (GUI) components, Java Virtual Machine (JVM), and applications required for a product. Some of these are made available in their original open-source form as part of the base kernel.

The BSP is not intended to be used for silicon verification. While it can play a role in this, the BSP functionality and the tests run on the BSP do not have sufficient coverage to replace traditional silicon verification test suites.

## 1.1 Software Base

The i.MX BSP is based on version 2.6.31 of the Linux kernel from the official Linux kernel web site (http://www.kernel.org). It is enhanced with the features provided by Freescale.

Freescale Semiconductor 1-1

#### Introduction

## 1.2 Features

Table 1-1 describes the features supported by the Linux BSP for specific platforms.

**Table 1-1. Linux BSP Supported Features**

| Feature                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Chapter Source                                             | Applicable<br>Platform |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------------|