# i.MX25 PDK Linux

Reference Manual

Part Number: 926-77210

ÁRev.Œ€JÈFG

€F£20F€

### How to Reach Us:

### Home Page:

www.freescale.com

#### E-mail:

support@freescale.com

### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

**Europe, Middle East, and Africa:** Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F -8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064, Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-521-6274 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2008-2009. All rights reserved.

# **Contents**

# **About This Book**

| Chapter 1 Introduction  1.1 Software Base                                       | . 17<br>. 17<br>. 20 |

|---------------------------------------------------------------------------------|----------------------|

| 1.2 Features.  Chapter 2 Architecture  2.1 Linux BSP Block Diagram. 2.2 Kernel. |                      |

| Architecture  2.1 Linux BSP Block Diagram                                       |                      |

| 2.2 Kernel                                                                      |                      |

|                                                                                 | 2-1                  |

| 2.2.1 Varial Configuration                                                      | 2-2                  |

| 2.2.1 Kernel Configuration                                                      | 2-2                  |

| 2.2.2 Machine Specific Layer (MSL)                                              | 2-3                  |

| 2.2.2.1 Memory Map                                                              |                      |

| 2.2.2.2 Interrupts                                                              |                      |

| 2.2.2.3 General Purpose Timer (GPT)                                             | 2-3                  |

| 2.2.2.4 Smart Direct Memory Access (SDMA) API                                   | 2-4                  |

| 2.2.2.5 Input/Output (I/O)                                                      | 2-5                  |

| 2.2.2.6 Shared Peripheral Bus Arbiter (SPBA)                                    | 2-5                  |

| 2.3 Drivers                                                                     | 2-5                  |

| 2.3.1 Universal Asynchronous Receiver/Transmitter (UART) Driver                 | 2-6                  |

| 2.3.1.1 UART Driver                                                             | 2-6                  |

| 2.3.2 Real-Time Clock (RTC) Driver                                              | 2-6                  |

| 2.3.3 Watchdog Timer (WDOG) Driver                                              | 2-7                  |

| 2.3.4 SDMA API Driver                                                           | 2-7                  |

| 2.3.5 Sound Driver                                                              | 2-7                  |

| 2.3.6 Memory Technology Device (MTD) Driver                                     | 2-8                  |

| 2.3.7 Networking Drivers                                                        | 2-9                  |

| 2.3.7.1 SMSC LAN9217 Ethernet Driver                                            |                      |

| 2.3.7.2 FEC driver                                                              | 2-9                  |

| 2.3.8 USB Driver                                                                | 2-9                  |

| 2.3.8.1 USB Host-Side API Model                                                 |                      |

| 2.3.8.2 USB Device-Side Gadget Framework                                        |                      |

| 2.3.8.3 USB OTG Framework                                                       |                      |

| 2.3.9 Security Drivers                                                          |                      |

| 2.3.9.1 Security Controller (SCC) Module Driver                                 |                      |

| 2.3.10 Power managementGeneral Drivers                                          |                      |

| 2.3.10.1 MMC/SD Host Driver                                                     |                      |

| 2.3.10.2 MMC/SD Slot Driver                                                     |                      |

| 2.3.10        |                                                        |      |

|---------------|--------------------------------------------------------|------|

| 2.3.10.4      | Configurable Serial Peripheral Interface (CSPI) Driver | 2-14 |

| 2.3.10.       | 5 Dynamic Power Management (DPM) Driver                | 2-14 |

| 2.3.10.       |                                                        |      |

| 2.4           | Boot Loaders                                           |      |

| 2.4.1         | Functions of Boot Loaders                              | 2-16 |

| 2.4.2         | RedBoot                                                |      |

|               |                                                        |      |

| Chapt<br>Mach | ter 3<br>ine Specific Layer (MSL)                      |      |

| 3.1           | Interrupts                                             | 3-1  |

| 3.1.1         | Interrupt Hardware Operation                           |      |

| 3.1.2         | Interrupt Software Operation                           |      |

| 3.1.3         | Interrupt Features                                     |      |

| 3.1.4         | Interrupt Source Code Structure                        |      |

| 3.1.5         | Interrupt Programming Interface                        |      |

| 3.2           | Timer                                                  |      |

| 3.2.1         | Timer Hardware Operation                               |      |

| 3.2.2         | Timer Software Operation                               |      |

| 3.2.3         | Timer Features                                         |      |

| 3.2.4         | Timer Source Code Structure                            |      |

|               | Memory Map                                             |      |

| 3.3.1         | Memory Map Hardware Operation.                         |      |

| 3.3.2         | Memory Map Software Operation                          |      |

| 3.3.3         | Memory Map Features                                    |      |

| 3.3.4         | Memory Map Source Code Structure                       |      |

| 3.3.5         | Memory Map Programming Interface                       |      |

|               | IOMUX                                                  |      |

| 3.4.1         | IOMUX Hardware Operation                               |      |

| 3.4.2         | IOMUX Software Operation                               |      |

| 3.4.3         | IOMUX Features                                         |      |

| 3.4.4         | IOMUX Source Code Structure                            |      |

| 3.4.5         | IOMUX Programming Interface.                           |      |

| 3.4.6         | IOMUX Control Through GPIO Module                      |      |

| 3.4.6.1       | GPIO Hardware Operation                                |      |

| 3.4.6.2       | GPIO Software Operation.                               |      |

| 3.4.6.3       | GPIO Features.                                         |      |

| 3.4.6.4       | GPIO Source Code Structure                             |      |

| 3.4.6.5       | GPIO Programming Interface                             |      |

|               | General Purpose Input/Output (GPIO)                    |      |

| 3.5.1         | GPIO Software Operation.                               |      |

| 3.5.1.1       | API for GPIO                                           |      |

| 3.5.2         | GPIO Features.                                         |      |

| 3.5.3         | GPIO Source Code Structure                             |      |

| 2.2.2         | Care Source Code Statement                             | 5 )  |

| 3.5.4 | GPIO Programming Interface             |             |

|-------|----------------------------------------|-------------|

| 3.6   | EDIO                                   | 3-9         |

| 3.6.1 | EDIO Hardware Operation                | 3-9         |

| 3.6.2 | EDIO Software Operation                |             |

| 3.6.3 | EDIO Features                          |             |

| 3.6.4 | EDIO Source Code Structure             |             |

| 3.6.5 | EDIO Programming Interface             |             |

| 3.7   | SPBA Bus Arbiter                       |             |

| 3.7.1 | SPBA Hardware Operation.               |             |

| 3.7.2 | SPBA Software Operation                |             |

| 3.7.3 | SPBA Features                          |             |

| 3.7.4 | SPBA Source Code Structure             |             |

| 3.7.5 | SPBA Programming Interface             |             |

| 3.7.3 | SFDA Flogramming interface             | <b>)-11</b> |

| Char  | oter 4                                 |             |

|       | rt Direct Memory Access (SDMA) API     |             |

| 4.1   | Overview                               | 4-1         |

| 4.2   | Hardware Operation                     |             |

| 4.3   | Software Operation                     |             |

| 4.4   | Source Code Structure                  |             |

| 4.5   | Menu Configuration Options             |             |

| 4.6   | Programming Interface                  |             |

| 4.7   | Usage Example                          |             |

| 4.7   | Osage Example                          | 4-4         |

|       | oter 5                                 |             |

| PMIC  | C (MC34704) Protocol Driver            |             |

| 5.1   | Key PMIC Features and Capabilities     | 5-1         |

| 5.1.1 | PMIC Register Access and Arbitration   |             |

| 5.1.2 | Event Notification                     |             |

| 5.2   | Driver Requirements                    |             |

| 5.3   | Driver Software Operation              |             |

| 5.4   | Driver Implementation Details          | 5-2         |

| 5.4.1 | Driver Initialization.                 |             |

| 5.4.2 | Driver Unloading                       |             |

| 5.4.3 | Register Access                        |             |

| 5.5   | Driver Source Code Structure           |             |

| 5.6   | Linux Menu Configuration Options       |             |

| 01    |                                        |             |

|       | oter 6<br>C (MC34704) Regulator Driver |             |

|       |                                        |             |

| 6.1   | PMIC Features                          |             |

| 6.2   | Driver Requirements                    | 6-1         |

| 6.3   | Driver Software Operation              |             |

|       |                                        |             |

| 6.4           | Regulator APIs                                       |      |

|---------------|------------------------------------------------------|------|

| 6.5           | Driver Architecture                                  |      |

| 6.6<br>6.7    | Driver Square Code Structure                         |      |

| 6.8           | Driver Source Code Structure                         |      |

|               |                                                      | 0-3  |

| i.MX2         | oter 7<br>25 Low-level Power Management (PM) Driver  |      |

| 7.1           | Hardware Operation                                   | 7-1  |

| 7.1.1         | Lower Power Mode                                     |      |

| 7.2           | Software Operations                                  | 7-1  |

| 7.3           | Source Code Structure                                |      |

| 7.4           | Linux Menu Configuration Options                     |      |

| 7.5           | Programming Interface                                | 7-2  |

|               | oter 8 Frequency Scaling (CPUFREQ) Driver            |      |

| 8.1           | Software Operation                                   | 8-1  |

| 8.2           | Source Code Structure                                |      |

| 8.3           | Menu Configuration Options                           |      |

| 8.3.1         | Board Configuration Options                          | 8-2  |

| Chap<br>Liqui | oter 9<br>d Crystal Display Controller (LCDC) Driver |      |

| 9.1           | LCD Driver Overview                                  | 9-1  |

| 9.1.1         | Hardware Operation                                   |      |

| 9.1.2         | Software Operation                                   |      |

| 9.1.3         | Graphics Window                                      |      |

| 9.1.4         | Architecture                                         | 9-2  |

| 9.2           | Source Code Structure Configuration                  |      |

| 9.3           | Linux Menu Configuration Options                     | 9-3  |

|               | oter 10<br>iVision Camera (OV2640) Driver            |      |

| 10.1          | Hardware Operation                                   | 10-1 |

| 10.2          | Software Operation                                   | 10-1 |

| 10.3          | Source Code Structure                                |      |

| 10.4          | Linux Menu Configuration Options                     | 10-2 |

|               | oter 11<br>Camera Sensor Interface (CSI) Driver      |      |

| 11.1          | Hardware Operation                                   | 11-1 |

|               | i.MX25 PDK Linux Reference Manual                    |      |

|               | I.IVIAZJ FUR LIIIUX RCICICIUC WAIIUAI                |      |

| 11.2<br>11.2.1<br>11.2.2<br>11.2.2.<br>11.2.2.<br>11.3<br>11.4                                                       | 1 V4L2 Capture Device                                                                                                                                                                                                                                                                                     | 11-1<br>11-1<br>11-2<br>11-2<br>11-2                                 |

|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 11.5                                                                                                                 | Programming Interface                                                                                                                                                                                                                                                                                     |                                                                      |

| Adva                                                                                                                 | ter 12<br>nced Linux Sound Architecture (ALSA)<br>em on a Chip (ASoC) Sound Driver                                                                                                                                                                                                                        |                                                                      |

| 12.1<br>12.1.1<br>12.1.2<br>12.1.3<br>12.1.4<br>12.2<br>12.3<br>12.4<br>12.4.1<br>12.4.2<br>12.4.3<br>12.5<br>12.5.1 | SoC Sound Card Stereo Codec Features 5.1 Codec Features 4-Channel ADC Codec Features. Sound Card Information ASoC Driver Source Architecture Menu Configuration Options Hardware Operation Stereo Audio Codec 5.1 Audio Codec 4-Channel ADC Codec Software Operation. Sound Card Registration Device Open | 12-2<br>12-2<br>12-3<br>12-3<br>12-6<br>12-6<br>12-7<br>12-7<br>12-7 |

|                                                                                                                      | ter 13<br>D Flash Memory Technology Device (MTD) Driver                                                                                                                                                                                                                                                   |                                                                      |

| 13.1<br>13.1.1<br>13.1.2<br>13.2<br>13.3<br>13.4<br>13.5                                                             |                                                                                                                                                                                                                                                                                                           | 13-1<br>13-1<br>13-2<br>13-2<br>13-2                                 |

|                                                                                                                      | ter 14<br>Level Keypad Driver                                                                                                                                                                                                                                                                             |                                                                      |

| 14.1<br>14.2<br>14.3<br>14.4                                                                                         | Hardware Operation                                                                                                                                                                                                                                                                                        | 14-1<br>14-3                                                         |

| 14.5<br>14.6<br>14.7<br>14.8<br>14.9                     | Source Code Structure  Menu Configuration Options  Programming Interface  Interrupt Requirements  Device-Specific Information.                                                         | 14-4<br>14-4<br>14-4                 |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

|                                                          | ter 15<br>h Screen and ADC Drivers                                                                                                                                                     |                                      |

| 15.1<br>15.2<br>15.3<br>15.4<br>15.5<br>15.6<br>15.7     | Driver Overview .  Hardware Operation .  Software Operation .  Source Code Structure .  Menu Configuration Options .  Programming Interface (Exported API) .  Interrupt Requirements . | 15-1<br>15-2<br>15-2<br>15-2<br>15-2 |

| Chap<br>SMS(                                             | ter 16<br>C LAN9217 Ethernet Driver                                                                                                                                                    |                                      |

| 16.1<br>16.2<br>16.3<br>16.4<br>16.5                     | Hardware Operation Software Operation Requirements Source Code Structure Linux Menu Configuration Options                                                                              | 16-1<br>16-2<br>16-2                 |

|                                                          | ter 17<br>Ethernet Controller (FEC) Driver                                                                                                                                             |                                      |

| 17.1<br>17.2<br>17.3<br>17.4<br>17.5<br>17.5.1<br>17.5.2 | Hardware Operation Software Operation Source Code Structure Menu Configuration Options Programming Interface Device-Specific Defines Getting a MAC Address                             | 17-3<br>17-3<br>17-4<br>17-4<br>17-4 |

|                                                          | ter 18<br>e Driver                                                                                                                                                                     |                                      |

| 18.1<br>18.2<br>18.3<br>18.4<br>18.5<br>18.6             | Dry Ice Driver Features and Capabilities  Driver Requirements.  Driver Software Operation  Driver Source Code Structure  Linux Menu Configuration Options  Hardware Configuration.     | 18-2<br>18-2<br>18-3<br>18-3         |

# **Chapter 19 Security Drivers**

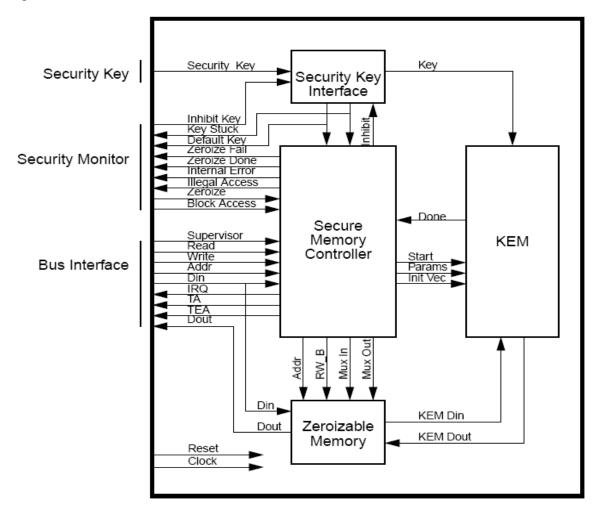

| 19.1                 | Hardware Overview                    | 19-1                 |

|----------------------|--------------------------------------|----------------------|

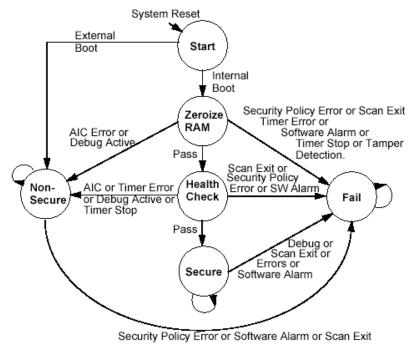

| 19.1.1               | Boot Security                        | 19-1                 |

| 19.1.2               | Secure RAM                           | 19-2                 |

| 19.1.3               | KEM                                  | 19-2                 |

| 19.1.4               | Zeroizable Memory                    | 19-2                 |

| 19.1.5               | Security Key Interface Module        | 19-3                 |

| 19.1.6               | Secure Memory Controller             | 19-3                 |

| 19.1.7               | Security Monitor                     | 19-3                 |

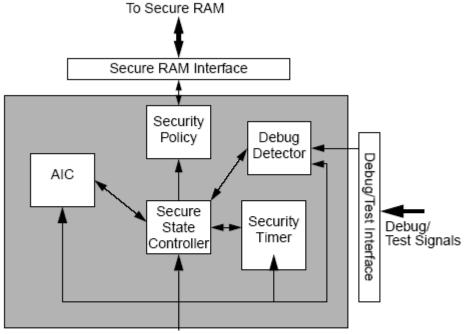

| 19.1.8               | Secure State Controller              | 19-4                 |

| 19.1.9               | Security Policy                      | 19-5                 |

| 19.1.10              | Algorithm Integrity Checker (AIC)    | 19-5                 |

| 19.1.11              | Secure Timer                         | 19-5                 |

| 19.1.12              | Debug Detector                       | 19-5                 |

| 19.2                 | Software Operation                   | 19-5                 |

| 19.2.1               | SCC Common Software Operations       | 19-5                 |

| 19.3                 | Driver Features                      | 19-6                 |

| 19.4                 | Source Code Structure                | 19-6                 |

| 19.5                 | Menu Configuration Options           | 19-7                 |

| 19.5.1               | Source Code Configuration Options    |                      |

| 19.5.1.              |                                      |                      |

|                      | C (I2C) Driver                       |                      |

|                      | I2C Bus Driver Overview              |                      |

|                      | I2C Device Driver Overview           |                      |

|                      | Hardware Operation                   |                      |

|                      | Software Operation                   |                      |

| 20.4.1               | I2C Bus Driver Software Operation    |                      |

| 20.4.2               | I2C Device Driver Software Operation |                      |

|                      | Driver Features                      |                      |

| 20.6                 | Source Code Structure                |                      |

|                      | Menu Configuration Options           |                      |

|                      | Programming Interface                |                      |

| 20.9                 |                                      |                      |

|                      | Interrupt Requirements               | 20-3                 |

| Chapt<br>Confi       |                                      | 20-3                 |

| <b>Confi</b><br>21.1 | ter 21                               | 21-1<br>21-1<br>21-1 |

| 21.2.3  | Standard Operations                                             | 21-3 |

|---------|-----------------------------------------------------------------|------|

| 21.2.4  | CSPI Synchronous Operation                                      | 21-4 |

| 21.3    | Driver Features                                                 | 21-4 |

| 21.4    | Source Code Structure                                           | 21-4 |

| 21.5    | Menu Configuration Options                                      | 21-4 |

| 21.6    | Programming Interface                                           | 21-5 |

| 21.7    | Interrupt Requirements                                          | 21-5 |

|         | ter 22                                                          |      |

| WINC    | SD/SDIO Host Driver                                             |      |

| 22.1    | Hardware Operation                                              | 22-1 |

| 22.2    | Software Operation                                              | 22-2 |

| 22.3    | Driver Features                                                 |      |

| 22.4    | Source Code Structure                                           | 22-4 |

| 22.5    | Menu Configuration Options                                      | 22-4 |

| 22.6    | Programming Interface                                           | 22-4 |

| Chan    | tor 22                                                          |      |

| Unive   | ter 23<br>ersal Asynchronous Receiver/Transmitter (UART) Driver |      |

| 23.1    | Hardware Operation                                              | 23-1 |

| 23.2    | Software Operation                                              |      |

| 23.3    | Driver Features                                                 |      |

| 23.4    | Source Code Structure                                           |      |

| 23.5    | Configuration                                                   | 23-3 |

| 23.5.1  | Menu Configuration Options                                      |      |

| 23.5.2  | Source Code Configuration Options                               |      |

| 23.5.2. |                                                                 |      |

| 23.5.2. |                                                                 |      |

| 23.6    | Programming Interface                                           |      |

| 23.7    | Interrupt Requirements                                          | 23-4 |

| 23.8    | Device Specific Information                                     | 23-5 |

| 23.8.1  | UART Ports                                                      | 23-5 |

| 23.8.2  | Board Setup Configuration                                       | 23-5 |

| 23.9    | Early UART Support                                              | 23-7 |

|         | ter 24                                                          |      |

| ARC     | USB Driver                                                      |      |

| 24.1    | Architectural Overview                                          | 24-2 |

| 24.2    | Hardware Operation                                              | 24-2 |

| 24.3    | Software Operation                                              |      |

| 24.4    | Driver Features                                                 | 24-3 |

| 24.5    | Source Code Structure                                           |      |

| 24.6    | Menu Configuration Options                                      |      |

|         |                                                                 |      |

i.MX25 PDK Linux Reference Manual

| 24.7<br>24.8                                                 | Programming Interface                                                                                                           |                                      |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Chap<br>FlexC                                                | ter 25<br>CAN Driver                                                                                                            |                                      |

| 25.1<br>25.2<br>25.3<br>25.4<br>25.5                         | Driver Overview                                                                                                                 | 25-1<br>25-1<br>25-2                 |

|                                                              | ter 26<br>Time Clock (RTC) (Drylce) Driver                                                                                      |                                      |

| 26.1<br>26.2<br>26.3<br>26.4<br>26.5                         | Hardware Operation  Software Operation  Requirements  Source Code Structure  Programming Interface                              | 26-1<br>26-1<br>26-1                 |

| Chap<br>SIM [                                                | ter 27<br>Driver                                                                                                                |                                      |

| 27.1<br>27.2<br>27.3<br>27.4<br>27.5<br>27.6                 | Hardware Operation Software Operation Requirements Source Code Structure Linux Menu Configuration Options Programming Interface | 27-1<br>27-3<br>27-3<br>27-3         |

| Chap<br>Watc                                                 | ter 28<br>hdog (WDOG) Driver                                                                                                    |                                      |

| 28.1<br>28.2<br>28.3<br>28.3.1<br>28.3.2<br>28.3.3<br>28.3.4 |                                                                                                                                 | 28-1<br>28-1<br>28-1<br>28-1<br>28-2 |

|                                                              | iter 29<br>Jently Asked Questions                                                                                               |                                      |

| 29.1<br>29.2                                                 | Downloading a File                                                                                                              |                                      |

|                                                              | i.MX25 PDK Linux Reference Manual                                                                                               |                                      |

| 29.3 | NFS Mounting Root File System                       | 29-2 |

|------|-----------------------------------------------------|------|

| 29.4 | Error: NAND MTD Driver Flash Erase Failure          | 29-3 |

| 29.5 | Error: NAND MTD Driver Attempt to Erase a Bad Block | 29-3 |

| 29.6 | How to Use the Memory Access Tool                   | 29-3 |

| 29.7 | How to Make Software Workable when JTAG is Attached | 29-4 |

i.MX25 PDK Linux Reference Manual

# **Tables**

| 1-1  | Linux BSP Supported Features                | 1-2  |

|------|---------------------------------------------|------|

| 2-1  | MSL Directories                             | 2-3  |

| 3-1  | Interrupt Files                             | 3-2  |

| 3-2  | Memory Map Files                            | 3-5  |

| 3-3  | IOMUX Files                                 | 3-6  |

| 3-4  | IOMUX Through GPIO Files                    | 3-8  |

| 3-5  | GPIO Files                                  | 3-9  |

| 3-6  | EDIO Files                                  | 3-10 |

| 3-7  | SPBA Files                                  | 3-11 |

| 4-1  | SDMA Channel Usage                          | 4-3  |

| 4-2  | SDMA API Source Files                       | 4-3  |

| 4-3  | SDMA Script Files                           | 4-3  |

| 5-1  | Events Supported by Protocol Driver         | 5-2  |

| 5-2  | PMIC Protocol Driver Files                  | 5-3  |

| 6-1  | MC34704 Power Management Driver Files       | 6-3  |

| 7-1  | Low Power Modes                             | 7-1  |

| 7-2  | PM Driver Files                             | 7-2  |

| 8-1  | CPUFREQ Driver Files                        | 8-1  |

| 9-1  | LCD Driver Files                            | 9-3  |

| 10-1 | Camera Driver Files                         | 10-2 |

| 11-1 | V4L2 and SI Driver Files                    | 11-3 |

| 12-1 | Stereo Codec SoC Driver Files               | 12-4 |

| 12-2 | 5.1 Codec SoC Driver Files                  | 12-5 |

| 12-3 | 4 channel ADC codec ASoC Driver Source File | 12-5 |

| 13-1 | NAND MTD Driver Files                       | 13-2 |

| 14-1 | Keypad Driver Files                         | 14-3 |

| 14-2 | Keypad Interrupt Timer Requirements         | 14-4 |

| 14-3 | Key Connections for Keypad                  | 14-4 |

| 15-1 | ADC Driver Files                            | 15-2 |

| 15-2 | Touch Screen Driver Files                   | 15-2 |

| 16-1 | Ethernet Driver Files                       | 16-2 |

| 17-1 | Pin Usage in MII, RMII and SNI Modes        |      |

| 17-2 | FEC Driver Files                            | 17-3 |

| 18-1 | DryIce Features                             | 18-2 |

| 18-2 | Dry Ice Driver Files                        | 18-3 |

| 19-1 | SCCDriver Files                             | 19-6 |

| 20-1 | I2C Bus Driver Files                        | 20-3 |

| 20-2 | I2C Interrupt Requirements                  | 20-3 |

| 21-1 | CSPI Driver Files                           | 21-4 |

|      |                                             |      |

| 21-2  | CSPI Interrupt Requirements              | 21-5 |

|-------|------------------------------------------|------|

| 22-1  | eSDHC Driver Files MMC/SD Driver Files   | 22-4 |

| 23-1  | UART Driver Files                        | 23-3 |

| 23-2  | UART Global Header Files                 | 23-3 |

| 23-3  | UART Interrupt Requirements              | 23-5 |

| 23-4  | UART General Configuration               | 23-5 |

| 23-5  | UART Active/Inactive Configuration       | 23-5 |

| 23-6  | UART IRDA Configuration                  | 23-5 |

| 23-7  | UART Mode Configuration                  | 23-5 |

| 23-8  | UART Shared Peripheral Configuration     | 23-6 |

| 23-9  | UART Hardware Flow Control Configuration | 23-6 |

| 23-10 | UART DMA Configuration                   | 23-6 |

| 23-11 | UART DMA RX Buffer Size Configuration    | 23-6 |

| 23-12 | UART UCR4_CTSTL Configuration            | 23-6 |

| 23-13 | UART UFCR_RXTL Configuration             | 23-6 |

| 23-14 | UART UFCR_TXTL Configuration             | 23-6 |

| 23-15 | UART Interrupt Mux Configuration         | 23-6 |

| 23-16 | UART Interrupt 1 Configuration           | 23-6 |

| 23-17 | UART Interrupt 2 Configuration           | 23-7 |

| 23-18 | UART interrupt 3 Configuration           | 23-7 |

| 24-1  | USB Driver Files                         | 24-4 |

| 24-2  | USB Platform Source Files                | 24-4 |

| 24-3  | USB Platform Header Files                | 24-4 |

| 24-4  | USB Common Platform Files                | 24-5 |

| 24-5  | Default USB Settings                     | 24-7 |

| 25-1  | FlexCAN Driver Files                     | 25-2 |

| 26-1  | RTC Driver Files                         | 26-1 |

| 27-1  | Available Platforms                      | 27-1 |

| 27-2  | SIM Driver File List                     | 27-3 |

| 28-1  | WDOG Driver Files                        | 28-2 |

|       |                                          |      |

i.MX25 PDK Linux Reference Manual

# **Figures**

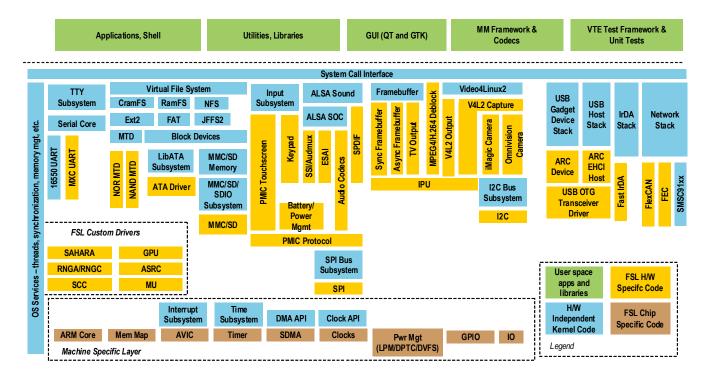

| 2-1  | BSP Block Diagram                        | 2-1  |

|------|------------------------------------------|------|

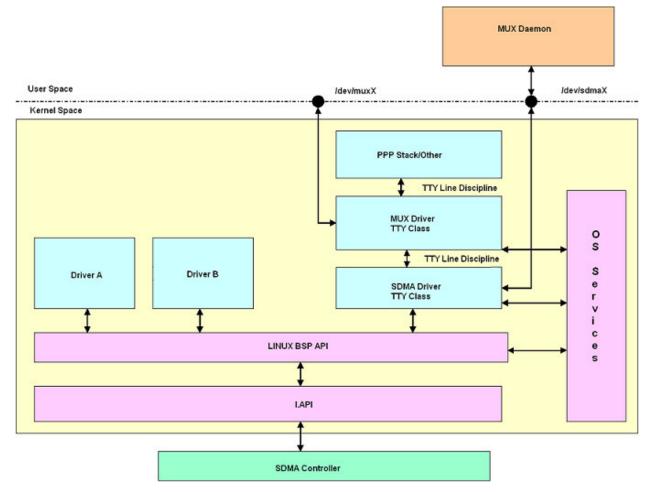

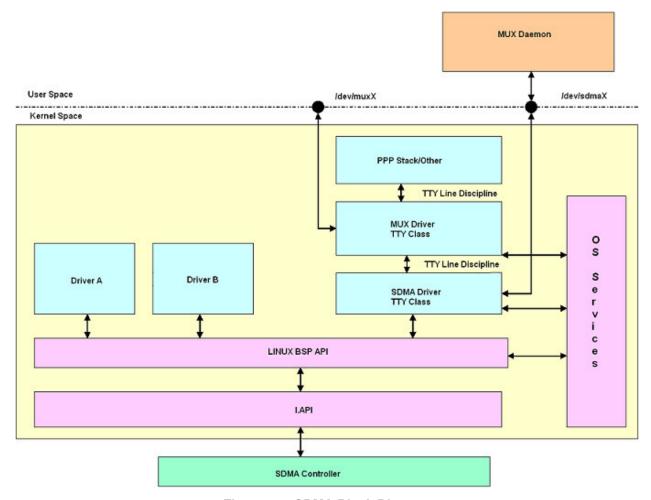

| 2-2  | SDMA Block Diagram                       | 2-4  |

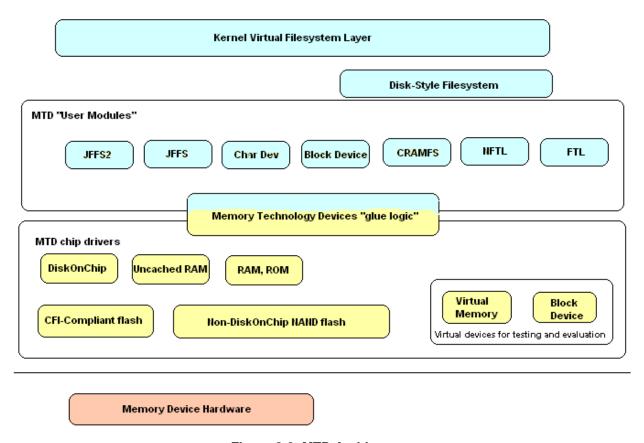

| 2-3  | MTD Architecture                         |      |

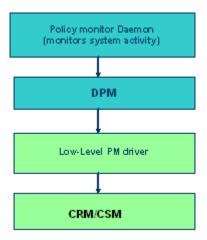

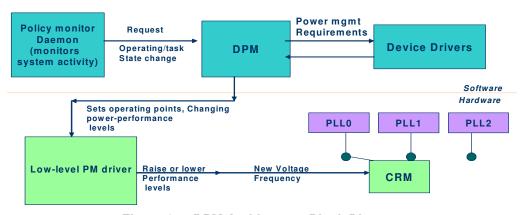

| 2-4  | DPM High Level Design                    | 2-15 |

| 2-5  | DPM Architecture Block Diagram           | 2-15 |

| 4-1  | SDMA Block Diagram                       |      |

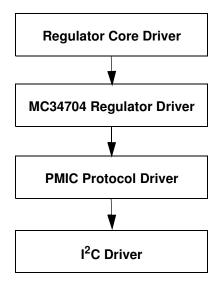

| 6-1  | MC34704 Regulator Driver Architecture    | 6-2  |

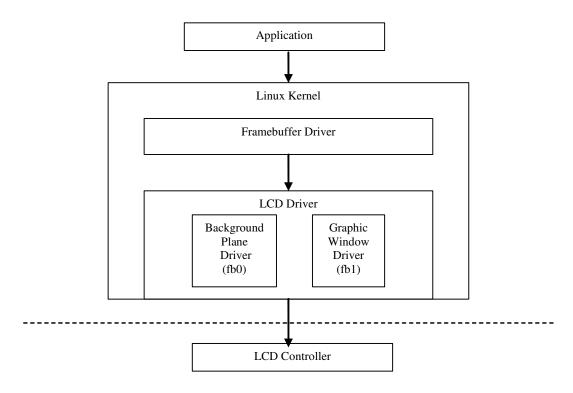

| 9-1  | LCD Driver Architecture                  | 9-3  |

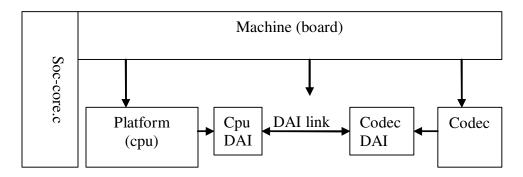

| 12-1 | ALSA SoC Software Architecture           | 12-1 |

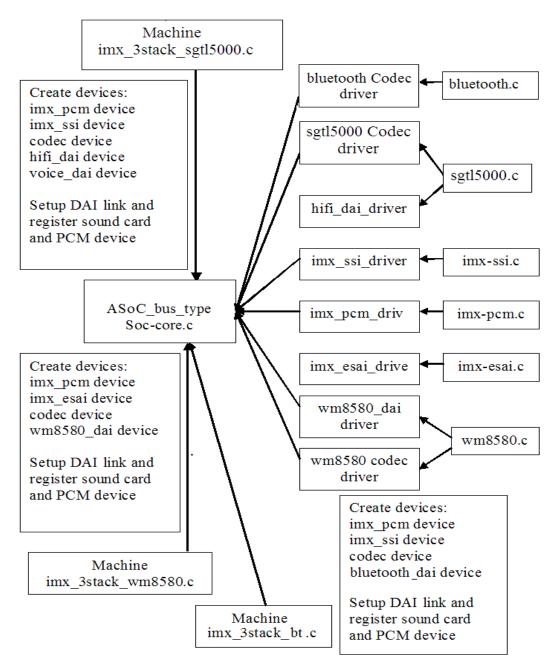

| 12-2 | ALSA SoC Source File Relationship        | 12-4 |

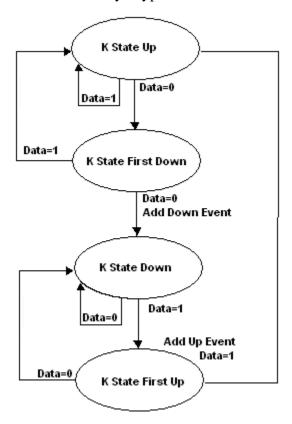

| 14-1 | Keypad Driver State Machine              | 14-2 |

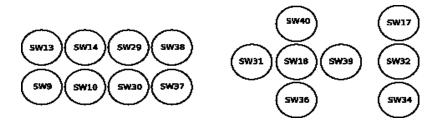

| 14-2 | Keypad Button Placement                  | 14-5 |

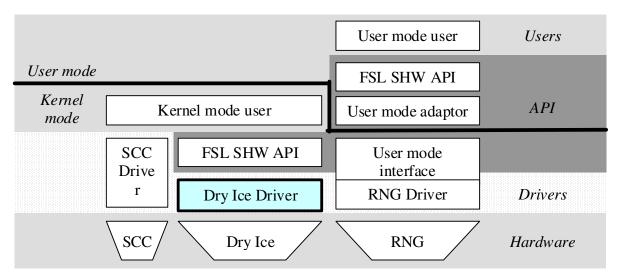

| 18-1 | Software Architecture                    | 18-2 |

| 19-1 | Secure RAM Block Diagram                 | 19-2 |

| 19-2 | Security Monitor Block Diagram           | 19-4 |

| 19-3 | Secure State Controller State Diagram    | 19-4 |

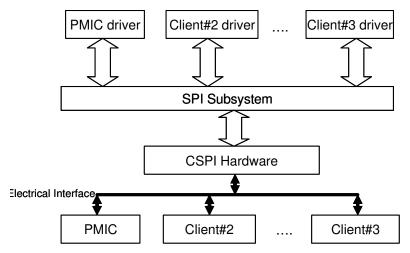

| 21-1 | SPI Subsystem                            |      |

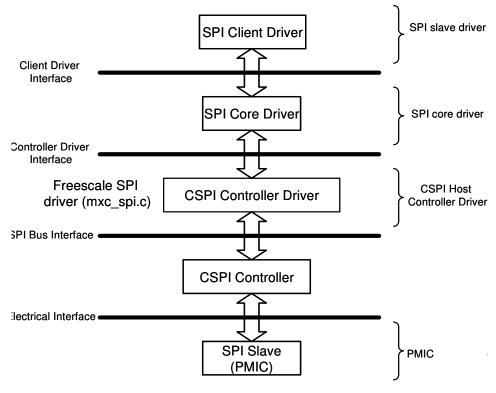

| 21-2 | Layering of SPI Drivers in SPI Subsystem | 21-2 |

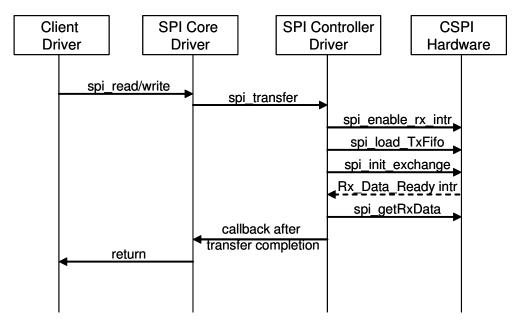

| 21-3 | CSPI Synchronous Operation               | 21-4 |

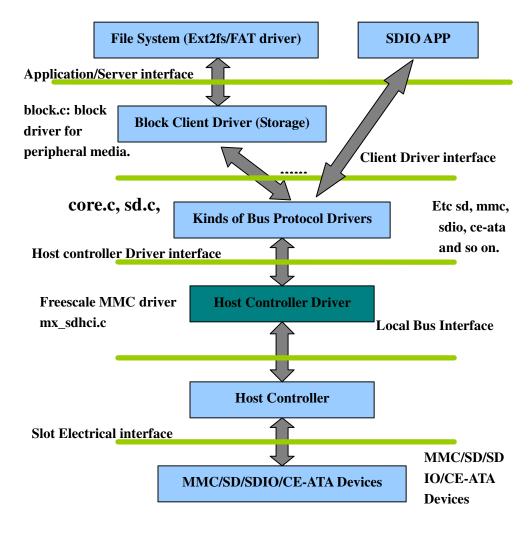

| 22-1 | MMC Drivers Layering                     | 22-3 |

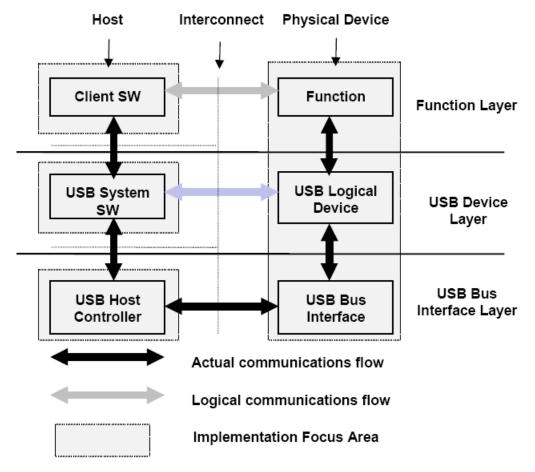

| 24-1 | USB Block Diagram                        |      |

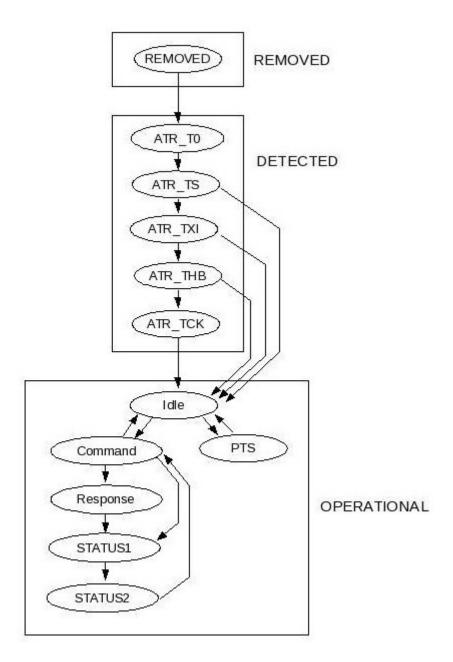

| 27-1 | SIM driver                               |      |

### **About This Book**

The Linux board support package (BSP) represents a porting of the Linux operating system (OS) to the i.MX processors and to their associated reference boards. The BSP supports many of the hardware features on the platforms, as well as most of the Linux OS features not dependent on any specific hardware feature.

### **Audience**

This document is targeted to individuals who will port the i.MX Linux BSP to customer-specific products. The audience is expected to have a working understanding of the Linux 2.6 kernel internals and driver models. An understanding of the i.MX processors is also required.

### **Conventions**

This document uses the following notational conventions:

- Courier monospaced type indicate commands, command parameters, code examples, and file and directory names.

- *Italic* type indicates replaceable command or function parameters.

- **Bold** type indicates function names.

# **Definitions, Acronyms, and Abbreviations**

The following table defines the acronyms and abbreviations used in this document.

### **Definitions and Acronyms**

| Term                   | Definition                                                                                                                                                               |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ADC                    | Asynchronous Display Controller                                                                                                                                          |  |

| address<br>translation | Address conversion from virtual domain to physical domain                                                                                                                |  |

| API                    | Application Programming Interface                                                                                                                                        |  |

| ARM <sup>®</sup>       | Advanced RISC Machines processor architecture                                                                                                                            |  |

| AUDMUX                 | Digital audio MUX—provides a programmable interconnection for voice, audio, and synchronous data routing between host serial interfaces and peripheral serial interfaces |  |

| BCD                    | Binary Coded Decimal                                                                                                                                                     |  |

| bus                    | A path between several devices through data lines                                                                                                                        |  |

| bus load               | The percentage of time a bus is busy                                                                                                                                     |  |

| CODEC                  | Coder/decoder or compression/decompression algorithm—used to encode and decode (or compress and decompress) various types of data                                        |  |

# **Definitions and Acronyms (continued)**

| Term       | Definition                                                                                                                                                                                                                                                                                                                                     |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CPU        | Central Processing Unit—generic term used to describe a processing core                                                                                                                                                                                                                                                                        |  |

| CRC        | Cyclic Redundancy Check—Bit error protection method for data communication                                                                                                                                                                                                                                                                     |  |

| CSI        | Camera Sensor Interface                                                                                                                                                                                                                                                                                                                        |  |

| DFS        | Dynamic Frequency Scaling                                                                                                                                                                                                                                                                                                                      |  |

| DMA        | Direct Memory Access—an independent block that can initiate memory-to-memory data transfers                                                                                                                                                                                                                                                    |  |

| DPM        | Dynamic Power Management                                                                                                                                                                                                                                                                                                                       |  |

| DRAM       | Dynamic Random Access Memory                                                                                                                                                                                                                                                                                                                   |  |

| DVFS       | Dynamic Voltage Frequency Scaling                                                                                                                                                                                                                                                                                                              |  |

| EMI        | External Memory Interface—controls all IC external memory accesses (read/write/erase/program) from all the masters in the system                                                                                                                                                                                                               |  |

| Endian     | Refers to byte ordering of data in memory.: little endian means that the least significant byte of the data is stored in a lower address than the most significant byte, in big endian, the order of the bytes is reversed                                                                                                                     |  |

| EPIT       | Enhanced Periodic Interrupt Timer—a 32-bit set and forget timer capable of providing precise interrupts at regular intervals with minimal processor intervention                                                                                                                                                                               |  |

| FCS        | Frame Checker Sequence                                                                                                                                                                                                                                                                                                                         |  |

| FIFO       | First In First Out                                                                                                                                                                                                                                                                                                                             |  |

| FIPS       | Federal Information Processing Standards—United States Government technical standards published by the National Institute of Standards and Technology (NIST). NIST develops FIPS when there are compelling Federal government requirements such as for security and interoperability but no acceptable industry standards                      |  |

| FIPS-140   | Security requirements for cryptographic modules—Federal Information Processing Standard 140-2(FIPS 140-2) is a standard that describes US Federal government requirements that IT products should meet for Sensitive, But Unclassified (SBU) use                                                                                               |  |

| Flash      | A non-volatile storage device similar to EEPROM, where erasing can only be done in blocks or the entire chip.                                                                                                                                                                                                                                  |  |

| Flash path | Path within ROM bootstrap pointing to an executable Flash application                                                                                                                                                                                                                                                                          |  |

| Flush      | Procedure to reach cache coherency. Refers to removing a data line from cache. This process includes cleaning the line, invalidating its VBR and resetting the tag valid indicator. The flush is triggered by a software command                                                                                                               |  |

| GPIO       | General Purpose Input/Output                                                                                                                                                                                                                                                                                                                   |  |

| hash       | Hash values are produced to access secure data. A hash value (or simply hash), also called a message digest, is a number generated from a string of text. The hash is substantially smaller than the text itself, and is generated by a formula in such a way that it is extremely unlikely that some other text produces the same hash value. |  |

| I/O        | Input/Output                                                                                                                                                                                                                                                                                                                                   |  |

| ICE        | In-Circuit Emulation                                                                                                                                                                                                                                                                                                                           |  |

| IP         | Intellectual Property                                                                                                                                                                                                                                                                                                                          |  |

| IPU        | Image Processing Unit —supports video and graphics processing functions and provides an interface to video/still image sensors and displays                                                                                                                                                                                                    |  |

| IrDA       | Infrared Data Association—a nonprofit organization whose goal is to develop globally adopted specifications for infrared wireless communication                                                                                                                                                                                                |  |

### i.MX25 PDK Linux Reference Manual

# **Definitions and Acronyms (continued)**

| Term                | Definition                                                                                                                                                                                                                                                                                                                                                                    |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ISR                 | Interrupt Service Routine                                                                                                                                                                                                                                                                                                                                                     |  |

| JTAG                | JTAG (IEEE Standard 1149.1) A standard specifying how to control and monitor the pins of compliant devices on a printed circuit board                                                                                                                                                                                                                                         |  |

| Kill                | Abort a memory access                                                                                                                                                                                                                                                                                                                                                         |  |

| KPP                 | KeyPad Port—16-bit peripheral used as a keypad matrix interface or as general purpose input/output (I/O)                                                                                                                                                                                                                                                                      |  |

| line                | Refers to a unit of information in the cache that is associated with a tag                                                                                                                                                                                                                                                                                                    |  |

| LRU                 | Least Recently Used—a policy for line replacement in the cache                                                                                                                                                                                                                                                                                                                |  |

| MMU                 | Memory Management Unit—a component responsible for memory protection and address translation                                                                                                                                                                                                                                                                                  |  |

| MPEG                | Moving Picture Experts Group—an ISO committee that generates standards for digital video compression and audio. It is also the name of the algorithms used to compress moving pictures and video                                                                                                                                                                              |  |

| MPEG<br>standards   | There are several standards of compression for moving pictures and video  • MPEG-1 is optimized for CD-ROM and is the basis for MP3  • MPEG-2 is defined for broadcast video in applications such as digital television set-top boxes and DVD  • MPEG-3 was merged into MPEG-2  • MPEG-4 is a standard for low-bandwidth video telephony and multimedia on the World-Wide Web |  |

| MQSPI               | Multiple Queue Serial Peripheral Interface—used to perform serial programming operations necessary to configure radio subsystems and selected peripherals                                                                                                                                                                                                                     |  |

| MSHC                | Memory Stick Host Controller                                                                                                                                                                                                                                                                                                                                                  |  |

| NAND Flash          | Flash ROM technology—NAND Flash architecture is one of two flash technologies (the other being NOR) used in memory cards such as the Compact Flash cards. NAND is best suited to flash devices requiring high capacity data storage. NAND flash devices offer storage space up to 512-Mbyte and offers faster erase, write, and read capabilities over NOR architecture       |  |

| NOR Flash           | See NAND Flash                                                                                                                                                                                                                                                                                                                                                                |  |

| PCMCIA              | Personal Computer Memory Card International Association—a multi-company organization that has developed a standard for small, credit card-sized devices, called PC Cards. There are three types of PCMCIA cards that have the same rectangular size (85.6 by 54 millimeters), but different widths                                                                            |  |

| physical<br>address | The address by which the memory in the system is physically accessed                                                                                                                                                                                                                                                                                                          |  |

| PLL                 | Phase Locked Loop—an electronic circuit controlling an oscillator so that it maintains a constant phase angle (a lock) on the frequency of an input, or reference, signal                                                                                                                                                                                                     |  |

| RAM                 | Random Access Memory                                                                                                                                                                                                                                                                                                                                                          |  |

| RAM path            | Path within ROM bootstrap leading to the downloading and the execution of a RAM application                                                                                                                                                                                                                                                                                   |  |

| RGB                 | The RGB color model is based on the additive model in which Red, Green, and Blue light are combined to create other colors. The abbreviation RGB come from the three primary colors in additive light models                                                                                                                                                                  |  |

| RGBA                | RGBA color space stands for Red Green Blue Alpha. The alpha channel is the transparency channel, and is unique to this color space. RGBA, like RGB, is an additive color space, so the more of a color placed, the lighter the picture gets. PNG is the best known image format that uses the RGBA color space                                                                |  |

| RNGA                | Random Number Generator Accelerator—a security hardware module that produces 32-bit pseudo random numbers as part of the security module                                                                                                                                                                                                                                      |  |

| ROM                 | Read Only Memory                                                                                                                                                                                                                                                                                                                                                              |  |

### i.MX25 PDK Linux Reference Manual

### **Definitions and Acronyms (continued)**

| Term             | Definition                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROM<br>bootstrap | Internal boot code encompassing the main boot flow as well as exception vectors                                                                                                                                                                                                                                                                                                              |

| RTIC             | Real-time integrity checker—a security hardware module                                                                                                                                                                                                                                                                                                                                       |

| SCC              | SeCurity Controller—a security hardware module                                                                                                                                                                                                                                                                                                                                               |

| SDMA             | Smart Direct Memory Access                                                                                                                                                                                                                                                                                                                                                                   |

| SDRAM            | Synchronous Dynamic Random Access Memory                                                                                                                                                                                                                                                                                                                                                     |

| SoC              | System on a Chip                                                                                                                                                                                                                                                                                                                                                                             |

| SPBA             | Shared Peripheral Bus Arbiter—a three-to-one IP-Bus arbiter, with a resource-locking mechanism                                                                                                                                                                                                                                                                                               |

| SPI              | Serial Peripheral Interface—a full-duplex synchronous serial interface for connecting low-/medium-bandwidth external devices using four wires. SPI devices communicate using a master/slave relationship over two data lines and two control lines: Also see SS, SCLK, MISO, and MOSI                                                                                                        |

| SRAM             | Static Random Access Memory                                                                                                                                                                                                                                                                                                                                                                  |

| SSI              | Synchronous-Serial Interface—standardized interface for serial data transfer                                                                                                                                                                                                                                                                                                                 |

| TBD              | To Be Determined                                                                                                                                                                                                                                                                                                                                                                             |

| UART             | Universal Asynchronous Receiver/Transmitter—asynchronous serial communication to external devices                                                                                                                                                                                                                                                                                            |

| UID              | Unique ID-a field in the processor and CSF identifying a device or group of devices                                                                                                                                                                                                                                                                                                          |

| USB              | Universal Serial Bus—an external bus standard that supports high speed data transfers. The USB 1.1 specification supports data transfer rates of up to 12Mb/s and USB 2.0 has a maximum transfer rate of 480 Mbps. A single USB port can be used to connect up to 127 peripheral devices, such as mice, modems, and keyboards. USB also supports Plug-and-Play installation and hot plugging |

| USBOTG           | USB On The Go—an extension of the USB 2.0 specification for connecting peripheral devices to each other. USBOTG devices, also known as dual-role peripherals, can act as limited hosts or peripherals themselves depending on how the cables are connected to the devices, and they also can connect to a host PC                                                                            |

| word             | A group of bits comprising 32 bits                                                                                                                                                                                                                                                                                                                                                           |

# **Suggested Reading**

The following documents contain information that supplements this guide:

- i.MX25 PDK Linux Quick Start Guide

- BSP API Document (BSP Doxygen Code Documentation)

- i.MX25 PDK Linux User's Guide

- i.MX25 PDK Hardware User's Guide

- i.MX25 Multimedia Applications Processor Reference Manual

- [KERN] *Linux kernel coding style*. This is included in Linux distributions as the file Documentation/CodingStyle

- [WSAS] WSAS Coding Conventions, version 0.4

- [ASM] WSAS Assembly Code Conventions

- [DOXY] WSAS Guidelines for Writing Doxygen Comments

# Chapter 1 Introduction

The i.MX family Linux board support package (BSP) supports the Linux operating system (OS) on the following processor:

• i.MX25 Applications Processor

Because of an order from the United States International Trade Commission, BGA-packaged product lines and part numbers indicated here currently are not available from Freescale for import or sale in the United States prior to September 2010: i.MX25,

### NOTE

The family of all i.MX processors is known as the i.MX platforms. This term is used in sections that apply to any of these application processors.

The purpose of this software package is to support Linux on the i.MX family of integrated circuits (ICs) and their associated platforms (3-Stack board). It provides the software necessary to interface the standard open-source Linux kernel to the i.MX hardware. The goal is to enable Freescale customers to rapidly build products based on i.MX devices that use the Linux OS.

The BSP is not a platform or product reference implementation. It does not contain all of the product-specific drivers, hardware-independent software stacks, GUI components, JVM, and applications required for a product. Some of these are made available in their original open-source form as part of the base kernel.

The BSP is not intended to be used for silicon verification. While it can play a role in this, the BSP functionality and the tests run on the BSP do not have sufficient coverage to replace traditional silicon verification test suites.

# 1.1 Software Base

The i.MX BSP is based on version 2.6.31 of the Linux kernel from the official Linux kernel web site (<a href="http://www.kernel.org">http://www.kernel.org</a>). It is enhanced with features provided by Freescale.

### Introduction

# 1.2 Features

Table 1-1 describes the features supported by the Linux BSP for specific platforms.

**Table 1-1. Linux BSP Supported Features**

| Feature       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Chapter Source                                        | Applicable Platform |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------|