# FMN1xx5SBS(130ball) Datasheet

- Do not leave this document unattended.

- This information contained in this document covered by the non-discloser agreement.

- Do not reproduce this document.

- This document is property of Fidelix Co., Ltd. and maybe be required to be returned at any time.

Fidelix Co., Ltd.

#### **Document Title**

Stacked Multi-Chip Product(MCP)

### **Revision History**

|   | Revision No. | History       | Draft date                   | Remark      |

|---|--------------|---------------|------------------------------|-------------|

| ſ | 0.0          | Initial Draft | May. 21 <sup>st</sup> , 2013 | Preliminary |

# Stacked Multi-Chip Product(MCP)

### 1.8V NAND Flash Memory and Mobile SDR/DDR

### 1. MCP Features

- Supply Voltages : 1.8V Operation

VCC : 1.7V~1.95V for Core/IO Power

- Operating Temperature Range

Industrial Part : -40°C ~ 85°C

- Package Type :

- 130-ball FBGA, 8x9mm<sup>2</sup>, 1.0T, 0.65mm Ball Pitch

- Lead & Halogen Free

### 2. MCP Selection Guide

### [1G NAND + 512Mb DDR SDRAM]

| MCP Part Number | Flash    | LP-DRAM    | DRAM   | Individua   | al Datasheet    | PKG Type |

|-----------------|----------|------------|--------|-------------|-----------------|----------|

|                 | 1 10511  |            | Freq.  | Flash       | LP-DRAM         | The type |

| FMN1ED5SBS-50IA | 1Gb(x8)  | 512Mb(x16) | 200Mhz | FMND1G08S3S | FMD8C16LAW-25EI | 130ball  |

| FMN1SD5SBS-50IA | 1Gb(x16) | 512Mb(x16) | 200Mhz | FMND1G16S3S | FMD8C16LAW-25EI | 130ball  |

### [1G NAND + 512Mb SDR SDRAM]

| MCP Part Number | CP Part Number   Flash     P-DRAM |            | DRAM   | Individua   | PKG Type        |           |

|-----------------|-----------------------------------|------------|--------|-------------|-----------------|-----------|

|                 | 1 Idolf                           |            | Freq.  | Flash       | LP-DRAM         | i no ijpo |

| FMN1ES5SBS-60IA | 1Gb(x8)                           | 512Mb(x16) | 166Mhz | FMND1G08S3S | FMS8C16LAW-60EI | 130ball   |

| FMN1SS5SBS-60IA | 1Gb(x16)                          | 512Mb(x16) | 166Mhz | FMND1G16S3S | FMS8C16LAW-60EI | 130ball   |

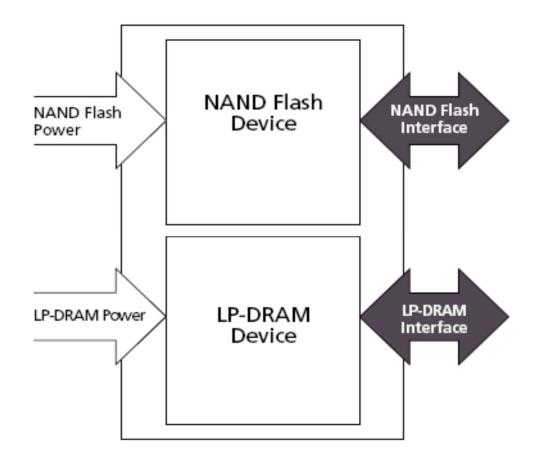

# 3. MCP Block Diagram

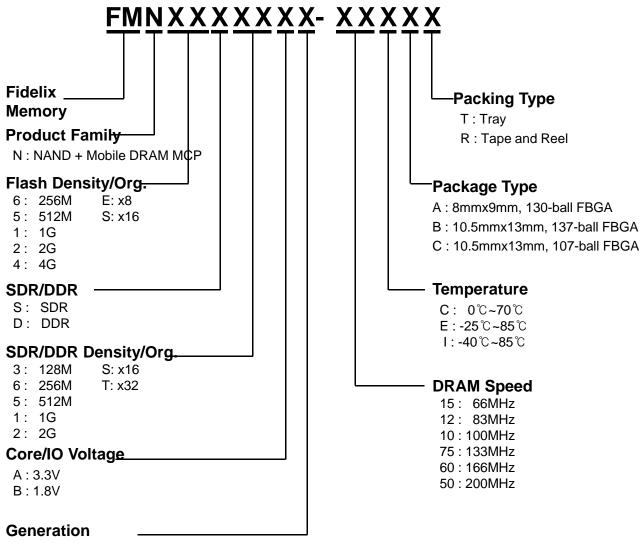

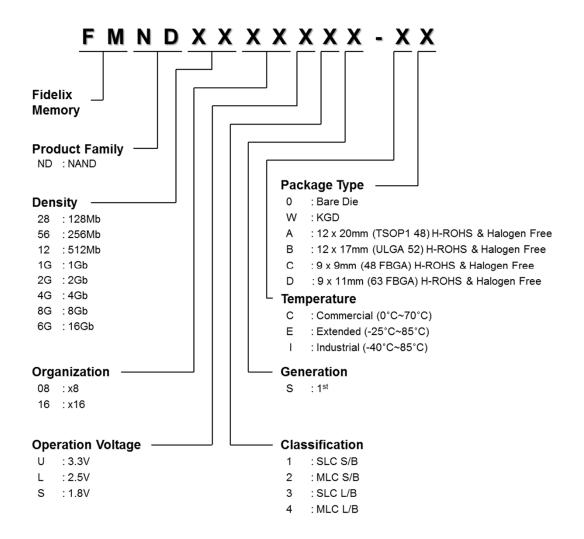

## 4. MCP Part Numbering System

S : 1<sup>st</sup>

|   | <br>1     | 2         | 3   | 4          | 5               | 6    | 7          | 8               | 9    | 10                   |

|---|-----------|-----------|-----|------------|-----------------|------|------------|-----------------|------|----------------------|

| Α | NC        | NC        | RE# | CLE        | VCC             | CE#  | WEn#       | VDD             | vss  | NC                   |

| В | vss       | <b>A4</b> | WP# | ALE        | VSSn            | R/B# | DQ15       | DQ14            | VDDQ | VSSQ                 |

| с | VDD       | <b>A5</b> | A7  | <b>A9</b>  |                 | DQ11 | DQ13       | DQ12            | VSSQ | VDDQ                 |

| D | <b>A6</b> | <b>A8</b> | СКЕ | NC         | UDQS            | NC   |            | DQ10            | VDDQ | VSSQ                 |

| Е | A12       | A11       | NC  | NC         | NC              |      | NC         | NC              | VSSQ | VDDQ                 |

| F | NC        | RAS#      | NC  | NC         | NC              | NC   | NC         | CLK             | VDDQ | VSSQ                 |

| G | VDD       | CAS#      | NC  | NC         | NC              | NC   | NC         |                 | vss  | VDD                  |

| Н | vss       | CS#       | BAO | NC         | NC              | NC   |            |                 | VSSQ | VDDQ                 |

| J | WE#       | BA1       | A10 | A0         | DQ7             | NC   | DQ6        | DQ4             | VDDQ | vssq                 |

| к | A1        | <b>A2</b> | A3  | DQO        | DQ1             | DQ2  | DQ3        |                 | VDDQ | vssq                 |

| L | VDD       | vss       | RFU | NC         | 103             | 105  | NC         | 107             | vssq | VDDQ                 |

| М | 100       | 101       | 102 | NC         | VCC             | 106  | NC         | NC              | VDDQ | VSSQ                 |

| N | NC        | NC        | NC  | NC         | NC              | VSSn | 104        | VDD             | vss  | NC                   |

|   |           |           |     |            |                 |      |            |                 |      |                      |

|   |           |           |     | $\bigcirc$ | NAND            |      | $\bigcirc$ | LPDDR<br>-DRAM  |      |                      |

|   |           |           |     | VCC        | NAND-<br>Supply |      | VDD        | LPDDR<br>Supply |      | LPDDR –<br>DQ Supply |

|   |           |           |     | VSSn       | NAND-<br>GND    |      | vss        | LPDDR-<br>GND   | vssq | LPDDR -<br>DQ GND    |

# 5-1. MCP Package Pin Configuration (130-ball FBGA, Top View) <u>NAND(x8) + DDR(x16)</u>

#### 1 2 3 4 5 6 7 8 9 10 NC CE# (WEn# VDD (vss NC NC RE# (vcc Α vss **A**4 (DQ15 (DQ14) VDDQ (vssq) WP# (ALE) (VSSn) (R/B#) В VDD A5 A7 (DQ13 (DQ12) (vssq) VDDQ С A9 СКЕ (UDQM) VDDQ (vssa) **A6 A8** NC NC NC D A12 A11 NC NC (vssq) VDDQ NC NC ( NC ) Ε NC RAS# NC CLK VDDQ NC NC NC NC (vssq) F VDD CAS# NC NC NC ( NC ) NC NC (vss) VDD G CS# (vssq) VDDQ (vss) NC ) BA0 NC NC NC н WE# DQ6 DQ4 VDDQ (vssq) BA1 A10 **A0** NC J **A1** A2 DQ5 VDDQ (vssq) **A3** DQ0 κ (vss) NC 107 (vssq) VDDQ VDD RFU ( 105 ) NC ( 103 ) L 100 ( 101 ( 102 ) NC vcc ( 106 ) NC NC (VDDQ) (vssq) Μ 104 VDD NC NC NC NC NC VSSn ังรร NC Ν LPSDR -DRAM NAND LPSDR -Supply LPSDR – DQ Supply NAND-Supply VDD VDDQ vcc NAND-GND LPSDR-GND LPSDR -DQ GND ้งรร VSSn vssa

# 5-2. MCP Package Pin Configuration (130-ball FBGA, Top View) <u>NAND(x8) + SDR(x16)</u>

|   | <br>1     | 2         | 3   | 4          | 5               | 6    | 7           | 8               | 9    | 10                   |

|---|-----------|-----------|-----|------------|-----------------|------|-------------|-----------------|------|----------------------|

| A | NC        | NC        | RE# | CLE        | VCC             | CE#  | WEn#        | VDD             | vss  | NC                   |

| В | vss       | <b>A4</b> | WP# | ALE        | VSSn            | R/B# | DQ15        | DQ14            | VDDQ | vssq                 |

| С | VDD       | <b>A5</b> | A7  | <b>A9</b>  | DQ9             | DQ11 | DQ13        | DQ12            | vssq | VDDQ                 |

| D | <b>A6</b> | <b>A8</b> | СКЕ | NC         | UDQS            | NC   |             | DQ10            | VDDQ | vssq                 |

| Е | A12       | A11       | NC  | NC         | NC              | DQ8  | NC          | NC              | vssq | VDDQ                 |

| F | NC        | RAS#      | NC  | NC         | NC              | NC   | NC          | CLK             | VDDQ | vssq                 |

| G | VDD       | CAS#      | NC  | NC         | NC              | NC   | NC          |                 | vss  | VDD                  |

| н | vss       | CS#       | BAO | NC         | NC              | NC   |             |                 | vssq | VDDQ                 |

| J | WE#       | BA1       | A10 | AO         | DQ7             | NC   |             | DQ4             | VDDQ | vssq                 |

| К | <b>A1</b> | <b>A2</b> | A3  |            | DQ1             | DQ2  |             |                 | VDDQ | vssq                 |

| L | VDD       | vss       | RFU | NC         | 103             | 105  | <b>IO14</b> | 107             | VSSQ | VDDQ                 |

| м | 100       | 101       | 102 | 1010       | VCC             | 106  | I013        | IO15            | VDDQ | vssq                 |

| N | NC        | 108       | 109 | 1011       | I012            | VSSn | 104         | VDD             | vss  | NC                   |

|   |           |           |     |            |                 |      |             |                 |      |                      |

|   |           |           |     | $\bigcirc$ | NAND            |      | $\bigcirc$  | LPDDR<br>-DRAM  |      |                      |

|   |           |           |     | VCC        | NAND-<br>Supply |      | VDD         | LPDDR<br>Supply |      | LPDDR –<br>DQ Supply |

|   |           |           |     | VSSn       | NAND-<br>GND    |      | vss         | LPDDR-<br>GND   | vssq | LPDDR -<br>DQ GND    |

# 5-3. MCP Package Pin Configuration (130-ball FBGA, Top View) <u>NAND(x16) + DDR(x16)</u>

|   | <br>1 | 2         | 3   | 4          | 5               | 6    | 7           | 8               | 9    | 10                   |

|---|-------|-----------|-----|------------|-----------------|------|-------------|-----------------|------|----------------------|

| A | NC    | NC        | RE# | CLE        | VCC             | CE#  | WEn#        | VDD             | VSS  | NC                   |

| В | vss   | <b>A4</b> | WP# | ALE        | VSSn            | R/B# |             | DQ14            | VDDQ | VSSQ                 |

| С | VDD   | <b>A5</b> | A7  | <b>A9</b>  |                 | DQ11 | DQ13        | DQ12            | vssq | VDDQ                 |

| D | A6    | <b>A8</b> | СКЕ | NC         | NC              | NC   |             | DQ10            | VDDQ | VSSQ                 |

| Е | A12   | A11       | NC  | NC         | NC              |      | NC          | NC              | vssq | VDDQ                 |

| F | NC    | RAS#      | NC  | NC         | NC              | NC   | NC          | CLK             | VDDQ | VSSQ                 |

| G | VDD   | CAS#      | NC  | NC         | NC              | NC   | NC          | NC              | vss  | VDD                  |

| н | vss   | CS#       | BAO | NC         | NC              | NC   | NC          |                 | vssq | VDDQ                 |

| J | WE#   | BA1       | A10 | AO         | DQ7             | NC   | DQ6         | DQ4             | VDDQ | VSSQ                 |

| к | A1    | <b>A2</b> | A3  |            | DQ1             | DQ2  | DQ3         | DQ5             | VDDQ | VSSQ                 |

| L | VDD   | vss       | RFU | NC         | 103             | 105  | <b>IO14</b> | 107             | vssq | VDDQ                 |

| М | 100   | 101       | 102 | 1010       | VCC             | 106  | <b>IO13</b> | 1015            | VDDQ | VSSQ                 |

| N | NC    | 108       | 109 | 1011       | 1012            | VSSn | 104         | VDD             | vss  | NC                   |

|   |       |           |     |            |                 |      |             |                 |      |                      |

|   |       |           |     | $\bigcirc$ | NAND            |      | $\bigcirc$  | LPSDR<br>-DRAM  |      |                      |

|   |       |           |     | VCC        | NAND-<br>Supply |      | VDD         | LPSDR<br>Supply |      | LPSDR –<br>DQ Supply |

|   |       |           |     | VSSn       | NAND-<br>GND    |      | VSS         | LPSDR-<br>GND   | vssq | LPSDR -<br>DQ GND    |

# 5-4. MCP Package Pin Configuration (130-ball FBGA, Top View) <u>NAND(x16) + SDR(x16)</u>

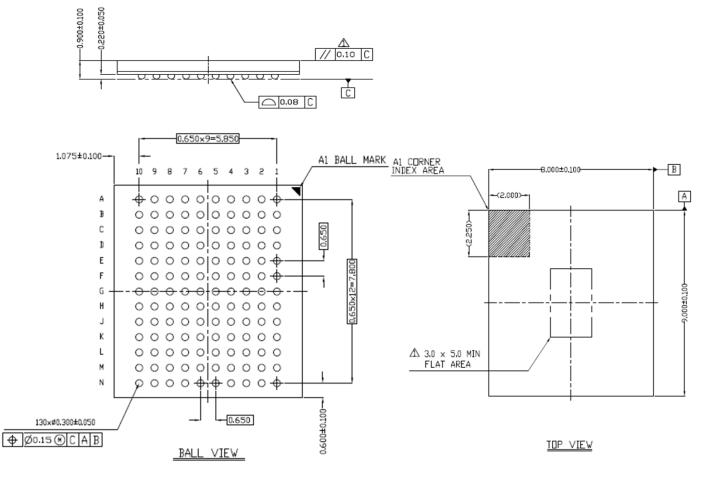

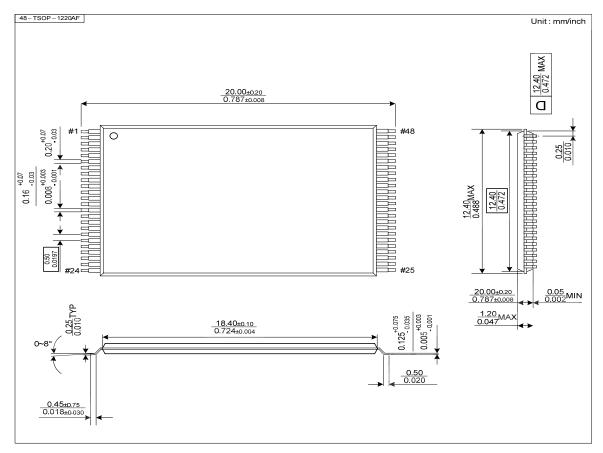

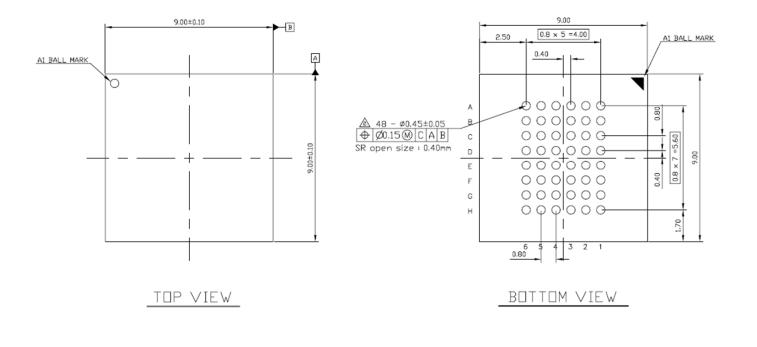

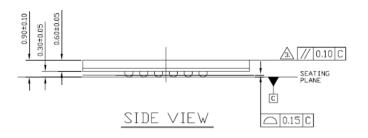

### 5-5. 130-ball FBGA Package Dimension (8mm x 9mm)

**SLC NAND FLASH**

# **SLC NAND FLASH**

#### Document Title 1Gbit, 4Gbit SLC NAND FLASH

#### **Revision History**

| Revision<br>No. | History              | Draft date                   | Remark      |

|-----------------|----------------------|------------------------------|-------------|

| 0.0             | Initial Draft        | May. 20 <sup>th</sup> , 2013 | Preliminary |

| 0.1             | Editorial Correction | Jun. 04 <sup>th</sup> , 2013 | Preliminary |

**Notice to Readers:** This document states the current technical specifications regarding the Fidelix product(s) described herein. Each product described herein may be designated as Advance Information, Preliminary, or Full Production. See Notice On Data Sheet Designations for definitions.

# **SLC NAND FLASH**

## **Notice On Data Sheet Designations**

Fidelix issues data sheets with Advance Information or Preliminary designations to advise readers of product information or intended specifications throughout the product life cycle, including development, qualification, initial production, and full production. In all cases, however, readers are encouraged to verify that they have the latest information before finalizing their design. The following descriptions of Fidelix data sheet designations are presented here to highlight their presence and definitions.

#### **Advance Information**

The Advance Information designation indicates that Fidelix is developing one or more specific products, but has not committed any design to production. Information presented in a document with this designation is likely to change, and in some cases, development on the product may discontinue. Fidelix therefore places the following conditions upon Advance Information content:

"This document contains information on one or more products under development at Fidelix

The information is intended to help you evaluate this product. Do not design in this product without contacting the factory. Fidelix reserves the right to change or discontinue work on this proposed product without notice."

#### Preliminary

The Preliminary designation indicates that the product development has progressed such that a commitment to production has taken place. This designation covers several aspects of the product life cycle, including product qualification, initial production, and the subsequent phases in the manufacturing process that occur before full production is achieved. Changes to the technical specifications presented in a Preliminary document should be expected while keeping these aspects of production under consideration. Fidelix places the following conditions upon Preliminary content:

"This document states the current technical specifications regarding the Fidelix product(s) described herein. The Preliminary status of this document indicates that product qualification has been completed, and that initial production has begun. Due to the phases of the manufacturing process that require maintaining efficiency and quality, this document may be revised by subsequent versions or modifications due to changes in technical specifications."

#### Combination

Some data sheets contain a combination of products with different designations (Advance Information, Preliminary, or Full Production). This type of document distinguishes these products and their designations wherever necessary, typically on the first page, the ordering information page, and pages with the DC Characteristics table and the AC Erase and Program table (in the table notes). The disclaimer on the first page refers the reader to the notice on this page.

#### Full Production (No Designation on Document)

When a product has been in production for a period of time such that no changes or only nominal changes are expected, the Preliminary designation is removed from the data sheet. Nominal changes may include those affecting the number of ordering part numbers available, such as the addition or deletion of a speed option, temperature range, package type, or VIO range. Changes may also include those needed to clarify a description or to correct a typographical error or incorrect specification. Fidelix applies the following conditions to documents in this category:

"This document states the current technical specifications regarding the Fidelix product(s) described herein. Fidelix deems the products to have been in sufficient production volume such that subsequent versions of this document are not expected to change. However, typographical or specification corrections, or modifications to the valid combinations offered may occur."

Questions regarding these document designations may be directed to your local sales office.

# **SLC NAND FLASH**

## **Distinctive Characteristics**

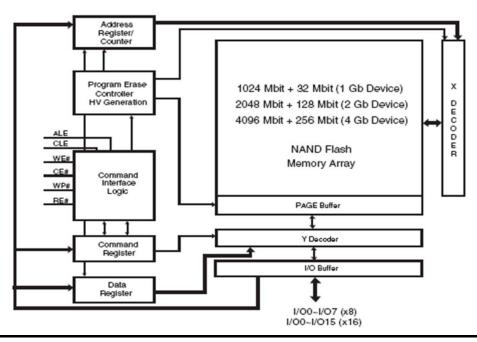

#### Density

- 1 Gbit / 2 Gbit / 4 Gbit

#### Architecture

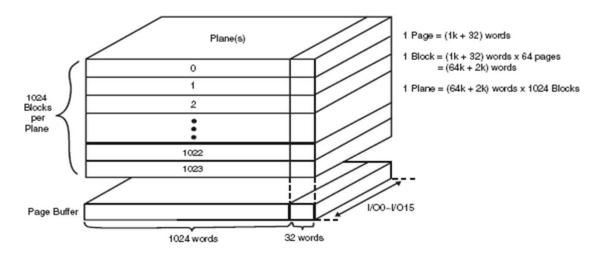

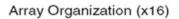

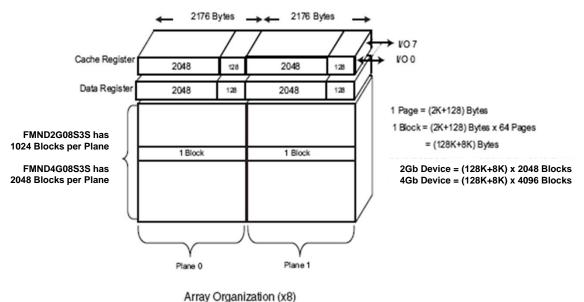

- Input / Output Bus Width: 8-bits / 16-bits

- Page Size:

- x8 1 Gbit: (2048 + 64) bytes; 64-byte spare area

- 2,4 Gbit: (2048 + 128) bytes; 128-byte spare area - x16

- 1 Gbit: (1024 + 32) words; 32-word spare area 2,4 Gbit: (1024 + 64) words; 64-word spare area

- Block Size: 64 Pages

- x8

- 1 Gbit: (128k + 4k) bytes

- 2,4 Gbit: (128k + 8k) bytes

- x16

- 1 Gbit: (64k + 2k) words

- 2,4 Gbit: (64k + 4k) words

- Plane Size:

- x8

- 1 Gbit: 1024 Blocks per Plane or (128M + 4M) bytes 2 Gbit: 1024 Blocks per Plane or (128M + 8M) bytes

- 4 Gbit: 2048 Blocks per Plane or (256M + 16M) bytes

- x16 1 Gbit: 1024 Blocks per Plane or (64M + 2M) words

- 2 Gbit: 1024 Blocks per Plane or (64M + 4M) words

- 4 Gbit: 2048 Blocks per Plane or (128M + 8M) words

- Device Size:

- 1 Gbit: 1 Plane per Device or 128 Mbyte

- 2 Gbit: 2 Planes per Device or 256 Mbyte

- 4 Gbit: 2 Planes per Device or 512 Mbyte

#### NAND Flash Interface

- Open NAND Flash Interface (ONFI) 1.0 compliant

- Address, Data, and Commands multiplexed

### Supply Voltage

- 1.8V device: VCC = 1.7V ~ 1.95V

- Security

- One Time Programmable (OTP) area

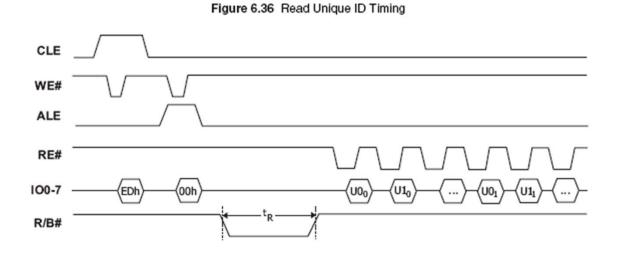

- Serial number (unique ID)

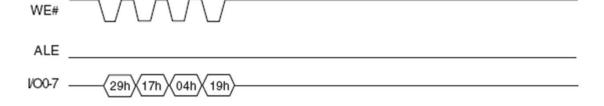

- Hardware program/erase disabled during power transition

#### **Additional Features**

- 2Gb and 4 Gb parts support Multiplane Program and Erase commands

- Supports Copy Back Program

- 2/4 Gb parts support Multiplane Copy Back Program

- Supports Read Cache

- **Electronic Signature**

- Manufacturer ID: 01h

- **Operating Temperature**

- Commercial: 0°C to 70°C - Extended: -30°C to 85°C

- Industrial: -40°C to 85°C

## Performance

- Page Read / Program

- Random access: 25 µs (Max) (FMND1GxxS3S)

- Random access: 30 µs (Max) (FMND2GxxS3S/FMND4GxxS3S)

- Sequential access: 45 ns (Min)

- Program time / Multiplane Program time: 300 µs (Typ)

- Block Erase

- Block Erase time: 3.0 ms (Typ)

- **Block Erase / Multiplane Erase** (FMND2GxxS3S, FMND4GxxS3S)

- Block Erase time: 3.5 ms (Typ)

#### Reliability

- 100,000 Program / Erase cycles (Typ)

- (with 4-bit ECC per 528 bytes (x8) or 264 words (x16))

- 10 Year Data retention (Typ)

- Block zero is a valid block and will be valid for at least 1000 program-erase cycles with ECC

#### **Package Options**

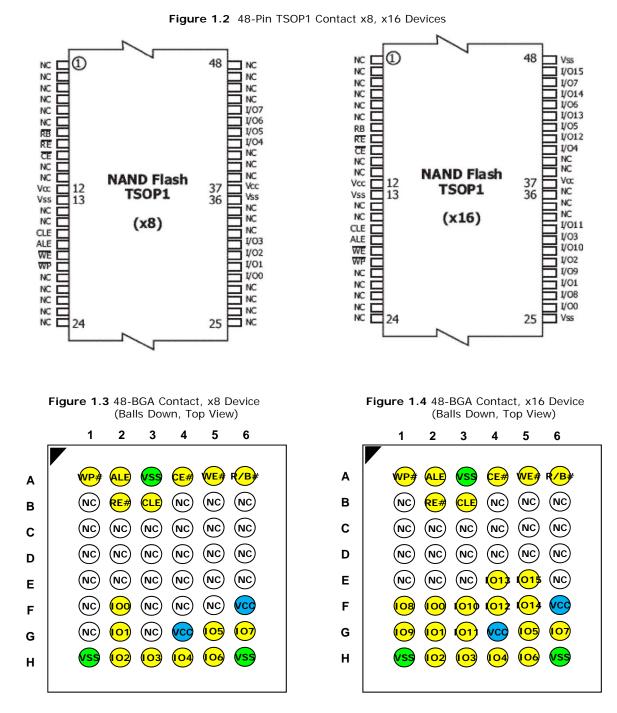

- 48-Pin TSOP 12 x 20 x 1.2 mm 48-Ball BGA 9 x 9 x 1 mm

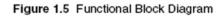

## **1. GENERAL DESCRIPTION**

The Fidelix FMND1GxxS3S, FMND2GxxS3S, and FMND4GxxS3S series is offered in 1.8 VCC and VCCQ power supply, and with x8 or x16 I/O interface. Its NAND cell provides the most cost-effective solution for the solid state mass storage market. The memory is divided into blocks that can be erased independently so it is possible to preserve valid data while old data is erased. The page size for x8 is (2048 + spare) bytes; for x16 (1024 + spare) words.

Each block can be programmed and erased up to 100,000 cycles with ECC (error correction code) on. To extend the lifetime of NAND flash devices, the implementation of an ECC is mandatory.

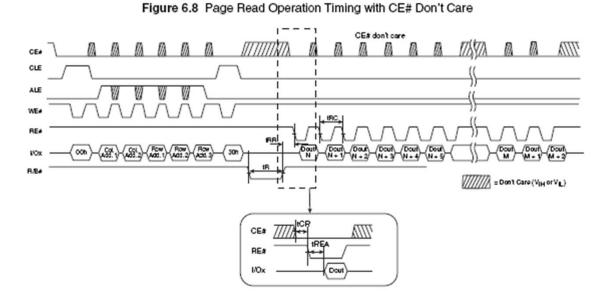

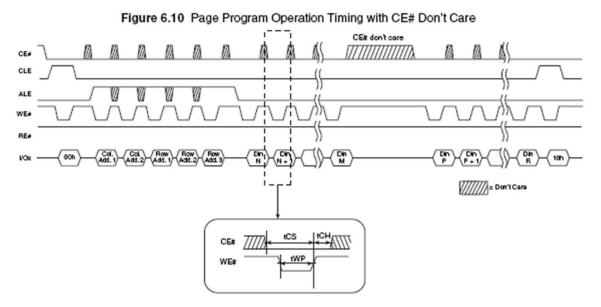

The chip supports CE# don't care function. This function allows the direct download of the code from the NAND flash memory device by a microcontroller, since the CE# transitions do not stop the read operation. The devices have a Read Cache feature that improves the read throughput for large files. During cache reading, the devices load the data in a cache register while the previous data is transferred to the I/O buffers to be read.

Like all other 2-kB page NAND flash devices, a program operation typically writes 2 kbytes (x8), or 1 kword (x16) in 300 µs and an erase operation can typically be performed in 3 ms (FMND1GxxS3S) on a 128-kB block (x8) or 64-kword block (x16). In addition, thanks to multiplane architecture, it is possible to program two pages at a time (one per plane) or to erase two blocks at a time (again, one per plane). The multiplane architecture allows program time to be reduced by 40% and erase time to be reduced by 50%.

In multiplane operations, data in the page can be read out at 45 ns cycle time per byte. The I/O pins serve as the ports for command and address input as well as data input/output. This interface allows a reduced pin count and easy migration towards different densities, without any rearrangement of the footprint.

Commands, Data, and Addresses are asynchronously introduced using CE#, WE#, ALE, and CLE control pins. The on-chip Program/Erase Controller automates all read, program, and erase functions including pulse repetition, where required, and internal verification and margining of data. A WP# pin is available to provide hardware protection against program and erase operations.

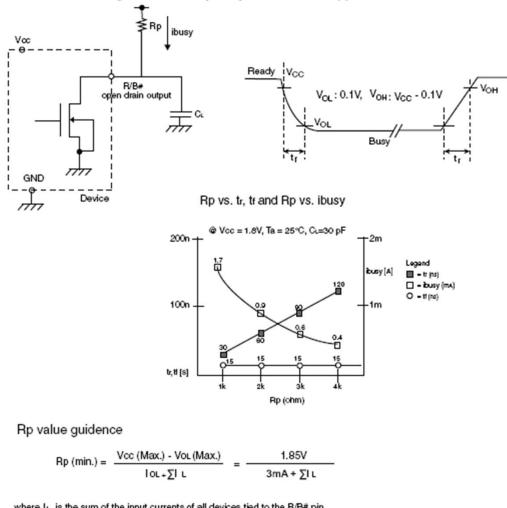

The output pin R/B# (open drain buffer) signals the status of the device during each operation. It identifies if the program/erase/read controller is currently active. The use of an open-drain output allows the Ready/Busy pins from several memories to connect to a single pull-up resistor. In a system with multiple memories the R/B# pins can be connected all together to provide a global status signal.

The Reprogram function allows the optimization of defective block management — when a Page Program operation fails the data can be directly programmed in another page inside the same array section without the time consuming serial data insertion phase.

Multiplane Copy Back is also supported. Data read out after Copy Back Read (both for single and multiplane cases) is allowed.

In addition, Cache Program and Multiplane Cache Program operations improve the programing throughput by programing data using the cache register.

The devices provide two innovative features: Page Reprogram and Multiplane Page Reprogram. The Page Reprogram re-programs one page. Normally, this operation is performed after a failed Page Program operation. Similarly, the Multiplane Page Reprogram re-programs two pages in parallel, one per plane. The first page must be in the first plane while the second page must be in the second plane. The Multiplane Page Reprogram operation is performed after a failed Multiplane Page Reprogram and Multiplane Page Reprogram guarantee improved performance, since data insertion can be omitted during re-program operations.

The devices come with the following security features:

- OTP (one time programmable) area, which is a restricted access area where sensitive data/code can be stored permanently.

- Serial number (unique identifier), which allows the devices to be uniquely identified.

These security features are subject to an NDA (non-disclosure agreement) and are, therefore, not described in the data sheet. For more details about them, contact your nearest Fidelix sales office.

| Device      | Densit                | y (bits)            | Number of Planes | Number of Blocks<br>per Plane |  |

|-------------|-----------------------|---------------------|------------------|-------------------------------|--|

| Device      | Main                  | Spare               | Number of Planes |                               |  |

| FMND1GxxS3S | 128M x 8<br>64M x 16  |                     |                  | 1024                          |  |

| FMND2GxxS3S | 256M x 8<br>128M x 16 | 16M x 8<br>8M x 16  | 2                | 1024                          |  |

| FMND4GxxS3S | 512M x 8<br>256M x 16 | 32M x 8<br>16M x 16 | 2                | 2048                          |  |

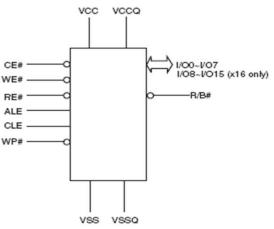

### 1.1 Logic Diagram

Figure 1.1 Logic Diagram

Table 1.1 Signal Names

| 1/07 - 1/00 (x8)   | Data land (Catalat          |  |  |  |  |

|--------------------|-----------------------------|--|--|--|--|

| I/O8 - I/O15 (x16) | Data Input / Outputs        |  |  |  |  |

| CLE                | Command Latch Enable        |  |  |  |  |

| ALE                | Address Latch Enable        |  |  |  |  |

| CE#                | Chip Enable                 |  |  |  |  |

| RE#                | Read Enable<br>Write Enable |  |  |  |  |

| WE#                |                             |  |  |  |  |

| WP#                | Write Protect               |  |  |  |  |

| R/B#               | Read/Busy                   |  |  |  |  |

| VCC                | Power Supply                |  |  |  |  |

| VSS                | Ground                      |  |  |  |  |

| NC                 | Not Connected               |  |  |  |  |

Rev. 0.1, Jun. '13

**Confidential**

### **SLC NAND FLASH**

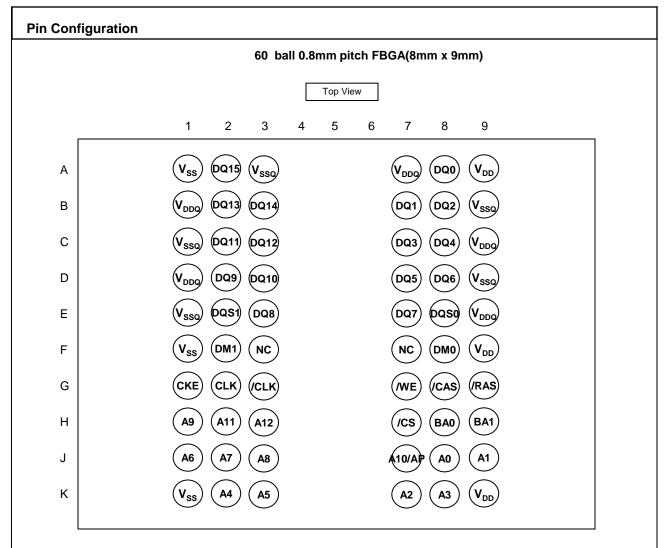

### **1.2 Connection Diagram**

# **SLC NAND FLASH**

# 1.3 Pin Description

| Table <sup>•</sup> | 1.2 | Pin | Description |

|--------------------|-----|-----|-------------|

|--------------------|-----|-----|-------------|

| Pin Name                | Description                                                                                                                                                                                                                                    |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O0 - I/O7 <b>(x8)</b> | Inputs/Outputs. The I/O pins are used for command input, address input, data input, and data output. The                                                                                                                                       |

| I/O8 - I/O15 (x16)      | I/O pins float to High-Z when the device is deselected or the outputs are disabled.                                                                                                                                                            |

| CLE                     | Command Latch Enable. This input activates the latching of the I/O inputs inside the Command Register on the rising edge of Write Enable (WE#).                                                                                                |

| ALE                     | Address Latch Enable. This input activates the latching of the I/O inputs inside the Address Register on the rising edge of Write Enable (WE#).                                                                                                |

| CE#                     | Chip Enable. This input controls the selection of the device. When the device is not busy CE# low selects the memory.                                                                                                                          |

| WE#                     | Write Enable. This input latches Command, Address and Data. The I/O inputs are latched on the rising edge of WE#.                                                                                                                              |

| RE#                     | Read Enable. The RE# input is the serial data-out control, and when active drives the data onto the I/O bus. Data is<br>valid t <sub>REA</sub> after the falling edge of RE# which also increments the internal column address counter by one. |

| WP#                     | Write Protect. The WP# pin, when low, provides hardware protection against undesired data modification (program / erase).                                                                                                                      |

| R/B#                    | Ready Busy. The Ready/Busy output is an Open Drain pin that signals the state of the memory.                                                                                                                                                   |

| vcc                     | Supply Voltage. The V <sub>CC</sub> supplies the power for all the operations (Read, Program, Erase). An internal lock circuit prevents the insertion of Commands when V <sub>CC</sub> is less than V <sub>LKO</sub> .                         |

| VSS                     | Ground.                                                                                                                                                                                                                                        |

| NC                      | Not Connected.                                                                                                                                                                                                                                 |

#### Notes:

A 0.1 μF capacitor should be connected between the V<sub>CC</sub> Supply Voltage pin and the V<sub>SS</sub> Ground pin to decouple the current surges from the power supply. The PCB track widths must be sufficient to carry the currents required during program and erase operations.

An internal voltage detector disables all functions whenever V<sub>CC</sub> is below 1.1V (1.8V device) to protect the device from any involuntary program/erase during power transitions.

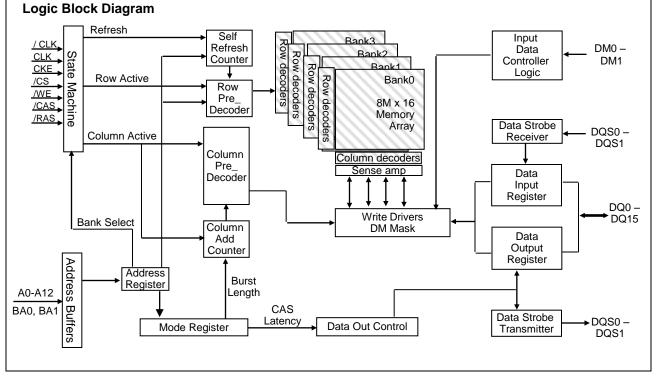

## 1.4 Block Diagram

## **SLC NAND FLASH**

## 1.5 Array Organization

Array Organization (x8)

Figure 1.7 Array Organization – FMND1G16S3S (x16)

Figure 1.8 Array Organization – FMND2G08S3S and FMND4G08S3S (x8)

Figure 1.9 Array Organization – FMND2G16S3S and FMND4G16S3S (x16)

# **SLC NAND FLASH**

## 1.6 Addressing

## 1.6.1 FMND1GxxS3S

| Bus Cycle                                                              | I/O [15:8] (5) | 1/00      | I/O1      | 1/02       | VO3        | VO4       | 1/05      | VO6       | 1/07      |  |

|------------------------------------------------------------------------|----------------|-----------|-----------|------------|------------|-----------|-----------|-----------|-----------|--|

| x8                                                                     |                |           |           |            |            |           |           |           |           |  |

| 1st — A0 (CA0) A1 (CA1) A2 (CA2) A3 (CA3) A4 (CA4) A5 (CA5) A6 (CA6) A |                |           |           |            |            |           |           |           | A7 (CA7)  |  |

| 2nd                                                                    | -              | A8 (CA8)  | A9 (CA9)  | A10 (CA10) | A11 (CA11) | Low       | Low       | Low       | Low       |  |

| 3rd                                                                    | -              | A12 (PA0) | A13 (PA1) | A14 (PA2)  | A15 (PA3)  | A16 (PA4) | A17 (PA5) | A18 (BA0) | A19 (BA1) |  |

| 4th                                                                    | -              | A20 (BA2) | A21 (BA3) | A22 (BA4)  | A23 (BA5)  | A24 (BA6) | A25 (BA7) | A26 (BA8) | A27 (BA9) |  |

|                                                                        |                |           |           | x16        |            |           |           |           | 2         |  |

| 1st                                                                    | Low            | A0 (CA0)  | A1 (CA1)  | A2 (CA2)   | A3 (CA3)   | A4 (CA4)  | A5 (CA5)  | A6 (CA6)  | A7 (CA7)  |  |

| 2nd                                                                    | Low            | A8 (CA8)  | A9 (CA9)  | A10 (CA10) | Low        | Low       | Low       | Low       | Low       |  |

| 3rd                                                                    | Low            | A11 (PA0) | A12 (PA1) | A13 (PA2)  | A14 (PA3)  | A15 (PA4) | A16 (PA5) | A17 (BA0) | A18 (BA1) |  |

| 4th                                                                    | Low            | A19 (BA2) | A20 (BA3) | A21 (BA4)  | A22 (BA5)  | A23 (BA6) | A24 (BA7) | A25 (BA8) | A26 (BA9) |  |

#### Table 1.3 Address Cycle Map — 1 Gb Device

Notes:

1. CAx = Column Address bit.

2. PAx = Page Address bit.

3. BAx = Block Address bit.

4. Block address concatenated with page address = actual page address.

5. I/O[15:8] are not used during the addressing sequence and should be driven Low.

For the x8 address bits, the following rules apply:

- A0 A11: column address in the page

- A12 A17: page address in the block

- A18 A27: block address

For the x16 address bits, the following rules apply:

- A0 A10: column address in the page

- A11 A16: page address in the block

- A17 A26: block address

# **SLC NAND FLASH**

# 1.6.2 FMND2GxxS3S

| Bus Cycle | VO [15:8] (6) | 1/00      | I/O1      | 1/02       | 1/03       | 1/04      | 1/05      | I/O6       | 1/07      |  |

|-----------|---------------|-----------|-----------|------------|------------|-----------|-----------|------------|-----------|--|

| x8        |               |           |           |            |            |           |           |            |           |  |

| 1st       | -             | A0 (CA0)  | A1 (CA1)  | A2 (CA2)   | A3 (CA3)   | A4 (CA4)  | A5 (CA5)  | A6 (CA6)   | A7 (CA7)  |  |

| 2nd       | -             | A8 (CA8)  | A9 (CA9)  | A10 (CA10) | A11 (CA11) | Low       | Low       | Low        | Low       |  |

| 3rd       | -             | A12 (PA0) | A13 (PA1) | A14 (PA2)  | A15 (PA3)  | A16 (PA4) | A17 (PA5) | A18 (PLA0) | A19 (BA0) |  |

| 4th       | -             | A20 (BA1) | A21 (BA2) | A22 (BA3)  | A23 (BA4)  | A24 (BA5) | A25 (BA6) | A26 (BA7)  | A27 (BA8) |  |

| 5th       | -             | A28 (BA9) | Low       | Low        | Low        | Low       | Low       | Low        | Low       |  |

|           |               |           |           | x16        |            |           |           |            |           |  |

| 1st       | Low           | A0 (CA0)  | A1 (CA1)  | A2 (CA2)   | A3 (CA3)   | A4 (CA4)  | A5 (CA5)  | A6 (CA6)   | A7 (CA7)  |  |

| 2nd       | Low           | A8 (CA8)  | A9 (CA9)  | A10 (CA10) | Low        | Low       | Low       | Low        | Low       |  |

| 3rd       | Low           | A11 (PA0) | A12 (PA1) | A13 (PA2)  | A14 (PA3)  | A15 (PA4) | A16 (PA5) | A17 (PLA0) | A18 (BA0) |  |

| 4th       | Low           | A19 (BA1) | A20 (BA2) | A21 (BA3)  | A22 (BA4)  | A23 (BA5) | A24 (BA6) | A25 (BA7)  | A26 (BA8) |  |

| 5th       | Low           | A27 (BA9) | Low       | Low        | Low        | Low       | Low       | Low        | Low       |  |

#### Table 1.4 Address Cycle Map - 2 Gb Device

Notes:

CAx = Column Address bit.

PAx = Page Address bit.

PLA0 = Plane Address bit zero.

BAx = Block Address bit.

5. Block address concatenated with page address and plane address = actual page address, also known as the row address.

6. I/O[15:8] are not used during the addressing sequence and should be driven Low.

For the x8 address bits, the following rules apply:

- A0 A11: column address in the page

- A12 A17: page address in the block

- A18: plane address (for multiplane operations) / block address (for normal operations)

- A19 A28: block address

For the x16 address bits, the following rules apply:

- A0 A10: column address in the page

- A11 A16: page address in the block

- A17: plane address (for multiplane operations) / block address (for normal operations)

- A18 A27: block address

# **SLC NAND FLASH**

# 1.6.3 FMND4GxxS3S

| Bus Cycle | VO [15:8] (6) | 1/00      | 1/01       | 1/02       | 1/03       | 1/04      | 1/05      | 1/06       | 1/07      |  |

|-----------|---------------|-----------|------------|------------|------------|-----------|-----------|------------|-----------|--|

| x8        |               |           |            |            |            |           |           |            |           |  |

| 1st       | -             | A0 (CA0)  | A1 (CA1)   | A2 (CA2)   | A3 (CA3)   | A4 (CA4)  | A5 (CA5)  | A6 (CA6)   | A7 (CA7)  |  |

| 2nd       | -             | A8 (CA8)  | A9 (CA9)   | A10 (CA10) | A11 (CA11) | Low       | Low       | Low        | Low       |  |

| 3rd       | -             | A12 (PA0) | A13 (PA1)  | A14 (PA2)  | A15 (PA3)  | A16 (PA4) | A17 (PA5) | A18 (PLA0) | A19 (BA0) |  |

| 4th       | -             | A20 (BA1) | A21 (BA2)  | A22 (BA3)  | A23 (BA4)  | A24 (BA5) | A25 (BA6) | A26 (BA7)  | A27 (BA8) |  |

| 5th       | -             | A28 (BA9) | A29 (BA10) | Low        | Low        | Low       | Low       | Low        | Low       |  |

|           |               |           |            | x16        |            |           |           |            |           |  |

| 1st       | Low           | A0 (CA0)  | A1 (CA1)   | A2 (CA2)   | A3 (CA3)   | A4 (CA4)  | A5 (CA5)  | A6 (CA6)   | A7 (CA7)  |  |

| 2nd       | Low           | A8 (CA8)  | A9 (CA9)   | A10 (CA10) | Low        | Low       | Low       | Low        | Low       |  |

| 3rd       | Low           | A11 (PA0) | A12 (PA1)  | A13 (PA2)  | A14 (PA3)  | A15 (PA4) | A16 (PA5) | A17 (PLA0) | A18 (BA0) |  |

| 4th       | Low           | A19 (BA1) | A20 (BA2)  | A21 (BA3)  | A22 (BA4)  | A23 (BA5) | A24 (BA6) | A25 (BA7)  | A26 (BA8) |  |

| 5th       | Low           | A27 (BA9) | A28 (BA10) | Low        | Low        | Low       | Low       | Low        | Low       |  |

#### Table 1.5 Address Cycle Map - 4 Gb Device

Notes:

1. CAx = Column Address bit.

2. PAx = Page Address bit.

3. PLA0 = Plane Address bit zero.

BAx = Block Address bit.

5. Block address concatenated with page address and plane address = actual page address, also known as the row address.

6. I/O[15:8] are not used during the addressing sequence and should be driven Low.

For the x8 address bits, the following rules apply:

- A0 A11: column address in the page

- A12 A17: page address in the block

- A18: plane address (for multiplane operations) / block address (for normal operations)

- A19 A29: block address

For the x16 address bits, the following rules apply:

- A0 A10: column address in the page

- A11 A16: page address in the block

- A17: plane address (for multiplane operations) / block address (for normal operations)

- A18 A28: block address

# **SLC NAND FLASH**

## **1.7 Mode Selection**

| Mode                     |               | CLE  | ALE  | CE#  | WE#    | RE#      | WP#          |

|--------------------------|---------------|------|------|------|--------|----------|--------------|

| Dead Mada                | Command Input | High | Low  | Low  | Rising | High     | х            |

| Read Mode                | Address Input | Low  | High | Low  | Rising | High     | х            |

| Deserve of Freedom Marke | Command Input | High | Low  | Low  | Rising | High     | High         |

| Program or Erase Mode    | Address Input | Low  | High | Low  | Rising | High     | High         |

| Data Input               |               | Low  | Low  | Low  | Rising | High     | High         |

| Data Output (on going)   |               | Low  | Low  | Low  | High   | Falling  | x            |

| Data Output (suspended)  |               | x    | х    | х    | High   | High     | x            |

| Busy Time in Read        |               | х    | х    | х    | х      | High (3) | x            |

| Busy Time in Program     |               | х    | х    | х    | x      | х        | High         |

| Busy Time in Erase       |               | x    | х    | х    | x      | х        | High         |

| Write Protect            |               | x    | х    | х    | x      | х        | Low          |

| Stand By                 |               | х    | х    | High | x      | х        | 0V / Vcc (2) |

#### Table 1.6 Mode Selection

Notes:

1. X can be VIL or VIH High = Logic level high. Low = Logic level low.

2. WP# should be biased to CMOS high or CMOS low for stand-by mode.

3. During Busy Time in Read, RE# must be held high to prevent unintended data out.

# **SLC NAND FLASH**

## 2. Bus Operation

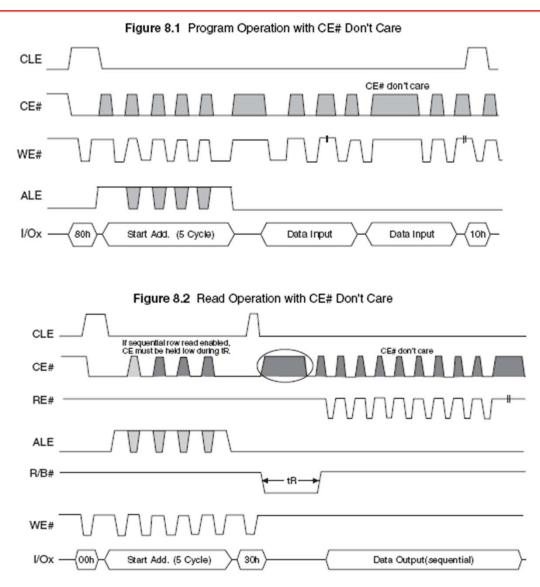

There are six standard bus operations that control the device: Command Input, Address Input, Data Input, Data Output, Write Protect, and Standby. (See Table 1.6.)

Typically glitches less than 5 ns on Chip Enable, Write Enable, and Read Enable are ignored by the memory and do not affect bus operations.

### 2.1 Command Input

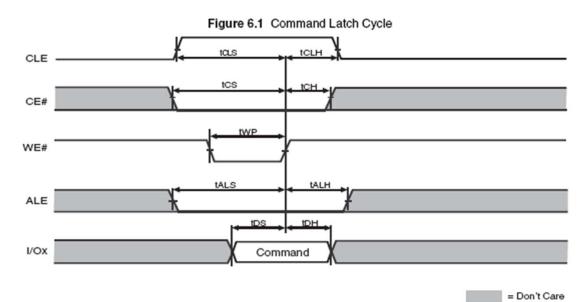

The Command Input bus operation is used to give a command to the memory device. Commands are accepted with Chip Enable low, Command Latch Enable high, Address Latch Enable low, and Read Enable high and latched on the rising edge of Write Enable. Moreover, for commands that start a modify operation (program/erase) the Write Protect pin must be high. See Figure 6.1 on page 39 and Table 5.4 on page 36 for details of the timing requirements. Command codes are always applied on I/O7:0 regardless of the bus configuration (x8 or x16).

### 2.2 Address Input

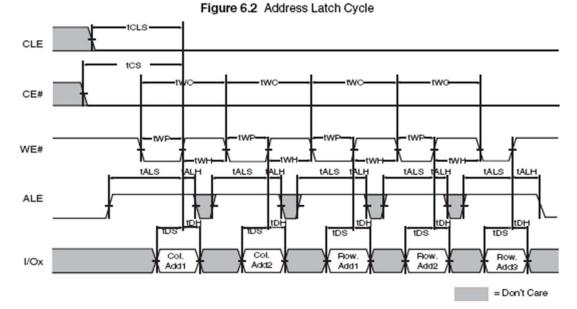

The Address Input bus operation allows the insertion of the memory address. For the FMND2GxxS3S and FMND4GxxS3S devices, five write cycles are needed to input the addresses. For the FMND1GxxS3S, four write cycles are needed to input the addresses. If necessary, a 5th dummy address cycle can be issued to FMND1GxxS3S, which will be ignored by the NAND device without causing problems. Addresses are accepted with Chip Enable low, Address Latch Enable high, Command Latch Enable low, and Read Enable high and latched on the rising edge of Write Enable. Moreover, for commands that start a modify operation (program/ erase) the Write Protect pin must be high. See Figure 6.2 on page 40 and Table 5.4 on page 36 for details of the timing requirements. Addresses are always applied on I/O7:0 regardless of the bus configuration (x8 or x16). Refer to Table 1.3 through Table 1.5 on page 13 for more detailed information.

### 2.3 Data Input

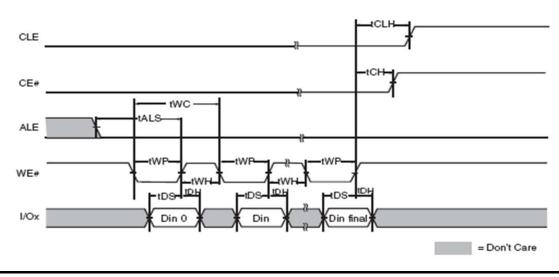

The Data Input bus operation allows the data to be programmed to be sent to the device. The data insertion is serial and timed by the Write Enable cycles. Data is accepted only with Chip Enable low, Address Latch Enable low, Command Latch Enable low, Read Enable high, and Write Protect high and latched on the rising edge of Write Enable. See Figure 6.3 on page 40 and Table 5.4 on page 36 for details of the timing requirements.

## 2.4 Data Output

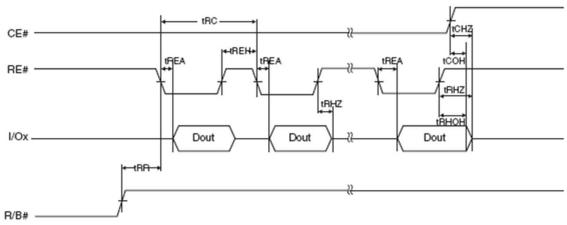

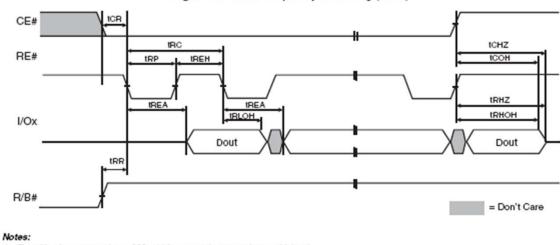

The Data Output bus operation allows data to be read from the memory array and to check the Status Register content, and the ID data. Data can be serially shifted out by toggling the Read Enable pin with Chip Enable low, Write Enable high, Address Latch Enable low, and Command Latch Enable low. See Figure 6.4 on page 41 and Table 5.4 on page 36 for details of the timings requirements.

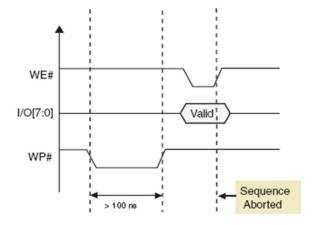

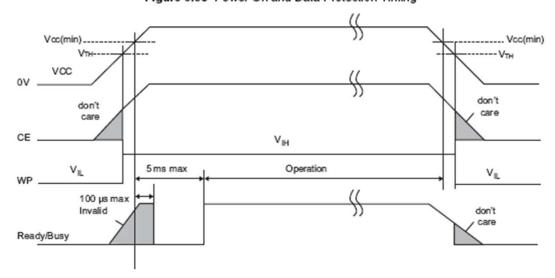

### 2.5 Write Protect

The Hardware Write Protection is activated when the Write Protect pin is low. In this condition, modify operations do not start and the content of the memory is not altered. The Write Protect pin is not latched by Write Enable to ensure the protection even during power up.

### 2.6 Standby

In Standby, the device is deselected, outputs are disabled, and power consumption is reduced.

# **SLC NAND FLASH**

# 3. Command Set

| Command                                        | 1st Cycle       | 2nd Cycle | 3rd Cycle | 4th Cycle | Acceptable<br>Command<br>during Busy | Supported on<br>FMND1GxxS3S |

|------------------------------------------------|-----------------|-----------|-----------|-----------|--------------------------------------|-----------------------------|

| Page Read                                      | 00h             | 30h       |           |           | No                                   | Yes                         |

| Page Program                                   | 80h             | 10h       |           |           | No                                   | Yes                         |

| Random Data Input                              | 85h             |           |           |           | No                                   | Yes                         |

| Random Data Output                             | 05h             | E0h       |           |           | No                                   | Yes                         |

| Multiplane Program                             | 80h             | 11h       | 81h       | 10h       | No                                   | No                          |

| ONFI Multiplane Program                        | 80h             | 11h       | 80h       | 10h       | No                                   | No                          |

| Page Reprogram                                 | 8Bh             | 10h       |           |           | No                                   | Yes                         |

| Multiplane Page Reprogram                      | 8Bh             | 11h       | 8Bh       | 10h       | No                                   | No                          |

| Block Erase                                    | 60h             | D0h       |           |           | No                                   | Yes                         |

| Multiplane Block Erase                         | 60h             | 60h       | D0h       |           | No                                   | No                          |

| ONFI Multiplane Block Erase                    | 60h             | D1h       | 60h       | D0h       | No                                   | No                          |

| Copy Back Read                                 | 00h             | 35h       |           |           | No                                   | Yes                         |

| Copy Back Program                              | 85h             | 10h       |           |           | No                                   | Yes                         |

| Multiplane Copy Back Program                   | 85h             | 11h       | 81h       | 10h       | No                                   | No                          |

| ONFI Multiplane Copy Back Program              | 85h             | 11h       | 85h       | 10h       | No                                   | No                          |

| Special Read For Copy Back                     | 00h             | 36h       |           |           | No                                   | No                          |

| Read Status Register                           | 70h             |           |           |           | Yes                                  | Yes                         |

| Read Status Enhanced                           | 78h             |           |           |           | Yes                                  | No                          |

| Reset                                          | FFh             |           |           |           | Yes                                  | Yes                         |

| Read Cache                                     | 31h             |           |           |           | No                                   | Yes                         |

| Read Cache Enhanced                            | 00h             | 31h       |           |           | No                                   | Yes                         |

| Read Cache End                                 | 3Fh             |           |           |           | No                                   | Yes                         |

| Cache Program (End)                            | 80h             | 10h       |           |           | No                                   | Yes                         |

| Cache Program (Start) / (Continue)             | 80h             | 15h       |           |           | No                                   | Yes                         |

| Multiplane Cache Program (Start/Continue)      | 80h             | 11h       | 81h       | 15h       | No                                   | No                          |

| ONFI Multiplane Cache Program (Start/Continue) | 80h             | 11h       | 80h       | 15h       | No                                   | No                          |

| Multiplane Cache Program (End)                 | 80h             | 11h       | 81h       | 10h       | No                                   | No                          |

| ONFI Multiplane Cache Program (End)            | 80h             | 11h       | 80h       | 10h       | No                                   | No                          |

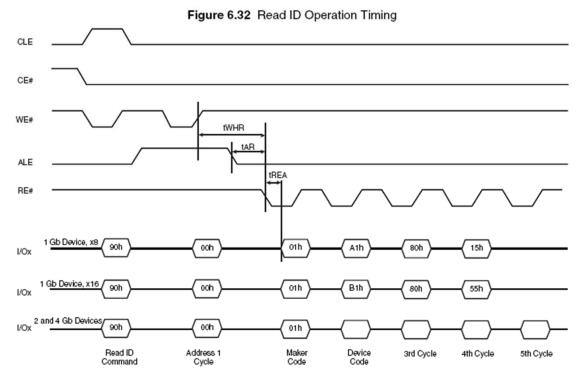

| Read ID                                        | 90h             |           |           |           | No                                   | Yes                         |

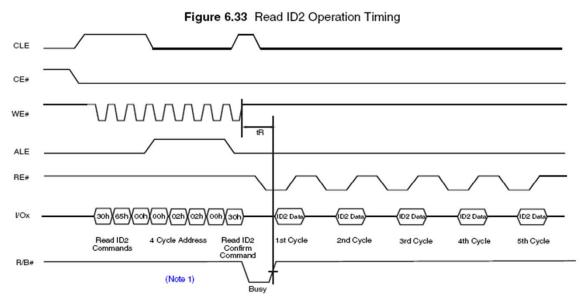

| Read ID2                                       | 30h-65h-00h     | 30h       |           |           | No                                   | Yes                         |

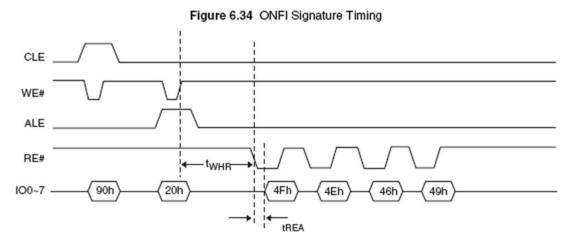

| Read ONFI Signature                            | 90h             |           |           |           | No                                   | Yes                         |

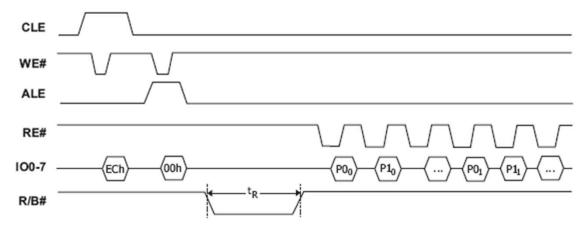

| Read Parameter Page                            | ECh             |           |           |           | No                                   | Yes                         |

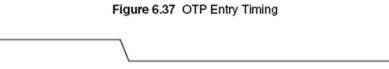

| One-time Programmable (OTP) Area Entry         | 29h-17h-04h-19h |           |           |           | No                                   | Yes                         |

#### Table 3.1 Command Set

# **SLC NAND FLASH**

## 3.1 Page Read

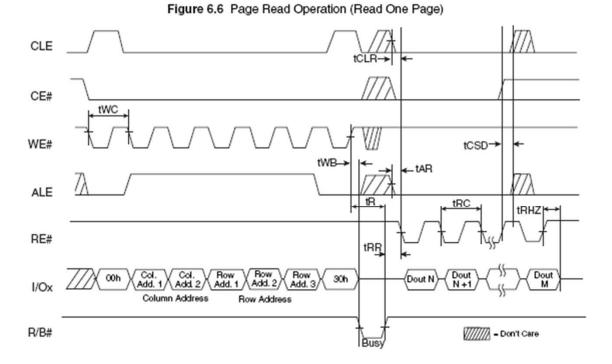

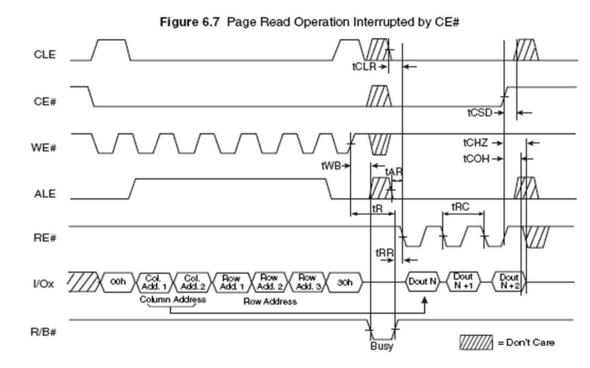

Page Read is initiated by writing 00h and 30h to the command register along with five address cycles (four or five cycles for FMND1GxxS3S). Two types of operations are available: random read and serial page read. Random read mode is enabled when the page address is changed. All data within the selected page are transferred to the data registers in less than 25  $\mu$ s (tR). The system controller may detect the completion of this data transfer (tR) by analyzing the output of the R/B pin. Once the data in a page is loaded into the data registers, they may be read out in 45 ns (x8) or 40 ns (x16) cycle time by sequentially pulsing RE#. The repetitive high to low transitions of the RE# signal makes the device output the data, starting from the selected column address up to the last column address.

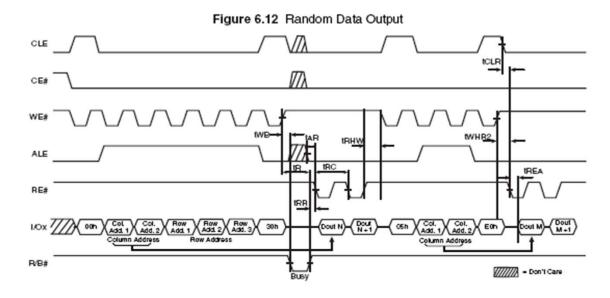

The device may output random data in a page instead of the sequential data by writing Random Data Output command. The column address of next data, which is going to be out, may be changed to the address that follows Random Data Output command. Random Data Output can be performed as many times as needed. After power up, the device is in read mode, so 00h command cycle is not necessary to start a read operation. Any operation other than read or Random Data Output causes the device to exit read mode. See Figure 6.6 on page 42 and Figure 6.12 on page 46 as references.

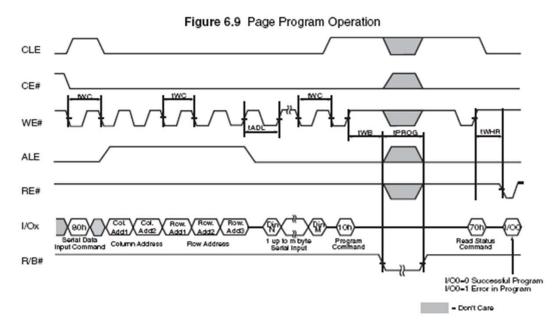

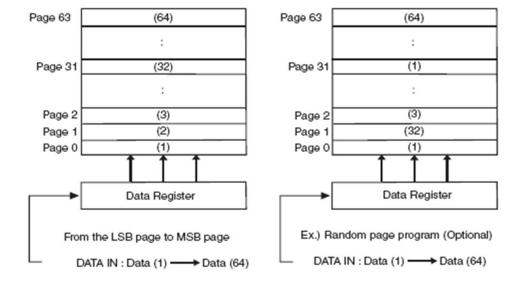

### 3.2 Page Program

A page program cycle consists of a serial data loading period in which up to 2112 bytes (x8) or 1056 words (x16) of data may be loaded into the data register, followed by a non-volatile programming period where the loaded data is programmed into the appropriate cell.

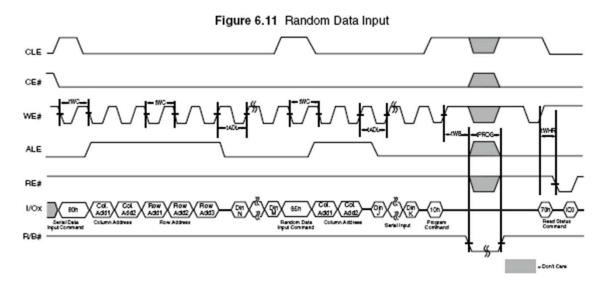

The serial data loading period begins by inputting the Serial Data Input command (80h), followed by the five cycle address inputs (four cycles for FMND1GxxS3S) and then serial data. The words other than those to be programmed do not need to be loaded. The device supports Random Data Input within a page. The column address of next data, which will be entered, may be changed to the address that follows the Random Data Input command (85h). Random Data Input may be performed as many times as needed.

The Page Program confirm command (10h) initiates the programming process. The internal write state controller automatically executes the algorithms and controls timings necessary for program and verify, thereby freeing the system controller for other tasks.

Once the program process starts, the Read Status Register commands (70h or 78h) may be issued to read the Status Register. The system controller can detect the completion of a program cycle by monitoring the R/B# output, or the Status bit (I/O6) of the Status Register. Only the Read Status commands (70h or 78h) or Reset command are valid while programming is in progress. When the Page Program is complete, the Write Status Bit (I/O0) may be checked. The internal write verify detects only errors for 1's that are not successfully programmed to 0's. The command register remains in Read Status command mode until another valid command is written to the command register. Figure 6.9 on page 44 and Figure 6.11 on page 45 detail the sequence.

The device is programmable by page, but it also allows multiple partial page programming of a word or consecutive bytes up to the full page in a single page program cycle.

The number of consecutive partial page programming operations (NOP) within the same page must not exceed the number indicated in Table 5.7 on page 38. Pages may be programmed in any order within a block. If a Page Program operation is interrupted by hardware reset, power failure or other means, the host must ensure that the interrupted page is not used for further reading or programming operations until the next uninterrupted block erase is complete.

# **SLC NAND FLASH**

## 3.3 Multiplane Program – FMND2GxxS3S and FMND4GxxS3S

The FMND2GxxS3S and FMND4GxxS3S device support Multiplane Program, making it possible to program two pages in parallel, one page per plane.

A Multiplane Program cycle consists of a double serial data loading period in which up to 4352 bytes (x8) or 2176 words (x16) of data may be loaded into the data register, followed by a non-volatile programming period where the loaded data is programmed into the appropriate cell. The serial data loading period begins with inputting the Serial Data Input command (80h), followed by the five cycle address inputs and serial data for the 1st page. The address for this page must be in the 1st plane (PLA0 = 0). The device supports Random Data Input exactly the same as in the case of page program operation. The Dummy Page Program Confirm command (11h) stops 1st page data input and the device becomes busy for a short time (tDBSY). Once it has become ready again, the '81h' command must be issued, followed by 2nd page address (5 cycles) and its serial data input. The address for this page must be in the 2nd plane (PLA0 = 1). The Program Confirm command (10h) starts parallel programming of both pages.

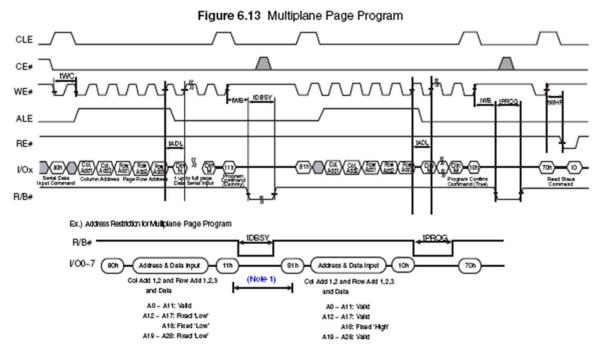

Figure 6.13 on page 46 describes the sequences using the legacy protocol. In this case, the block address bits for the first plane are all zero and the second address issued selects the block for both planes.

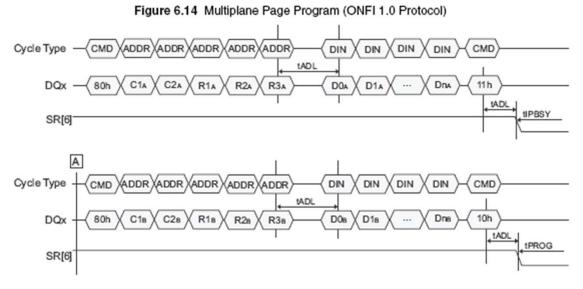

Figure 6.14 on page 47 describes the sequences using the ONFI protocol. For both addresses issued in this protocol, the block address bits must be the same except for the bit(s) that select the plane.

The user can check operation status by monitoring R/B# pin or reading the Status Register (command 70h or 78h). The Read Status Register command is also available during Dummy Busy time (tDBSY). In case of failure in either page program, the fail bit of the Status Register will be set. Refer to Section 3.8 on page 22 for further info.

The number of consecutive partial page programming operations (NOP) within the same page must not exceed the number indicated in Table 5.7 on page 38. In addition, pages must be programmed sequentially within a block.

If a Multiplane Program operation is interrupted by hardware reset, power failure or other means, the host must ensure that the interrupted pages are not used for further reading or programming operations until the next uninterrupted block erases are complete for the applicable blocks.

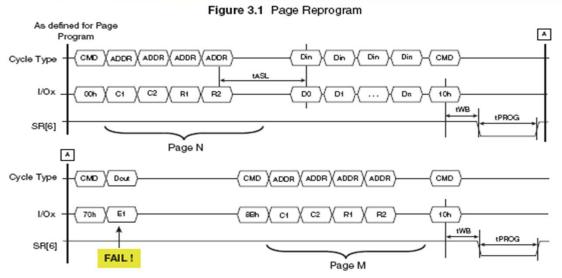

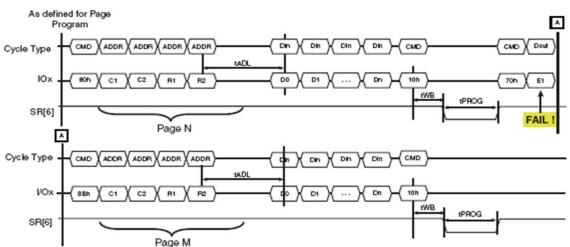

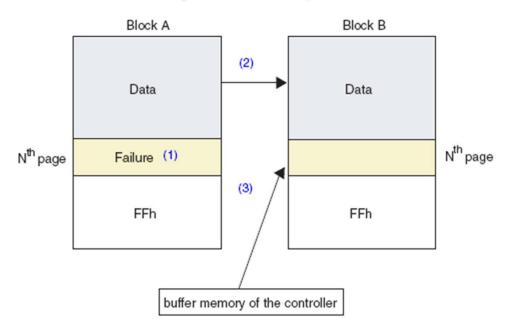

### 3.4 Page Reprogram

Page Program may result in a fail, which can be detected by Read Status Register. In this event, the host may call Page Reprogram. This command allows the reprogramming of the same pattern of the last (failed) page into another memory location. The command sequence initiates with reprogram setup (8Bh), followed by the five cycle address inputs of the target page. If the target pattern for the destination page is not changed compared to the last page, the program confirm can be issued (10h) without any data input cycle, as described in Figure 3.1.

## **SLC NAND FLASH**

On the other hand, if the pattern bound for the target page is different from that of the previous page, data in cycles can be issued before program confirm '10h', as described in Figure 3.2.

Figure 3.2 Page Reprogram with Data Manipulation

The device supports Random Data Input within a page. The column address of next data, which will be entered, may be changed to the address which follows the Random Data Input command (85h). Random Data Input may be operated multiple times regardless of how many times it is done in a page.

The Program Confirm command (10h) initiates the re-programming process. The internal write state controller automatically executes the algorithms and controls timings necessary for program and verify, thereby freeing the system controller for other tasks. Once the program process starts, the Read Status Register command may be issued to read the Status Register. The system controller can detect the completion of a program cycle by monitoring the R/B# output, or the Status bit (I/O6) of the Status Register.

Only the Read Status command and Reset command are valid when programming is in progress. When the Page Program is complete, the Write Status Bit (I/O0) may be checked. The internal write verify detects only errors for 1's that are not successfully programmed to 0's. The command register remains in Read Status command mode until another valid command is written to the command register.

# **SLC NAND FLASH**

The Page Reprogram must be issued in the same plane as the Page Program that failed. In order to program the data to a different plane, use the Page Program operation instead. The Multiplane Page Reprogram can re-program two pages in parallel, one per plane. The Multiplane Page Reprogram operation is performed after a failed Multiplane Page Program operation. The command sequence is very similar to Figure 6.13 on page 46, except that it requires the Page Reprogram Command (8Bh) instead of 80h and 81h.

If a Page Reprogram operation is interrupted by hardware reset, power failure or other means, the host must ensure that the interrupted page is not used for further reading or programming operations until the next uninterrupted block erase is complete.

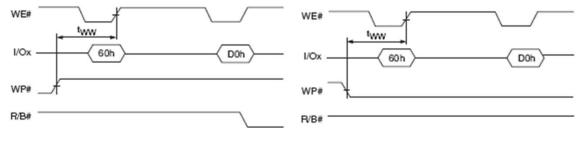

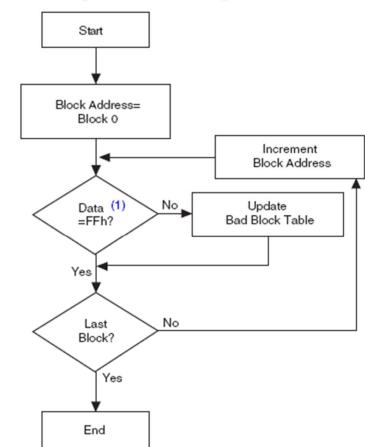

## 3.5 Block Erase

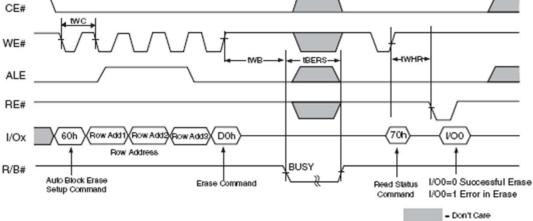

The Block Erase operation is done on a block basis. Block address loading is accomplished in three cycles (two cycles for FMND1GxxS3S) initiated by an Erase Setup command (60h). Only the block address bits are valid while the page address bits are ignored.

The Erase Confirm command (D0h) following the block address loading initiates the internal erasing process. This two-step sequence of setup followed by the execution command ensures that memory contents are not accidentally erased due to external noise conditions.

At the rising edge of WE# after the erase confirm command input, the internal write controller handles erase and erase verify. Once the erase process starts, the Read Status Register commands (70h or 78h) may be issued to read the Status Register.

The system controller can detect the completion of an erase by monitoring the R/B# output, or the Status bit (I/O6) of the Status Register. Only the Read Status commands (70h or 78h) and Reset command are valid while erasing is in progress. When the erase operation is completed, the Write Status Bit (I/O0) may be checked. Figure 6.15 on page 47 details the sequence.

If a Block Erase operation is interrupted by hardware reset, power failure or other means, the host must ensure that the interrupted block is erased under continuous power conditions before that block can be trusted for further programming and reading operations.

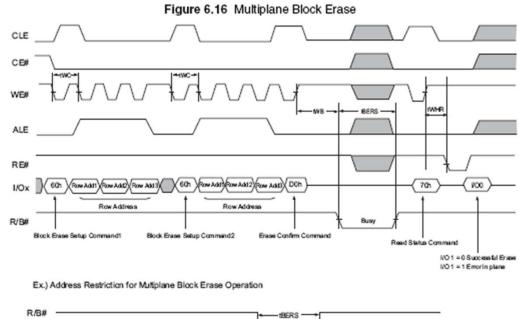

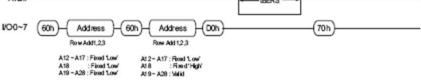

# 3.6 Multiplane Block Erase – FMND2GxxS3S and FMND4GxxS3S

Multiplane Block Erase allows the erase of two blocks in parallel, one block per memory plane. The Block erase setup command (60h) must be repeated two times, followed by 1st and 2nd block address respectively (3 cycles each). As for block erase, D0h command makes embedded operation start. In this case, multiplane erase does not need any Dummy Busy Time between 1st and 2nd block insertion. See Table 5.7 on page 38 for performance information.

For the Multiplane Block Erase operation, the address of the first block must be within the first plane (PLA0 = 0) and the address of the second block in the second plane (PLA0 = 1). See Figure 6.16 on page 48 for a description of the legacy protocol. In this case, the block address bits for the first plane are all zero and the second address issued selects the block for both planes. Figure 6.17 on page 48 describes the sequences using the ONFI protocol. For both addresses issued in this protocol, the block address bits must be the same except for the bit(s) that select the plane.

The user can check operation status by monitoring R/B# pin or reading the Status Register (command 70h or 78h). The Read Status Register command is also available during Dummy Busy time (tDBSY). In case of failure in either erase, the fail bit of the Status Register will be set. Refer to Section 3.8 on page 22 for further information.

If a Multiplane Block Erase operation is interrupted by hardware reset, power failure or other means, the host must ensure that the interrupted blocks are erased under continuous power conditions before those block can be trusted for further programming and reading operations.

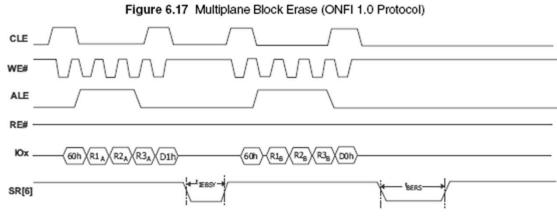

## 3.7 Copy Back Program

The copy back feature is intended to quickly and efficiently rewrite data stored in one page without utilizing an external memory. Since the time-consuming cycles of serial access and re-loading cycles are removed, the system performance is greatly improved. The benefit is especially obvious when a portion of a block needs to be updated and the rest of the block also needs to be copied to the newly assigned free block. The operation for performing a copy back is a sequential execution of page-read (without mandatory serial access) and Copy Back Program with the address of destination page. A read operation with the '35h' command and the address of the source page moves the whole 2112-byte (x8) or 1056-word (x16) data into the internal data buffer. As soon as the device returns to Ready state, optional data read-out is allowed by toggling RE# (see Figure 6.18 on page 49), or Copy Back Program command (85h) with the address cycles of destination page may be written. The Program Confirm command (10h) is required to actually begin programming.

The source and destination page in the Copy Back Program sequence must belong to the same device plane (same PLA0 for FMND2GxxS3S and FMND4GxxS3S). Copy Back Read and Copy Back Program for a given plane must be between odd address pages or between even address pages for the device to meet the program time (tPROG) specification. Copy Back Program may not meet this specification when copying from an odd address page (source page) to an even address page (target page) or from an even address page (source page) to an odd address page (target page) or from an even address page (source page) to an odd address page (target page). The data input cycle for modifying a portion or multiple distinct portions of the source page is allowed as shown in Figure 6.19 on page 49.

If a Copy Back Program operation is interrupted by hardware reset, power failure or other means, the host must ensure that the interrupted page is not used for further reading or programming operations until the next uninterrupted block erase is complete.

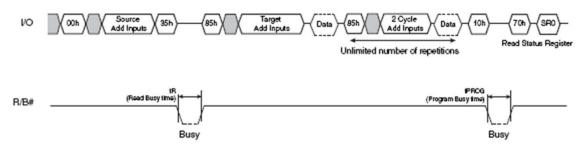

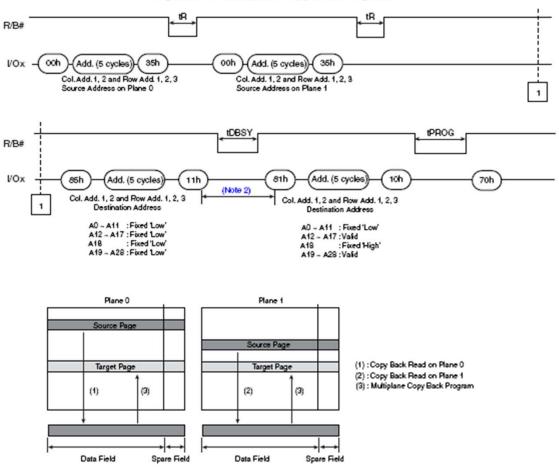

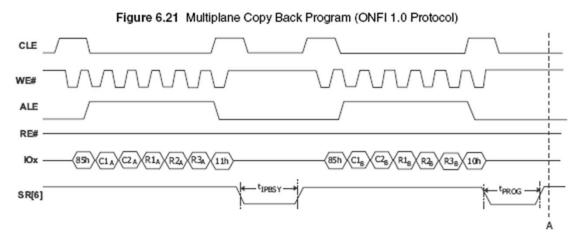

## 3.7.1 Multiplane Copy Back Program – FMND2GxxS3S and FMND4GxxS3S

The device supports Multiplane Copy Back Program with exactly the same sequence and limitations as the Page Program. Multiplane Copy Back Program must be preceded by two single page Copy Back Read command sequences (1st page must be read from the 1st plane and 2nd page from the 2nd plane). Multiplane Copy Back cannot cross plane boundaries — the contents of the source page of one device plane can be copied only to a destination page of the same plane.

The Multiplane Copy Back Program sequence represented in Figure 6.20 on page 50 shows the legacy protocol. In this case, the block address bits for the first plane are all zero and the second address issued selects the block for both planes. Figure 6.21 on page 51 describes the sequence using the ONFI protocol. For both addresses issued in this protocol, the block address bits must be the same except for the bit(s) that select the plane.

If a Multiplane Program operation is interrupted by hardware reset, power failure or other means, the host must ensure that the interrupted pages are not used for further reading or programming operations until the next uninterrupted block erases are complete for the applicable blocks.

# 3.7.2 Special Read for Copy Back – FMND2GxxS3S and FMND4GxxS3S

The device features the "Special Read for Copy Back." If Copy Back Read (described in Section 3.7 and Section 3.7.1 on page 21) is triggered with confirm command '36h' instead '35h', Copy Back Read from target page(s) will be executed with an increased internal (VPASS) voltage.

This special feature is used in order to minimize the number of read errors due to over-program or read disturb — it shall be used only if ECC read errors have occurred in the source page using Page Read or Copy Back Read sequences.

Excluding the Copy Back Read confirm command, all other features described in Section 3.7 and Section 3.7.1 for standard copy back remain valid (including the figures referred to in those sections).

# **SLC NAND FLASH**

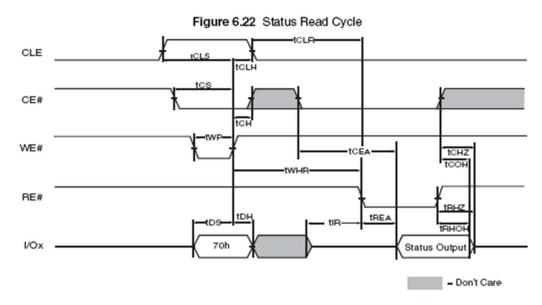

## 3.8 Read Status Register

The Status Register is used to retrieve the status value for the last operation issued. After writing 70h command to the command register, a read cycle outputs the content of the Status Register to the I/O pins on the falling edge of CE# or RE#, whichever occurs last. This two-line control allows the system to poll the progress of each device in multiple memory connections even when R/B# pins are common-wired. Refer to Section 3.2 on page 17 for specific Status Register definition, and to Figure 6.22 on page 51 for timings. If the Read Status Register command is issued during multiplane operations then Status Register polling will return the combined status value related to the outcome of the operation in the two planes according to the following table:

| Status Register Bit    | Composite Status Value |

|------------------------|------------------------|

| Bit 0, Pass/Fail       | OR                     |

| Bit 1, Cache Pass/Fail | OR                     |

In other words, the Status Register is dynamic; the user is not required to toggle RE# / CE# to update it. The command register remains in Status Read mode until further commands are issued. Therefore, if the Status Register is read during a random read cycle, the read command (00h) should be given before starting read cycles. Note: The Read Status Register command shall not be used for concurrent operations in multi-die stack configurations (single CE#). "Read Status Enhanced" shall be used instead.

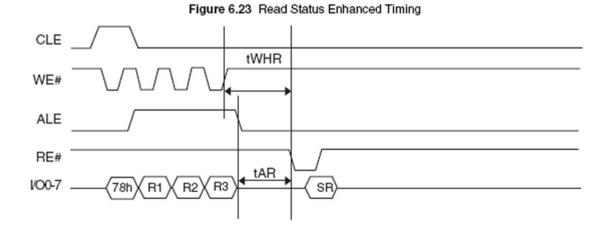

### 3.9 Read Status Enhanced – FMND2GxxS3S and FMND4GxxS3S

Read Status Enhanced is an additional feature used to retrieve the status value for a previous operation in the case of multiplane operations in the same die.

Figure 6.23 on page 52 defines the Read Status Enhanced behavior and timings. The plane and die address must be specified in the command sequence in order to retrieve the status of the die and the plane of interest. Refer to Table 3.2 for specific Status Register definitions. The command register remains in Status Read mode until further commands are issued.

The Status Register is dynamic; the user is not required to toggle RE# / CE# to update it.

### 3.10 Read Status Register Field Definition

Table 3.2 below lists the meaning of each bit of the Read Status Register and Read Status Enhanced (FMND2GxxS3S and FMND4GxxS3S).

| ID | Page<br>Program /<br>Page<br>Reprogram | Block Erase   | Read          | Read Cache              | Cache<br>Program /<br>Cache<br>Reprogram | Coding                                            |

|----|----------------------------------------|---------------|---------------|-------------------------|------------------------------------------|---------------------------------------------------|

| 0  | Pass / Fail                            | Pass / Fail   | NA            | NA                      | Pass / Fail (N)                          | N Page<br>Pass: 0<br>Fail: 1                      |

| 1  | NA                                     | NA            | NA            | NA                      | Pass / Fail (N-1)                        | N - 1 Page<br>Pass: 0<br>Fail: 1                  |

| 2  | NA                                     | NA            | NA            | NA                      | NA                                       | _                                                 |

| 3  | NA                                     | NA            | NA            | NA                      | NA                                       | —                                                 |

| 4  | NA                                     | NA            | NA            | NA                      | NA                                       | —                                                 |

| 5  | Ready / Busy                           | Ready / Busy  | Ready / Busy  | P/E/R<br>Controller Bit | Ready / Busy                             | Ready / Busy<br>Busy: 0<br>Ready: 1               |

| 6  | Ready / Busy                           | Ready / Busy  | Ready / Busy  | Ready / Busy            | Ready / Busy                             | Data Cache<br>Ready / Busy<br>Busy: 0<br>Ready: 1 |

| 7  | Write Protect                          | Write Protect | Write Protect | NA                      | Write Protect                            | Protected: 0<br>Not Protected: 1                  |

Table 3.2 Status Register Coding

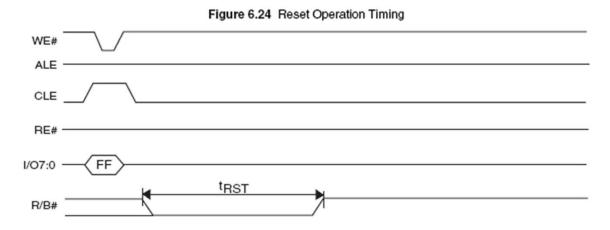

## 3.11 Reset

The Reset feature is executed by writing FFh to the command register. If the device is in Busy state during random read, program, or erase mode, the Reset operation will abort these operations. The contents of memory cells being altered are no longer valid, as the data may be partially programmed or erased. The command register is cleared to wait for the next command, and the Status Register is cleared to value E0h when WP# is high or value 60h when WP# is low. If the device is already in reset state a new Reset command will not be accepted by the command register. The R/B# pin transitions to low for tRST after the Reset command is written. Refer to Figure 6.24 on page 52 for further details. The Status Register can also be read to determine the status of a Reset operation.

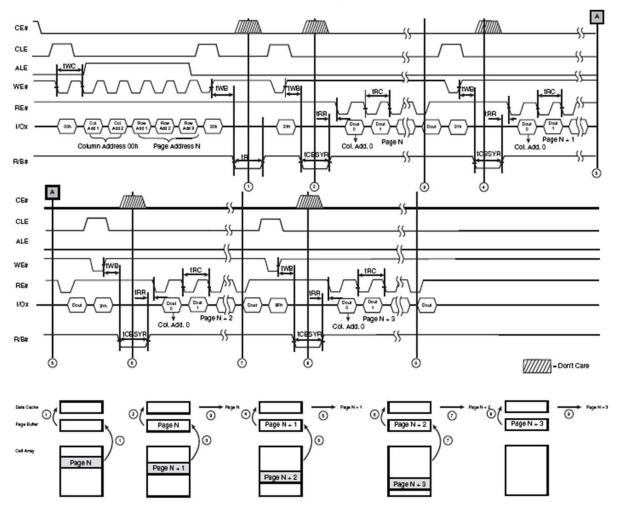

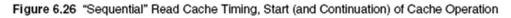

### 3.12 Read Cache

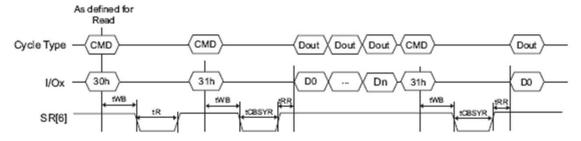

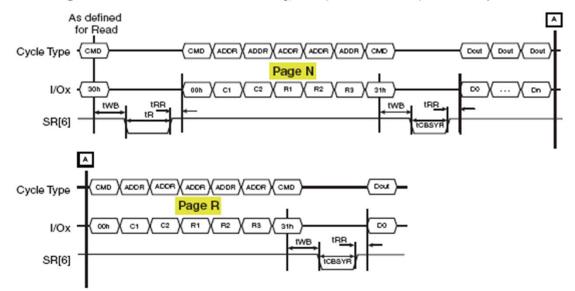

Read Cache can be used to increase the read operation speed, as defined in Section 3.1 on page 17, and it cannot cross a block boundary. As soon as the user starts to read one page, the device automatically loads the next page into the cache register. Serial data output may be executed while data in the memory is read into the cache register. Read Cache is initiated by the Page Read sequence (00-30h) on a page M. After random access to the first page is complete (R/B# returned to high, or Read Status Register I/O6 switches to high), two command sequences can be used to continue read cache:

- Read Cache (command '31h' only): once the command is latched into the command register (see Figure 6.26 on page 53), device goes busy for a short time (tCBSYR), during which data of the first page is transferred from the data register to the cache register. At the end of this phase, the cache register data can be output by toggling RE# while the next page (page address M+1) is read from the memory array into the data register.

- Read Cache Enhanced (sequence '00h' < page N address> '31'): once the command is latched into the command register (see Figure 6.27 on page 54), device goes busy for a short time (tCBSYR), during which data of the first page is transferred from the data register to the cache register. At the end of this phase, cache register data can be output by toggling RE# while page N is read from the memory array into the data register.

- Note: The FMND1GxxS3S device does not support Read Cache Enhanced.

Subsequent pages are read by issuing additional Read Cache or Read Cache Enhanced command sequences. If serial data output time of one page exceeds random access time (tR), the random access time of the next page is hidden by data downloading of the previous page.

On the other hand, if 31h is issued prior to completing the random access to the next page, the device will stay busy as long as needed to complete random access to this page, transfer its contents into the cache register, and trigger the random access to the following page.

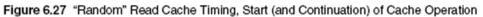

To terminate the Read Cache operation, 3Fh command should be issued (see Figure 6.28 on page 54). This command transfers data from the data register to the cache register without issuing next page read. During the Read Cache operation, the device doesn't allow any other command except for 00h, 31h, 3Fh, Read SR, or Reset (FFh). To carry out other operations, Read Cache must be terminated by the Read Cache End command (3Fh) or the device must be reset by issuing FFh.

Read Status command (70h) may be issued to check the status of the different registers and the busy/ready status of the cached read operations.

- The Cache-Busy status bit I/O6 indicates when the cache register is ready to output new data.

- The status bit I/O5 can be used to determine when the cell reading of the current data register contents is complete. Note: The Read Cache and Read Cache End commands reset the column counter, thus, when RE# is toggled to output the data of a given page, the first output data is related to the first byte of the page (column address 00h). Random Data Output command can be used to switch column address.

**SLC NAND FLASH**

# **°FIDELIX**

## 3.13 Cache Program

Cache Program can improve the program throughput by using the cache register. The Cache Program operation cannot cross a block boundary. The cache register allows new data to be input while the previous data that was transferred to the data register is programmed into the memory array.

After the serial data input command (80h) is loaded to the command register, followed by five cycles of address, a full or partial page of data is latched into the cache register.

Once the cache write command (15h) is loaded to the command register, the data in the cache register is transferred into the data register for cell programming. At this time the device remains in the Busy state for a short time (tCBSYW). After all data of the cache register is transferred into the data register, the device returns to the Ready state and allows loading the next data into the cache register through another cache program command sequence (80h-15h).

The Busy time following the first sequence 80h - 15h equals the time needed to transfer the data from the cache register to the data register. Cell programming the data of the data register and loading of the next data into the cache register is consequently processed through a pipeline model.

In case of any subsequent sequence 80h - 15h, transfer from the cache register to the data register is held off until cell programming of current data register contents is complete; till this moment the device will stay in a busy state (tCBSYW).

Read Status commands (70h or 78h) may be issued to check the status of the different registers, and the pass/fail status of the cached program operations.

- The Cache-Busy status bit I/O6 indicates when the cache register is ready to accept new data.

- The status bit I/O5 can be used to determine when the cell programming of the current data register contents is complete.

- The cache program error bit I/O1 can be used to identify if the previous page (page N-1) has been successfully programmed or not in a cache program operation. The status bit is valid upon I/O6 status bit changing to 1.

- The error bit I/O0 is used to identify if any error has been detected by the program/erase controller while programming page N. The status bit is valid upon I/O5 status bit changing to 1.

#### I/O1 may be read together with I/O0.

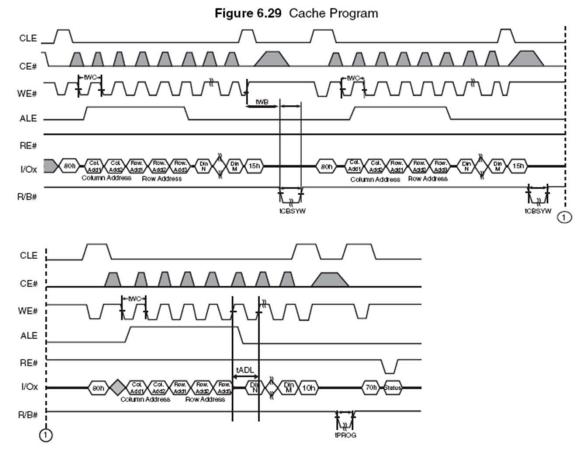

If the system monitors the progress of the operation only with R/B#, the last page of the target program sequence must be programmed with Page Program Confirm command (10h). If the Cache Program command (15h) is used instead, the status bit I/O5 must be polled to find out if the last programming is finished before starting any other operation. See Table 3.2 on page 22 and Figure 6.29 on page 55 for more details. If a Cache Program operation is interrupted by hardware reset, power failure or other means, the host must ensure that the interrupted pages are not used for further reading or programming operations until the next uninterrupted block erases are complete for the applicable blocks.

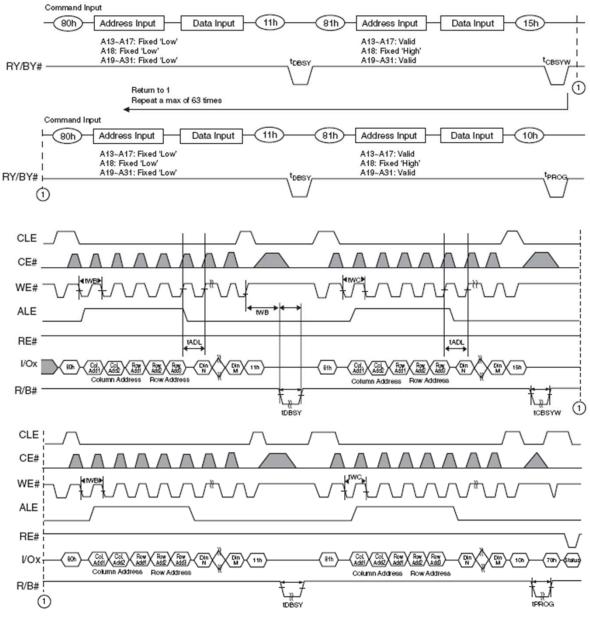

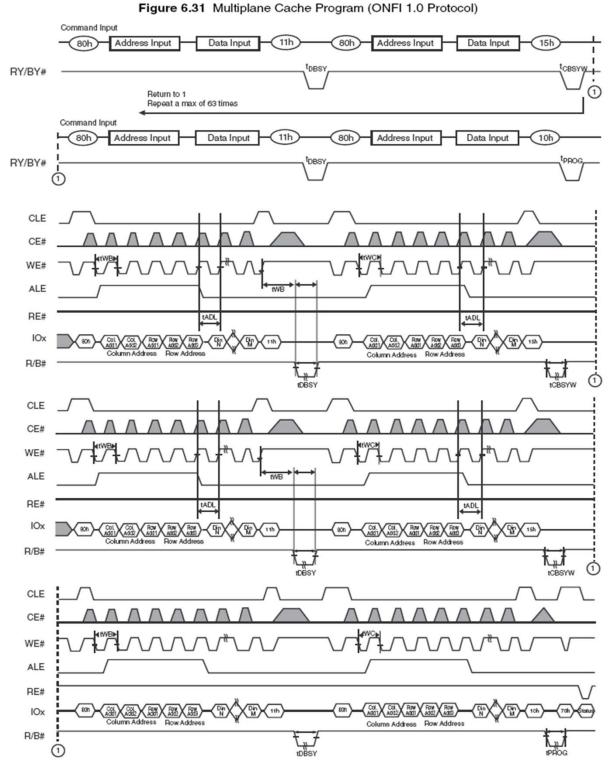

## 3.14 Multiplane Cache Program – FMND2GxxS3S and FMND4GxxS3S

The Multiplane Cache Program enables high program throughput by programming two pages in parallel, while exploiting the data and cache registers of both planes to implement cache. The command sequence can be summarized as follows:

■ Serial Data Input command (80h), followed by the five cycle address inputs and then serial data for the 1<sup>st</sup> page. Address for this page must be within 1st plane (PLA0 = 0). The data of 1st page other than those to be programmed do not need to be loaded. The device supports Random Data Input exactly like Page Program operation.