# i.MX 6Dual/6Quad Linux Reference Manual

Document Number: IMX6QLXRM Rev L3.0.35\_4.1.0, 09/2013

#### **Contents**

| Section number |         | umber Title                                              | Page         |

|----------------|---------|----------------------------------------------------------|--------------|

|                |         | Chapter 1<br>About this Book                             |              |

| 1.1            | Audie   | ence                                                     | 23           |

|                | 1.1.1   | Conventions                                              | 23           |

|                | 1.1.2   | Definitions, Acronyms, and Abbreviations                 | 23           |

|                |         | Chapter 2<br>Machine Specific Layer (MSL)                |              |

| 2.1            | Introd  | luction                                                  | 27           |

| 2.2            | Interru | upts (Operation)                                         | 28           |

|                | 2.2.1   | Interrupt Hardware Operation                             | 28           |

|                | 2.2.2   | Interrupt Software Operation                             | 28           |

|                | 2.2.3   | Interrupt Features                                       | 29           |

|                | 2.2.4   | Interrupt Source Code Structure                          | 29           |

|                | 2.2.5   | Interrupt Programming Interface                          | 29           |

| 2.3            | Timer   | 30                                                       |              |

|                | 2.3.1   | Timer Software Operation.                                | 30           |

|                | 2.3.2   | Timer Features.                                          | 30           |

|                | 2.3.3   | Timer Source Code Structure                              | 31           |

|                | 2.3.4   | Timer Programming Interface                              | 31           |

| 2.4            | Memo    | огу Мар                                                  | 31           |

|                | 2.4.1   | Memory Map Hardware Operation                            | 31           |

|                | 2.4.2   | Memory Map Software Operation                            | 31           |

|                | 2.4.3   | Memory Map Features.                                     | 31           |

|                | 2.4.4   | Memory Map Source Code Structure                         | 32           |

|                | 2.4.5   | Memory Map Programming Interface                         | 32           |

| 2.5            | IOMU    | JX                                                       | 32           |

|                | 2.5.1   | IOMUX Hardware Operation.                                | 33           |

|                | 2.5.2   | IOMUX Software Operation                                 | 33           |

|                |         | i.MX 6Dual/6Quad Linux Reference Manual, Rev. L3.0.35_4. | 1.0, 09/2013 |

| Section number |       | number Title                                    | Page |

|----------------|-------|-------------------------------------------------|------|

|                | 2.5.3 | IOMUX Features                                  | 34   |

|                | 2.5.4 | IOMUX Source Code Structure                     | 34   |

|                | 2.5.5 | IOMUX Programming Interface                     | 34   |

|                | 2.5.6 | IOMUX Control Through GPIO Module               | 34   |

|                |       | 2.5.6.1 GPIO Hardware Operation                 | 35   |

|                |       | 2.5.6.1.1 Muxing Control                        | 35   |

|                |       | 2.5.6.1.2 PULLUP Control                        | 35   |

|                |       | 2.5.6.2 GPIO Software Operation (general)       | 35   |

|                |       | 2.5.6.3 GPIO Implementation                     | 36   |

|                |       | 2.5.6.4 GPIO Source Code Structure              | 36   |

|                |       | 2.5.6.5 GPIO Programming Interface              | 36   |

| 2.6            | Gener | ral Purpose Input/Output(GPIO)                  | 36   |

|                | 2.6.1 | GPIO Software Operation                         | 36   |

|                |       | 2.6.1.1 API for GPIO                            | 37   |

|                | 2.6.2 | GPIO Features                                   | 37   |

|                | 2.6.3 | GPIO Module Source Code Structure               | 38   |

|                | 2.6.4 | GPIO Programming Interface 2                    | 38   |

|                |       | Chapter 3 Smart Direct Memory Access (SDMA) API |      |

| 3.1            | Overv | view                                            | 39   |

|                | 3.1.1 | Hardware Operation                              | 39   |

|                | 3.1.2 | Software Operation                              | 39   |

|                | 3.1.3 | Source Code Structure                           | 40   |

|                | 3.1.4 | Menu Configuration Options                      | 41   |

|                | 3.1.5 | Programming Interface                           | 41   |

|                | 3.1.6 | Usage Example                                   | 41   |

| Chapter 4                                     |

|-----------------------------------------------|

| AHB-to-APBH Bridge with DMA (APBH-Bridge-DMA) |

| 4.1 | Overvi  | ew                                                                   | 43 |

|-----|---------|----------------------------------------------------------------------|----|

|     | 4.1.1   | Hardware Operation.                                                  | 43 |

|     | 4.1.2   | Software Operation                                                   | 44 |

|     | 4.1.3   | Source Code Structure                                                | 44 |

|     | 4.1.4   | Menu Configuration Options.                                          | 45 |

|     | 4.1.5   | Programming Interface.                                               | 45 |

|     | 4.1.6   | Usage Example                                                        | 45 |

|     |         | Chapter 5 Image Processing Unit (IPU) Drivers                        |    |

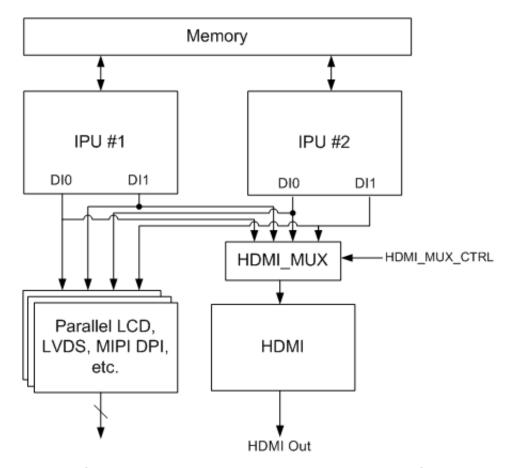

| 5.1 | Introdu | action                                                               | 47 |

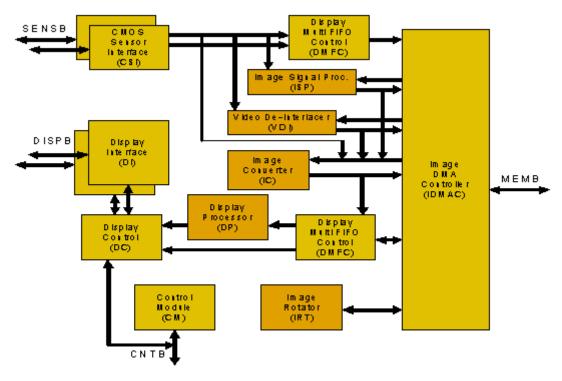

| 5.2 | Hardw   | are Operation                                                        | 48 |

| 5.3 | Softwa  | re Operation                                                         | 49 |

|     | 5.3.1   | Overview of IPU Frame Buffer Drivers                                 | 50 |

|     |         | 5.3.1.1 IPU Frame Buffer Hardware Operation.                         | 51 |

|     |         | 5.3.1.2 IPU Frame Buffer Software Operation                          | 51 |

|     |         | 5.3.1.3 Synchronous Frame Buffer Driver                              | 52 |

|     | 5.3.2   | IPU Backlight Driver.                                                | 53 |

|     | 5.3.3   | IPU Device Driver.                                                   | 53 |

| 5.4 | Source  | Code Structure                                                       | 54 |

|     | 5.4.1   | Menu Configuration Options                                           | 55 |

| 5.5 | Unit To | est                                                                  | 58 |

|     | 5.5.1   | Framebuffer Tests                                                    | 59 |

|     | 5.5.2   | Video4Linux API test                                                 | 59 |

|     | 5.5.3   | IPU Device Unit test                                                 | 60 |

|     |         | Chapter 6 MIPI DSI Driver                                            |    |

| 6.1 | Introdu | action                                                               | 65 |

|     | 6.1.1   | Overview of MIPI DSI IP Driver                                       | 65 |

|     |         | i.MX 6Dual/6Quad Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013 |    |

| Sec | tion n | number Title                                     | Page |

|-----|--------|--------------------------------------------------|------|

|     | 6.1.2  | Overview of MIPI DSI Display Panel Driver        | 66   |

|     | 6.1.3  | Hardware Operation.                              | 66   |

| 6.2 | Softw  | Software Operation                               |      |

|     | 6.2.1  | MIPI DSI IP Driver Software Operation            | 66   |

|     | 6.2.2  | MIPI DSI Display Panel Driver Software Operation | 67   |

| 6.3 | Drive  | r Features                                       | 67   |

|     | 6.3.1  | Source Code Structure                            | 68   |

|     | 6.3.2  | Menu Configuration Options                       | 68   |

|     | 6.3.3  | Programming Interface                            | 68   |

|     |        | Chapter 7<br>LVDS Display Bridge(LDB) Driver     |      |

| 7.1 | Introd | luction                                          | 69   |

|     | 7.1.1  | Hardware Operation.                              | 69   |

|     | 7.1.2  | Software Operation                               | 69   |

|     | 7.1.3  | Source Code Structure                            | 70   |

|     | 7.1.4  | Menu Configuration Options                       | 70   |

|     |        | Chapter 8<br>Video for Linux Two (V4L2) Driver   |      |

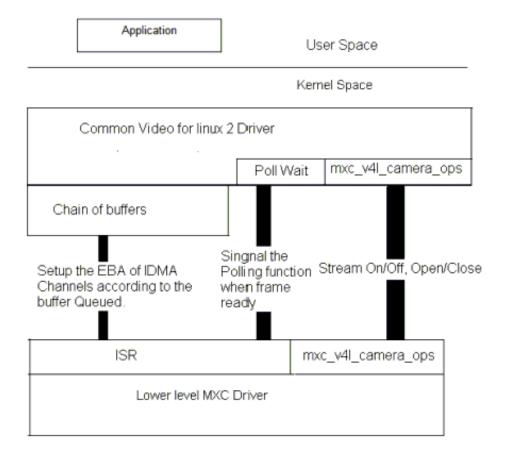

| 8.1 | Introd | luction                                          | 71   |

| 8.2 | V4L2   | Capture Device.                                  | 72   |

|     | 8.2.1  | V4L2 Capture IOCTLs                              | 72   |

|     | 8.2.2  | Using the V4L2 Capture APIs                      | 74   |

| 8.3 | V4L2   | Output Device                                    | 75   |

|     | 8.3.1  | V4L2 Output IOCTLs                               |      |

|     | 8.3.2  | Using the V4L2 Output APIs                       | 76   |

| 8.4 | Source | e Code Structure                                 |      |

|     | 8.4.1  | Menu Configuration Options.                      | 77   |

|     | 8.4.2  | V4L2 Programming Interface.                      | 77   |

# Chapter 9 Graphics Processing Unit (GPU)

|      | Graphics Processing Offic (GPO)                        |    |

|------|--------------------------------------------------------|----|

| 9.1  | Introduction.                                          | 79 |

|      | 9.1.1 Driver Features                                  | 79 |

|      | 9.1.1.1 Hardware Operation                             | 80 |

|      | 9.1.1.2 Software Operation                             | 80 |

|      | 9.1.1.3 Source Code Structure                          | 80 |

|      | 9.1.1.4 Library Structure                              | 81 |

|      | 9.1.1.5 API References                                 | 82 |

|      | 9.1.1.6 Menu Configuration Options.                    | 82 |

|      | Chapter 10<br>Direct FB                                |    |

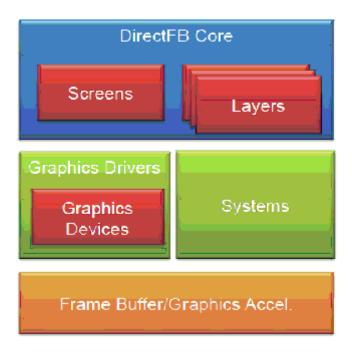

| 10.1 | Introduction.                                          | 85 |

|      | 10.1.1 Hardware Operation                              | 85 |

| 10.2 | Software Operation                                     | 85 |

|      | 10.2.1 DirectFB Acceleration Architecture              | 86 |

|      | 10.2.2 i.MX DirectFB Driver Details                    | 87 |

|      | 10.2.3 The gal_config File for i.MX DirectFB Driver    | 87 |

| 10.3 | DirectFB EGL                                           | 88 |

| 10.4 | Setting Up DirectFB Acceleration                       | 89 |

|      | Chapter 11<br>HDMI Driver                              |    |

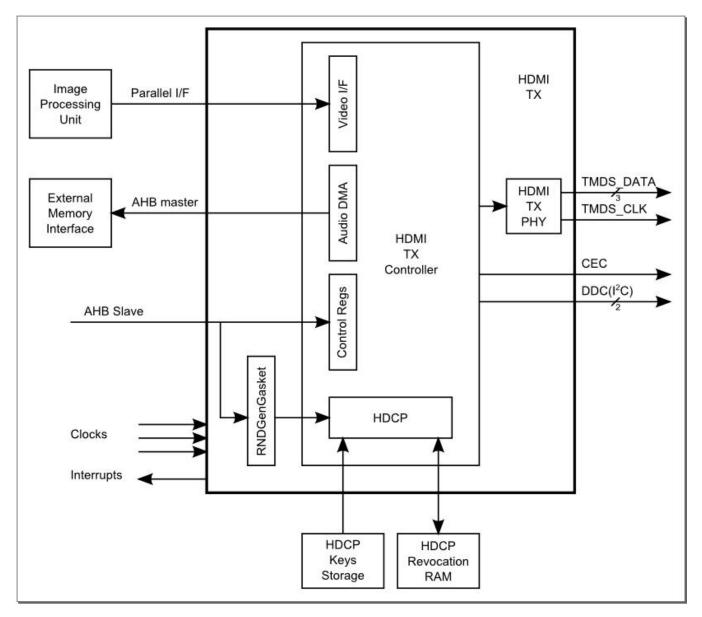

| 11.1 | Introduction                                           | 91 |

|      | 11.1.1 Hardware Operation                              | 91 |

| 11.2 | Software Operation                                     | 93 |

|      | 11.2.1 Core                                            | 93 |

|      | 11.2.2 Video                                           | 94 |

|      | 11.2.3 Display Device Registration and Initialization. | 95 |

|      | 11.2.4 Hotplug Handling and Video Mode Changes         | 96 |

|      | 11.2.5 Audio                                           | 96 |

|      |                                                        |    |

| Section number Title |                                                                        | Page                 |

|----------------------|------------------------------------------------------------------------|----------------------|

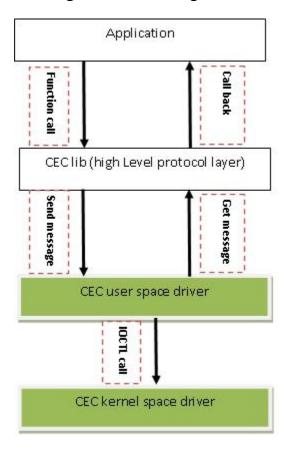

|                      | 11.2.6 CEC                                                             | 98                   |

| 11.3                 | Source Code Structure                                                  | 98                   |

|                      | 11.3.1 Linux Menu Configuration Options                                |                      |

| 11.4                 | Unit Test                                                              | 101                  |

|                      | 11.4.1 Video                                                           | 101                  |

|                      | 11.4.2 Audio                                                           |                      |

|                      | 11.4.3 CEC                                                             |                      |

|                      | Chapter 12<br>X Windows Acceleration                                   |                      |

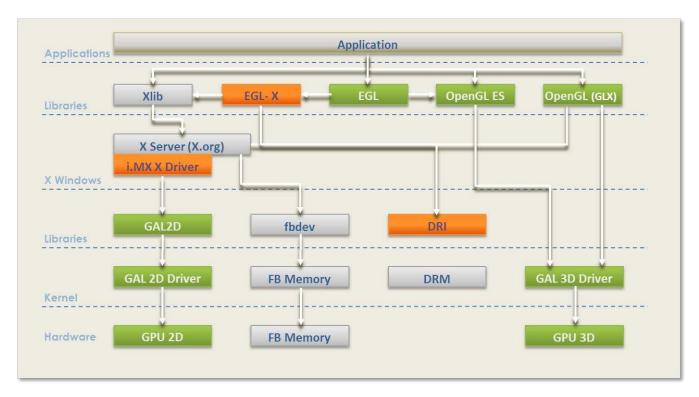

| 12.1                 | Introduction                                                           |                      |

| 12.2                 | Hardware Operation                                                     | 103                  |

| 12.3                 | Software Operation                                                     | 103                  |

|                      | 12.3.1 X Windows Acceleration Architecture                             | 104                  |

|                      | 12.3.2 i.MX 6 Driver for X-Windows System                              | 105                  |

|                      | 12.3.3 i.MX 6 Direct Rendering Infrastructure (DRI) for X-Windows Syst | tem107               |

|                      | 12.3.4 EGL- X Library                                                  |                      |

|                      | 12.3.5 xorg.conf for i.MX 6                                            |                      |

|                      | 12.3.6 Setup X-Windows System Acceleration                             |                      |

|                      | Chapter 13<br>Video Processing Unit (VPU) Di                           | river                |

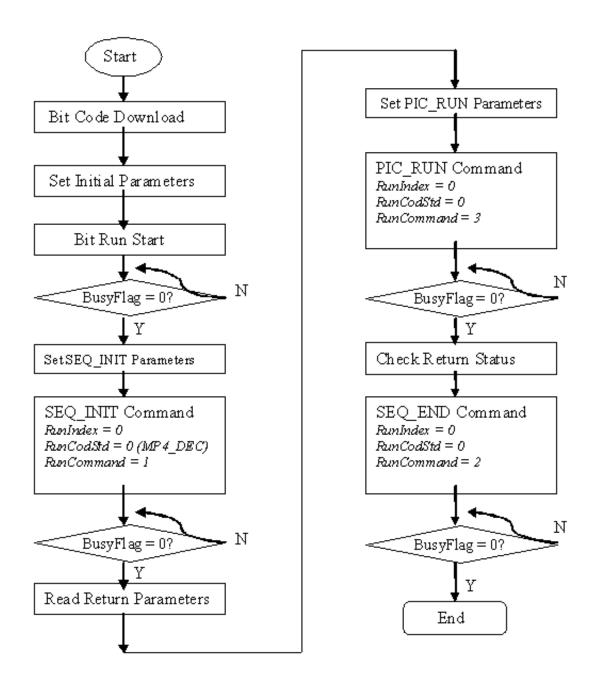

| 13.1                 | Hardware Operation                                                     |                      |

|                      | 13.1.1 Software Operation                                              | 114                  |

|                      | 13.1.2 Source Code Structure                                           | 115                  |

|                      | 13.1.3 Menu Configuration Options                                      | 116                  |

|                      | 13.1.4 Programming Interface                                           | 117                  |

|                      | 13.1.5 Defining an Application                                         | 118                  |

|                      | Chapter 14<br>OmniVision Camera Driver                                 |                      |

| 14.1                 | OV5640 Using MIPI CSI-2 interface                                      | 119                  |

|                      | 14.1.1 Hardware Operation                                              | 119                  |

|                      | i.MX 6Dual/6Quad Linux Reference Manual, Rev. L3                       | .0.35_4.1.0, 09/2013 |

| Sec  | tion number Title                                   | Page |

|------|-----------------------------------------------------|------|

|      | 14.1.2 Software Operation                           | 119  |

|      | 14.1.3 Source Code Structure                        |      |

|      | 14.1.4 Linux Menu Configuration Options             | 120  |

| 14.2 | OV5640 Using parallel interface                     |      |

|      | 14.2.1 Hardware Operation                           | 121  |

|      | 14.2.2 Software Operation                           |      |

|      | 14.2.3 Source Code Structure                        |      |

|      | 14.2.4 Linux Menu Configuration Options             |      |

|      | Chapter 15<br>MIPI CSI2 Driver                      |      |

| 15.1 | Introduction                                        | 123  |

|      | 15.1.1 MIPI CSI2 Driver Overview                    | 123  |

|      | 15.1.2 Hardware Operation                           | 124  |

| 15.2 | Software Operation                                  | 124  |

|      | 15.2.1 MIPI CSI2 Driver Initialize Operation.       | 124  |

|      | 15.2.2 MIPI CSI2 Common API Operation               | 125  |

| 15.3 | Driver Features.                                    | 125  |

|      | 15.3.1 Source Code Structure                        |      |

|      | 15.3.2 Menu Configuration Options                   | 126  |

|      | 15.3.3 Programming Interface                        | 126  |

|      | 15.3.4 Interrupt Requirements                       | 127  |

|      | Chapter 16<br>Low-level Power Management (PM) Drive | er   |

| 16.1 | Hardware Operation.                                 |      |

|      | 16.1.1 Software Operation                           | 129  |

|      | 16.1.2 Source Code Structure                        |      |

|      | 16.1.3 Menu Configuration Options                   | 130  |

|      | 16.1.4 Programming Interface                        | 131  |

|      | 16.1.5 Unit Test                                    | 131  |

| Sec  | tion number Title                                | Page |

|------|--------------------------------------------------|------|

| 20.2 | Hardware Operation                               | 145  |

|      | 20.2.1 Thermal Driver Software Operation         | 146  |

| 20.3 | Driver Features                                  | 146  |

|      | 20.3.1 Source Code Structure                     | 146  |

|      | 20.3.2 Menu Configuration Options.               | 146  |

|      | 20.3.3 Programming Interface                     | 147  |

|      | 20.3.4 Interrupt Requirements                    | 147  |

| 20.4 | Unit Test                                        | 147  |

|      | Chapter 21<br>Anatop Regulator Driver            |      |

| 21.1 | Introduction.                                    | 149  |

|      | 21.1.1 Hardware Operation                        | 149  |

| 21.2 | Driver Features.                                 | 149  |

|      | 21.2.1 Software Operation.                       | 150  |

|      | 21.2.2 Regulator APIs                            | 150  |

|      | 21.2.3 Driver Interface Details                  | 151  |

|      | 21.2.4 Source Code Structure                     | 151  |

|      | 21.2.5 Menu Configuration Options                | 151  |

|      | Chapter 22<br>SNVS Real Time Clock (SRTC) Driver |      |

| 22.1 | Introduction.                                    | 153  |

|      | 22.1.1 Hardware Operation                        | 153  |

| 22.2 | Software Operation                               | 153  |

|      | 22.2.1 IOCTL                                     | 153  |

|      | 22.2.2 Keeping Alive in the Power Off State      | 154  |

| 22.3 | Driver Features                                  | 154  |

|      | 22.3.1 Source Code Structure                     | 155  |

|      | 22.3.2 Menu Configuration Options.               | 155  |

# Chapter 23 Advanced Linux Sound Architecture (ALSA) System on a Chip (ASoC) Sound Driver

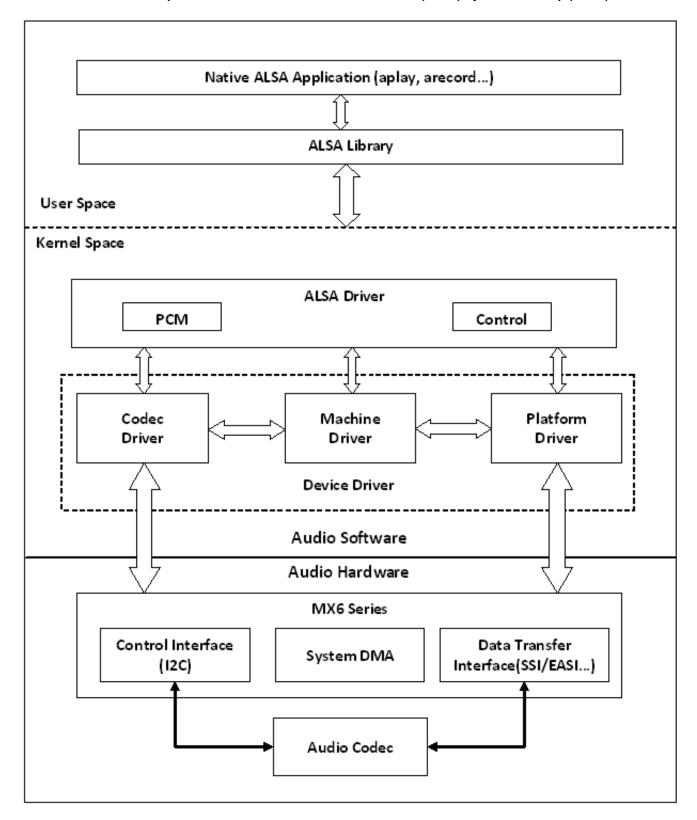

| 23.1 | ALSA Sound Driver Introduction.                             | 157 |

|------|-------------------------------------------------------------|-----|

| 23.2 | SoC Sound Card                                              | 160 |

|      | 23.2.1 Stereo CODEC Features                                | 160 |

|      | 23.2.2 7.1 Audio Codec Features                             | 161 |

|      | 23.2.3 AM/FM Codec Features                                 | 161 |

|      | 23.2.4 Sound Card Information                               | 161 |

| 23.3 | Hardware Operation.                                         | 162 |

|      | 23.3.1 Stereo Audio CODEC                                   | 162 |

|      | 23.3.2 7.1 Audio Codec                                      | 163 |

|      | 23.3.3 AM/FM Codec                                          | 163 |

| 23.4 | Software Operation.                                         | 163 |

|      | 23.4.1 ASoC Driver Source Architecture                      | 164 |

|      | 23.4.2 Sound Card Registration.                             | 165 |

|      | 23.4.3 Device Open                                          | 165 |

|      | 23.4.4 Platform Data                                        | 166 |

|      | 23.4.5 Menu Configuration Options                           | 166 |

| 23.5 | Unit Test.                                                  | 167 |

|      | 23.5.1 Stereo CODEC Unit Test                               | 167 |

|      | 23.5.2 7.1 Audio Codec Unit Test                            | 168 |

|      | 23.5.3 AM/FM Codec Unit Test                                | 169 |

|      | Chapter 24 Asynchronous Sample Rate Converter (ASRC) Driver |     |

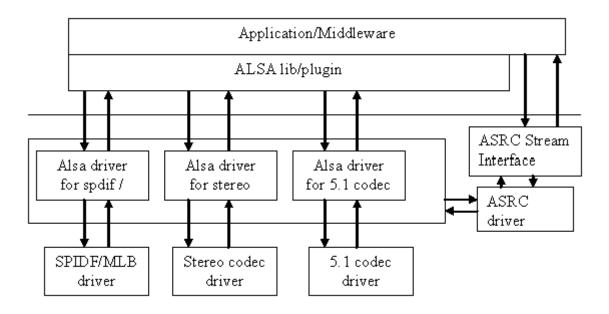

| 24.1 | Introduction                                                | 171 |

|      | 24.1.1 Hardware Operation                                   | 171 |

| 24.2 | Software Operation                                          | 172 |

|      | 24.2.1 Sequence for Memory to ASRC to Memory                | 173 |

|      | 24.2.2 Sequence for Memory to ASRC to Peripheral            | 173 |

| Sec  | tion number                                | Title                                        | Page   |

|------|--------------------------------------------|----------------------------------------------|--------|

| 24.3 | Source Code Structure                      |                                              | 174    |

|      | 24.3.1 Linux Menu Configuration Options    |                                              | 174    |

| 24.4 | Platform Data                              |                                              | 174    |

|      | 24.4.1 Programming Interface (Exported API | and IOCTLs)                                  | 175    |

|      | The Sony/Philips [                         | Chapter 25<br>Digital Interface (S/PDIF) Dri | ver    |

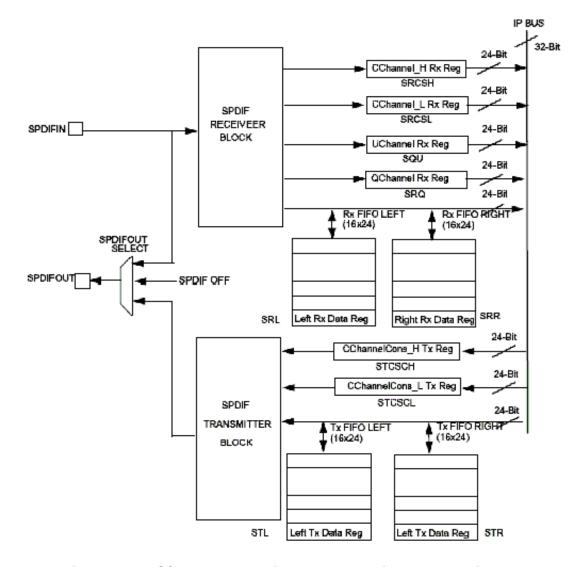

| 25.1 | Introduction                               |                                              | 177    |

|      | 25.1.1 S/PDIF Overview                     |                                              | 177    |

|      | 25.1.2 Hardware Overview                   |                                              | 178    |

|      | 25.1.3 Software Overview                   |                                              | 179    |

|      | 25.1.4 ASoC layer                          |                                              | 179    |

| 25.2 | S/PDIF Tx Driver                           |                                              | 179    |

|      | 25.2.1 Driver Design                       |                                              | 180    |

|      | 25.2.2 Provided User Interface             |                                              | 180    |

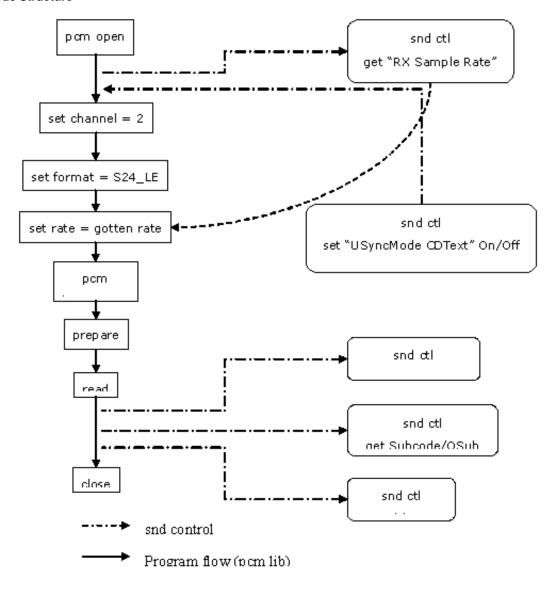

| 25.3 | S/PDIF Rx Driver                           |                                              | 181    |

|      | 25.3.1 Driver Design                       |                                              | 182    |

|      | 25.3.2 Provided User Interfaces            |                                              | 182    |

| 25.4 | Source Code Structure                      |                                              | 184    |

| 25.5 | Menu Configuration Options                 |                                              | 185    |

| 25.6 | Platform Data                              |                                              | 185    |

| 25.7 | Interrupts and Exceptions                  |                                              | 186    |

| 25.8 | Unit Test Preparation                      |                                              | 186    |

|      | 25.8.1 Tx test step                        |                                              | 186    |

|      | 25.8.2 Rx test step                        |                                              | 186    |

|      | SPI NOR Flash Memor                        | Chapter 26<br>ry Technology Device (MTD)     | Driver |

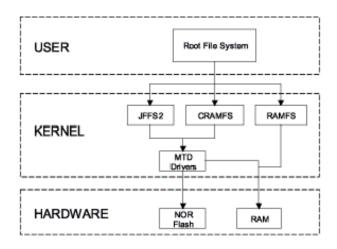

| 26.1 | Introduction                               |                                              | 189    |

|      | 26.1.1 Hardware Operation                  |                                              | 189    |

|      | 26.1.2 Software Operation                  |                                              | 190    |

| Section number                 | Title                                        | Page        |

|--------------------------------|----------------------------------------------|-------------|

| 26.1.3 Driver Features         |                                              | 190         |

| 26.1.4 Source Code Structure   |                                              | 190         |

| 26.1.5 Menu Configuration Op   | otions                                       | 191         |

|                                | Chapter 27<br>MMC/SD/SDIO Host Driver        |             |

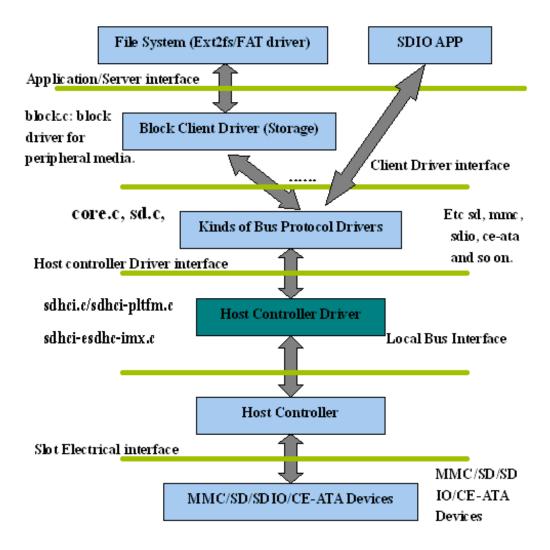

| 27.1 Introduction              |                                              | 193         |

| 27.1.1 Hardware Operation      |                                              | 193         |

| 27.1.2 Software Operation      |                                              | 194         |

| 27.2 Driver Features           |                                              | 196         |

| 27.2.1 Source Code Structure   |                                              | 197         |

| 27.2.2 Menu Configuration Op   | otions                                       | 197         |

| 27.2.3 Platform Data           |                                              | 198         |

| 27.2.4 Programming Interface.  |                                              | 198         |

| 27.2.5 Loadable Module Opera   | ations                                       | 199         |

|                                | Chapter 28<br>NAND GPMI Flash Driver         |             |

| 28.1 Introduction              |                                              | 201         |

| 28.1.1 Hardware Operation      |                                              | 201         |

| 28.2 Software Operation        |                                              | 201         |

| 28.2.1 Basic Operations: Read/ | /Write                                       | 202         |

| 28.2.2 Error Correction        |                                              | 202         |

| 28.2.3 Boot Control Block Man  | nagement                                     | 202         |

| 28.2.4 Bad Block Handling      |                                              |             |

| 28.3 Source Code Structure     |                                              | 203         |

| 28.3.1 Menu Configuration Op   | otions                                       |             |

|                                | Chapter 29<br>SATA Driver                    |             |

| 29.1 Hardware Operation        |                                              | 205         |

| 29.1.1 Software Operation      |                                              | 205         |

| 29.1.2 Source Code Structure C | Configuration                                | 205         |

| i.MX 6Dual/6Qu                 | ad Linux Reference Manual, Rev. L3.0.35_4.1. | .0, 09/2013 |

| Sec  | tion number Title                                                              | Page |

|------|--------------------------------------------------------------------------------|------|

|      | 29.1.3 Linux Menu Configuration Options                                        | 205  |

|      | 29.1.4 Board Configuration Options.                                            | 206  |

| 29.2 | Programming Interface.                                                         | 206  |

|      | 29.2.1 Usage Example2                                                          | 206  |

|      | 29.2.2 Usage Example                                                           | 207  |

|      | Chapter 30<br>Inter-IC (I2C) Driver                                            |      |

| 30.1 | Introduction                                                                   | 209  |

|      | 30.1.1 I2C Bus Driver Overview                                                 | 209  |

|      | 30.1.2 I2C Device Driver Overview                                              | 210  |

|      | 30.1.3 Hardware Operation                                                      | 210  |

| 30.2 | Software Operation                                                             | 210  |

|      | 30.2.1 I2C Bus Driver Software Operation                                       | 210  |

|      | 30.2.2 I2C Device Driver Software Operation                                    | 211  |

| 30.3 | Driver Features.                                                               | 211  |

|      | 30.3.1 Source Code Structure                                                   | 212  |

|      | 30.3.2 Menu Configuration Options                                              | 212  |

|      | 30.3.3 Programming Interface                                                   | 212  |

|      | 30.3.4 Interrupt Requirements.                                                 | 212  |

|      | Chapter 31<br>Enhanced Configurable Serial Peripheral Interface (ECSPI) Driver |      |

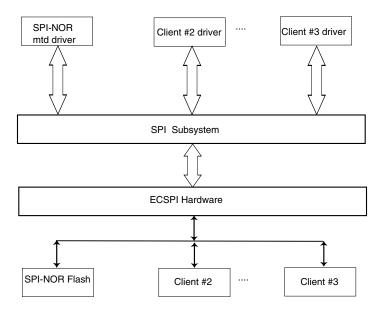

| 31.1 | Introduction                                                                   | 215  |

|      | 31.1.1 Hardware Operation                                                      | 215  |

| 31.2 | Software Operation.                                                            | 215  |

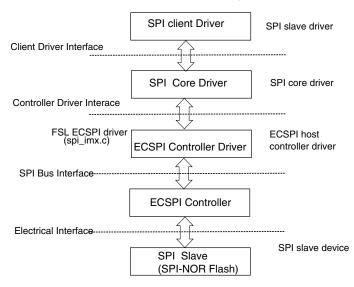

|      | 31.2.1 SPI Sub-System in Linux                                                 | 216  |

|      | 31.2.2 Software Limitations                                                    | 217  |

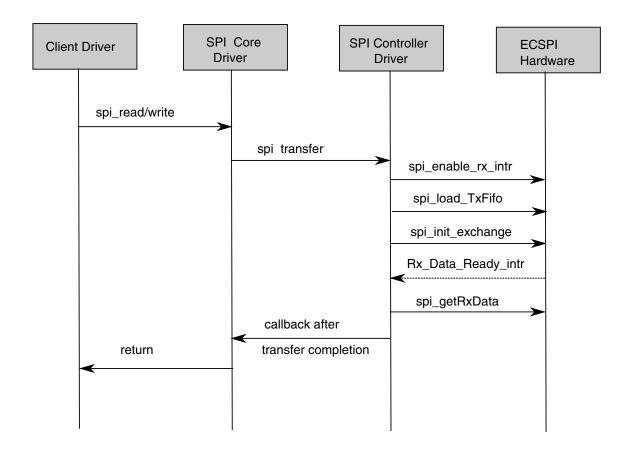

|      | 31.2.3 Standard Operations                                                     | 217  |

|      | 31.2.4 ECSPI Synchronous Operation                                             | 218  |

| Sec  | tion number                        | Title                                | Page |

|------|------------------------------------|--------------------------------------|------|

| 31.3 | Driver Features                    |                                      | 220  |

|      | 31.3.1 Source Code Structure       |                                      | 220  |

|      | 31.3.2 Menu Configuration Options  |                                      | 220  |

|      | 31.3.3 Programming Interface       |                                      | 220  |

|      | 31.3.4 Interrupt Requirements      |                                      | 221  |

|      |                                    | Chapter 32<br>FlexCAN Driver         |      |

| 32.1 | Driver Overview                    |                                      | 223  |

|      | 32.1.1 Hardware Operation          |                                      | 223  |

|      | 32.1.2 Software Operation          |                                      | 223  |

|      | 32.1.3 Source Code Structure       |                                      | 224  |

|      | 32.1.4 Linux Menu Configuration Op | otions                               | 224  |

|      |                                    | Chapter 33<br>Media Local Bus Driver |      |

| 33.1 | Introduction                       |                                      | 227  |

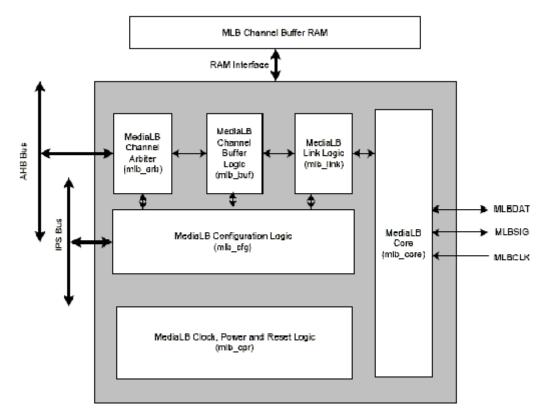

|      | 33.1.1 MLB Device Module           |                                      | 227  |

|      | 33.1.2 Supported Feature           |                                      | 228  |

|      | 33.1.3 Modes of Operation          |                                      | 229  |

|      | 33.1.4 MLB Driver Overview         |                                      | 229  |

| 33.2 | MLB Driver                         |                                      | 229  |

|      | 33.2.1 Supported Features          |                                      | 229  |

|      | 33.2.2 MLB Driver Architecture     |                                      | 229  |

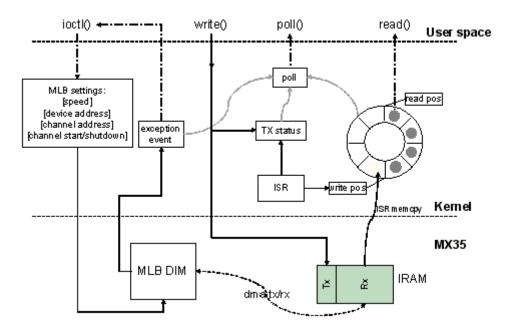

|      | 33.2.3 Software Operation          |                                      | 231  |

| 33.3 | Driver Files                       |                                      | 232  |

| 33.4 | Menu Configuration Options         |                                      | 232  |

|      |                                    | Chapter 34<br>ARC USB Driver         |      |

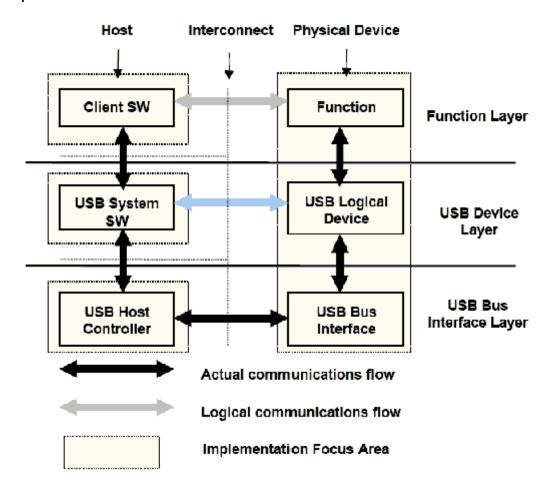

| 34.1 | Introduction                       |                                      | 233  |

|      | 34.1.1 Architectural Overview      |                                      | 233  |

| tion number Title                                 | Page               |

|---------------------------------------------------|--------------------|

| Hardware Operation                                | 234                |

| 34.2.1 Software Operation                         | 234                |

| 34.2.2 Source Code Structure                      | 235                |

| 34.2.3 Menu Configuration Options                 | 236                |

| 34.2.4 Programming Interface                      | 239                |

| System WakeUp                                     | 239                |

| 34.3.1 USB Wakeup usage                           | 239                |

| 34.3.2 How to Enable USB WakeUp System Ability    | 239                |

| 34.3.3 WakeUp Events Supported by USB             | 240                |

| 34.3.4 How to Close the USB Child Device Power    | 241                |

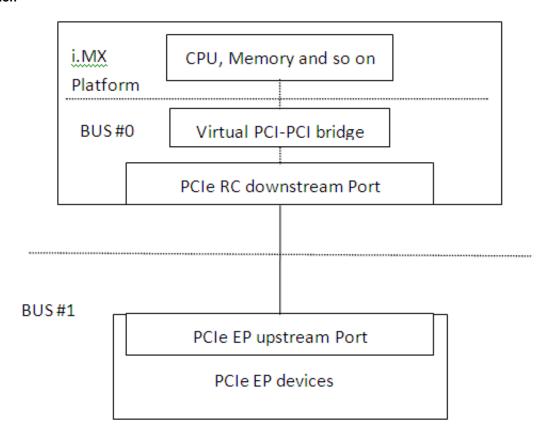

| Chapter 35 i.MX 6 PCI Express Root Complex Driver |                    |

| Introduction                                      | 243                |

| 35.1.1 PCIe                                       | 243                |

| 35.1.2 Terminology and Conventions                | 243                |

| 35.1.3 PCIe Topology on i.MX 6 in PCIe RC Mode    | 245                |

| 35.1.4 Features                                   | 247                |

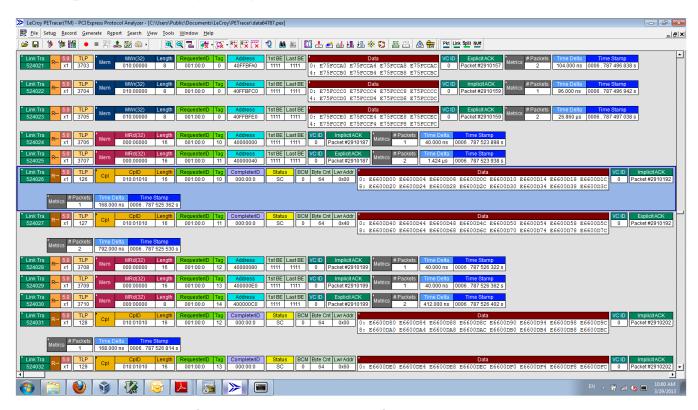

| Linux PCI Subsystem and RC driver                 | 247                |

| 35.2.1 RC driver source files                     | 248                |

| 35.2.2 Kernel configurations.                     | 248                |

| System Resource: Memory Layout                    | 249                |

| 35.3.1 System Resource: Interrupt lines           | 249                |

| Using PCIe Endpoint and running Tests             | 250                |

| 35.4.1 Ensuring PCIe System Initialization.       | 251                |

| 35.4.2 Tests                                      | 251                |

| 35.4.3 Known Issues                               | 252                |

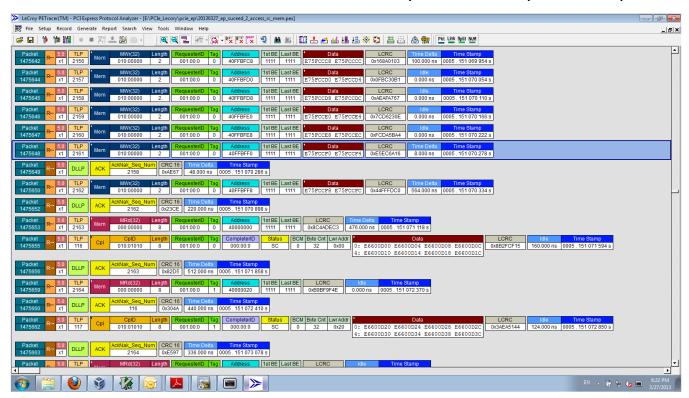

| i.MX 6Quad SD PCIe RC/EP Validation System        | 252                |

| 35.5.1 Hardware Setup                             | 252                |

| 35.5.2 Software Configurations                    | 252                |

|                                                   | Hardware Operation |

|      | tion number Title                              | Page   |

|------|------------------------------------------------|--------|

|      | 35.5.3 Features                                |        |

|      | 35.5.4 Results                                 |        |

|      | Chapter 36<br>WEIM NOR Driver                  |        |

| 36.1 | Introduction                                   | 257    |

| 36.2 | Hardware Operation                             | 257    |

| 36.3 | Software Operation                             | 257    |

| 36.4 | Source Code                                    | 257    |

| 36.5 | Enabling the WEIM NOR                          | 257    |

|      | Chapter 37<br>Fast Ethernet Controller (FEC) D | )river |

| 37.1 | Introduction                                   |        |

| 37.2 | Hardware Operation.                            |        |

|      | 37.2.1 Software Operation                      |        |

|      | 37.2.2 Source Code Structure                   |        |

|      | 37.2.3 Menu Configuration Options              |        |

| 37.3 | Programming Interface                          |        |

|      | 37.3.1 Device-Specific Defines                 |        |

|      | 37.3.2 Getting a MAC Address                   |        |

|      | Chapter 38<br>ENET IEEE-1588 Driver            |        |

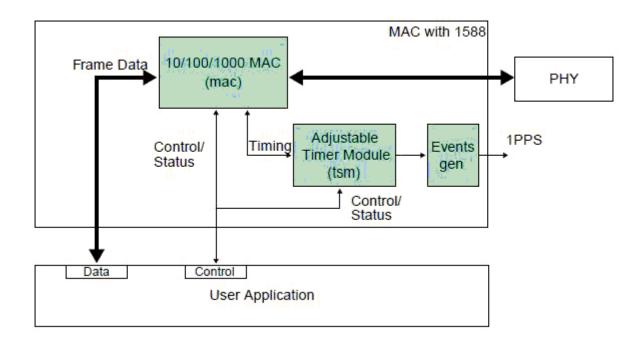

| 38.1 | Hardware Operation.                            |        |

|      | 38.1.1 Transmit Timestamping                   |        |

|      | 38.1.2 Receive Timestamping                    | 266    |

| 38.2 | Software Operation                             | 266    |

|      | 38.2.1 Source Code Structure                   | 267    |

|      | 38.2.2 Linux Menu Configuration Options        | 267    |

| 38.3 | Programming Interface                          | 267    |

|      | 38.3.1 IXXAT Specific Data structure Defines   | 267    |

|      | 38.3.2 IXXAT IOCTL Commands Defines            |        |

# Chapter 39 Universal Asynchronous Receiver/Transmitter (UART) Driver

| 39.1 | Introduction                             | 271 |

|------|------------------------------------------|-----|

| 39.2 | Hardware Operation                       | 272 |

|      | 39.2.1 Software Operation                | 272 |

|      | 39.2.2 Driver Features                   | 273 |

|      | 39.2.3 Source Code Structure             | 273 |

| 39.3 | Configuration.                           | 274 |

|      | 39.3.1 Menu Configuration Options        | 274 |

|      | 39.3.2 Source Code Configuration Options | 275 |

|      | 39.3.3 Chip Configuration Options        | 275 |

|      | 39.3.4 Board Configuration Options       | 275 |

| 39.4 | Programming Interface                    | 275 |

|      | 39.4.1 Interrupt Requirements            | 275 |

|      | Chapter 40<br>AR6003 WiFi                |     |

| 40.1 | Hardware Operation                       | 277 |

|      | 40.1.1 Software Operation                | 277 |

|      | 40.1.2 Driver features                   | 277 |

|      | 40.1.3 Source Code Structure             | 278 |

|      | 40.1.4 Linux Menu Configuration Options. | 278 |

|      | Chapter 41<br>Bluetooth Driver           |     |

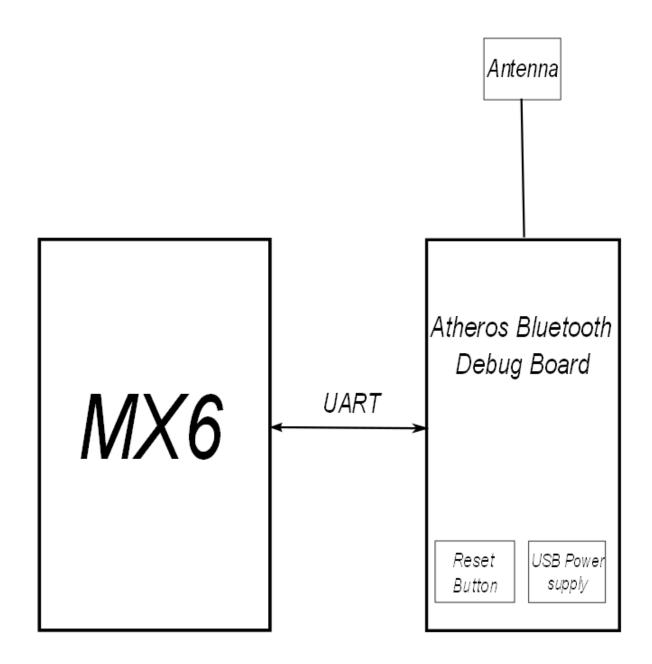

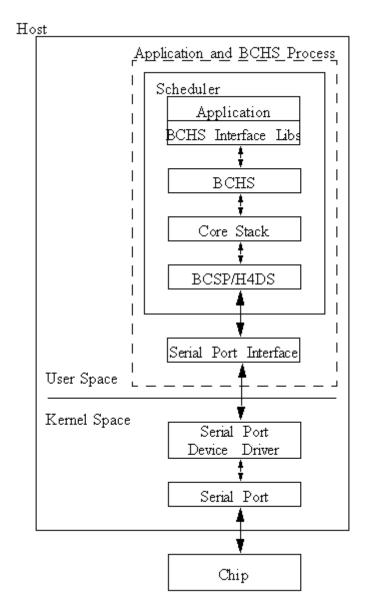

| 41.1 | Introduction.                            | 279 |

|      | 41.1.1 Hardware Operation                | 279 |

| 41.2 | Software Operation                       | 281 |

|      | 41.2.1 UART Control                      | 282 |

|      | 41.2.2 Reset and Power control           | 283 |

|      | 41.2.3 Configuration                     | 283 |

# Chapter 42 Pulse-Width Modulator (PWM) Driver

|      | Taloo Matti Modalator (1 1111) 211101   |     |

|------|-----------------------------------------|-----|

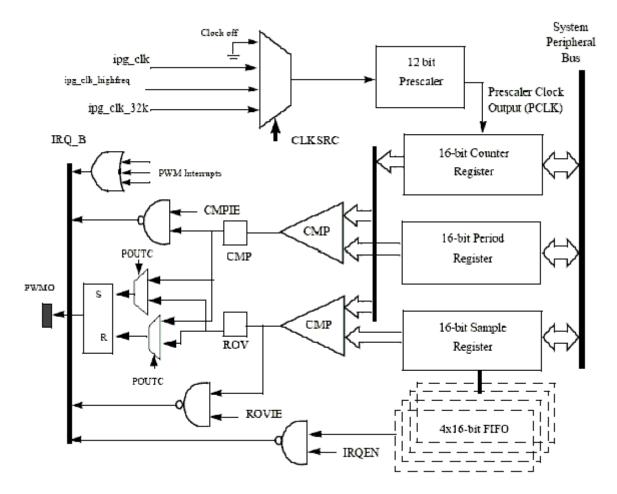

| 42.1 | Introduction.                           | 285 |

|      | 42.1.1 Hardware Operation               | 285 |

|      | 42.1.2 Clocks                           | 286 |

|      | 42.1.3 Software Operation               | 287 |

|      | 42.1.4 Driver Features                  | 287 |

|      | 42.1.5 Source Code Structure            | 287 |

|      | 42.1.6 Menu Configuration Options.      | 288 |

|      | Chapter 43<br>Watchdog (WDOG) Driver    |     |

| 43.1 | Introduction                            | 289 |

|      | 43.1.1 Hardware Operation               | 289 |

|      | 43.1.2 Software Operation               | 289 |

| 43.2 | Generic WDOG Driver                     | 289 |

|      | 43.2.1 Driver Features                  | 290 |

|      | 43.2.2 Menu Configuration Options       | 290 |

|      | 43.2.3 Source Code Structure            | 290 |

|      | 43.2.4 Programming Interface            | 291 |

|      | Chapter 44 OProfile                     |     |

| 44.1 | Introduction                            | 293 |

|      | 44.1.1 Overview                         | 293 |

|      | 44.1.2 Features                         | 293 |

|      | 44.1.3 Hardware Operation               | 294 |

| 44.2 | Software Operation.                     | 294 |

|      | 44.2.1 Architecture Specific Components | 294 |

|      | 44.2.2 oprofilefs Pseudo Filesystem     | 295 |

|      | 44.2.3 Generic Kernel Driver            | 295 |

|      | 44.2.4 OProfile Daemon                  | 295 |

|      |                                         |     |

| Sect  | tion number Title                                                 | Page |

|-------|-------------------------------------------------------------------|------|

|       | 44.2.5 Post Profiling Tools                                       | 296  |

| 44.3  | Requirements                                                      | 296  |

|       | 44.3.1 Source Code Structure                                      | 296  |

|       | 44.3.2 Menu Configuration Options.                                | 296  |

|       | 44.3.3 Programming Interface                                      | 297  |

|       | 44.3.4 Interrupt Requirements                                     | 297  |

|       | 44.3.5 Example Software Configuration.                            | 297  |

|       | Chapter 45 CAAM (Cryptographic Acceleration and Assurance Module) |      |

| 45.1  | CAAM Device Driver Overview                                       | 299  |

| 45.2  | Configuration and Job Execution Level                             | 299  |

| 45.3  | Control/Configuration Driver                                      | 300  |

| 45.4  | Job Ring Driver                                                   | 300  |

| 45.5  | API Interface Level                                               | 301  |

| 45.6  | Driver Configuration.                                             | 304  |

| 45.7  | Limitations                                                       | 305  |

| 45.8  | Limitations in the Existing Implementation Overview               | 305  |

| 45.9  | Initialize Keystore Management Interface                          | 306  |

| 45.10 | Detect Available Secure Memory Storage Units                      | 306  |

| 45.11 | Establish Keystore in Detected Unit                               | 307  |

| 45.12 | Release Keystore                                                  | 307  |

| 45.13 | Allocate a Slot from the Keystore                                 | 308  |

| 45.14 | Load Data into a Keystore Slot                                    | 308  |

| 45.15 | Demo Image Update                                                 | 309  |

| 45.16 | Decapsulate Data in the Keystore                                  | 309  |

| 45.17 | Read Data From a Keystore Slot                                    | 310  |

| 45.18 | Release a Slot back to the Keystore                               | 311  |

| 45.19 | CAAM/SNVS - Security Violation Handling Interface Overview        | 313  |

| 45.20 | Operation                                                         | 313  |

| Sect  | ion number                     | Title | Page |

|-------|--------------------------------|-------|------|

| 45.21 | Configuration Interface        |       | 313  |

| 45.22 | Install a Handler              |       | 314  |

| 45.23 | Remove an Installed Driver     |       | 314  |

| 45.24 | Driver Configuration CAAM/SNVS |       | 315  |

# Chapter 1 About this Book

#### 1.1 Audience

This document is targeted to individuals who will port the i.MX Linux BSP to customer-specific products.

The audience is expected to have a working knowledge of the Linux 3.0 kernel internals, driver models, and i.MX processors.

#### 1.1.1 Conventions

This document uses the following notational conventions:

- Courier monospaced type indicate commands, command parameters, code examples, and file and directory names.

- *Italic* type indicates replaceable command or function parameters.

- **Bold** type indicates function names.

### 1.1.2 Definitions, Acronyms, and Abbreviations

The following table defines the acronyms and abbreviations used in this document.

**Definitions and Acronyms**

| Term                   | Definition                                                |

|------------------------|-----------------------------------------------------------|

| ADC                    | Asynchronous Display Controller                           |

| address<br>translation | Address conversion from virtual domain to physical domain |

| API                    | Application Programming Interface                         |

| ARM <sup>®</sup>       | Advanced RISC Machines processor architecture             |

Table continues on the next page...

#### **Audience**

| Term       | Definition                                                                                                                                                                                                                                                                                                                                     |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AUDMUX     | Digital audio MUX-provides a programmable interconnection for voice, audio, and synchronous data routing between host serial interfaces and peripheral serial interfaces                                                                                                                                                                       |

| BCD        | Binary Coded Decimal                                                                                                                                                                                                                                                                                                                           |

| bus        | A path between several devices through data lines                                                                                                                                                                                                                                                                                              |

| bus load   | The percentage of time a bus is busy                                                                                                                                                                                                                                                                                                           |

| CODEC      | Coder/decoder or compression/decompression algorithm-used to encode and decode (or compress and decompress) various types of data                                                                                                                                                                                                              |

| CPU        | Central Processing Unit-generic term used to describe a processing core                                                                                                                                                                                                                                                                        |

| CRC        | Cyclic Redundancy Check-Bit error protection method for data communication                                                                                                                                                                                                                                                                     |

| CSI        | Camera Sensor Interface                                                                                                                                                                                                                                                                                                                        |

| DFS        | Dynamic Frequency Scaling                                                                                                                                                                                                                                                                                                                      |

| DMA        | Direct Memory Access-an independent block that can initiate memory-to-memory data transfers                                                                                                                                                                                                                                                    |

| DPM        | Dynamic Power Management                                                                                                                                                                                                                                                                                                                       |

| DRAM       | Dynamic Random Access Memory                                                                                                                                                                                                                                                                                                                   |

| DVFS       | Dynamic Voltage Frequency Scaling                                                                                                                                                                                                                                                                                                              |

| EMI        | External Memory Interface-controls all IC external memory accesses (read/write/erase/program) from all the masters in the system                                                                                                                                                                                                               |

| Endian     | Refers to byte ordering of data in memory. Little endian means that the least significant byte of the data is stored in a lower address than the most significant byte. In big endian, the order of the bytes is reversed                                                                                                                      |

| EPIT       | Enhanced Periodic Interrupt Timer-a 32-bit set and forget timer capable of providing precise interrupts at regular intervals with minimal processor intervention                                                                                                                                                                               |

| FCS        | Frame Checker Sequence                                                                                                                                                                                                                                                                                                                         |

| FIFO       | First In First Out                                                                                                                                                                                                                                                                                                                             |

| FIPS       | Federal Information Processing Standards-United States Government technical standards published by the National Institute of Standards and Technology (NIST). NIST develops FIPS when there are compelling Federal government requirements such as for security and interoperability but no acceptable industry standards                      |

| FIPS-140   | Security requirements for cryptographic modules-Federal Information Processing Standard 140-2(FIPS 140-2) is a standard that describes US Federal government requirements that IT products should meet for Sensitive, but Unclassified (SBU) use                                                                                               |

| Flash      | A non-volatile storage device similar to EEPROM, where erasing can be done only in blocks or the entire chip.                                                                                                                                                                                                                                  |

| Flash path | Path within ROM bootstrap pointing to an executable Flash application                                                                                                                                                                                                                                                                          |

| Flush      | Procedure to reach cache coherency. Refers to removing a data line from cache. This process includes cleaning the line, invalidating its VBR and resetting the tag valid indicator. The flush is triggered by a software command                                                                                                               |

| GPIO       | General Purpose Input/Output                                                                                                                                                                                                                                                                                                                   |

| hash       | Hash values are produced to access secure data. A hash value (or simply hash), also called a message digest, is a number generated from a string of text. The hash is substantially smaller than the text itself, and is generated by a formula in such a way that it is extremely unlikely that some other text produces the same hash value. |

| I/O        | Input/Output                                                                                                                                                                                                                                                                                                                                   |

| ICE        | In-Circuit Emulation                                                                                                                                                                                                                                                                                                                           |

| IP         | Intellectual Property                                                                                                                                                                                                                                                                                                                          |

| IPU        | Image Processing Unit -supports video and graphics processing functions and provides an interface to video/still image sensors and displays                                                                                                                                                                                                    |

Table continues on the next page...

| Term                | Definition                                                                                                                                                                                                                                                                                                                                                              |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IrDA                | Infrared Data Association-a nonprofit organization whose goal is to develop globally adopted specifications for infrared wireless communication                                                                                                                                                                                                                         |  |

| ISR                 | Interrupt Service Routine                                                                                                                                                                                                                                                                                                                                               |  |

| JTAG                | JTAG (IEEE Standard 1149.1) A standard specifying how to control and monitor the pins of compliant devices on a printed circuit board                                                                                                                                                                                                                                   |  |

| Kill                | Abort a memory access                                                                                                                                                                                                                                                                                                                                                   |  |

| KPP                 | KeyPad Port-16-bit peripheral used as a keypad matrix interface or as general purpose input/output (I/O)                                                                                                                                                                                                                                                                |  |

| line                | Refers to a unit of information in the cache that is associated with a tag                                                                                                                                                                                                                                                                                              |  |

| LRU                 | Least Recently Used-a policy for line replacement in the cache                                                                                                                                                                                                                                                                                                          |  |

| MMU                 | Memory Management Unit-a component responsible for memory protection and address translation                                                                                                                                                                                                                                                                            |  |

| MPEG                | Moving Picture Experts Group-an ISO committee that generates standards for digital video compression and audio. It is also the name of the algorithms used to compress moving pictures and video                                                                                                                                                                        |  |

| MPEG                | Several standards of compression for moving pictures and video:                                                                                                                                                                                                                                                                                                         |  |

| standards           | <ul> <li>MPEG-1 is optimized for CD-ROM and is the basis for MP3</li> <li>MPEG-2 is defined for broadcast video in applications such as digital television set-top boxes and DVD</li> <li>MPEG-3 was merged into MPEG-2</li> <li>MPEG-4 is a standard for low-bandwidth video telephony and multimedia on the World-Wide Web</li> </ul>                                 |  |

| MQSPI               | Multiple Queue Serial Peripheral Interface-used to perform serial programming operations necessary to configure radio subsystems and selected peripherals                                                                                                                                                                                                               |  |

| MSHC                | Memory Stick Host Controller                                                                                                                                                                                                                                                                                                                                            |  |

| NAND Flash          | Flash ROM technology-NAND Flash architecture is one of two flash technologies (the other being NOR) used in memory cards such as the Compact Flash cards. NAND is best suited to flash devices requiring high capacity data storage. NAND flash devices offer storage space up to 512-Mbyte and offers faster erase, write, and read capabilities over NOR architecture |  |

| NOR Flash           | See NAND Flash                                                                                                                                                                                                                                                                                                                                                          |  |

| PCMCIA              | Personal Computer Memory Card International Association-a multi-company organization that has developed a standard for small, credit card-sized devices, called PC Cards. There are three types of PCMCIA cards that have the same rectangular size (85.6 by 54 millimeters), but different widths                                                                      |  |

| physical<br>address | The address by which the memory in the system is physically accessed                                                                                                                                                                                                                                                                                                    |  |

| PLL                 | Phase Locked Loop-an electronic circuit controlling an oscillator so that it maintains a constant phase angle (a lock) on the frequency of an input, or reference, signal                                                                                                                                                                                               |  |

| RAM                 | Random Access Memory                                                                                                                                                                                                                                                                                                                                                    |  |

| RAM path            | Path within ROM bootstrap leading to the downloading and the execution of a RAM application                                                                                                                                                                                                                                                                             |  |

| RGB                 | The RGB color model is based on the additive model in which Red, Green, and Blue light are combined to create other colors. The abbreviation RGB comes from the three primary colors in additive light models                                                                                                                                                           |  |

| RGBA                | RGBA color space stands for Red Green Blue Alpha. The alpha channel is the transparency channel, and is unique to this color space. RGBA, like RGB, is an additive color space, so the more of a color placed, the lighter the picture gets. PNG is the best known image format that uses the RGBA color space                                                          |  |

| RNGA                | Random Number Generator Accelerator-a security hardware module that produces 32-bit pseudo random numbers as part of the security module                                                                                                                                                                                                                                |  |

| ROM                 | Read Only Memory                                                                                                                                                                                                                                                                                                                                                        |  |

| ROM<br>bootstrap    | Internal boot code encompassing the main boot flow as well as exception vectors                                                                                                                                                                                                                                                                                         |  |

| RTIC                | Real-Time Integrity Checker-a security hardware module                                                                                                                                                                                                                                                                                                                  |  |

| SCC                 | SeCurity Controller-a security hardware module                                                                                                                                                                                                                                                                                                                          |  |

Table continues on the next page...

#### **Audience**

| Term   | Definition                                                                                                                                                                                                                                                                                                                                                                                    |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDMA   | Smart Direct Memory Access                                                                                                                                                                                                                                                                                                                                                                    |

| SDRAM  | Synchronous Dynamic Random Access Memory                                                                                                                                                                                                                                                                                                                                                      |

| SoC    | System on a Chip                                                                                                                                                                                                                                                                                                                                                                              |

| SPBA   | Shared Peripheral Bus Arbiter-a three-to-one IP-Bus arbiter, with a resource-locking mechanism                                                                                                                                                                                                                                                                                                |

| SPI    | Serial Peripheral Interface-a full-duplex synchronous serial interface for connecting low-/medium-bandwidth external devices using four wires. SPI devices communicate using a master/slave relationship over two data lines and two control lines: Also see SS, SCLK, MISO, and MOSI                                                                                                         |

| SRAM   | Static Random Access Memory                                                                                                                                                                                                                                                                                                                                                                   |

| SSI    | Synchronous-Serial Interface-standardized interface for serial data transfer                                                                                                                                                                                                                                                                                                                  |

| TBD    | To Be Determined                                                                                                                                                                                                                                                                                                                                                                              |

| UART   | Universal Asynchronous Receiver/Transmitter-asynchronous serial communication to external devices                                                                                                                                                                                                                                                                                             |

| UID    | Unique ID-a field in the processor and CSF identifying a device or group of devices                                                                                                                                                                                                                                                                                                           |

| USB    | Universal Serial Bus-an external bus standard that supports high speed data transfers. The USB 1.1 specification supports data transfer rates of up to 12 Mb/s and USB 2.0 has a maximum transfer rate of 480 Mbps. A single USB port can be used to connect up to 127 peripheral devices, such as mice, modems, and keyboards. USB also supports Plug-and-Play installation and hot plugging |

| USBOTG | USB On The Go-an extension of the USB 2.0 specification for connecting peripheral devices to each other. USBOTG devices, also known as dual-role peripherals, can act as limited hosts or peripherals themselves depending on how the cables are connected to the devices, and they also can connect to a host PC                                                                             |

| word   | A group of bits comprising 32-bits                                                                                                                                                                                                                                                                                                                                                            |

# **Chapter 2 Machine Specific Layer (MSL)**

#### 2.1 Introduction

The Machine Specific Layer (MSL) provides the Linux kernel with the following machine-dependent components:

- Interrupts including GPIO and EDIO (only on certain platforms)

- Timer

- Memory map

- General Purpose Input/Output (GPIO) including IOMUX on certain platforms

- Shared Peripheral Bus Arbiter (SPBA)

- Smart Direct Memory Access (SDMA)

These modules are normally available in the following directory:

```

<ltib_dir>/rpm/BUILD/linux/arch/arm/mach-mx6 for i.MX 6 platform

```

The header files are implemented under the following directory:

```

<ltib dir>/rpm/BUILD/linux/arch/arm/plat-mxc/include/mach

```

The MSL layer contains not only the modules common to all the boards using the same processor, such as the interrupts and timer, but it also contains modules specific to each board, such as the memory map. The following sections describe the basic hardware and software operations and the software interfaces for MSL modules. First, the common modules, such as Interrupts and Timer are discussed. Next, the board-specific modules, such as Memory Map and General Purpose Input/Output (GPIO) (including IOMUX on some platforms) are detailed. Because of the complexity of the SDMA module, its design is explained in SDMA relevant chapter.

Each of the following sections contains an overview of the hardware operation. For more information, see the corresponding device documentation.

# 2.2 Interrupts (Operation)

This section explains the hardware and software operation of interrupts on the device.

### 2.2.1 Interrupt Hardware Operation

The Interrupt Controller controls and prioritizes a maximum of 128 internal and external interrupt sources.

Each source can be enabled or disabled by configuring the Interrupt Enable Register or using the Interrupt Enable/Disable Number Registers. When an interrupt source is enabled and the corresponding interrupt source is asserted, the Interrupt Controller asserts a normal or a fast interrupt request depending on the associated Interrupt Type Register settings.

Interrupt Controller registers can only be accessed in supervisor mode. The Interrupt Controller interrupt requests are prioritized in the following order: fast interrupts and normal interrupts for the highest priority level, then highest source number with the same priority. There are 16 normal interrupt levels for all interrupt sources, with level zero being the lowest priority. The interrupt levels are configurable through eight normal interrupt priority level registers. Those registers, along with the Normal Interrupt Mask Register, support software-controlled priority levels for normal interrupts and priority masking.

### 2.2.2 Interrupt Software Operation