# RENESAS

## DATASHEET

## ISL79987, ISL79988

4-Channel Differential Input Video Decoder with MIPI-CSI2/BT.656 Output for Around View Applications

FN8907 Rev.1.00 Mar 19, 2019

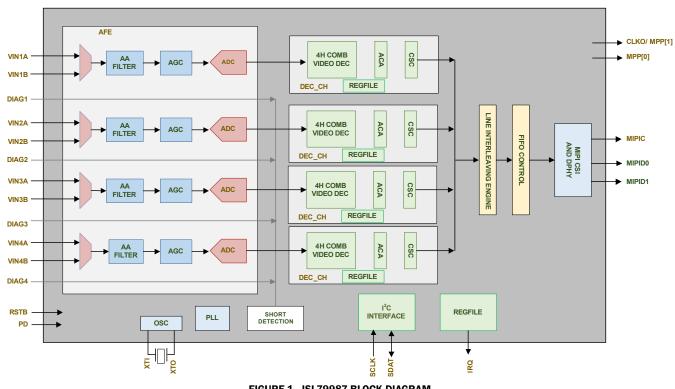

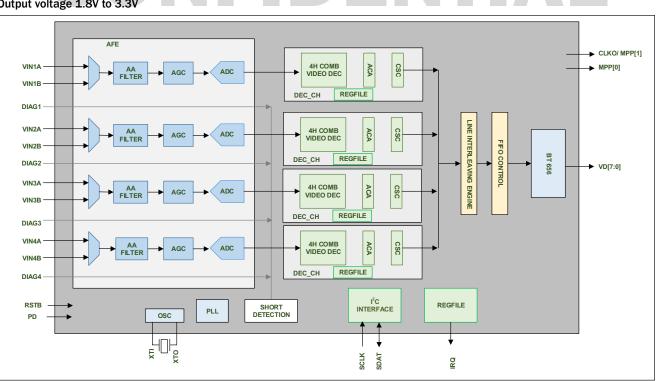

The ISL79987 and ISL79988 integrate four, high-quality NTSC/PAL/SECAM video decoders that convert analog composite video signals to digital component YCbCr data for automotive applications. Each channel contains a 10-bit ADC that supports single-ended, differential, and pseudo differential composite video inputs. The ISL79987 and ISL79988 use a 4H-comb filter for separating luminance and chrominance to reduce cross noise artifacts, and proprietary clamp and gain controllers. Integrated short-to-battery and short-to-ground detection, advanced image enhancement capabilities such as the programmable Automatic Contrast Adjustment (ACA), and the MIPI-CSI2/ITU-R BT.656 output interface make the ISL79987 and ISL79988 an ideal solution for the demands of automotive around view applications.

## **Applications**

Automotive around view

## **Related Literature**

- For a full list of related documents, visit our website:

- ISL79987, ISL79988 device pages

## **Features**

#### **Analog Video Decoder**

- Software-selectable analog input control allows for combinations of single-ended CVBS and differential CVBS

- Integrated, four-video analog anti-aliasing filters and 10-bit CMOS ADCs with differential and single-ended inputs

- Fully programmable static gain or automatic gain control for the Y-channel

- Programmable white peak control for the Y-channel

- 4-H adaptive comb filter Y/C separation

- · PAL delay line for color phase error correction

- · Digital subcarrier PLL for accurate color decoding

- Digital horizontal PLL for synchronization processing and pixel sampling

- Advanced synchronization processing and sync detection for handling non-standard and weak signals

- Automatic color control and color killer

- Chroma IF compensation

- Programmable output cropping

FIGURE 1. ISL79987 BLOCK DIAGRAM

#### **Features (continued)**

#### **Video Processing**

- · Automatic Contrast Adjustment (ACA)

- · Programmable hue, brightness, saturation, contrast, and sharpness

- · Image enhancement with peaking and CTI

#### **MIPI Output**

- MIPI CSI-2 version 1.1 compliant unidirectional output

- · Standard virtual identification channel support

- · Non-standard pseudo virtual channel support

- · One or two data lanes

- YUV422 or RGB565 output format

#### **Digital Output**

- · Supports standard ITU-R BT.656 format or time multiplexed output with 27/54/108MHz

- Output voltage 1.8V to 3.3V

#### **Miscellaneous**

- · Low power consumption

- · Power save and power-down mode

- · Short-to-battery detection

- · Short-to-ground detection

- · Two wire MPU serial bus interface

- · Supports real time control interface

- · Single 27MHz crystal for all operations

- 1.2V/3.3V power supply

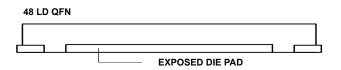

- 48 Ld QFN package

- ISL79987ARZ and ISL79988ARZ are AEC-0100 qualified

FIGURE 2. ISL79988 BLOCK DIAGRAM

## **Table of Contents**

| Ordering Information                                                                            |

|-------------------------------------------------------------------------------------------------|

| Pin Configurations                                                                              |

| Pin Descriptions (ISL79987 - MIPI)                                                              |

| Pin Descriptions (ISL79988 - ITU-R BT.656)                                                      |

| Absolute Maximum Ratings                                                                        |

| Thermal Information                                                                             |

| Recommended Operating Conditions                                                                |

| Electrical Specifications                                                                       |

| Serial Host Interface Timing                                                                    |

| ISL79987 MIPI Low Power AC Timing                                                               |

| ISL79987 MIPI High Speed AC Timing                                                              |

| ISL79988 Video Data/Sync Timing                                                                 |

| Functional Description                                                                          |

| Video Input Formats                                                                             |

| Analog Front-End                                                                                |

| Decimation Filter       16         Automatic Gain Control and Clamping       16                 |

| Automatic Gain Control and Clamping       16         Sync Processing       16                   |

| Y/C Separation                                                                                  |

| Color Decoding                                                                                  |

| Chrominance Processing                                                                          |

| Luminance Processing                                                                            |

| Short Diagnostics                                                                               |

| Video Cropping       18         Test Pattern Generator       18                                 |

| ISL79988 - BT.656 Line-Interleaved Output                                                       |

| BT.656 Preamble Format                                                                          |

| BT.656 Interleaved Data Transmission with Channel ID 19                                         |

| BT.656 Optional Header                                                                          |

| Programmable D-PHY Timing       23         Optional Histogram as Additional Pixel Data       24 |

| PCB Layout Considerations                                                                       |

| -                                                                                               |

| Thermal PAD Considerations   25                                                                 |

| Thermal Pad Land Design Input                                                                   |

| Thermal Via Design    25      Stencil Recommendation    25                                      |

| ISL79987, ISL7998788 Register Summary                                                           |

| ISL79987 and ISL79988 Register Detail                                                           |

| Common Registers - Page 0                                                                       |

| Decoder Registers - Page 1, 2, 3, and 4 for Four Decoders                                       |

| ACA Registers – Page 1, 2, 3 and 4                                                              |

| Line Interleave Engine Registers – Page 5 61                                                    |

| Revision History                                                                                |

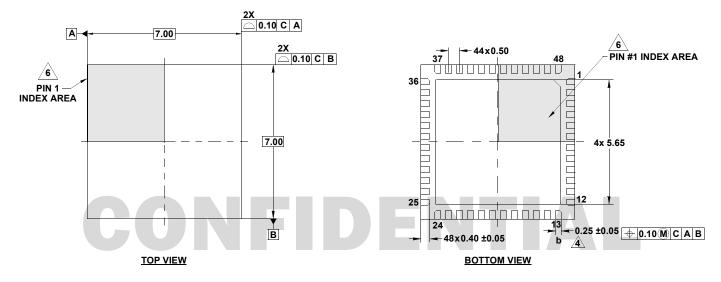

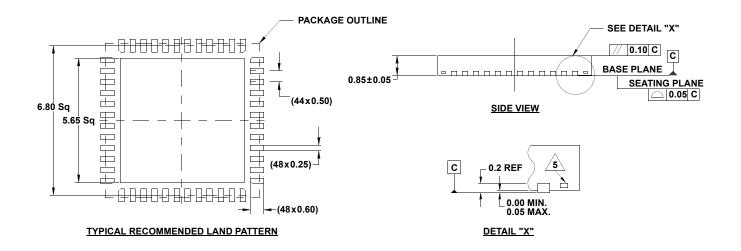

| Package Outline Drawing                                                                         |

## **Ordering Information**

| PART NUMBER<br>( <u>Notes 2</u> , <u>3</u> ) | PART MARKING     | TEMP RANGE (°C) | TAPE AND REEL<br>(Units) ( <u>Note 1</u> ) | PACKAGE<br>(RoHS COMPLIANT) | PKG.<br>DWG. # |

|----------------------------------------------|------------------|-----------------|--------------------------------------------|-----------------------------|----------------|

| ISL79987ARZ                                  | ISL79987 ARZ     | -40 to +105     | -                                          | 48 Ld QFN (7mmx7mm)         | L48.7x7W       |

| ISL79987ARZ-T                                | ISL79987 ARZ     | -40 to +105     | Зk                                         | 48 Ld QFN (7mmx7mm)         | L48.7x7W       |

| ISL79987IRZ                                  | ISL79987 IRZ     | -40 to +85      | -                                          | 48 Ld QFN (7mmx7mm)         | L48.7x7W       |

| ISL79987IRZ-T                                | ISL79987 IRZ     | -40 to +85      | Зk                                         | 48 Ld QFN (7mmx7mm)         | L48.7x7W       |

| ISL79988ARZ                                  | ISL79988 ARZ     | -40 to +105     | -                                          | 48 Ld QFN (7mmx7mm)         | L48.7x7W       |

| ISL79988ARZ-T                                | ISL79988 ARZ     | -40 to +105     | Зk                                         | 48 Ld QFN (7mmx7mm)         | L48.7x7W       |

| ISL79988IRZ                                  | ISL79988 IRZ     | -40 to +85      | -                                          | 48 Ld QFN (7mmx7mm)         | L48.7x7W       |

| ISL79988IRZ-T                                | ISL79988 IRZ     | -40 to +85      | Зk                                         | 48 Ld QFN (7mmx7mm)         | L48.7x7W       |

| ISL79987-EVAL                                | Evaluation Board | 1               |                                            |                             |                |

| ISL79988-EVAL                                | Evaluation Board |                 |                                            |                             |                |

1. See TB347 for details about reel specifications.

2. These Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), see the ISL79987 and ISL79988 device pages. For more information about MSL, see TB363.

#### TABLE 1. KEY DIFFERENCES BETWEEN FAMILY OF PARTS

|                           | PART          | PART FAMILY ALTERNATIVES |               |               |               |  |

|---------------------------|---------------|--------------------------|---------------|---------------|---------------|--|

| PARAMETERS                | ISL79987      | ISL79988                 | TW9984        | TW9966        | TW9992        |  |

| Number of Inputs          | 8             | 8                        | 8             | 8             | 8             |  |

| Number of Channels/Device | 4             | 4                        | 4             | 4             | 1             |  |

| Resolution                | D1            | D1                       | D1            | D1            | D1            |  |

| Video DAC                 | No            | No                       | Yes           | Yes           | No            |  |

| Comb Filter               | 2D            | 2D                       | 2D            | 2D            | 2D            |  |

| Interface Type            | MIPI1.1       | BT.656                   | BT.656        | BT.656, BT601 | MIPI1.1       |  |

| Analog Output             | No            | No                       | CVBS          | CVBS          | No            |  |

| Qualification Level       | Automotive    | Automotive               | Automotive    | Automotive    | Automotive    |  |

| Function                  | Video Decoder | Video Decoder            | Video Decoder | Video Decoder | Video Decoder |  |

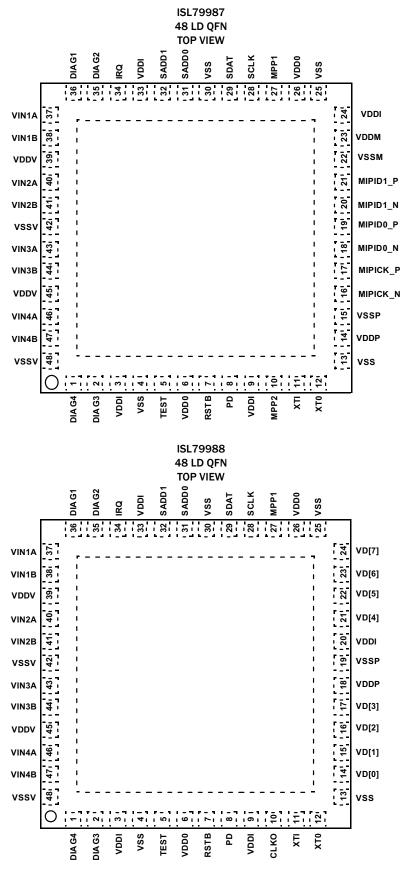

## **Pin Configurations**

FN8907 Rev.1.00 Mar 19, 2019

RENESAS

## Pin Descriptions (ISL79987 - MIPI)

| PIN#         | I/O         | PIN<br>NAME | DESCRIPTION                                                                                                                                              |

|--------------|-------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANALOG VIDI  | EO SIGNAL   |             |                                                                                                                                                          |

| 37           | I           | VIN1A       | Single-ended analog CVBS Input 1A/Differential CVBS positive Input 1                                                                                     |

| 38           | I           | VIN1B       | Single-ended analog CVBS Input 1B/Differential CVBS negative Input 1                                                                                     |

| 40           | I           | VIN2A       | Single-ended analog CVBS Input 2A/Differential CVBS positive Input 2                                                                                     |

| 41           | I           | VIN2B       | Single-ended analog CVBS Input 2B/Differential CVBS negative Input 2                                                                                     |

| 43           | I           | VIN3A       | Single-ended analog CVBS Input 3A/Differential CVBS positive Input 3                                                                                     |

| 44           | I           | VIN3B       | Single-ended analog CVBS Input 3B/Differential CVBS negative Input 3                                                                                     |

| 46           | I           | VIN4A       | Single-ended analog CVBS Input 4A/Differential CVBS positive Input 4                                                                                     |

| 47           | I           | VIN4B       | Single-ended analog CVBS Input 4B/Differential CVBS negative Input 4                                                                                     |

| 36           |             | DIAG1       | Short detection Input 1                                                                                                                                  |

| 35           |             | DIAG2       | Short detection Input 2                                                                                                                                  |

| 2            |             | DIAG3       | Short detection Input 3                                                                                                                                  |

| 1            |             | DIAG4       | Short detection Input 4                                                                                                                                  |

| MIPI SIGNAL  | s           |             |                                                                                                                                                          |

| 17           | 0           | MIPICK_P    | MIPI clock channel                                                                                                                                       |

| 16           | 0           | MIPICK_N    |                                                                                                                                                          |

| 19           | 0           | MIPID0_P    | MIPI data Channel 0                                                                                                                                      |

| 18           | 0           | MIPID0_N    |                                                                                                                                                          |

| 21           | 0           | MIPID1_P    | MIPI data Channel 1                                                                                                                                      |

| 20           | 0           | MIPID1_N    |                                                                                                                                                          |

| CRYSTAL CLO  | OCK SIGNALS |             |                                                                                                                                                          |

| 12           | 0           | XTO         | Crystal clock output. Open when a single-ended oscillator is connected to XTI.                                                                           |

| 11           | I           | ХТІ         | Crystal clock input. A 27MHz fundamental (or third overtone) crystal or a single-ended oscillator can be connected.                                      |

| GENERAL SIG  | GNALS       | •           |                                                                                                                                                          |

| 34           | 0           | IRQ         | Interrupt request output signal                                                                                                                          |

| 27           | I/0         | MPP1        | Multi-purpose IO 1                                                                                                                                       |

| 10           | I/0         | MPP2        | Multi-purpose IO 2                                                                                                                                       |

| 8            | I           | PD          | Power-down control pin. (1: Power-down 0: Normal operation).<br>When active, the XTI stops oscillation and all inputs to the analog module are inactive. |

| 7            | I           | RSTB        | Reset input. Low active.                                                                                                                                 |

| 5            | I           | TEST        | Test pin. Connect to ground.                                                                                                                             |

| SERIAL IO IN | TERFACE     |             | ·                                                                                                                                                        |

| 28           | I           | SCLK        | MPU serial interface clock line                                                                                                                          |

| 29           | I/0         | SDAT        | MPU serial interface data line                                                                                                                           |

| 31           | I           | SADD0       | Serial IO bus address selection LSB                                                                                                                      |

| 32           | I           | SADD1       | Serial IO bus address selection LSB+1                                                                                                                    |

## Pin Descriptions (ISL79987 - MIPI) (Continued)

| PIN#          | I/O         | PIN<br>NAME | DESCRIPTION                                |

|---------------|-------------|-------------|--------------------------------------------|

| POWER AND     | GROUND PINS | 5           |                                            |

| 3, 9, 24, 33  | PWR         | VDDI        | 1.2V digital core power                    |

| 4, 13, 25, 30 | GND         | VSS         | Ground return for digital core and IO ring |

| 6, 26         | PWR         | VDDO        | 3.3 or 1.8V digital I/O power              |

| 39, 45        | PWR         | VDDV        | 3.3V analog power for video ADC            |

| 42, 48        | GND         | VSSV        | Ground return for video ADC                |

| 23            | PWR         | VDDM        | 1.2V analog power for MIPI                 |

| 22            | GND         | VSSM        | Ground return for MIPI                     |

| 14            | PWR         | VDDP        | 1.2V analog power for PLL and BG           |

| 15            | GND         | VSSP        | Ground for PLL and BG                      |

NOTE: Connect unused input pin to AGND through 0.1µF capacitor.

# Pin Descriptions (ISL79988 - ITU-R BT.656)

| PIN#        | I/0 | PINNAME | DESCRIPTION                                                          |

|-------------|-----|---------|----------------------------------------------------------------------|

| 37          | I   | VIN1A   | Single-ended analog CVBS Input 1A/differential CVBS positive Input 1 |

| 38          | I   | VIN1B   | Single-ended analog CVBS Input 1B/differential CVBS negative Input 1 |

| 40          | I   | VIN2A   | Single-ended analog CVBS Input 2A/differential CVBS positive Input 2 |

| 41          | I   | VIN2B   | Single-ended analog CVBS Input 2B/differential CVBS negative Input 2 |

| 43          | I   | VIN3A   | Single-ended analog CVBS Input 3A/differential CVBS positive Input 3 |

| 44          | I   | VIN3B   | Single-ended analog CVBS Input 3B/differential CVBS negative Input 3 |

| 46          | I   | VIN4A   | Single-ended analog CVBS Input 4A/differential CVBS positive Input 4 |

| 47          | I   | VIN4B   | Single-ended analog CVBS Input 4B/differential CVBS negative Input 4 |

| 36          | I   | DIAG1   | Short detection Input 1                                              |

| 35          | I   | DIAG2   | Short detection Input 2                                              |

| 2           | I   | DIAG3   | Short detection Input 3                                              |

| 1           | I   | DIAG4   | Short detection Input 4                                              |

| BT.656 SIGN | ALS | ·       |                                                                      |

| 10          | 0   | CLKO    | BT.656 clock output                                                  |

| 24          | 0   | VD[7]   | BT.656 data Bit 7                                                    |

| 23          | 0   | VD[6]   | BT.656 data Bit 6                                                    |

| 22          | 0   | VD[5]   | BT.656 data Bit 5                                                    |

| 21          | 0   | VD[4]   | BT.656 data Bit 4                                                    |

| 17          | 0   | VD[3]   | BT.656 data Bit 3                                                    |

| 16          | 0   | VD[2]   | BT.656 data Bit 2                                                    |

| 15          | 0   | VD[1]   | BT.656 data Bit 1                                                    |

| 14          | 0   | VD[0]   | BT.656 data Bit 0                                                    |

## Pin Descriptions (ISL79988 - ITU-R BT.656)(Continued)

| PIN#          | I/O         | PINNAME | DESCRIPTION                                                                                                                                          |

|---------------|-------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| CRYSTAL CLO   | CK SIGNALS  |         |                                                                                                                                                      |

| 12            | 0           | XT0     | Crystal clock output. Open when a single-ended oscillator is connected to XTI.                                                                       |

| 11            | I           | ХТІ     | Crystal clock input. A 27MHz fundamental (or third overtone) crystal or a single-ended oscillator can be connected.                                  |

| GENERAL SIG   | NALS        |         |                                                                                                                                                      |

| 34            | 0           | IRQ     | Interrupt request output signal                                                                                                                      |

| 27            | I/0         | MPP1    | Multi-purpose IO 1                                                                                                                                   |

| 8             | I           | PD      | Power-down control pin. (1: Power-down 0: Normal operation).<br>When active, the XTI stops oscillation and all inputs to analog module are inactive. |

| 7             | I           | RSTB    | Reset input. Low active.                                                                                                                             |

| 5             | I           | TEST    | Test pin. Connect to ground.                                                                                                                         |

| SERIAL IO INT | TERFACE     |         |                                                                                                                                                      |

| 28            |             | SCLK    | MPU serial interface clock line                                                                                                                      |

| 29            | I/0         | SDAT    | MPU serial interface data line                                                                                                                       |

| 31            | I           | SADD0   | Serial IO bus address selection LSB                                                                                                                  |

| 32            | I           | SADD1   | Serial IO Bus address selection LSB+1                                                                                                                |

| POWER AND     | GROUND PINS | 5       |                                                                                                                                                      |

| 3, 9, 20, 33  | PWR         | VDDI    | 1.2V digital core power                                                                                                                              |

| 4, 13, 25, 30 | GND         | VSS     | Ground return for digital core and IO ring                                                                                                           |

| 6, 26         | PWR         | VDDO    | 3.3 or 1.8V digital I/O power                                                                                                                        |

| 39, 45        | PWR         | VDDV    | 3.3V analog power for video ADC                                                                                                                      |

| 42, 48        | GND         | VSSV    | Ground return for video ADC                                                                                                                          |

| 18            | PWR         | VDDP    | 1.2V analog power for PLL and BG                                                                                                                     |

| 19            | GND         | VSSP    | Ground for PLL and BG                                                                                                                                |

NOTE: Connect unused input pins to AGND through  $0.1\mu\text{F}$  capacitor.

#### **Absolute Maximum Ratings**

| VDDI to VSS                                                   |

|---------------------------------------------------------------|

| VDDV to VSSV                                                  |

| VDDP to VSSP                                                  |

| VDDM to VSSM                                                  |

| Any Digital Pin to VSS                                        |

| AFE Analog Pin to VSSV0.5V to +2.3V                           |

| MIPI Analog Pin to VSSM                                       |

| ESD Ratings                                                   |

| Human Body Model (Tested per AEC-Q100-002) 2kV                |

| Machine Model (Tested per AEC-A100-003)                       |

| Charged Device Model (Tested per AEC-Q100-011)                |

| Latch-Up (Per JESD-78D; Class 2, Level A; AEC-Q100-004) 100mA |

#### **Thermal Information**

| Thermal Resistance (Typical)                | θ <b>JA</b> (°C/W) | θ <b>JC</b> (°C∕W) |

|---------------------------------------------|--------------------|--------------------|

| 48 Ld 7x7 QFN ( <u>Notes 4</u> , <u>5</u> ) | 24                 | 1                  |

| Junction Temperature Range                  | 65                 | 5°C to +150°C      |

| Storage Temperature Range                   | 65                 | 5°C to +150°C      |

| Pb-Free Reflow Profile                      |                    | see <u>TB493</u>   |

#### **Recommended Operating Conditions**

| VDDI                                      | +1.1V to +1.3V  |

|-------------------------------------------|-----------------|

| VDD0                                      | +1.62V to +3.6V |

| VDDV                                      | +2.97V to +3.6V |

| VDDP, VDDM                                | +1.1V to +1.3V  |

| Ambient Temperature Range (ISL79987/8IRZ) | 40°C to +85°C   |

| Ambient Temperature Range (ISL79987/8ARZ) | 40°C to +105°C  |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

NOTES:

4. θ<sub>JA</sub> is measured in free air with the component mounted on a high-effective thermal conductivity test board with "direct attach" features. See <u>TB379</u>.

5. For θ<sub>JC</sub>, the "case temp" location is the center of the exposed metal pad on the package underside.

**Electrical Specifications** VDDI = VDDM = VDDP = 1.2V, VDD33 = VDDO = VDDV = 3.3V, unless otherwise noted, typical values are at

T<sub>A</sub> = +25°C.

| PARAMETER                                                         | SYMBOL           | MIN<br>( <u>Note 6</u> ) | ТҮР | MAX<br>( <u>Note 6</u> ) | UNIT |

|-------------------------------------------------------------------|------------------|--------------------------|-----|--------------------------|------|

| DIGITAL INPUTS                                                    |                  |                          |     |                          |      |

| Input High Voltage (at VDDO = 3.3V)                               | V <sub>IH</sub>  | 2.0                      |     | 3.6                      | v    |

| Input Low Voltage (at VDDO = 3.3V)                                | VIL              | -0.3                     |     | 0.8                      | v    |

| Input High Voltage (at VDDO = 1.8V)                               | V <sub>IH</sub>  | 1.17                     |     | 1.98                     | v    |

| Input Low Voltage (at VDDO = 1.8V)                                | V <sub>IL</sub>  | -0.3                     |     | 0.63                     | v    |

| Input Leakage Current (at V <sub>I</sub> = 3.3V or OV)            | ١L               |                          |     | ±10                      | μA   |

| Input Capacitance                                                 | C <sub>IN</sub>  |                          | 6   |                          | pF   |

| DIGITAL OUTPUTS                                                   | I                |                          | ·   | · · ·                    |      |

| Output High Voltage (at VDDO = 3.3V)                              | V <sub>OH</sub>  | 2.4                      |     |                          | v    |

| Output Low Voltage (at VDDO = 3.3V)                               | V <sub>OL</sub>  |                          |     | 0.4                      | v    |

| Output High Voltage (at VDDO = 1.8V)                              | V <sub>OH</sub>  | 1.35                     |     |                          | v    |

| Output Low Voltage (VDDO = 1.8V)                                  | V <sub>OL</sub>  |                          |     | 0.45                     | v    |

| High Level Output Current (at VDDO = 1.8V)                        | I <sub>ОН</sub>  | 2.4                      |     |                          | mA   |

| Low Level Output Current (at VDDO = 1.8V)                         | I <sub>OL</sub>  | 3.5                      |     |                          | mA   |

| Tri-State Output Leakage Current (at V <sub>0</sub> = 3.3V or 0V) | I <sub>OZ</sub>  |                          |     | ±10                      | μA   |

| Output Capacitance                                                | c <sub>o</sub>   |                          | 6   |                          | pF   |

| Analog Pin Input Capacitance                                      | C <sub>A</sub>   |                          | 6   |                          | pF   |

| ANALOG INPUT                                                      |                  |                          |     | <u> </u>                 |      |

| VIN1~4 Input Range (AC coupling)                                  | V <sub>P-P</sub> | 0.5                      | 1.0 | 2.0                      | v    |

| Analog Pin Input Capacitance                                      | C <sub>A</sub>   |                          | 6   |                          | pF   |

### **Electrical Specifications** VDDI = VDDM = VDDP = 1.2V, VDD33 = VDDO = VDDV = 3.3V, unless otherwise noted, typical values are at

T<sub>A</sub> = +25°C. (Continued)

| PARAMETER                                                                                                                                         | SYMBOL                  | MIN<br>( <u>Note 6</u> )         | ТҮР     | MAX<br>( <u>Note 6</u> ) | UNIT               |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------------|---------|--------------------------|--------------------|

| SUPPLY CURRENT                                                                                                                                    | L                       | L                                |         |                          | 1                  |

| Analog Video ADC Supply Current (VDDV, 3.3V)                                                                                                      | I <sub>DDV</sub>        |                                  | 46.8    |                          | mA                 |

| MIPI Supply Current (VDDM, 1.2V)                                                                                                                  | I <sub>DDM</sub>        |                                  | 12.3    |                          | mA                 |

| Clock PLL Supply Current (VDDP, 1.2V)                                                                                                             | IDDP                    |                                  | 5.1     |                          | mA                 |

| Digital Internal Supply Current (VDDI, 1.2V)                                                                                                      | I <sub>DDI</sub>        |                                  | 65.5    |                          | mA                 |

| Digital I/O Supply Current (VDDO, 3.3/1.8V)                                                                                                       | I <sub>DDO</sub>        |                                  | 1.2/4.3 |                          | mA                 |

| Total Power Dissipation (VDD0 = 1.8/3.3V)                                                                                                         | Р                       |                                  | 258/270 |                          | mW                 |

| MIPI OUTPUT LOW POWER                                                                                                                             |                         |                                  |         |                          |                    |

| Output High Voltage                                                                                                                               | V <sub>OH_LP</sub>      | 1.1                              | 1.2     | 1.3                      | v                  |

| Output Low Voltage                                                                                                                                | V <sub>OL_LP</sub>      | -50                              |         | 50                       | mV                 |

| Output Impedance                                                                                                                                  | ZO_LP                   | 110                              |         |                          | Ω                  |

| Slew Rate at C <sub>LOAD</sub> = 0 to 70pF (Rising Edge Only)                                                                                     | δV/δtSR                 | 30                               |         |                          | mV/ns              |

| Slew Rate at C <sub>LOAD</sub> = 0 to 70pF (Rising Edge Only) for V400mV < V0<br><700mV                                                           | δV/δtSR                 | 30                               |         |                          | mV/ns              |

| Slew Rate at C <sub>LOAD</sub> = 0 to 70pF (Rising Edge Only) for VO > 700mV<br>(VO, INST is the Instantaneous Output Voltage, VDP or VDN, in mV) | δV∕δtSR                 | 30 - 0.075 *<br>(V0, INST - 700) |         |                          | mV/ns              |

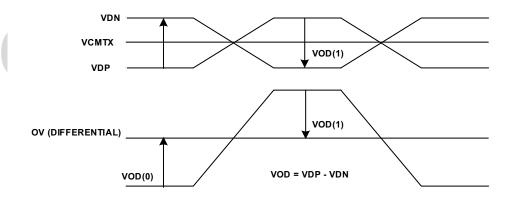

| MIPI OUTPUT HIGH SPEED                                                                                                                            | L                       | L                                |         |                          | I                  |

| Static Common-Mode Voltage                                                                                                                        | V <sub>CMTX</sub>       | 150                              | 200     | 250                      | mV                 |

| $V_{\mbox{CMTX}}$ Mismatch between $V_{\mbox{OD}(0)}$ and $V_{\mbox{OD}}$                                                                         | DV <sub>CMTX(1,0)</sub> |                                  |         | 5                        | mV                 |

| V <sub>CMTX</sub> Common Level Variation                                                                                                          | DV <sub>CMTX(LF)</sub>  |                                  |         | 25                       | mV <sub>PEAK</sub> |

| Differential Voltage                                                                                                                              | V <sub>OD</sub>         | 140                              | 200     | 270                      | mV/ns              |

| $V_{OD}$ Mismatch Between $V_{OD(0)}$ and $V_{OD}$                                                                                                | DV <sub>OD</sub>        |                                  |         | 14                       | mV/ns              |

| Output High Voltage                                                                                                                               | V <sub>OHHS</sub>       |                                  |         | 360                      | mV/ns              |

| Single-Ended Output Impedance                                                                                                                     | Z <sub>OS</sub>         | 40                               | 50      | 62.5                     | Ω                  |

| Z <sub>OS</sub> Mismatch                                                                                                                          | DZ <sub>OS</sub>        |                                  |         | 10                       | %                  |

NOTE:

6. Compliance to datasheet limits is assured by one or more methods: production test, characterization, and/or design.

#### TABLE 2. CRYSTAL REQUIREMENT SPECIFICATION

| PARAMETER                       | SYMBOL         | ТҮР | MAX | UNIT |

|---------------------------------|----------------|-----|-----|------|

| Nominal Frequency (Fundamental) |                | 27  |     | MHz  |

| Deviation                       |                |     | ±50 | ppm  |

| Load Capacitance                | CL             | 20  |     | pF   |

| Series Resistor                 | R <sub>S</sub> | 80  |     | Ω    |

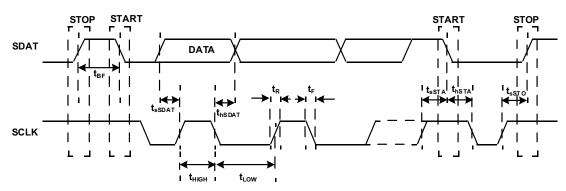

## **Serial Host Interface Timing**

| TEST PARAMETER                       | SYMBOL             | MIN<br>( <u>Note 7</u> ) | MAX<br>( <u>Note 7</u> ) | UNIT |

|--------------------------------------|--------------------|--------------------------|--------------------------|------|

| Bus Free Time between STOP and START | t <sub>BF</sub>    | 500                      |                          | ns   |

| SDAT Set-Up Time                     | t <sub>sSDAT</sub> | 50                       |                          | ns   |

| SDAT Hold Time                       | t <sub>hSDAT</sub> | 0                        |                          | ns   |

| Set-Up Time for START Condition      | t <sub>sSTA</sub>  | 260                      |                          | ns   |

| Set-Up Time for STOP Condition       | t <sub>sSTOP</sub> | 260                      |                          | ns   |

| Hold Time for START Condition        | t <sub>hSTA</sub>  | 260                      |                          | ns   |

| Rise Time for SCLK and SDAT          | t <sub>R_SB</sub>  |                          | 120                      | ns   |

| Fall Time for SCLK and SDAT          | t <sub>F_SB</sub>  |                          | 120                      | ns   |

| SCLK Low Time                        | tLoW               | 260                      |                          | ns   |

| SCLK High Time                       | tHIGH              | 500                      |                          | ns   |

| Capacitive Load for Each Bus Line    | C <sub>BUS</sub>   |                          | 550                      | pF   |

| SCLK Clock Frequency                 | fsclk              |                          | 1000                     | kHz  |

#### NOTE:

7. Compliance to datasheet limits is assured by one or more methods: production test, characterization, and/or design.

FIGURE 3. SERIAL HOST INTERFACE TIMING DIAGRAM

## **ISL79987 MIPI Low Power AC Timing**

| TEST PARAMETER                                                                                          | SYMBOL                             | MIN<br>( <u>Note 7</u> ) | ТҮР | MAX<br>( <u>Note 7</u> ) | UNIT | NOTES                                                |

|---------------------------------------------------------------------------------------------------------|------------------------------------|--------------------------|-----|--------------------------|------|------------------------------------------------------|

| Rise/Fall Time 15% to 85% of $V_{\mbox{OH}}$ to $V_{\mbox{OL}}$                                         | t <sub>RLP</sub> /t <sub>FLP</sub> |                          |     | 25                       | ns   | C <sub>LOAD</sub> ≤70pF                              |

| Rise/Fall Time 30% to 85% from HS Differential<br>Amplitude Drops Below 70mV to V <sub>DP</sub> = 880mV | T <sub>REOT</sub>                  |                          |     | 35                       | ns   | $C_{LOAD}$ ≤70pF with additional $C_{CM}$ up to 60pF |

| Pulse Width of LP XOR Clock                                                                             | t <sub>LP-PULSE-TX</sub>           | 40                       |     |                          | ns   | First/last pulse after/before Stop state             |

|                                                                                                         | t <sub>LP-PULSE-TX</sub>           | 20                       |     |                          | ns   | All other pulses                                     |

| Period of LP XOR Clock                                                                                  | t <sub>LP-PER-TX</sub>             | 90                       |     |                          | ns   |                                                      |

| Transmitted Length (duration) of Any Low Power<br>State                                                 | t <sub>LPX</sub>                   | 50                       |     |                          | ns   | This is an internal parameter                        |

FIGURE 4. ISL79987 MIPI LOW POWER AC TIMING

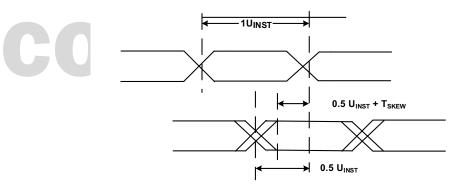

## **ISL79987 MIPI High Speed AC Timing**

| TEST PARAMETER                                           | SYMBOL                         | MIN   | ТҮР                       | MAX  | UNIT               | NOTES                                              |

|----------------------------------------------------------|--------------------------------|-------|---------------------------|------|--------------------|----------------------------------------------------|

| Unit Interval Instantaneous                              | UI <sub>INST</sub>             |       | 4.629/<br>2.314/<br>1.157 |      | ns                 |                                                    |

| UI Variation                                             | ΔUI                            | -10%  |                           | 10%  | UI                 | Variation within a single burst with UI $\geq$ 1ns |

| Clock Lane DDR Clock Frequency<br>( = 1/(2*UI INST MIN)) | fh <sub>MAX</sub>              |       | 108/<br>216/<br>432       |      | MHz                | f <sub>XTAL</sub> = 27MHz with 8b line coding      |

| Rise/Fall Time 20% to 80%                                | t <sub>R</sub> ∕t <sub>F</sub> |       |                           | 0.3  | UI                 | UI ≥ 1ns                                           |

|                                                          |                                | 150   |                           |      | ps                 |                                                    |

| Data to Clock Skew                                       | T <sub>SKEW</sub>              | -0.15 |                           | 0.15 | UI <sub>INST</sub> | UI ≥ 1ns                                           |

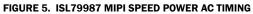

## ISL79988 Video Data/Sync Timing

| TEST PARAMETER                              | SYMBOL | MIN<br>( <u>Note 8</u> ) | ТҮР | MAX<br>( <u>Note 8</u> ) | UNIT |

|---------------------------------------------|--------|--------------------------|-----|--------------------------|------|

| Hold from CLKO to Video Data/Sync (27MHz)   | 2a     | 3                        |     |                          | ns   |

| Delay from CLKO to Video Data/Sync (27MHz)  | 2b     |                          |     | 7                        | ns   |

| Hold from CLKO to Video Data/Sync (54MHz)   | 4a     | 3                        |     |                          | ns   |

| Delay from CLKO to Video Data/Sync (54MHz)  | 4b     |                          |     | 7                        | ns   |

| Hold from CLKO to Video Data/Sync (108MHz)  | 6a     | 3                        |     |                          | ns   |

| Delay from CLKO to Video Data/Sync (108MHz) | 6b     |                          |     | 7                        | ns   |

#### NOTE:

8. CLKO timing is related to CLKO\_DEL register value. Figure 6 illustrates an example where the CLKO\_DEL is set to 0 hex and CLKO\_POL is set to 0.

FIGURE 6. ISL79988 VIDEO DATA/SYNC TIMING

## **Functional Description**

#### **Video Input Formats**

The ISL79987 and ISL79988 has built-in automatic standard discrimination circuitry. The circuit uses burst-phase, burst-frequency, and frame rate to identify NTSC, PAL, or SECAM color signals. The standards that can be identified are NTSC (M), NTSC (4.43), PAL (B, D, G, H, I), PAL (M), PAL (N), PAL (60), and

SECAM (M). Each standard can be included or excluded in the standard recognition process by software control. The exceptions are the base standard NTSC and PAL, which are always enabled. The identified standard is indicated by the Standard Selection (SDT) register. Automatic standard detection can be overridden by software controlled standard selection.

ISL79987 and ISL79988 support all common video formats shown in Table 3.

| TABLE 3. | 3. VIDEO INPUT FORMATS SUPPORTED BY THE ISL79987. IS | L79988 |

|----------|------------------------------------------------------|--------|

|          |                                                      |        |

| FORMAT                       | LINES | FIELDS | FSC (MHz)   | COUNTRY                                     |

|------------------------------|-------|--------|-------------|---------------------------------------------|

| NTSC-M                       | 525   | 60     | 3.579545    | U.S., many others                           |

| NTSC-Japan ( <u>Note 9</u> ) | 525   | 60     | 3.579545    | Japan                                       |

| PAL-B, G, N                  | 625   | 50     | 4.433619    | Many                                        |

| PAL-D                        | 625   | 50     | 4.433619    | China                                       |

| PAL-H                        | 625   | 50     | 4.433619    | Belgium                                     |

| PAL-I                        | 625   | 50     | 4.433619    | Great Britain, others                       |

| PAL-M                        | 525   | 60     | 3.575612    | Brazil                                      |

| PAL-CN                       | 625   | 50     | 3.582056    | Argentina                                   |

| SECAM                        | 625   | 50     | 4.406, 4.25 | France, Eastern Europe, Middle East, Russia |

| PAL-60                       | 525   | 60     | 4.433619    | China                                       |

| NTSC (4.43)                  | 525   | 60     | 4.433619    | Transcoding                                 |

NOTE:

9. NTSC-Japan has 0 IRE setup.

#### Analog Front-End

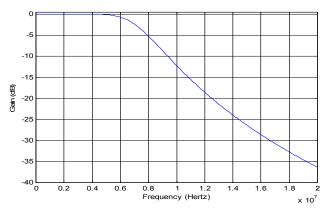

The ISL79987 and ISL79988 contain four 10-bit Analog to Digital Converters (ADCs) to digitize the analog video inputs. The ADCs can be put into power-down mode by the ADC\_PD register (0x36[6] at Pages 1, 2, 3, 4). The ISL79987 and ISL79988 also contain an anti-aliasing filter to prevent out-of-band frequencies in the analog video input signal. As a result, there is no need for external components in front of the analog input pins, except for the AC coupling capacitor and termination resistor.

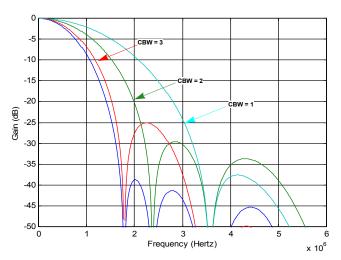

Figure 7 shows the frequency response of the anti-aliasing filter.

FIGURE 7. FREQUENCY RESPONSE OF THE ANTI-ALIASING FILTER

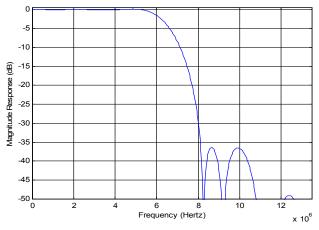

#### **Decimation Filter**

The digitized composite video data is over-sampled to simplify the design of the analog filter. The decimation filter is required to achieve optimum performance and prevent high-frequency components from being aliased back into the video image when down-sampled. Figure 8 shows the characteristic of the decimation filter.

FIGURE 8. FREQUENCY RESPONSE OF THE DECIMATION FILTER

#### **Automatic Gain Control and Clamping**

All four analog channels have a built-in clamping circuit that restores the signal's DC level. The video input restores the back porch of the digitized video to a level of 60. This operation is automatic through an internal feedback loop. The Automatic Gain Control (AGC) of the video input adjusts the input gain so that the sync tip is at a desired level. Programmable white peak protection logic is included to prevent saturation in the case of an abnormal signal proportion between the sync and white peak level.

#### Sync Processing

The ISL79987 and ISL79988 sync processor detects horizontal synchronization and vertical synchronization signals in the composite video signal. The processor contains a digital Phase-Locked Loop (PLL) and decision logic to achieve reliable sync detection in a stable signal and in an unstable signal such as those from a VCR fast forward or rewind.

The vertical sync separator detects the vertical synchronization pattern in the input video signals. In addition, the actual sync determination is controlled by a detection window to provide more reliable synchronization. An option is available to provide faster responses for certain applications. The field status is determined at the vertical synchronization time. The field logic can also be controlled to toggle automatically while tracking the input.

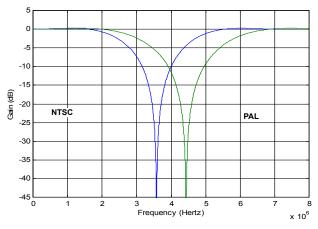

#### Y/C Separation

The color-decoding block contains the luma/chroma separation for a composite video signal and multi-standard color demodulation. For NTSC and PAL standard signals, the luma/chroma separation can be done either by comb filter or notch/band-pass filter combination. For SECAM standard signals, an adaptive notch/band-pass filter is used. The default selection for NTSC/PAL is a comb filter.

When using the comb filter, the ISL79987 and ISL79988 separate the luma (Y) and chroma (C) of a NTSC/PAL composite video signal using a proprietary 4H adaptive comb filter. The filter uses a four-line buffer. Adaptive logic combines the upper-comb and the lower-comb results based on the signal changes among the previous, current, and next lines. This technique leads to excellent Y/C separation with small cross luma and cross color at both the horizontal and vertical edges.

Due to the fact that a line buffer is used in the comb filter, there is always a two-line processing delay in the output.

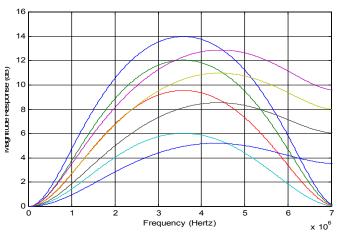

<u>Figures 9</u> and <u>10</u> shows the characteristics of the filters when notch/band-pass filter is selected.

FIGURE 9. CHARACTERISTICS OF LUMINANCE NOTCH FILTER FOR PAL

FIGURE 10. CHROMA BAND-PASS FILTER CURVES

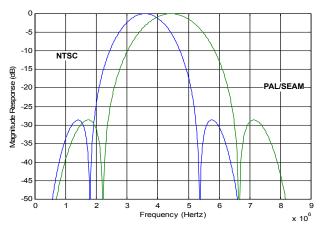

#### **Color Decoding**

#### **CHROMINANCE DEMODULATION**

The color demodulation for NTSC and PAL standards is done by first quadrature mixing the chroma signal to the base band. A low-pass filter is then used to remove the carrier signal and yield chroma components. The low-pass filter characteristic can be selected for optimized transient color performance. For the PAL system, the PAL ID or the burst phase switching is identified to aid in the PAL color demodulation.

For SECAM, the color information is FM modulated onto a different carrier. The demodulation process therefore consists of FM demodulator and de-emphasis filter. During the FM demodulation, the chroma carrier frequency is identified and used to control the SECAM color demodulation.

**Note:** The subcarrier signal for use in the color demodulator is generated by direct digital synthesis PLL that locks onto the input subcarrier reference (color burst). This arrangement allows any sub-standard of NTSC and PAL to be demodulated easily with single crystal frequency.

Figure 11 shows the frequency response of chrominance low-pass filter curves.

FIGURE 11. CHROMINANCE LOW-PASS FILTER CURVES

#### **AUTOMATIC CHROMA GAIN CONTROL (ACC)**

The Automatic Chroma Gain Control (ACC) compensates for reduced amplitudes caused by high-frequency loss in the video signal. In the NTSC/PAL standard, the color reference signal is the burst on the back porch. It is measured to control the chroma output gain. The range of ACC control is -6dB to +24dB.

#### **Chrominance Processing**

#### CHROMINANCE GAIN, OFFSET, AND HUE ADJUSTMENT

When decoding NTSC signals, the ISL79987 and ISL79988 can adjust the hue of the chroma signal. The hue is defined as a phase shift of the subcarrier with respect to the burst. This phase shift of NTSC decoding can be programmed through a control register. For the PAL standard, the PAL delay line is provided to compensate any hue error; therefore, no hue adjustment is available. The color saturation can be adjusted by changing the gain of the Cb and Cr signals for all NTSC, PAL, and SECAM formats. The Cb and Cr gain can be adjusted independently for flexibility.

#### **COLOR TRANSIENT IMPROVEMENT (CTI)**

The Color Transient Improvement (CTI) function to further enhances the image quality. The CTI enhances the color edge transient without any overshoot or undershoot.

#### **Luminance Processing**

The ISL79987 and ISL79988 adjust brightness by adding a programmable value (in register BRIGHTNESS) to the Y signal. It adjusts the picture contrast by changing the gain (in register CONTRAST) of the Y signal.

The ISL79987 and ISL79988 also provide programmable peaking function to further enhance the video sharpness. The peaking control has a built-in coring function to prevent enhancement of noise. Figure 12 on page 18 shows the characteristic of the peaking filter for four different gain modes and different center frequencies.

#### **Short Diagnostics**

#### SHORT-TO-BATTERY AND SHORT-TO-GROUND

The ISL79987 and ISL79988 provide a Short-to-Battery (STB) and Short-to-Ground (STG) detection capability. The short diagnostics module has four channels, one for each video input. Both STB and STG support 8-step programmable threshold levels (3 bits per threshold). The Short-to-Ground thresholds range from 1/152 to 8/152 of the 3.3V power supply. The Short-to-Battery thresholds range from 20/152, 26/152, 32/152, ..., 62/152 of the 3.3V power supply. STB and STG events can be detected by either polling registers or by using the interrupt pin.

#### **Video Cropping**

Cropping allows only a subsection of a video image to be output. The active video region is determined by the HDELAY, HACTIVE, VDELAY, and VACTIVE registers. The VACTIVE signal can be programmed to indicate the number of active lines to be displayed in a video field, and the HACTIVE signal can be programmed to indicate the number of active pixels to be displayed in a video line. The start of the field or frame in the vertical direction is indicated by the leading edge of VSYNC. The start of the line in the horizontal direction is indicated by the leading edge of the HSYNC. The start of the active lines from vertical sync edge is indicated by the VDELAY register. The start of the active pixels from the horizontal edge is indicated by the HDELAY register. The sizes and location of the active video are determined by HDELAY, HACTIVE, VDELAY, and VACTIVE registers. These registers are eight bits wide; the lower eight bits are, respectively, in HDELAY LO, HACTIVE LO, VDELAY LO, and VACTIVE\_LO. Their upper two bits share the same register CROP\_HI.

The Horizontal Delay register (HDELAY) determines the number of pixels delay between the leading edge of HSYNC and the leading edge of the HACTIVE. Note that this value is referenced to the unscaled pixel number. The Horizontal Active register (HACTIVE) determines the number of active pixels to be output or scaled after the delay from the sync edge is met. This value is also referenced to the unscaled pixel number. Therefore, if the scaling ratio is changed, the active video region used for scaling remains unchanged as set by the HACTIVE register, but the valid pixels output are equal or reduced due to downscaling. For the cropping to work properly, <u>Equation 1</u> should be satisfied.

HDELAY + HACTIVE < Total number of pixels per line (EQ. 1)

For NTSC output at 13.5MHz pixel rate, the total number of pixels is 858. For PAL output at 13.5MHz rate, the total number of pixels is 864. HACTIVE should be set to 720.

The Vertical Delay register (VDELAY) determines the number of lines delay between the leading edge of the VSYNC and the start of the active video lines. It indicates the number of lines to skip at the start of a frame before asserting the VACTIVE signal. This value is referenced to the incoming scan lines before the vertical scaling. The number of scan lines is 525 for the 60Hz systems and 625 for the 50Hz systems. The Vertical Active register (VACTIVE) determines the number of lines to be used in the vertical scaling. Therefore, the number of scan lines output is equal or less than the value set in this register depending on the vertical scaling ratio. For the vertical cropping to work properly, <u>Equation 2</u> should be observed.

VDELAY + VACTIVE < Total number of lines per field (EQ. 2)

#### **Test Pattern Generator**

For each input video channel, the chip provides a corresponding test pattern generator that can be used to replace the real input video for testing purposes. Each generator can be programmed to output NTSC or PAL format, and can generate fixed-sync or variable-sync timing to emulate real video source timings with a much wider variation range.

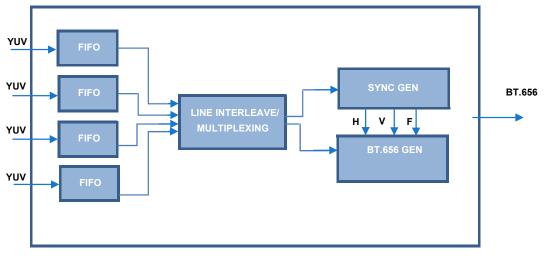

#### ISL79988 - BT.656 Line-Interleaved Output

The ISL79988 supports up to 4-channel CVBS inputs and merges multi-video streams into a single BT.656 output bus. If streaming two or more channels, a line-interleaved method is employed. The ISL79988 supports one single video stream format and two multi-video stream formats that are clocked at 27MHz, 54MHz, and 108MHz (see Table 4 for details). When outputting multi-video stream on the BT.656 bus, channel IDs are inserted in sync word. Each line starts with an EAV, followed by horizontal blank data, SAV, and active data. The channel ID is embedded into SAV/EAV's least-significant two bits and in horizontal blank data on the least-significant two bits.

| TABLE 4. |       |        | EODMAT |

|----------|-------|--------|--------|

| IADLE 4. | VIDEU | UUIPUI | FURMAI |

| VIDEO OUTPUT FORMAT | OUTPUT CLOCK FREQUENCY (MHz) |

|---------------------|------------------------------|

| 1-CH with 480i      | 27                           |

| 2-CH with 480i      | 54                           |

| 4-CH WITH 480i      | 108                          |

Figure 13 on page 19 illustrates that the four independent channels' video data are merged by the line-interleaved method to the BT.656 output.

FIGURE 13. ISL79988 - BT.656 LINE-INTERLEAVED OUTPUT

#### **BT.656 Preamble Format**

The receiver should detect the EAV and SAV by looking for the 8-bit FFh-00h-00h-XXh preamble sequence. The last status byte of the preamble sequence indicates channel ID, field, VSYNC, and HSYNC information.

| PREAMBLE       | D7 | D6 | D5 | D4 | D3 | D2 | D1          | DO          |

|----------------|----|----|----|----|----|----|-------------|-------------|

| STATUS<br>WORD | 1  | F  | v  | н  | 0  | 0  | CH<br>ID[1] | CH<br>ID[0] |

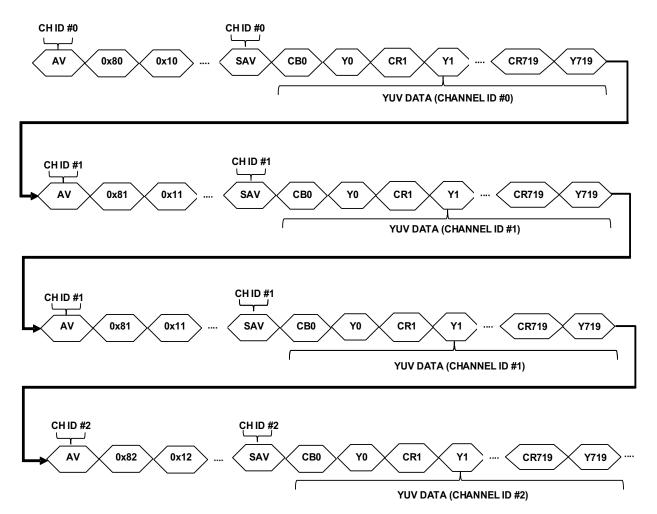

#### BT.656 Interleaved Data Transmission with Channel ID

The channel ID is updated in preamble EAV on each line and retains the channel ID information for the horizontal blank data and the preamble SAV. Every output line always starts with an EAV followed by Horizontal Blank, SAV, and active data on the same channel. However, the channel order may not be sequential due to the sync-variation between different channels, which means that it is possible to output two consecutive lines from the same channel before switching to another channel. Figure 14 on page 20 shows an example of an output sequence.

FIGURE 14. BT.656 INTERLEAVED DATA TRANSMISSION WITH CHANNEL ID

#### **BT.656 Optional Header**

In addition to the channel ID in EAV, Horizotnal blank, and SAV sequence, there is an optional 8-byte header insert followed by each SAV to provide additional information for that horizontal line. In this case, each horizontal line has 1448 bytes of active data instead of 1440 bytes. This special 8-byte header is defined to avoid conflict with the SAV and EAV byte sequence.

HD1 is sent out first and HD2 follows it. HD8 is the last byte that is sent out. Active video data follows HD8.

| BIT | BIT 7      | BIT 6       | BIT 5       | BIT 4       | BIT 3  | BIT 2       | BIT 1   | BIT O    |

|-----|------------|-------------|-------------|-------------|--------|-------------|---------|----------|

| HD1 | <b>'1'</b> | '0'         | <b>'1</b> ' | '0'         |        | Fra         | me[3:0] |          |

| HD2 | <b>'1'</b> | 'O'         | <b>'1'</b>  | <b>'</b> 0' | ʻ0'    | <b>'</b> 0' | ʻ0'     | Field    |

| HD3 | <b>'1'</b> | <b>'</b> 0' | <b>'1'</b>  | <b>'O'</b>  |        | Lin         | e[11:8] |          |

| HD4 | <b>'1'</b> | ʻ0'         | <b>'1'</b>  | <b>'</b> 0' |        | Lii         | ne[7:4] |          |

| HD5 | <b>'1'</b> | ʻ0'         | <b>'1'</b>  | '0'         |        | Lir         | ne[3:0] |          |

| HD6 | <b>'1'</b> | '0'         | <b>'1'</b>  | '0'         | ʻ0'    | ʻ0'         | Сні     | D[1:0]   |

| HD7 | <b>'1'</b> | '0'         | <b>'1</b> ' | '0'         | VDLOSS | HLOCK       | SLOCK   | VLOCK    |

| HD8 | <b>'1'</b> | ʻ0'         | <b>'1'</b>  | ʻ0'         | MONO   | DET50       | DETSTUS | V_STABLE |

- CHID Video channel ID, from 0 to 3

- · Line Line number

- Field Field indicator. 0 is first (top) field. 1 is second (bottom) field

- Frame Frame number

- VDLOSS Same as 0x103[7]

- HLOCK, SLOCK, VLOCK Same as 0x103[6], 0x103[5], 0x103[3]

- MONO Same as 0x103[1]

- DET50 Same as 0x103[0]

- DETSTUS Same as 0x11c[7]

- V\_STABLE Video data stable flag when video is detected and all syncs are in lock

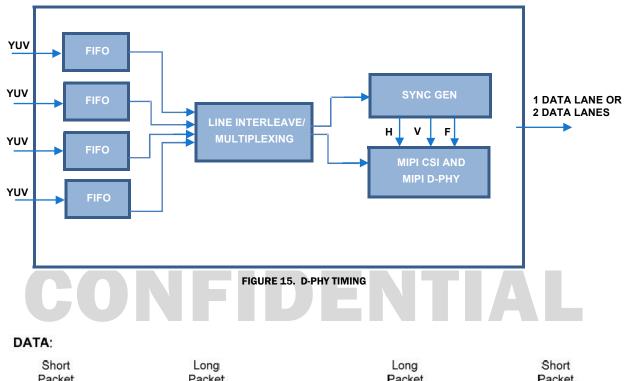

#### ISL79987 - MIPI OUTPUT

The MIPI transmitter consists of a protocol module that is compatible with the MIPI CSI-2 v1.1 interface standard, and a physical layer module that is compatible with the MIPI D-PHY V1.1 standard.

In the protocol module, up to four (one, two, or four) independent NTSC or PAL standard video channels are line-interleaved into a single data stream, which is then de-multiplexed into one or two data lanes following the CSI-2 specification. The digital data, along with the MIPI-specific clock and data digital control signals, are fed to the analog D-PHY module.

In the D-PHY module, the data, clock, and control signals are converted into MIPI-compatible, serialized data ready for output. Depending on the input and output configuration, the chip supports the following five major modes of operation. Different output clock frequencies are generated by an on-chip PLL module, which uses a unique 27MHz crystal input reference clock.

- 1-channel input with 1-data-lane mode: MIPI clock is 108MHz with 216Mbps data rate.

- 2-channel input with 1-data-lane mode: MIPI clock is 216MHz with 432Mbps data rate.

- 2-channel input with 2-data-lanes mode: MIPI clock is 108MHz with 216Mbps data rate.

- 4-channel input with 1-data-lane mode: MIPI clock is 432MHz with 864Mbps data rate.

- 4-channel input with 2-data-lanes mode: MIPI clock is 216MHz with 432Mbps data rate.

| VIDEO OUTPUT FORMAT | OUTPUT MIPI CLOCK FREQUENCY (MHz) |

|---------------------|-----------------------------------|

| 1-CH with 480i      | 108 (1 lane)                      |

| 2-CH with 480i      | 216 (1 Lane)                      |

| 2-CH with 480i      | 108 (2 Lanes)                     |

| 4-CH with 480i      | 432 (1 Lane)                      |

| 4-CH with 480i      | 216 (2 Lanes)                     |

Figure 15 on page 22 illustrates that the four independent channels' video data are merged by the line-interleaved method to the BT.656 output.

#### **Programmable D-PHY Timing**

The low-power and high-speed data timing, and the clock-to-data timing are programmable based on the input channel-number and data-lane selections.

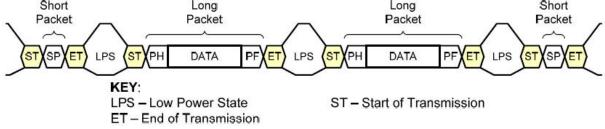

#### SHORT AND LONG PACKETS

The ISL79987 supports two types of short packets, Frame-Start (FS, 0x00) and Frame-End (FE, 0x01), which specify the start and end of a picture. There are also two types of long packets: YUV422 8-bit (0x1E) and YUV422 8-bit-user defined (0x30). The 0x30 data type is used to refer to the specific histogram-line data. Note that when the histogram-line option is selected, the 128-bin histogram data of an incoming picture is attached following the last line of the picture. Because the histogram-bin data is considerably different from the regular video format, it is sufficient to use a different data type "30" to designate it to the MIPI receiver. Figure 16 on page 22 shows an example of long and short packets.

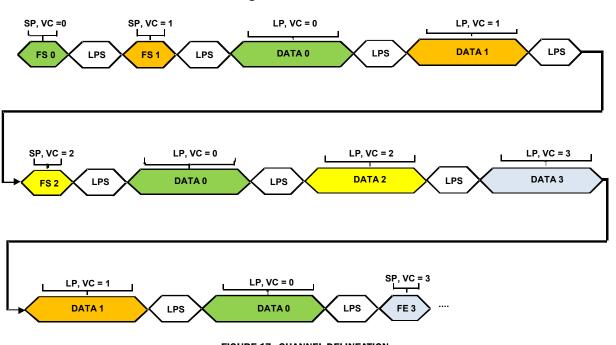

#### **CHANNEL DELINEATION**

Two options for merging mutli-channel video onto a single MIPI link are:

- CSI-2 Standard mode

- Pseudo Single-Frame mode

These modes are described in the following sections.

#### **CSI-2 Standard Mode**

A 2-bit, Virtual-Channel (VC) field is embedded in the long-packet header's Data-ID field and short-packet Data-ID field, Bits 7-6, to specify which channel the upcoming long and short packet belongs to. As defined in CSI-2 standard, each long packet should contain a complete horizontal line data. Each virtual channel has its own FS and FE packets. All the short and long packets from the four channels are interleaved into a single MIPI data stream following the original sync and data timing as close as possible. Therefore, the channel order may not be sequential due to sync-variation between different channels.

#### **Pseudo Single-Frame Mode**

In Pseudo Single-Frame mode, the MIPI receiver should treat the received 4-channel data as a pseudo one-channel data. In this case, only one Frame-Start (FS) and one Frame-End (FE) short packets are sent following either:

- · The first channel's vertical sync timing, or

- · A fixed line-accummulator's line-counter setting

The spacing between FE to the next FS is crucial for the receiver to finish its interrupt service routine and is limited to be no more than two lines due to the finite line-FIFO size constraint of the MIPI transmitter. Due to the asynchorous nature of multi-video input, the number of long packets (lines) between FS to FE can vary in the first case, while in the second case, the number of long packets are fixed. Only active data and auxliary data are transmitted in a long packet. Figure 17 and the following bit table show an example of a transmission sequence.

An 8-byte header is embedded immediately following the MIPI 4-byte long Packet Header (PH) for the receiver to identify the channel data. The 8-byte source video header has to be parsed by the receiver's host processor to decide where to store the received data pertaining to the received channel. The special 8-byte header is defined to avoid emulation of "00" or "FF" bytes.

SHD1 is sent out first and HD2 follows it. The first active video data follows the HD8 byte.

FIGURE 17. CHANNEL DELINEATION

| BIT | BIT 7      | BIT 6       | BIT 5       | BIT 4       | BIT 3       | BIT 2       | BIT 1   | BIT O          |  |  |

|-----|------------|-------------|-------------|-------------|-------------|-------------|---------|----------------|--|--|

| HD1 | <b>'1'</b> | <b>'</b> 0' | <b>'1'</b>  | <b>'O'</b>  | Frame[3:0]  |             |         |                |  |  |

| HD2 | <b>'1'</b> | <b>'O'</b>  | <b>'1'</b>  | <b>'</b> 0' | ʻ0'         | '0'         | ʻ0'     | Field          |  |  |

| HD3 | <b>'1'</b> | <b>'</b> 0' | <b>'1'</b>  | <b>'</b> 0' |             | Lin         | e[11:8] |                |  |  |

| HD4 | <b>'1'</b> | '0'         | <b>'1</b> ' | <b>'</b> 0' | Line[7:4]   |             |         |                |  |  |

| HD5 | <b>'1'</b> | '0'         | <b>'1</b> ' | <b>'</b> 0' |             | Li          | ne[3:0] |                |  |  |

| HD6 | <b>'1'</b> | ʻ0'         | <b>'1'</b>  | <b>'</b> 0' | <b>'</b> 0' | <b>'</b> 0' | CHIE    | <b>D</b> [1:0] |  |  |

| HD7 | <b>'1'</b> | ʻ0'         | <b>'1'</b>  | <b>'</b> 0' | VDLOSS      | HLOCK       | SLOCK   | VLOCK          |  |  |

| HD8 | <b>'1'</b> | ʻ0'         | <b>'1'</b>  | ʻ0'         | MONO        | DET50       | DETSTUS | V_STABLE       |  |  |

- CHID Video channel ID, from 0 to 3

- Line Line number

- Field Field indicator. 0 is the first (top) field. 1 is the second (bottom) field

- Frame Frame number

- VDLOSS Same as 0x103[7]

- HLOCK, SLOCK, VLOCK Same as 0x103[6], 0x103[5], 0x103[3]

- MONO Same as 0x103[1]

- DET50 Same as 0x103[0]

- DETSTUS Same as 0x11c[7]

- V\_STABLE Video data stable flag when video is detected

#### **Optional Histogram as Additional Pixel Data**

To enable histogram-line output on either a MIPI or BT.656 output, the following register bits need to be set:

- Reg0x1C0[7] = master (four separate histograms)

- Reg0x1C0[6] = union (4-in-1 histogram)

- Reg0x1E7[0] = hist\_on1 = 1 in both master or union mode

- Reg0x2E7[0] = hist\_on2 = 1 in master mode only

- Reg0x3E7[0] = hist\_on3 = 1 in master mode only

- Reg0x4E7[0] = hist\_on4 = 1 in master mode only

Because VActiveNs do not line up in union mode, Channels 2-4 evaluate the histogram following Channel 1's Vactive. The reported histogram is the partial frame of Channels 2-4. In the union mode, there is no need to turn on histogram-line for Channels 2-4, because they are not precisely one-frame's histogram and they are not in use.

There are two modes in sending histogram[18:0] over to the SoC receiver. Both modes stretch 19 bits to 4 bytes.

| • MIPI-mode:             | {8'h00},                        |

|--------------------------|---------------------------------|

|                          | {8'h00},                        |

|                          | {8'h00},                        |

|                          | {8'h00},                        |

|                          | {8'h00},                        |

|                          | {5'h00, histogram[18:16],       |

|                          | {histogram[15:8]},              |

|                          | {histogram[7:0]} }              |

| • CCIR656-mode: {8'h55}, | {8'h55},                        |

|                          | {8'h55},                        |

|                          | {4'h5, 1'h0, histogram[18:16]}, |

|                          | {4'h5, histogram[15:12]},       |

|                          | {4'h5, histogram[11:8]},        |

|                          | {4'h5, histogram[7:4]},         |

|                          | {4'h5, histogram[3:0]} }        |

The format is cast in the decif\_csc module and cannot be changed in the CSI because there is no need to furnish both simultaneously.

The accumulated histogram of each picture is allocated to 128-bins by grouping two levels into one bin.

At the end of a picture, the video-active is extended by one or more lines and the last line contains histogram data.

These 128 bins are transmitted as the first 1024 active pixels according to the above format. The remaining (1440-1024) active pixels are filled with the black pixels "8'h80" and "8'h10".

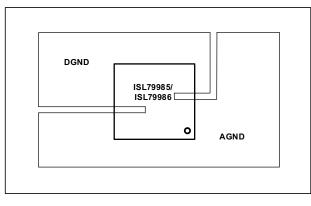

## **PCB Layout Considerations**

In the Printed Circuit Board (PCB) layout, ground is the most important consideration to achieve a low level of noise. In general, avoid long current loops, especially when mixing analog signals with digital signals. The best way to achieve this is to partition the analog and digital portions very carefully so that the signal and return paths can be localized in their vicinity. Strategic partitioning and placement may make splitting the plane into digital and analog ground unnecessary. This helps prevent the split planes from creating longer loops that are bad for EMC and can spread interference to other sections.

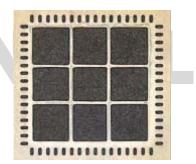

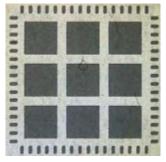

The ground plane should cover most of the PCB area with separated digital and analog ground planes surrounding the chip. These two planes should be at the same electrical potential and connected together under the ISL79987 and ISL79988. Figure 18 shows a ground plane layout example.

To minimize crosstalk, separate the digital signals of the ISL79987 and ISL79988 from the analog circuitry. The digital signals should not cross over the analog power and ground plane. Avoid running parallel digital lines for long distance.

For the QFN package, the exposed die pad (ground bond) can be either floating or soldered to the PCB ground to enhance thermal performance, see Figure 19.

FIGURE 18. GROUND PLANES

FIGURE 19. EXPOSED DIE PAD

## **Thermal PAD Considerations**

#### **Thermal Pad Land Design Input**

The size of the thermal land should at least match the exposed die flag size. However, it is necessary to avoid solder bridging between thermal pad and the perimeter pads. Renesas recommends a clearance of 0.15mm between thermal pad and perimeter pads.

#### **Thermal Via Design**