MCIMX8DXL-WEVK Board User Manual

Rev. 1 — 10 March 2023

**User manual**

#### **Document Information**

| Information | Content                                                                                                                                                         |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | MCIMX8DXL-WEVKUM, MCIMX8DXL-WEVK, i.MX 8DXL, i.MX 8DualXLite                                                                                                    |

| Abstract    | The MCIMX8DXL-WEVK board provides a comprehensive platform for design and evaluation of most commonly used features of the NXP i.MX 8DXL applications processor |

MCIMX8DXL-WEVK Board User Manual

## 1 Overview

The MCIMX8DXL-WEVK board provides a comprehensive platform for design and evaluation of most commonly used features of the NXP i.MX 8DXL applications processor, in a small and low-cost package.

The MCIMX8DXL-WEVK board is an entry-level development board to familiarize you with the processor, before you invest a large amount of resources in more specific designs. The board is lead-free and RoHS-compliant.

For information on how to set up and boot the board, see *i.MX 8DXL Evaluation Kit Quick Start Guide*, which is available in the MCIMX8DXL-WEVK board kit. To run the preloaded image, the board DIP switch SW1 must be set to make the board boot from processor internal eFuse (default setting). For more details, see <u>Section 1.10</u>.

This document provides detailed information about the MCIMX8DXL-WEVK board interfaces, power supplies, clocks, connectors, jumpers, push buttons, DIP switch, and LEDs.

## 1.1 Acronyms

The table below lists the acronyms used in this document.

| Table 1. Acronyms |                                                     |  |  |

|-------------------|-----------------------------------------------------|--|--|

| Acronym           | Meaning                                             |  |  |

| ACM               | Audio clock mux                                     |  |  |

| ADC               | Analog-to-digital converter                         |  |  |

| BCU               | Board Control Utilities                             |  |  |

| BSP               | Board support package                               |  |  |

| CAN               | Controller Area Network                             |  |  |

| СС                | Configuration channel                               |  |  |

| DFP               | Downstream-Facing Port                              |  |  |

| DIP               | Dual in-line package                                |  |  |

| DRP               | Dual-Role Power                                     |  |  |

| EEPROM            | Electrically erasable programmable read-only memory |  |  |

| eMMC              | Embedded Multimedia Card                            |  |  |

| ESD               | Electrostatic discharge                             |  |  |

| FlexCAN           | Flexible Controller Area Network                    |  |  |

| FlexSPI           | Flexible Serial Peripheral Interface                |  |  |

| 12C               | Inter-Integrated Circuit                            |  |  |

| IC                | Integrated circuit                                  |  |  |

| I2S               | Inter-IC Sound                                      |  |  |

| JTAG              | Joint Test Action Group                             |  |  |

| LCD               | Liquid Crystal Display                              |  |  |

| LCDIF             | Liquid Crystal Display Interface                    |  |  |

| LDO               | Low-dropout regulator                               |  |  |

| LED               | Light-emitting diode                                |  |  |

| LPDDR4            | Low-Power Double Data Rate Gen4                     |  |  |

MCIMX8DXL-WEVKUM

© 2023 NXP B.V. All rights reserved.

MCIMX8DXL-WEVK Board User Manual

|         | Table 1. Acronymscontinued                  |  |  |  |  |

|---------|---------------------------------------------|--|--|--|--|

| Acronym | Meaning                                     |  |  |  |  |

| MII     | Media-Independent Interface                 |  |  |  |  |

| MPSSE   | Multi-protocol synchronous serial engine    |  |  |  |  |

| MT/s    | Megatransfers per second                    |  |  |  |  |

| OS      | Operating system                            |  |  |  |  |

| OTG     | On-The-Go                                   |  |  |  |  |

| PMIC    | Power management integrated circuit         |  |  |  |  |

| PMT     | Power Measurement Tool                      |  |  |  |  |

| QSPI    | Quad Serial Peripheral Interface            |  |  |  |  |

| RGMII   | Reduced Gigabit Media-Independent Interface |  |  |  |  |

| RTC     | Real-time clock                             |  |  |  |  |

| SAI     | Serial Audio Interface                      |  |  |  |  |

| SCU     | System controller unit                      |  |  |  |  |

| SD      | Secure digital                              |  |  |  |  |

| SDRAM   | Synchronous dynamic random-access memory    |  |  |  |  |

| SPI     | Serial Peripheral Interface                 |  |  |  |  |

| TFT     | Thin film transistor                        |  |  |  |  |

| UART    | Universal Asynchronous Receiver/Transmitter |  |  |  |  |

| UFP     | Upstream-Facing Port                        |  |  |  |  |

| USDHC   | Ultra Secured Digital Host Controller       |  |  |  |  |

| USB     | Universal Serial Bus                        |  |  |  |  |

| V2X     | Vehicle-to-everything                       |  |  |  |  |

| WLAN    | Wireless local-area network                 |  |  |  |  |

## **1.2 Related documentation**

The table below lists and explains the additional documents and resources that you can refer to for more information on the board. Some of the documents listed below may be available only under a non-disclosure agreement (NDA). To request access to these documents, contact your local field applications engineer (FAE) or sales representative.

Table 2. Related documentation

| Documents                                                                        | Description                                                                                                                           | Link / how to obtain                          |

|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| i.MX 8DXL Evaluation Kit Quick<br>Start Guide                                    | Provides information on how to set up and boot the MCIMX8DXL-WEVK board                                                               | Available in the MCIMX8DXL-<br>WEVK board kit |

| i.MX 8DualXLite/8SoloXLite<br>Applications Processor Reference<br>Manual         | Intended for system software and hardware<br>developers and applications programmers who<br>want to develop products with this device | Contact NXP FAE / sales<br>representative     |

| i.MX 8XLite Automotive and<br>Infotainment Applications<br>Processors Data Sheet | Provides information about electrical characteristics, hardware design considerations, and ordering information                       |                                               |

### MCIMX8DXL-WEVK Board User Manual

| Documents                                                         | Description                                                                                                                                                                                                                                                                                                                                                                                    | Link / how to obtain |

|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| i.MX 8XLite Industrial Applications<br>Processors Data Sheet      |                                                                                                                                                                                                                                                                                                                                                                                                |                      |

| i.MX 8QM / i.MX 8QXP / i.MX<br>8DXL Hardware Developer's<br>Guide | This purpose of this document is to help hardware<br>engineers design and test their i.MX 8QM/8<br>QXP/8DXL processor-based designs. It provides<br>information about board layout recommendations<br>and design checklists to ensure first-pass<br>success and avoid board bring-up problems.                                                                                                 |                      |

| i.MX 8DXL Errata                                                  | Mask set errata to mask 0P23B                                                                                                                                                                                                                                                                                                                                                                  | -                    |

| MCIMX8DXL-WEVK design files                                       | Board schematics, assembly layout                                                                                                                                                                                                                                                                                                                                                              |                      |

| i.MX Linux User's Guide                                           | This document describes how to build and install<br>the i.MX Linux OS BSP (where BSP stands for<br>board support package) on the i.MX platform.<br>It also covers special i.MX features and how to<br>use them. The document also provides the steps<br>to run the i.MX platform, including board DIP<br>switch settings, and instructions on configuring<br>and using the U-Boot boot loader. |                      |

#### Table 2. Related documentation...continued

## 1.3 Kit contents

The table below lists the items included in the MCIMX8DXL-WEVK hardware kit.

| Item              | Description                                                                                                               |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------|--|

| Board             | MCIMX8DXL-WEVK                                                                                                            |  |

| AC power cord     | IEC cable assembly with locking system for IEC C14 inlet, US version, 1.83 m                                              |  |

| SD card           | 16 GB SD card                                                                                                             |  |

| Power supply      | 12 V AC/DC, 11.5 A, level VI power supply, with 4-pin DIN output type                                                     |  |

| Worldwide adapter | Hardware accessory, universal adapter                                                                                     |  |

| Wi-Fi card        | Wi-Fi card with Wi-Fi 6, 802.11 a/b/g/n, Bluetooth 5.2 BR/EDR/LE, SDIO 3.0 interface, SDR104 at 208 MHz, NXP 88W9098 chip |  |

| Fastner/screw     | Fastner, screw M2.5x4 machine PHP SS                                                                                      |  |

| USB Type-C cable  | USB 3.0 Type-C male to Type-A male cable assembly for serial download                                                     |  |

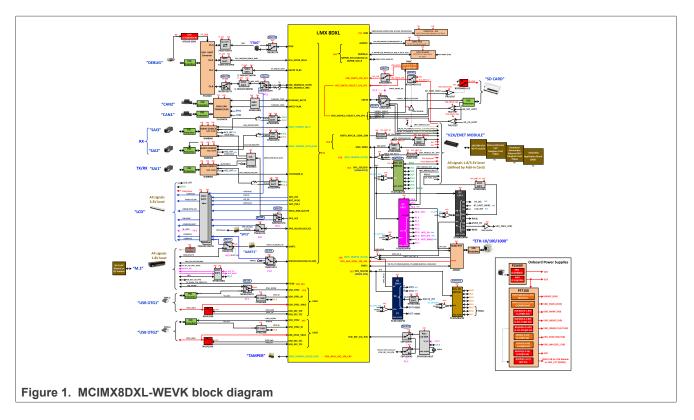

## 1.4 Block diagram

The figure below shows the MCIMX8DXL-WEVK block diagram.

MCIMX8DXL-WEVK Board User Manual

## 1.5 Board features

The table below lists the features of the MCIMX8DXL-WEVK board.

| Board feature    | Processor feature used                                         | Description                                                                                                                                                                                                                                                                                        |

|------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processor        |                                                                | NXP i.MX 8DualXLite processor (PIMX8DL1AVNFZAB), with two Arm<br>Cortex-A35 cores each running at 1.2 GHz and one Arm Cortex-M4F<br>core running at 264 MHz frequency.<br><b>Note:</b> For details on MIMX8UD7DVP10SA, see i.MX 8DualXLite/8Solo<br>XLite Applications Processor Reference Manual. |

| LPDDR4           | DDR controller and PHY                                         | 1 GB LPDDR4 SDRAM with 16-bit data bus and 4.266 Gbit/s data rate                                                                                                                                                                                                                                  |

| Octal flash      | Two FlexSPI controllers,<br>QSPI0A and QSPI0B                  | 512 Mbit octal SPI NOR flash memory with maximum frequency 200 MHz and operating voltage 1.8 V                                                                                                                                                                                                     |

| eMMC             | USDHC0 controller                                              | 32 GB NAND flash eMMC memory with 8-bit data bus                                                                                                                                                                                                                                                   |

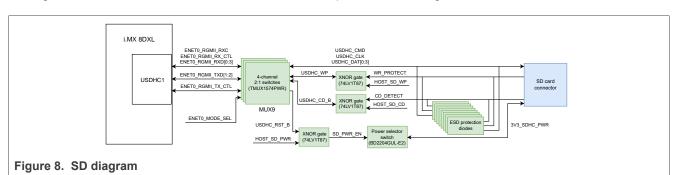

| SD card          | USDHC1 controller                                              | SD card connector                                                                                                                                                                                                                                                                                  |

| V2X/Ethernet     | ENET0, USDHC1, USDHC2,<br>SPI2, and SNVS_TAMPER<br>controllers | V2X/Ethernet socket for adding a V2X/Ethernet extension board                                                                                                                                                                                                                                      |

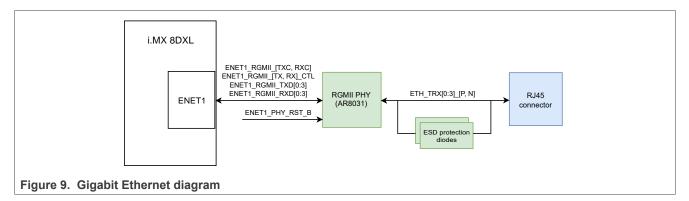

| Gigabit Ethernet | ENET1 controller                                               | An RGMII Ethernet PHY terminating at an RJ45 Gigabit Ethernet (10/100/1000 Mbit/s) connector                                                                                                                                                                                                       |

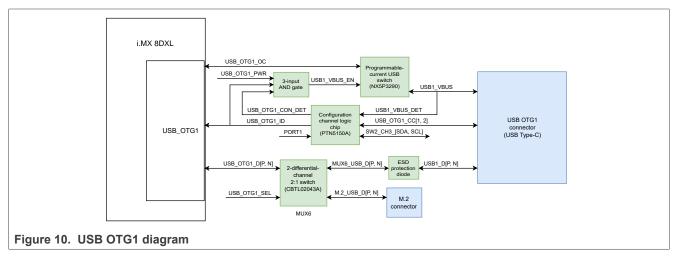

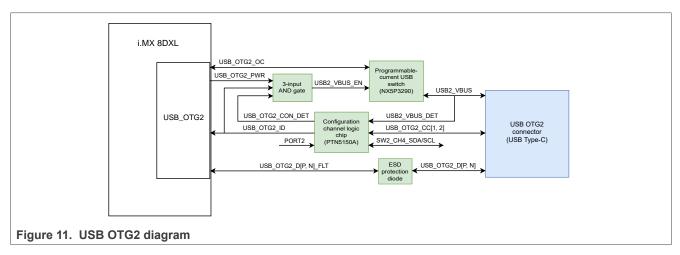

| USB              | USB_OTG1 and USB_OTG2 controllers                              | USB_OTG1 controller is connected to a USB 3.2 Gen 2 Type-C connector. USB_OTG2 controller is connected to another USB 3.2 Gen 2 Type-C connector or M.2 connector.                                                                                                                                 |

Table 3. MCIMX8DXL-WEVK features

## MCIMX8DXL-WEVK Board User Manual

| Board feature           | Processor feature used                                | Description                                                                                                                                                                                  |

|-------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

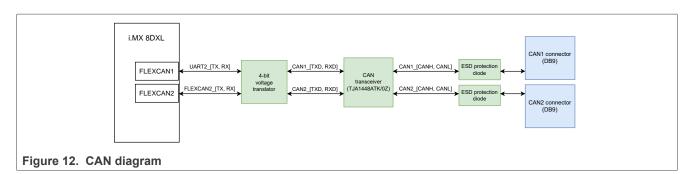

| CAN                     | FlexCAN1 and FlexCAN2 controllers                     | A high-speed dual CAN transceiver terminating at two DB9 female CAN connectors                                                                                                               |

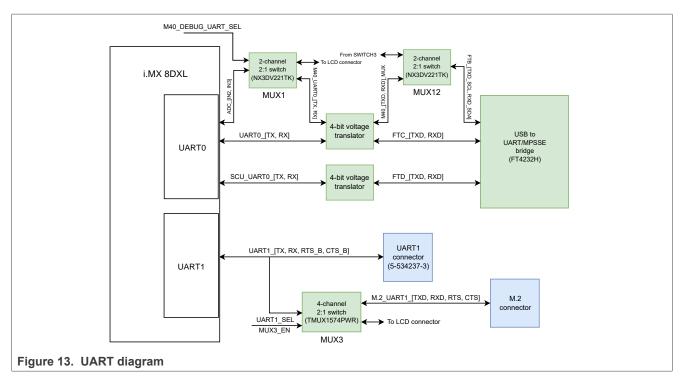

| UART                    | UART0 and UART1 controllers                           | UART0 controller is connected to the debug USB host via a USB to UART/MPSSE bridge. UART1 controller is connected to UART1 connector and M.2 connector (software-controlled).                |

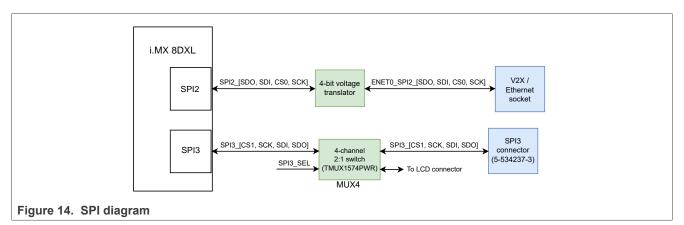

| SPI                     | SPI2 and SPI3 controllers                             | SPI2 controller is connected to a V2X/Ethernet socket. SPI3 controller is connected to SPI3 connector (software-controlled).                                                                 |

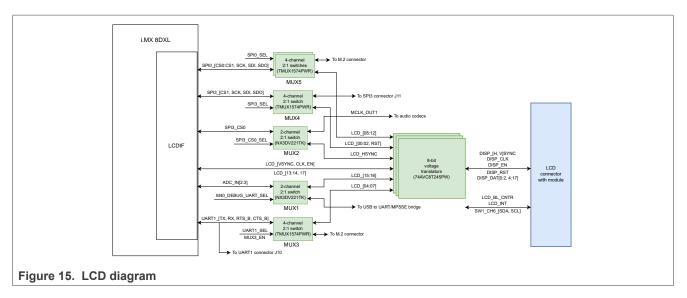

| LCD                     | LCDIF controller                                      | LCD connector with a TFT touch screen module                                                                                                                                                 |

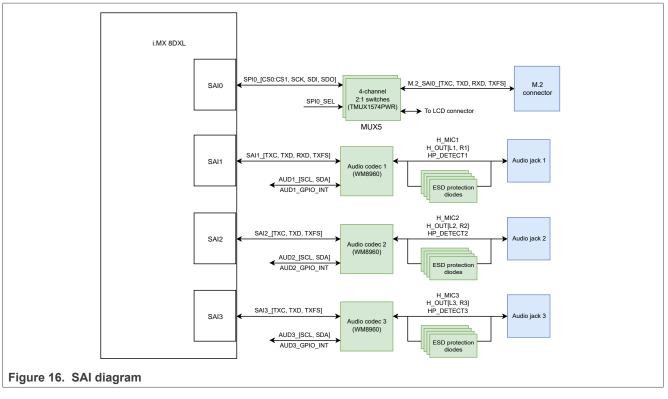

| SAI                     | SAI0, SAI1, SAI2, and SAI3 controllers                | SAI0 controller is connected to M.2 connector. Each of the SAI1, SAI2, and SAI3 controllers is connected to an audio codec terminating at an audio jack.                                     |

| M.2                     | USB_OTG1, SAI0, UART1,<br>PCIE0, PCIE_IOB controllers | M.2 Key-E mini card connector                                                                                                                                                                |

| I/O expander            |                                                       | Five input/output expanders for remote I/O expansion via the I2C-bus interface                                                                                                               |

| I2C                     | I2C2, I2C3, and PMIC_I2C controllers                  | I2C2, I2C3, and PMIC_I2C buses for processor; FTB bus for debug USB host (via USB to UART/MPSSE bridge)                                                                                      |

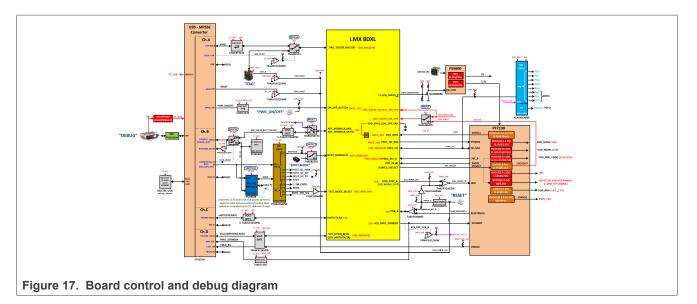

| Board control and debug |                                                       | A USB to UART/MPSSE bridge (connected to host computer through<br>a USB micro-B connector), DIP switch, and JTAG header for board<br>control and debug                                       |

| Power                   |                                                       | The board gets powered from external 12 V DC supply through a DIN connector. It has a PMIC device for managing board power. It provides six power monitors for power and energy measurement. |

| Clock                   |                                                       | Six crystal oscillators and one two-output PCIe clock generator                                                                                                                              |

#### Table 3. MCIMX8DXL-WEVK features...continued

## **1.6 Board pictures**

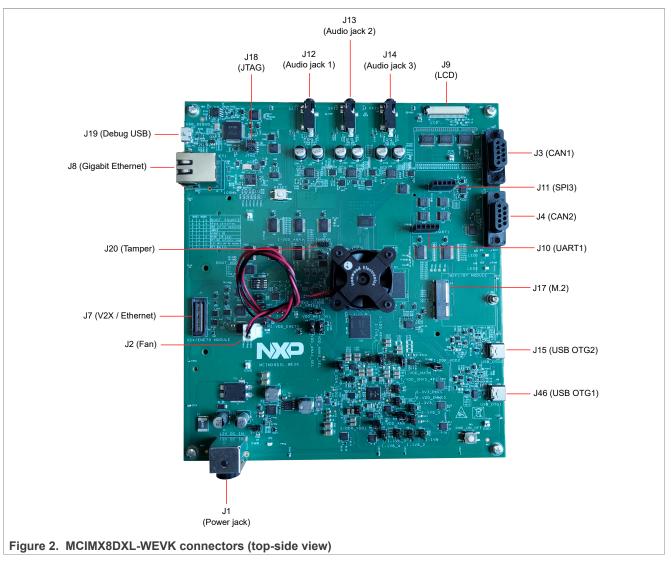

The figure below shows the top-side view of the MCIMX8DXL-WEVK board, with connectors highlighted.

## **NXP Semiconductors**

# MCIMX8DXL-WEVKUM

### MCIMX8DXL-WEVK Board User Manual

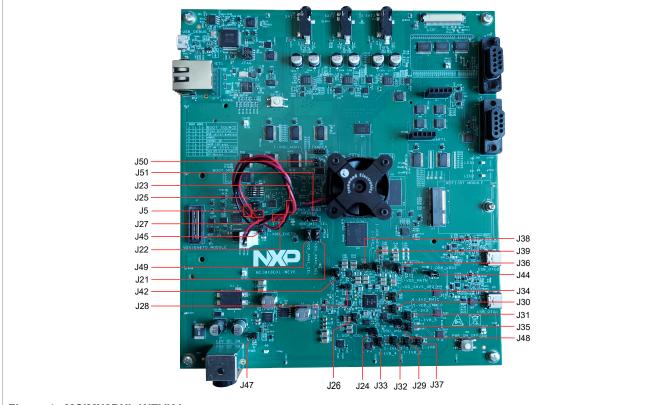

The figure below shows the bottom-side view of the MCIMX8DXL-WEVK board, with one connector highlighted.

## MCIMX8DXL-WEVK Board User Manual

Figure 3. MCIMX8DXL-WEVK connectors (bottom-side view)

The figure below shows the board jumpers highlighted.

## MCIMX8DXL-WEVK Board User Manual

Figure 4. MCIMX8DXL-WEVK jumpers

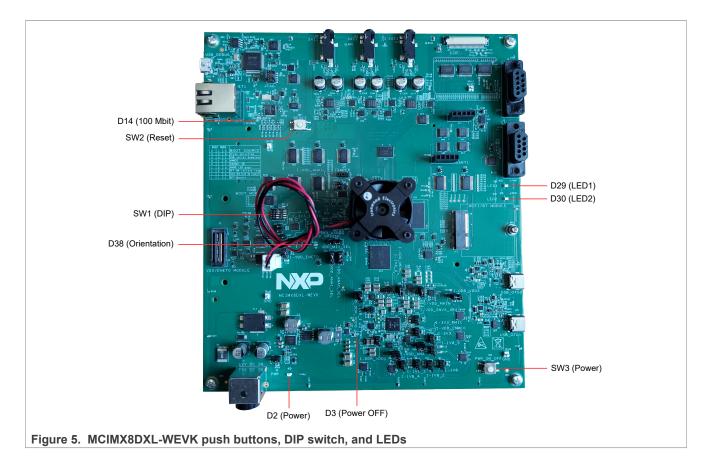

The figure below shows the push buttons, DIP switch, and LEDs of the board highlighted.

## MCIMX8DXL-WEVK Board User Manual

## **1.7 Connectors**

The table below describes the connectors of the MCIMX8DXL-WEVK board. The connectors are shown in Figure 2 and Figure 3.

| Part identifier | PCB label           | Connector type        | Description                         | Reference section |

|-----------------|---------------------|-----------------------|-------------------------------------|-------------------|

| J1              | 12V DC IN           | 4-pin DIN connector   | DC power jack                       | Section 2.2       |

| J6              | SD CARD             | SD card receptacle    | SD card slot                        | Section 2.7       |

| J7              | V2X/ENET0<br>MODULE | 2x30-pin connector    | V2X/Ethernet socket                 | Section 2.8       |

| J8              | ENET1               | RJ45 connector        | Gigabit Ethernet connector          | Section 2.9       |

| J46             | USB_OTG1            | USB 3.2 Gen 2 Type-C  | USB OTG1 connector                  | Section 2.10      |

| J15             | USB_OTG2            | connector             | USB OTG2 connector                  |                   |

| J3              | CAN1                | DB9 female connector  | CAN1 connector                      | Section 2.11      |

| J4              | CAN2                |                       | CAN2 connector                      |                   |

| J10             | UART1               | 5-position receptacle | UART1 connector                     | Section 2.12      |

| J11             | SPI3                | 5-position receptacle | SPI3 connector                      | Section 2.13      |

| J9              | LCD                 | 40-pin connector      | LCD connector                       | Section 2.14      |

| J12             | SAI1                | 5-pin audio jack      | Input/output jack for audio codec 1 | Section 2.15      |

### Table 4. MCIMX8DXL-WEVK connectors

## MCIMX8DXL-WEVK Board User Manual

| Part identifier | PCB label         | Connector type               | Description                                     | Reference section                                         |

|-----------------|-------------------|------------------------------|-------------------------------------------------|-----------------------------------------------------------|

| J13             | SAI2              |                              | Input/output jack for audio codec 2             |                                                           |

| J14             | SAI3              | _                            | Input/output jack for audio codec 3             |                                                           |

| J17             | WIFI/BT<br>MODULE | 75-pin M.2 connector         | M.2 Key-E mini card connector                   | Section 2.16                                              |

| J19             | USB_DEBUG         | USB 2.0 micro-B<br>connector | Debug USB connector                             | Section 2.19.3                                            |

| J18             | JTAG              | 2x5-pin header               | JTAG header                                     | Section 2.19.4                                            |

| J2              | FAN               | 1x3-pin header               | Fan header with lock                            | For more information                                      |

| J20             | TAMPER            | 1x3-pin header               | Allows remote tamper detection of the processor | on these connectors,<br>see MCIMX8DXL-<br>WEVK schematics |

### Table 4. MCIMX8DXL-WEVK connectors...continued

## 1.8 Jumpers

The table below describes the jumpers of the MCIMX8DXL-WEVK board. The jumpers are shown in Figure 4.

\_\_\_\_

| Part identifier | PCB label   | Jumper type    | Description                                                                                                                                                                                                                                               | Reference section |

|-----------------|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| J22             | I-5V0       | 1x2-pin header | <ul><li>5V0 supply current measurement disable jumper:</li><li>Open (default setting): 5V0</li></ul>                                                                                                                                                      | Section 2.2.1     |

|                 |             |                | <ul> <li>supply current is measured by<br/>onboard power monitor U11</li> <li>Shorted: Current measurement<br/>is disabled for 5V0 supply</li> </ul>                                                                                                      |                   |

| J23             | I-3V3_USB   | 1x2-pin header | 3V3_USB supply current<br>measurement disable jumper:                                                                                                                                                                                                     |                   |

|                 |             |                | <ul> <li>Open (default setting):<br/>3V3_USB supply current is<br/>measured by onboard power<br/>monitor U11</li> </ul>                                                                                                                                   |                   |

|                 |             |                | <ul> <li>Shorted: Current measurement<br/>is disabled for 3V3_USB supply</li> </ul>                                                                                                                                                                       |                   |

| J25             | I-3V3_IO    | 1x2-pin header | <ul> <li>3V3_IO supply current<br/>measurement disable jumper:</li> <li>Open (default setting): 3V3_IO<br/>supply current is measured by<br/>onboard power monitor U11</li> <li>Shorted: Current measurement<br/>is disabled for 3V3_IO supply</li> </ul> |                   |

| J27             | I-3V3_ENET0 | 1x2-pin header | <ul> <li>VDD_ENET0_VSEL- supply<br/>current measurement disable<br/>jumper:</li> <li>Open (default setting): VDD_<br/>ENET0_VSEL- supply current<br/>is measured by onboard power<br/>monitor U11</li> </ul>                                              |                   |

Table 5. MCIMX8DXL-WEVK jumpers

## MCIMX8DXL-WEVK Board User Manual

| Part identifier | PCB label  | Jumper type    | Description                                                                                                                                                                                                                                                              | Reference section |

|-----------------|------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|                 |            |                | Shorted: Current measurement<br>is disabled for VDD_ENET0_<br>VSEL- supply                                                                                                                                                                                               | _                 |

| J24             | I-VDD_ANA  | 1x2-pin header | <ul> <li>VDD_ANA supply current<br/>measurement disable jumper:</li> <li>Open: VDD_ANA supply current<br/>is measured by onboard power<br/>monitor U12</li> <li>Shorted (default setting):<br/>Current measurement is<br/>disabled for VDD_ANA supply</li> </ul>         |                   |

| J26             | I-DDR_VDD1 | 1x2-pin header | <ul> <li>DDR_VDD1 supply current<br/>measurement disable jumper:</li> <li>Open (default setting): DDR_<br/>VDD1 supply current is<br/>measured by onboard power<br/>monitor U12</li> <li>Shorted: Current measurement<br/>is disabled for DDR_VDD1<br/>supply</li> </ul> |                   |

| J28             | I-1V8_1    | 1x2-pin header | <ul> <li>1V8_1 supply current<br/>measurement disable jumper:</li> <li>Open (default setting): 1V8_1<br/>supply current is measured by<br/>onboard power monitor U12</li> <li>Shorted: Current measurement<br/>is disabled for 1V8_1 supply</li> </ul>                   | -                 |

| J29             | I-1V8_2    | 1x2-pin header | <ul> <li>1V8_2 supply current<br/>measurement disable jumper:</li> <li>Open (default setting): 1V8_2<br/>supply current is measured by<br/>onboard power monitor U12</li> <li>Shorted: Current measurement<br/>is disabled for 1V8_2 supply</li> </ul>                   |                   |

| J30             | I-3V3_PMIC | 1x2-pin header | <ul> <li>3V3_PMIC supply current<br/>measurement disable jumper:</li> <li>Open (default setting): 3<br/>V3_PMIC supply current is<br/>measured by onboard power<br/>monitor U14</li> <li>Shorted: Current measurement<br/>is disabled for 3V3_PMIC<br/>supply</li> </ul> |                   |

| J31             | I-3V3      | 1x2-pin header | <ul> <li>3V3 supply current measurement disable jumper:</li> <li>Open (default setting): 3V3 supply current is measured by onboard power monitor U14</li> <li>Shorted: Current measurement is disabled for 3V3 supply</li> </ul>                                         |                   |

### Table 5. MCIMX8DXL-WEVK jumpers...continued

# MCIMX8DXL-WEVK Board User Manual

| Part identifier | PCB label      | Jumper type    | Description                                                                                                                                                                                                                                                                 | Reference section |

|-----------------|----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| J34             | I-VDD_SNVS_4P2 | 1x2-pin header | <ul> <li>VDD_SNVS1 supply current<br/>measurement disable jumper:</li> <li>Open (default setting): VDD_<br/>SNVS1 supply current is<br/>measured by onboard power<br/>monitor U14</li> <li>Shorted: Current measurement<br/>is disabled for VDD_SNVS1<br/>supply</li> </ul> |                   |

| J36             | I-VDD_MAIN     | 1x2-pin header | <ul> <li>VDD_MAIN supply current<br/>measurement disable jumper:</li> <li>Open: VDD_MAIN supply<br/>current is measured by onboard<br/>power monitor U14</li> <li>Shorted (default setting):<br/>Current measurement is<br/>disabled for VDD_MAIN supply</li> </ul>         |                   |

| J32             | I-1V8_3        | 1x2-pin header | <ul> <li>1V8_3 supply current<br/>measurement disable jumper:</li> <li>Open (default setting): 1V8_3<br/>supply current is measured by<br/>onboard power monitor U15</li> <li>Shorted: Current measurement<br/>is disabled for 1V8_3 supply</li> </ul>                      |                   |

| J33             | I-1V8_4        | 1x2-pin header | <ul> <li>1V8_4 supply current<br/>measurement disable jumper:</li> <li>Open (default setting): 1V8_4<br/>supply current is measured by<br/>onboard power monitor U15</li> <li>Shorted: Current measurement<br/>is disabled for 1V8_4 supply</li> </ul>                      |                   |

| J35             | I-1V8_5        | 1x2-pin header | <ul> <li>1V8_5 supply current<br/>measurement disable jumper:</li> <li>Open (default setting): 1V8_5<br/>supply current is measured by<br/>onboard power monitor U15</li> <li>Shorted: Current measurement<br/>is disabled for 1V8_5 supply</li> </ul>                      |                   |

| J37             | I-1V8          | 1x2-pin header | <ul> <li>1V8 supply current measurement disable jumper:</li> <li>Open (default setting): 1V8 supply current is measured by onboard power monitor U15</li> <li>Shorted: Current measurement is disabled for 1V8 supply</li> </ul>                                            |                   |

| J38             | I-1V8_6        | 1x2-pin header | <ul> <li>1V8_6 supply current<br/>measurement disable jumper:</li> <li>Open (default setting): 1V8_6<br/>supply current is measured by<br/>onboard power monitor U18</li> </ul>                                                                                             |                   |

### Table 5. MCIMX8DXL-WEVK jumpers...continued

# MCIMX8DXL-WEVK Board User Manual

| Part identifier | PCB label      | Jumper type    | Description                                                                                                                                                                                                                                                                                                                                                                   | Reference section |

|-----------------|----------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|                 |                |                | Shorted: Current measurement<br>is disabled for 1V8_6 supply                                                                                                                                                                                                                                                                                                                  |                   |

| J50             | I-VDD_ANA1     | 1x2-pin header | <ul> <li>Processor VDD_ANA1_1</li> <li>P8 power domain current<br/>measurement disable jumper:</li> <li>Open (default setting):<br/>Processor VDD_ANA1_1</li> <li>P8 power domain current is<br/>measured by onboard power<br/>monitor U18</li> <li>Shorted: Current measurement<br/>is disabled for VDD_ANA1_1P8<br/>power domain of the processor</li> </ul>                |                   |

| J48             | I-VDD_EMMC0    | 1x2-pin header | <ul> <li>Processor VDD_EMMC0_1</li> <li>P8_3P3 power domain current<br/>measurement disable jumper:</li> <li>Open: Processor VDD_<br/>EMMC0_1P8_3P3 power<br/>domain current is measured by<br/>onboard power monitor U18</li> <li>Shorted (default setting):<br/>Current measurement is<br/>disabled for VDD_EMMC0_1<br/>P8_3P3 power domain of the<br/>processor</li> </ul> |                   |

| J47             | I-12V          | 1x2-pin header | <ul> <li>12V0 supply current measurement<br/>disable jumper:</li> <li>Open (default setting): 12V0<br/>supply current is measured by<br/>onboard power monitor U18</li> <li>Shorted: Current measurement<br/>is disabled for 12V0 supply</li> </ul>                                                                                                                           |                   |

| J39             | I-VDD_MEMC     | 1x2-pin header | <ul> <li>VDD_MEMC supply current<br/>measurement disable jumper:</li> <li>Open: VDD_MEMC supply<br/>current is measured by onboard<br/>power monitor U19</li> <li>Shorted (default setting):<br/>Current measurement is<br/>disabled for VDD_MEMC supply</li> </ul>                                                                                                           | ,                 |

| J42             | I-VDD_DDR_VDDQ | 1x2-pin header | <ul> <li>VDD_DDR_VDDQ supply current measurement disable jumper:</li> <li>Open: VDD_DDR_VDDQ supply current is measured by onboard power monitor U19</li> <li>Shorted (default setting): Current measurement is disabled for VDD_DDR_VDDQ supply</li> </ul>                                                                                                                   |                   |

| J44             | I-DDR_VDD2     | 1x2-pin header | DDR_VDD2 supply current measurement disable jumper:                                                                                                                                                                                                                                                                                                                           |                   |

#### Table 5. MCIMX8DXL-WEVK jumpers...continued

MCIMX8DXL-WEVKUM

© 2023 NXP B.V. All rights reserved.

## MCIMX8DXL-WEVK Board User Manual

| Part identifier | PCB label    | Jumper type    | Description                                                                                                                                                                                                                                                                                                                     | Reference section                                                              |

|-----------------|--------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

|                 |              |                | <ul> <li>Open: DDR_VDD2 supply<br/>current is measured by onboard<br/>power monitor U19</li> <li>Shorted (default setting):<br/>Current measurement is<br/>disabled for DDR_VDD2 supply</li> </ul>                                                                                                                              |                                                                                |

| J45             | I-VDD_ENET0  | 1x2-pin header | <ul> <li>VDD_ENET0 supply current<br/>measurement disable jumper:</li> <li>Open: VDD_ENET0 supply<br/>current is measured by onboard<br/>power monitor U19</li> <li>Shorted (default setting):<br/>Current measurement is<br/>disabled for VDD_ENET0<br/>supply</li> </ul>                                                      |                                                                                |

| J21             | VDD_ANA0_SEL | 1x3-pin header | <ul> <li>Processor VDD_ANA0_1P8<br/>source power supply selection<br/>jumper:</li> <li>Pins 1-2 shorted (default<br/>setting): Processor analog<br/>supply VDD_ANA0_1P8 gets<br/>powered from VDD_ANA supply</li> <li>Pins 2-3 shorted: VDD_ANA0_<br/>1P8 gets powered from 1V8_1<br/>supply</li> </ul>                         | For more information<br>on these jumpers,<br>see MCIMX8DXL-<br>WEVK schematics |

| J49             | VDD_ANA1_SEL | 1x3-pin header | <ul> <li>Processor VDD_ANA1_1P8<br/>source power supply selection<br/>jumper:</li> <li>Pins 1-2 shorted (default<br/>setting): Processor analog<br/>supply VDD_ANA1_1P8 gets<br/>powered from VDD_ANA supply</li> <li>Pins 2-3 shorted: VDD_ANA1_<br/>1P8 gets powered from 1V8_1<br/>supply</li> </ul>                         |                                                                                |

| J51             | VDD_MII_SEL  | 1x3-pin header | <ul> <li>MDC/MDIO voltage selection<br/>jumper:</li> <li>1-2 shorted (default setting):<br/>Use this jumper setting if<br/>module connected to V2X/<br/>ENET0 socket uses 3.3 V for<br/>MDC/MDIO signal pair</li> <li>2-3 shorted: Use this jumper<br/>setting if the connected module<br/>provides MDC/MDIO voltage</li> </ul> |                                                                                |

| J5              | PWR_TEST     | 1x2-pin header | <ul> <li>Force enable onboard power supplies jumper:</li> <li>Open (default setting): If the processor was installed with correct orientation during assembly, then onboard power supplies are enabled during</li> </ul>                                                                                                        |                                                                                |

### Table 5. MCIMX8DXL-WEVK jumpers...continued

### MCIMX8DXL-WEVK Board User Manual

| Part identifier | PCB label | Jumper type | Description                                                                                                                                                                                                                                                                                                                                                         | Reference section |

|-----------------|-----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|                 |           |             | <ul> <li>power-on; otherwise, onboard<br/>power supplies are disabled<br/>during power-on</li> <li>Shorted: Onboard power<br/>supplies are enabled during<br/>power-on, irrespective of<br/>processor orientation. This<br/>jumper setting allows to test<br/>onboard power supplies before<br/>installing the processor during<br/>board manufacturing.</li> </ul> |                   |

|                 |           |             | <b>CAUTION:</b> Do not short jumper<br>J5 if the processor is installed on<br>the board. Shorting this jumper<br>with processor installed may<br>cause unrecoverable damage to<br>the processor.                                                                                                                                                                    |                   |

#### Table 5. MCIMX8DXL-WEVK jumpers...continued

### **1.9 Push buttons**

The table below describes the push buttons of the MCIMX8DXL-WEVK board. The push buttons are shown in Figure 5.

| Part identifier | PCB label  | Button name | Description                                                                                                               |

|-----------------|------------|-------------|---------------------------------------------------------------------------------------------------------------------------|

| SW2             | RESET      |             | Pressing this button resets the system and begins a boot sequence                                                         |

| SW3             | PWR_ON_OFF |             | To turn ON power, press and hold this button for 0.5 seconds. To turn OFF power, press and hold the button for 5 seconds. |

### 1.10 DIP switch

The MCIMX8DXL-WEVK board has a dual inline package (DIP) switch SW1, which has a set of four switches: SW1[1:4].

SW1[1:3] are used for selecting boot mode and they are connected to the i.MX 8DXL processor pins SCU\_BOOT\_MODE[0:2], respectively.

SW1[4] is used for controlling system ID memory write protection and it is connected to the debug USB host through the I2C-bus interface of the USB to UART/MPSSE bridge.

For each switch within the DIP switch:

- "OFF" setting corresponds to 0

- "ON" setting corresponds to 1

The table below describes the DIP switch settings. The DIP switch is shown in Figure 5.

| Switches | Supported function | Description                                                                        |

|----------|--------------------|------------------------------------------------------------------------------------|

| SW1[1:3] |                    | SW1[3:1] (SW_BOOT_MODE[2:0]):<br>• 000: Processor internal eFuse (default setting) |

© 2023 NXP B.V. All rights reserved.

### MCIMX8DXL-WEVK Board User Manual

| Switches | Supported function                        | Description                                                                                                                                                                                                                                                     |

|----------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                                           | <ul> <li>001: USB serial download (processor can download a program image from a USB connection)</li> <li>010: EMMC0</li> <li>011: USDHC1: SD card</li> <li>100: NAND, 128 pages</li> <li>101: Reserved</li> <li>110: FlexSPI</li> <li>111: Reserved</li> </ul> |

| SW1[4]   | System ID memory write protection control | <ul> <li>0: Both read and write operations are allowed into system<br/>ID memory U104 (default setting)</li> <li>1: System ID memory is write-protected, only read<br/>operation is allowed</li> </ul>                                                          |

#### Table 7. DIP switch settings...continued

**Note:** For more details on i.MX 8DXL boot modes and boot mode configuration, see "System Boot" chapter of i.MX 8DualXLite/8SoloXLite Applications Processor Reference Manual.

### 1.11 LEDs

The MCIMX8DXL-WEVK board provides six light-emitting diodes (LEDs) for monitoring system functions, such as power-on, reset, and board faults. The information collected from LEDs can be used for debugging purposes.

The table below describes the MCIMX8DXL-WEVK LEDs. The LEDs are shown in Figure 5.

| able o. Michimkodal-WEVA LEDS |                  |           |                                                 |                                                                                                                                                                   |  |

|-------------------------------|------------------|-----------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Part identifier               | PCB label        | LED color | Associated function                             | Description (when LED is ON)                                                                                                                                      |  |

| D2                            | PWR              | Green     | Board power ON<br>status                        | Board is powered ON                                                                                                                                               |  |

| D3                            | PWR_OFF          | Red       | Board power OFF<br>status                       | Board is powered OFF                                                                                                                                              |  |

| D38                           | CHECK_<br>ORIENT | Red       | Processor<br>orientation error                  | The processor is rotated by 90°, 180°, or 270°<br>from pin 1 orientation. To protect the processor,<br>board and processor power supplies have been<br>shut down. |  |

| D14                           | 100Mb            | Red       | 100 Mbit/s<br>Ethernet link<br>connection error | 100 Mbit/s Ethernet link connection is active from<br>RGMII PHY transceiver; 1000 Mbit/s (1 Gbit/s)<br>Ethernet link connection is disabled                       |  |

| D29                           | LED1             | Green     | User LED 1                                      |                                                                                                                                                                   |  |

| D30                           | LED2             | Green     | User LED 2                                      |                                                                                                                                                                   |  |

#### Table 8. MCIMX8DXL-WEVK LEDs

MCIMX8DXL-WEVK Board User Manual

# 2 Functional description

This section describes the features and functions of the MCIMX8DXL-WEVK board.

**Note:** For details of the *i*.MX 8DXL processor features, see *i*.MX 8DualXLite/8SoloXLite Applications Processor Reference Manual.

### 2.1 Processor

The i.MX 8DualXLite (8DXL) applications processor is a member of the i.MX 8 family. This series of applications processors is focused on offering powerful solutions and multiple possibilities of development on projects with advanced graphics and safety-critical applications. More specifically, the i.MX 8DXL is a device that targets the automotive and industrial market segments and offers the possibility of a wide variety of embedded applications.

The chip has a flexible architecture allowing both high performance and low power consumption. It features two Arm Cortex-A35 cores, in addition to one Arm Cortex-M4F general-purpose core. The device includes V2X capabilities, as well as TSN networking and telematics.

For more information about the i.MX 8DXL processor, see the *i.MX* 8DualXLite/8SoloXLite Applications Processor Reference Manual and *i.MX* 8XLite Automotive and Infotainment Applications Processors Data Sheet.

## 2.2 Power supply

The MCIMX8DXL-WEVK board has the following primary power supplies:

- External 12 V DC power supply through 4-pin DIN connector J1

- External 5 V DC power supply through USB micro-B connector J19

These primary power supplies are used to produce secondary power supplies on the board to power the board components, including the i.MX 8DXL processor, power regulators, clock generator, LPDDR4 memory, octal flash memory, eMMC memory, V2X/Ethernet socket, Gigabit Ethernet PHY, CAN transceiver, LCD connector, audio codecs, M.2 connector, USB to UART/MPSSE bridge, JTAG header, DIP switch, and LEDs.

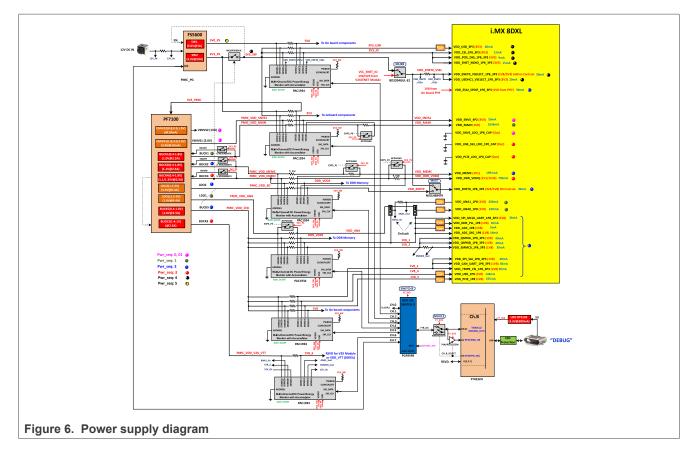

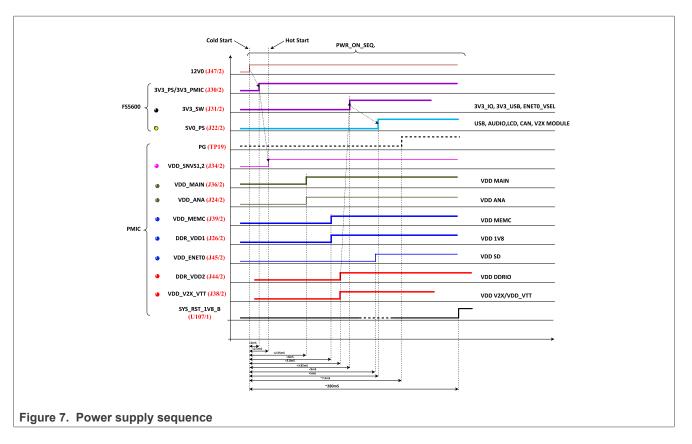

The figure below shows the MCIMX8DXL-WEVK power supply diagram.

## MCIMX8DXL-WEVK Board User Manual

The table below describes the MCIMX8DXL-WEVK power supplies.

| Table 9. | MCIMX8DXL          | -WEVK | power | supplies |

|----------|--------------------|-------|-------|----------|

| 10010 01 | III O IIII/(O D/(E |       | ponor | oupphoo  |

| Power source                                                 | Manufacturer and part number | Power supply           | Description                                                                                                                                                                                                                 |

|--------------------------------------------------------------|------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| External 12 V DC<br>supply through 4-pin<br>DIN connector J1 |                              | 12V0 (12 V)            | <ul> <li>Supplies power to i.MX 8DXL processor, fan header<br/>J2, and power regulator U1</li> <li>Alternative 12 V power for V2X/Ethernet socket</li> </ul>                                                                |

| Power regulator U1                                           | NXP MFS5600<br>AMMA7ES       | SW1: 5V0_PS (5 V)      | <ul><li>Supplies LDO2 power to PMIC</li><li>Produces 5V0 supply</li></ul>                                                                                                                                                   |

|                                                              |                              | SW2: 3V3_PS (3.3<br>V) | <ul> <li>Supplies power to LEDs (D2 and D3), MUX13 (U102), PMIC loopback switches (U130 and U131), and power switches (U10, U13, U16, and U17)</li> <li>Produces 3V3_PMIC supply</li> <li>Produces 3V3_SW supply</li> </ul> |

| From 5V0_PS<br>supply                                        |                              | 5V0 (5 V)              | <ul> <li>Supplies power to LCD connector (J9) and<br/>programmable-current USB switches (U62 and U65)</li> <li>Supplies 5 V power to CAN transceiver, V2X/<br/>Ethernet socket, and audio codecs 1, 2, and 3</li> </ul>     |

| From 3V3_PS<br>supply                                        |                              | 3V3_PMIC (3.3 V)       | Supplies SW1, SW2, SW3, SW4, SW5, LDO1, and VIN power to PMIC                                                                                                                                                               |

| From 3V3_PS<br>supply through<br>power switch U4             |                              | 3V3_SW (3.3 V)         | <ul> <li>Supplies 3.3 V power to MUX8 U39</li> <li>Produces 3V3 supply</li> <li>Produces 3V3_USB supply</li> </ul>                                                                                                          |

## MCIMX8DXL-WEVK Board User Manual

| Power source                                           | Manufacturer and<br>part number | Power supply                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------|---------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                        |                                 |                                            | <ul> <li>Produces 3V3_IO supply</li> <li>One of the source power supplies for VDD_ENET0_<br/>VSEL+ supply</li> <li>One of the source power supplies for VDD_ENET0_<br/>VSEL- supply</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| From 3V3_SW<br>supply                                  |                                 | 3V3 (3.3 V)                                | <ul> <li>Supplies power to M.2 connector, EXPANDER1<br/>(U80), EXPANDER2 (U84), EXPANDER3 (U82),<br/>EXPANDER4 (U110), MUX1 (U44), MUX2 (U50),<br/>MUX3 (U49), MUX4 (U52), MUX5 (U46 and U47),<br/>MUX6 (U67), MUX7 (U34), MUX9 (U26, U29, and<br/>U31), MUX11 (U86), SWITCH1 (U75), SWITCH2<br/>(U76), voltage translators (U21, U30, U35, U36,<br/>U40, U45, U48, U51, U55, U68, and U74), inverter<br/>ICs (U38, U73, U112, U128, U136, and U137), logic<br/>gates (U72, U77, U78, U79, U81, U83, U113, and<br/>U116), configuration channel logic chips (U114 and<br/>U117), differential 2:1 switches (U70 and U71),<br/>power switch (U32), and 2:1 switch (U134)</li> <li>Supplies 3.3 V power to eMMC memory, CAN<br/>transceiver, Gigabit Ethernet PHY, V2X/Ethernet<br/>socket, and audio codecs 1, 2, and 3</li> <li>3V3 supply is filtered to produce AVDD33 power for<br/>Gigabit Ethernet PHY</li> <li>3V3 supply is filtered to produce VBUS power for<br/>programmable-current USB switches U62 and U65</li> </ul> |

| From 3V3_SW<br>supply                                  |                                 | 3V3_USB (3.3 V)                            | Supplies 3.3 V power to i.MX 8DXL USB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| From 3V3_SW<br>supply                                  |                                 | 3V3_IO (3.3 V)                             | Supplies 3.3 V power to i.MX 8DXL ENET0, uSDHC, SPI1, and PCIe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| From pin 57 of V2X/<br>ENET0 socket (J7)               |                                 | VCC_ENET_IO (3.<br>3/1.8 V)                | <ul> <li>Supplies power to voltage translators U35, U36, U37, and U40</li> <li>Supplies 3.3/1.8 V power to MUX8 U39</li> <li>Another source power supply for VDD_ENET0_VSEL+ supply</li> <li>Alternative power supply for voltage translator U30</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| From 3V3_SW<br>supply or VCC_<br>ENET_IO supply        |                                 | VDD_ENET0_VSEL<br>+ (3.3/1.8 V)            | Another source power supply for VDD_ENET0_VSEL-<br>supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| From 3V3_SW<br>supply or VDD_<br>ENET0_VSEL+<br>supply |                                 | VDD_ENET0_VSEL-<br>(3.3/1.8 V)             | <ul> <li>Supplies power to logic gates U118, U119, and U120</li> <li>Supplies another 3.3 V power to i.MX 8DXL ENET0</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Power management integrated circuit                    | NXP PPF7100<br>BVMA1ES          | SW1: PMIC_VDD_<br>MAIN (1 V at 2.5 A)      | Produces VDD_MAIN supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| (PMIC) U5                                              |                                 | SW2: PMIC_VDD_<br>MEMC (1.1 V at 2.5<br>A) | Produces VDD_MEMC supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

### Table 9. MCIMX8DXL-WEVK power supplies...continued

## MCIMX8DXL-WEVK Board User Manual

| Power source                     | Manufacturer and<br>part number | Power supply                                   | Description                                                                                                                                                                                                                                                                                       |

|----------------------------------|---------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  |                                 | SW3: PMIC_VDD_<br>V2X_VTT (1.8 V at<br>2.5 A)  | Produces 1V8_6 supply                                                                                                                                                                                                                                                                             |

|                                  |                                 | SW4: PMIC_VDD_<br>DDRIO (1.1 V at 2.5<br>A)    | <ul><li>Produces VDD_DDR_VDDQ supply</li><li>Produces DDR_VDD2 supply</li></ul>                                                                                                                                                                                                                   |

|                                  |                                 | SW5: PMIC_VDD_1<br>V8 (1.8 V at 2.5 A)         | <ul> <li>Produces DDR_VDD1 supply</li> <li>Produces 1V8_1 supply</li> <li>Produces 1V8_2 supply</li> <li>Produces 1V8_3 supply</li> <li>Produces 1V8_4 supply</li> <li>Produces 1V8_5 supply</li> <li>Produces 1V8 supply</li> </ul>                                                              |

|                                  |                                 | LDO1: PMIC_VDD_<br>ANA (1.8 V at 0.4 A)        | Produces VDD_ANA supply                                                                                                                                                                                                                                                                           |

|                                  |                                 | LDO2: PMIC_VDD_<br>SD (3.3/1.8 V at 0.4<br>A)  | Produces VDD_ENET0 supply                                                                                                                                                                                                                                                                         |

|                                  |                                 | VSNVS1: PMIC_<br>VDD_SNVS1 (3 V at<br>10 mA)   | Produces VDD_SNVS1 supply                                                                                                                                                                                                                                                                         |

|                                  |                                 | VSNVS2: PMIC_<br>VDD_SNVS2 (1.8 V<br>at 10 mA) | Supplies power to voltage translators (U125 and U132), logic gates (U106 and U108), buffer / line driver (U107), and inverter IC (U109)                                                                                                                                                           |

| From PMIC_VDD_<br>MAIN supply    |                                 | VDD_MAIN (1 V at<br>2.5 A)                     | Supplies power to VDD_MAIN power domain of the i.MX 8DXL processor                                                                                                                                                                                                                                |

| From PMIC_VDD_<br>MEMC supply    |                                 | VDD_MEMC (1.1 V<br>at 2.5 A)                   | Supplies power to VDD_MEMC power domain of the i.MX 8DXL processor                                                                                                                                                                                                                                |

| From PMIC_VDD_<br>V2X_VTT supply |                                 | 1V8_6 (1.8 V at 2.5<br>A)                      | Alternative 1.8 V power for V2X/Ethernet socket                                                                                                                                                                                                                                                   |

| From PMIC_VDD_<br>DDRIO supply   |                                 | VDD_DDR_VDDQ<br>(1.1 V at 2.5 A)               | Supplies power to VDD_DDR_VDDQ power domain of the i.MX 8DXL processor                                                                                                                                                                                                                            |

| From PMIC_VDD_<br>DDRIO supply   |                                 | DDR_VDD2 (1.1 V<br>at 2.5 A)                   | Supplies VDD2 and VDDQ power to LPDDR4 memory                                                                                                                                                                                                                                                     |

| From PMIC_VDD_1<br>V8 supply     |                                 | DDR_VDD1 (1.8 V<br>at 2.5 A)                   | Supplies VDD1 power to LPDDR4 memory                                                                                                                                                                                                                                                              |

| From PMIC_VDD_1<br>V8 supply     |                                 | 1V8_1 (1.8 V at 2.5<br>A)                      | <ul> <li>Supplies power to i.MX 8DXL ENET1, UART0/<br/>LCDIF, UART1, SPI3, and MCLK</li> <li>Supplies power to VDD_DDR_PLL power domain of<br/>the i.MX 8DXL processor</li> <li>Alternative supply for VDD_ANA0_1P8 and VDD_<br/>ANA1_1P8 power domains of the i.MX 8DXL<br/>processor</li> </ul> |

| From PMIC_VDD_1<br>V8 supply     |                                 | 1V8_2 (1.8 V at 2.5<br>A)                      | <ul> <li>Supplies power to octal flash memory and i.MX<br/>8DXL QSPI and eMMC</li> <li>Supplies 1.8 V power to eMMC memory</li> </ul>                                                                                                                                                             |

### Table 9. MCIMX8DXL-WEVK power supplies...continued

## MCIMX8DXL-WEVK Board User Manual

| Power source                                                      | Manufacturer and<br>part number | Power supply                       | Description                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------|---------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| From PMIC_VDD_1<br>V8 supply                                      |                                 | 1V8_3 (1.8 V at 2.5<br>A)          | Supplies power to i.MX 8DXL SNVS, FlexCAN, UART0, and SPI0                                                                                                                                                                                                                                                                                                                                                           |

| From PMIC_VDD_1<br>V8 supply                                      |                                 | 1V8_4 (1.8 V at 2.5<br>A)          | Supplies 1.8 V power to i.MX 8DXL USB                                                                                                                                                                                                                                                                                                                                                                                |

| From PMIC_VDD_1<br>V8 supply                                      |                                 | 1V8_5 (1.8 V at 2.5<br>A)          | Supplies 1.8 V power to i.MX 8DXL PCIe                                                                                                                                                                                                                                                                                                                                                                               |

| From PMIC_VDD_1<br>V8 supply                                      |                                 | 1V8 (1.8 V at 2.5 A)               | <ul> <li>Supplies power to PCIe clock generator (U69), clock buffer (U57), logic gates (U121 and U126), voltage translator/buffer (U85), and voltage translators (U21, U37, U45, U48, U51, U53, U55, U58, U60, U68, U74, and U96)</li> <li>Supplies 1.8 V power to audio codecs 1, 2, and 3</li> </ul>                                                                                                               |