**Objective Datasheet**

# General description

1

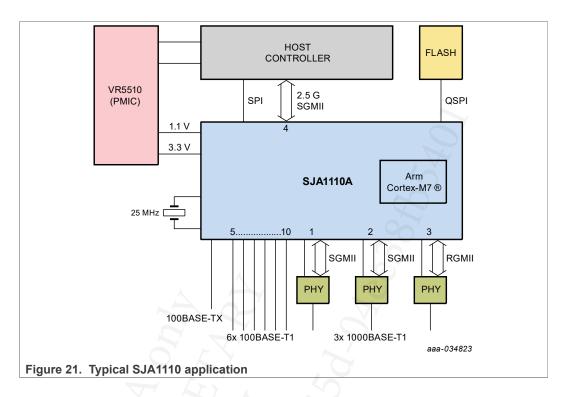

SJA1110 is a family of automotive Ethernet switches offering a rich set of security, safety and TSN capabilities.

SJA1110 devices integrate:

- Up to six IEEE 100BASE-T1 PHYs

- A single IEEE 100BASE-TX PHY

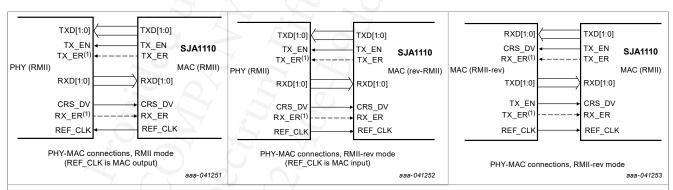

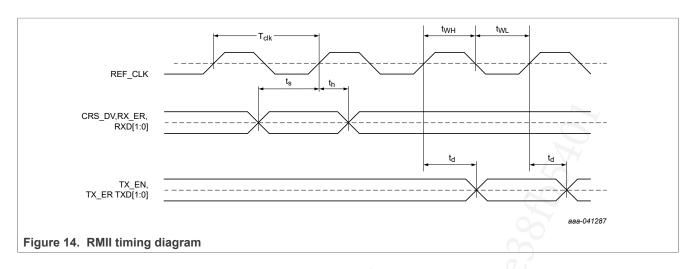

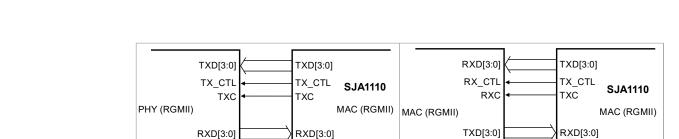

- Up to two MII/RMII/RGMII interfaces

- Up to four SGMII interfaces

- An Arm Cortex-M7 ® based host controller

IEEE Audio Video Bridging (AVB) and the latest Time-Sensitive Networking (TSN) standards are supported.

The device comes in four variants, each capable of supporting a flexible and modular ECU design for Gateway, ADAS and Infotainment applications.

Flexible boot options allow for configuration via a selection of external NVMs or via an external host controller. Advanced security features allow for a secure boot mode to authenticate firmware before execution.

Innovative features such as frame inspection with a width of up to 128 bytes and two SGMII interfaces that can operate at up to 2.5 Gbit/s enable efficient cascading and uplinking to a host controller.

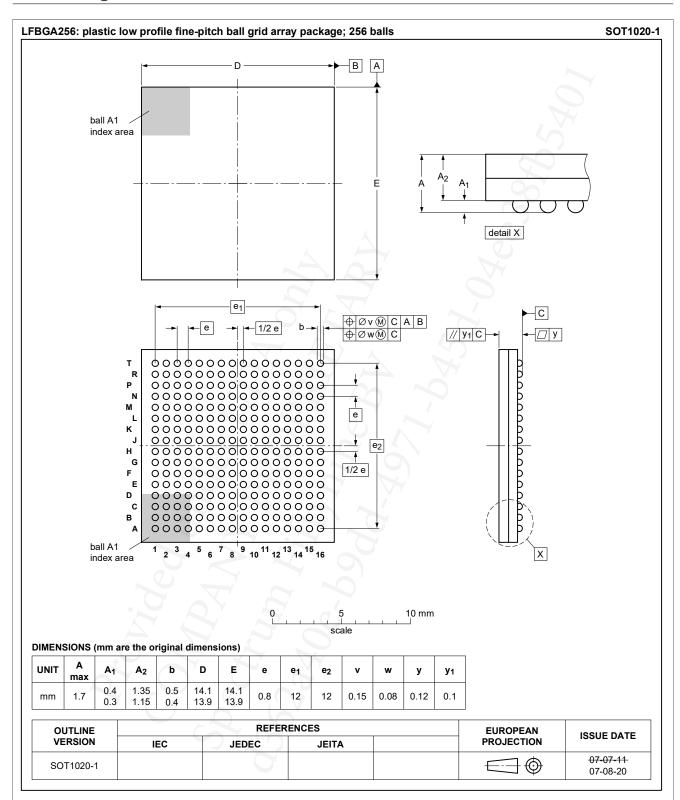

The SJA1110 is a purpose-built automotive switch that is AEC-Q100 qualified and compliant with ISO26262 ASIL B. All variants come in a 256-pin, 14 mm x 14 mm LFBGA package.

DRAFT DRAFT DRAFT

# 2 Features and benefits

#### 2.1 General

- 10-port store-and-forward architecture for switch core with integrated 100BASE-T1 and 100BASE-TX transceivers

- Integrated Arm Cortex-M7 ® processor for autonomous and secure operation

- Selectable I/O voltages (1.8 V, 2.5 V and 3.3 V) offer design flexibility

- · Small footprint

- LFBGA256 (14 mm x 14 mm) package with 0.8 mm pitch

- Maximum junction temperature: +150 °C

- Automotive Grade 2 (ambient temperature: -40 °C to +105 °C)<sup>1</sup>

- Variants A, B and C

- Automotive Grade 1 (ambient temperature: -40 °C to +125 °C)<sup>1</sup>

- Variant D<sup>2</sup>

- All variants are Grade 1 where total power dissipation does not exceed 1 W

- Automotive product qualification in accordance with AEC-Q100 Rev-H

- · ISO 26262, ASIL-B compliant

- Sleep current <100 μA

#### 2.2 Data interfaces

- Up to 10 data ports with integrated and external PHYs <sup>3</sup>

- 6x integrated 100BASE-T1 PHYs

- 1x 100BASE-TX or SGMII

- 2x MII/RMII/RGMII or SGMII

- 1x SGMII

- MII/RMII 10/100 Mbit/s: 1.8 V/2.5 V/3.3 V selectable I/O operating voltage and programmable drive strength

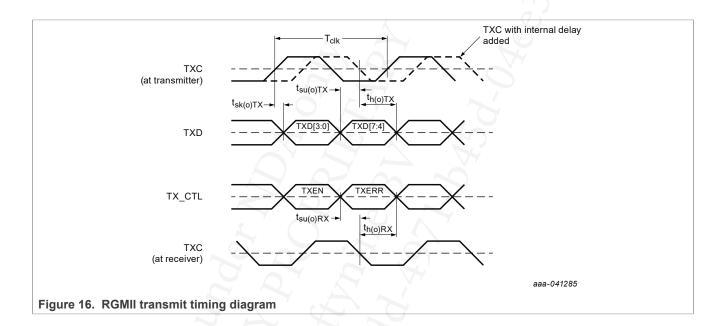

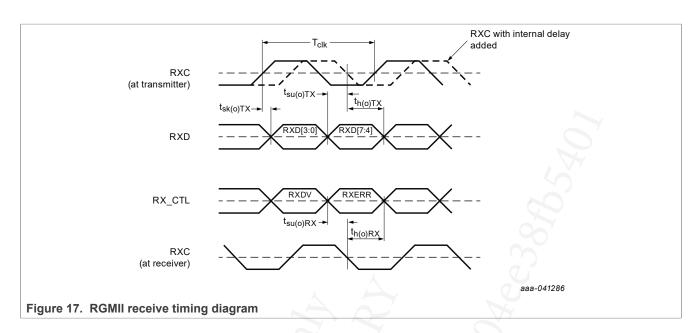

- RGMII 10/100/1000 Mbit/s; optional integrated delay (RGMII-ID), 1.8 V/2.5 V/3.3 V configurable I/O operating voltage with programmable drive strength

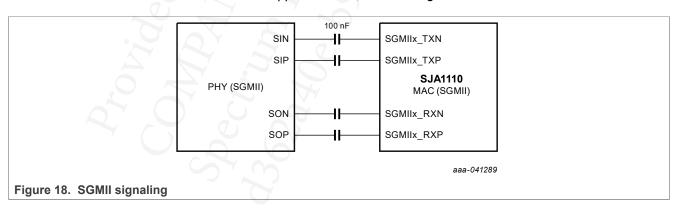

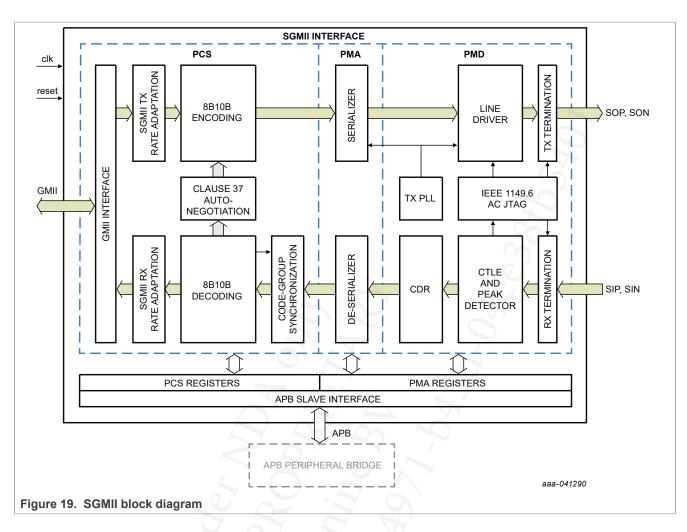

- SGMII 10/100/1000 Mbit/s or 2500 Mbit/s<sup>4</sup> operation with 3.3 V I/O supply; programmable swing

### 2.3 100BASE-T1 PHYs

- Compliant with IEEE 802.3bw-2015 (100BASE-T1)

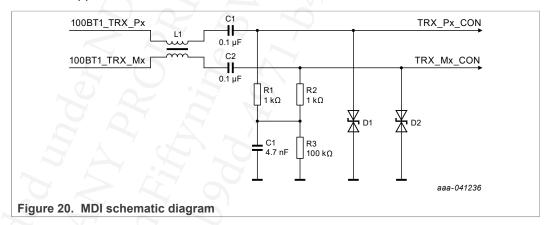

- · Fully integrated MDI pin filtering

- Remote wake-up detection and forwarding according to OPEN Alliance TC10

- Up to 15 m cable length, including 110 ns propagation delay

- Dedicated PHY enable/disable input pin to support ISO 26262

- · Local wake-up via dedicated wake pin

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved

<sup>1</sup> Automotive grade rating determined under conditions defined in JEDEC JESD51-6.

<sup>2</sup> With 1.8 V xMII supply.

<sup>3</sup> Number of interfaces depends on variant; highest number of ports (10) on variant A.

<sup>4 2500</sup> Mbit/s operation supported for two dedicated ports.

- Enhanced link diagnosis

- Diagnosis of cable errors

- Signal Quality Index

- Link training time

- Link failure and link losses

- ESD robustness

- MDI balls protected against ±4 kV HBM; ±2 kV HBM and 500 V CDM at any ball

- MDI connector pins protected against ±6 kV IEC 61000-4-2 and ±8 kV(contact)/ ±15 kV(air) ISO 10605 with standard MDI circuitry

- Link robustness for powered ESD Class-A1 up to 3 kV; prevents unwanted wake-up according to ESD Class-A3 up to 3 kV

#### 2.4 L2 switch features

- IEEE802.3 and 802.1D compliant

- 256 kB frame buffer

- 1024 collision-free L2 lookup based on TCAM

- · 2 kB frame length handling

- IEEE 802.1Q defined tag support

- 4096 VLANs

- · Egress tagging/untagging on a per-VLAN basis per port

- QoS handling based on L2 (PCP bits) or L3 (IP TOS)

- · Per-port policing based on PCP

- · Per-port policing for multicast and broadcast traffic

- Per-port priority remapping and 8 configurable egress queues per port

- · QinQ tag (double tag) support

- Configurable shapers (leaky bucket/credit based) and schedulers (strict priority, Weighted Round Robin (WRR), weighted fair queuing) per egress queue

- Frame replication, retagging and mirroring of traffic for enhanced diagnostics

- Extensive support for statistic counters, status flags and interrupt generation

### 2.5 Advanced traffic engineering features

- Additional configurable TCAM-based filter (bytes x depth): 16 x 1024/32 x 512/64 x 256/128 x128 for look-up and filtering capability up to L5 header

- Up to 1024 streams, each with IEEE 802.1Qci based policing capabilities

- Up to 4096 policers for L2 based streams (DA/SA/VID)

- Replication of frames toward a host and simultaneous forwarding for real-time traffic monitoring

- · Timestamp capturing on filtered frames

- Support for static routing for L2 header replacement (SA or DA fields)

#### 2.6 AVB and TSN features

- Hardware support for IEEE 802.1AS-2020 and IEEE 802.1Q AVB handling

- · Ingress and egress timestamping per port

- · Transit time in device measurement

- Credit-based shapers available according to IEEE 802.1Qav; shapers can be freely allocated to any priority queue on a per port basis

SJA1110

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved

- Support for SR Class A, Class B and Class C traffic

- · Free run and rate-corrected clock counters

- · Software configurable PTP/media clock output

- IEEE 1588v2 E2E transparent operation in hardware

- IEEE 802.1Qci Per-stream Filtering and Policing (PSFP)

- Up to 1024 streams based on configurable TCAM lookup

- Up to 1024 Two Rate, Three Color (2R3C) policers with up to 8 input gates

- IEEE 802.1Qbv enhancements for scheduled traffic (time aware shaper)

- Up to 256 schedule entries with 25 byte-time granularity for gate events

- IEEE 802.1CB frame replication and elimination for reliability

- Stream selection based on either L2 TCAM or extended TCAM lookup

- Operation as a talker end system, relay system or listener end system for every stream

- Up to 64 streams for stream generation and recovery with L2 header modification

### 2.7 Integrated microcontroller features

- Arm Cortex-M7 ® core @ 200 MHz

- 512 kB integrated SRAM as Instruction Tightly Coupled Memory (ITCM)

- 256 kB integrated SRAM as Data Tightly Coupled Memory (DTCM)

- Double-precision floating-point unit

- Memory Protection Unit

- Boot time of less than 100 ms with a 512 kB firmware with authentication<sup>5</sup>

- · Configurable boot options: from NVM (Flash/EEPROM) or external host

- Peripherals

- SW Watchdog

- 16-channel eDMA

- 4-channel low-power interrupt timer (LPIT)

- Cryptographic Acceleration and Assurance Module (CAAM)

- Communication peripherals

- 1x 100 Mbit/s internal Ethernet MAC to switch core

- 1x QSPI for external flash (quad lane or single lane) or serial EEPROM (single lane) for firmware and device configuration

- 1x SPI for communication with peripherals (e.g. SBC)

- 1x SPI for communication from external host

- 1x SMI output for controlling external PHYs

#### 2.8 External host interface

- SPI host interface to external microcontroller (direct register access to switch and PHY cores or proxied through internal microcontroller) for operation with a trusted host or when the integrated microcontroller is not used

- Access point SMI slave for configuration of internal 100BASE-T1 PHYs

- Separate reset inputs for the entire device and for the core only to enable Wake/Sleep operation

- · Interrupt output

5 Using QSPI at 25 MHz.

# 2.9 Safety features

- Fail-safe shutdown inputs for integrated 100BASE-T1 PHYs

- Integrated system integrity unit monitoring health of device with an error indication output

- · Memory with ECC

- Temperature sensors

# 2.10 Security features

- · Ethernet security

- IEEE 802.1X support for setting port reachability and disabling address learning

- Extensive filtering rules for frame forwarding retagging/tunneling/double tagging

- Address learning space can be configured for static and learned addresses

- Enhanced support for address learning restrictions for security

- Ingress rate-limiting on a per-port basis for unicast/multicast and broadcast traffic

- Broadcast storm protection

- · Microcontroller security

- Support for secure boot based on RSASSA-PSS 2048 and SHA-256 asymmetric signature verification

- Firmware update via internal controller or external host

- Firmware and key versioning for rollback prevention

- Option to boot from an NVM (flash over QSPI, EEPROM over SPI) or from an external host controller via SPI

#### 2.11 Clocks

- · 25 MHz oscillator or clock reference input

- Four 25 MHz reference clock outputs

- · Software configurable PTP clock output

# 2.12 Manufacturing and debug

- IEEE1149.1 and 1149.6 compliant JTAG and boundary scan interface

- · Serial wire debug interface multiplexed with JTAG for software debugging

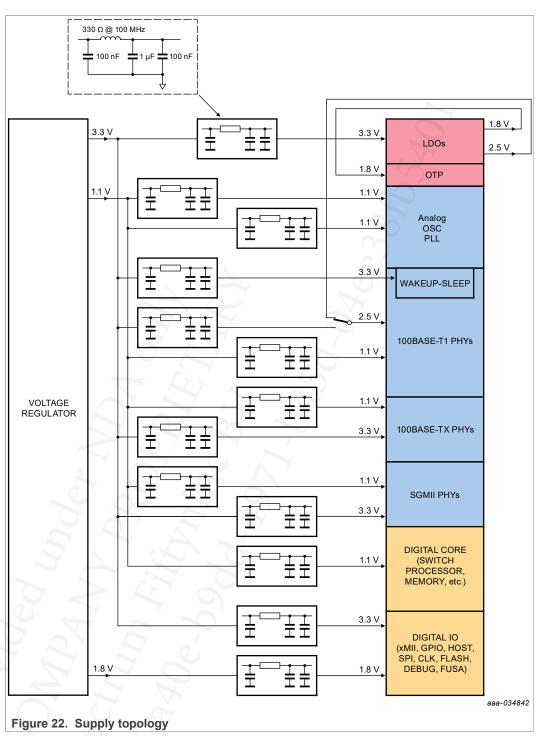

#### 2.13 Supply voltage

- 3.3 V and 1.1 V supply

- · 2.5 V supply: external or internal from integrated regulator

- Selectable IO voltage (1.8 V, 2.5 V, 3.3 V)

### 2.14 Other features

- 16 GPIOs

- Sync input/output

- Pinstrap options for boot configuration

- · Pinstrap options for PHY configuration

### **NXP Semiconductors**

#### **Product family overview** 3

Table 1. Feature overview of the SJA1110X family

| Variant  | Total No. of Ports <sup>[1]</sup> | 100BASE-T1 PHYs | 100BASE-TX PHYs | 10/100/1000 SGMII | 10/100/1000/2500 SGMII | MI/RMII/RGMII | AEC-Q100 Temp Grade <sup>[2]</sup> | LFBGA256 14 x 14 mm² |

|----------|-----------------------------------|-----------------|-----------------|-------------------|------------------------|---------------|------------------------------------|----------------------|

| SJA1110A | 10                                | 6               | 1               | 2                 | 2                      | 2             | 2                                  | •                    |

| SJA1110B | 9                                 | 5               | 1               | 0                 | 2                      | 2             | 2                                  | •                    |

| SJA1110C | 7                                 | 3               | 1               | 0                 | 1                      | 2             | 2                                  | •                    |

| SJA1110D | 7                                 | 3               | 0               | 2                 | 2                      | 2             | 1 <sup>[3]</sup>                   | •                    |

- Note that some interfaces are multiplexed and cannot be used at the same time.

- All variants are Grade 1 when total dissipation does not exceed 1 W.

- With 1.8 V xMII supply

DRAFT DRAFT DRAFT

DRAFT DRAFT DRAFT SJA11110 AFT DRAFT

# **NXP Semiconductors**

# **Ordering information**

Table 2. Ordering information

| Type number | Package  |                                                                   |           |  |  |  |  |

|-------------|----------|-------------------------------------------------------------------|-----------|--|--|--|--|

|             | Name     | Description                                                       | Version   |  |  |  |  |

| SJA1110AEL  | LFBGA256 | plastic low profile fine-pitch ball grid array package; 256 balls | SOT1020-3 |  |  |  |  |

| SJA1110BEL  |          |                                                                   |           |  |  |  |  |

| SJA1110CEL  |          | 40                                                                |           |  |  |  |  |

| SJA1110DEL  |          | 60                                                                |           |  |  |  |  |

DRAFT DRAFT DRAFT

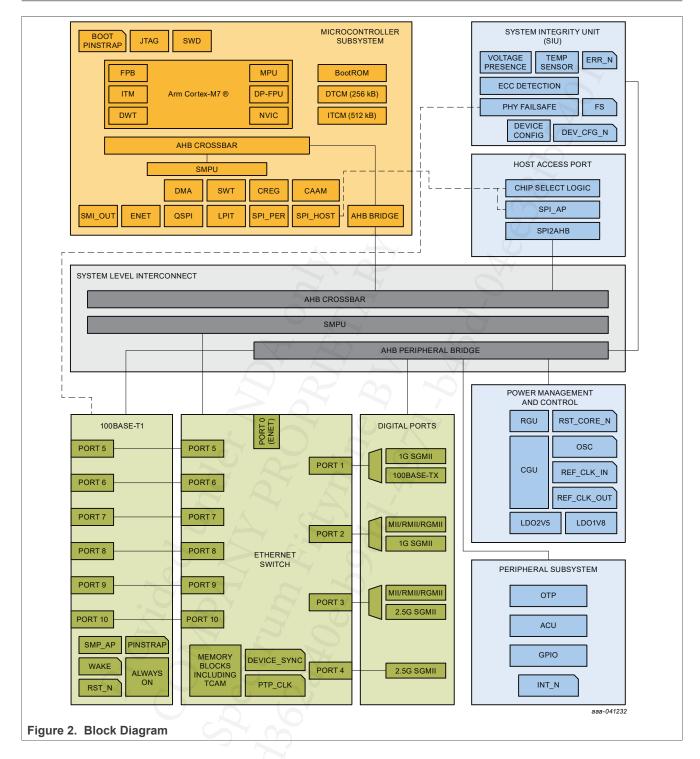

# 5 Block diagram

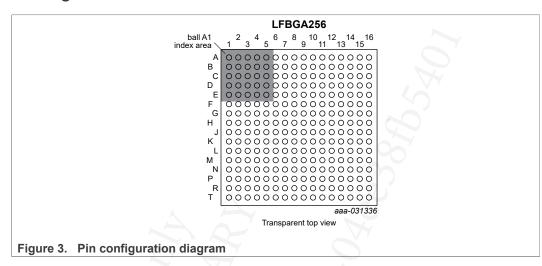

# 6 Pinning information

# 6.1 Pinning

Table 3. Pin description

Pinning is for SJA1110A variant; some ports might be disabled depending on the variant.

|   | 1                         | 2               | 3                      | 4                      | 5                      | 6                      | 7                      | 8                      |

|---|---------------------------|-----------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| Α | VSS                       | FSI1            | MII2_RX_DV             | MII2_RXD2              | MII2_RXD0              | MII2_TX_EN             | MII2_TXD2              | MII2_TXD0              |

| В | ERR_N                     | FSI2            | MII2_RXD3              | MII2_RXD1              | MII2_RX_CLK            | MII2_TX_CLK            | MII2_TXD3              | MII2_TXD1              |

| С | OSC_IN                    | VDDA11_OSC      | VDDIO_FUSA             | VSSIO_MII2             | VDDIO_MII2             | VSSIO_MII2             | VDDIO_MII2             | GPIO1                  |

| D | OSC_OUT                   | VSSA_OSC        | VSS                    | SPI_HAP_<br>SDO        | INT_N                  | MII2_RX_ER             | MII2_TX_ER             | GPIO2                  |

| E | VSSA_PLL                  | VDDA11_PLL      | VDDIO_HOST             | SPI_HAP_<br>SCLK       | SPI_HAP_SDI            | VDD11_CORE             | GPIO0                  | GPIO3                  |

| F | VDDIO_SYNC                | DEVICE_<br>SYNC | VSS                    | SPI_HAP_<br>SS0_N      | SPI_HAP_<br>SS1_N      | VDD11_CORE             | VSS                    | VDDIO_GPIO1            |

| G | VDDIO_<br>REFCLK_<br>OUT1 | REFCLK_<br>OUT1 | VSSIO_<br>REFCLK12     | RST_CORE_N             | DEVICE_<br>CFG_N       | VSS                    | VSS                    | VSS                    |

| Н | VDDIO_<br>REFCLK_<br>OUT2 | REFCLK_<br>OUT2 | VDDA18_<br>OTP_IN      | VDDA18_<br>OTP_OUT     | VDDA25_<br>VREG_OUT    | VDDA33_<br>VREG_IN     | VSS                    | VSS                    |

| J | VSS                       | VSS             | VSS                    | GPIO8                  | GPIO10                 | VDDIO_GPIO3            | VSS                    | VSS                    |

| K | SGMII4_TXP                | SGMII4_TXN      | VDDA33_<br>SGMII4      | GPIO9                  | GPIO11                 | VDD11_CORE             | VSS                    | VSS                    |

| L | SGMII4_RXP                | SGMII4_RXN      | VDDA11_<br>SGMII4      | GPIO12                 | GPIO14                 | VDD11_CORE             | VSS                    | VSS                    |

| M | VSS                       | VSS             | VSS                    | GPIO13                 | GPIO15                 | VDDIO_GPIO4            | VDDIO_HOST             | VDD33_AO               |

| N | SGMII2_TXP                | SGMII2_TXN      | VDDA11_<br>SGMII2      | WAKE_IN_<br>OUT        | LOC_WAKE_<br>IN        | SMI_AP_MDC             | BOOT_<br>OPTION0       | PHY_ADDR3              |

| Р | SGMII2_RXP                | SGMII2_RXN      | VDDA33_<br>SGMII2      | RST_N                  | INH                    | SMI_AP_<br>MDIO        | BOOT_<br>OPTION1       | VDDA25_RX_<br>100BT1   |

| R | VSS                       | VSS             | VSSA25_<br>100BT1_TXM5 | VDDA25_<br>100BT1_TXM5 | VSSA25_<br>100BT1_TXM6 | VDDA25_<br>100BT1_TXM6 | VSSA25_<br>100BT1_TXM7 | VDDA25_<br>100BT1_TXM7 |

DRAFT DRAFT DRAFT

# SJA11110 AFT DRAFT

# **NXP Semiconductors**

Table 3. Pin description...continued

Pinning is for SJA1110A variant; some ports might be disabled depending on the variant.

|   | 1                      | 2                      | 3                      | 4                      | 5                           | 6                           | 7                 | 8                         |

|---|------------------------|------------------------|------------------------|------------------------|-----------------------------|-----------------------------|-------------------|---------------------------|

| Т | VSS                    | VSS                    | 100BT1_TRX_<br>P5      | 100BT1_TRX_<br>M5      | 100BT1_TRX_<br>P6           | 100BT1_TRX_<br>M6           | 100BT1_TRX_<br>P7 | 100BT1_TRX_<br>M7         |

|   | Ĭ                      | )                      | 1                      |                        |                             | 1                           |                   |                           |

|   | 9                      | 10                     | 11                     | 12                     | 13                          | 14                          | 15                | 16                        |

| Α | MII3_RX_DV             | MII3_RXD2              | MII3_RXD0              | MII3_TX_EN             | MII3_TXD2                   | MII3_TXD0                   | VSS               | VSS                       |

| В | MII3_RXD3              | MII3_RXD1              | MII3_RX_CLK            | MII3_TX_CLK            | MII3_TXD3                   | MII3_TXD1                   | PTP_CLK           | VDDIO_PTP_<br>CLK         |

| С | GPIO4                  | VDDIO_MII3             | VSSIO_MII3             | VDDIO_MII3             | VSSIO_MII3                  | VDDIO_SMI_<br>OUT           | SMI_OUT_<br>MDC   | SMI_OUT_<br>MDIO          |

| D | GPIO5                  | MII3_RX_ER             | MII3_TX_ER             | QSPI_SS_N              | QSPI_IO2                    | VSS                         | REFCLK_<br>OUT3   | VDDIO_<br>REFCLK_<br>OUT3 |

| E | GPIO6                  | GPI07                  | VDD11_CORE             | QSPI_IO0               | QSPI_IO1                    | VSSIO_<br>REFCLK34          | REFCLK_<br>OUT4   | VDDIO_<br>REFCLK_<br>OUT4 |

| F | VDDIO_GPIO2            | VSS                    | VDD11_CORE             | QSPI_SCLK              | QSPI_IO3                    | VSSA11_<br>100BTX           | VSSA11_<br>100BTX | VSSA11_<br>100BTX         |

| G | VSS                    | VSS                    | VDDIO_<br>FLASH        | SPI_PER_<br>MOSI       | SPI_PER_<br>MISO            | VDDA33_<br>100BTX           | 100BTX_RX_P       | 100BTX_RX_<br>M           |

| Н | VSS                    | VSS                    | VDDIO_SPI_<br>PER      | SPI_PER_<br>SCLK       | SPI_PER_<br>SS0_N           | VDDA11_<br>100BTX           | 100BTX_TX_P       | 100BTX_TX_<br>M           |

| J | VSS                    | VSS                    | VDDIO_<br>DEBUG        | тск                    | SPI_PER_<br>SS1_N           | VSSA11_<br>100BTX           | 100BTX_<br>EXTRES | VSSA11_<br>100BTX         |

| K | VSS                    | VSS                    | VDD11_CORE             | TDI                    | TMS                         | VDDA33_<br>SGMII3           | SGMII3_RXN        | SGMII3_RXP                |

| L | VSSA11_<br>100BT1      | VSS                    | VDD11_CORE             | TDO                    | TRST_N                      | VDDA11_<br>SGMII3           | SGMII3_TXN        | SGMII3_TXP                |

| M | VDDA11_<br>100BT1      | PHY_ADDR2              | VDD11_CORE             | PHY_M_S10              | PHY_M_S9                    | VSS                         | VSS               | VSS                       |

| N | PHY_ADDR0              | PHY_ADDR1              | PHY_M_S5               | PHY_AUTO_<br>MODE      | PHY_M_S7                    | VDDA11_<br>SGMII1           | SGMII1_RXN        | SGMII1_RXP                |

| Р | VSSA25_<br>100BT1_RXM  | PHY_ADDR4              | PHY_M_S6               | PHY_AUTO_<br>POL_DET   | PHY_M_S8                    | VDDA33_<br>SGMII1           | SGMII1_TXN        | SGMII1_TXP                |

| R | VSSA25_<br>100BT1_TXM8 | VDDA25_<br>100BT1_TXM8 | VSSA25_<br>100BT1_TXM9 | VDDA25_<br>100BT1_TXM9 | VSSA25_<br>100BT1_<br>TXM10 | VDDA25_<br>100BT1_<br>TXM10 | VSS               | VSS                       |

| Т | 100BT1_TRX_<br>P8      | 100BT1_TRX_<br>M8      | 100BT1_TRX_<br>P9      | 100BT1_TRX_<br>M9      | 100BT1_TRX_<br>P10          | 100BT1_TRX_<br>M10          | VSS               | VSS                       |

# 6.2 Pin description

# 6.2.1 Digital supply and ground

Table 4. Digital supply and ground

| Symbol     | Pin                                                                                                                                                                                                | Type [1] | Description                       |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------|

| VDD11_CORE | E11, E6, F11, F6, K11, K6, L11, L6, M11                                                                                                                                                            | Р        | 1.1 V digital core supply voltage |

| VSS        | A1, A15, A16, D14, D3, F10, F3, F7, G10, G6, G7, G8, G9, H10, H7, H8, H9, J1, J10, J2, J3, J7, J8, J9, K10, K7, K8, K9, L10, L7, L8, M1, M14, M15, M16, M2, M3, R1, R15, R16, R2, T1, T15, T16, T2 | Р        | digital supply ground             |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog input; AO: analog output; P: power; G: ground.

# 6.2.2 Power supply management

Table 5. Power supply management

| Symbol          | Pin | Type [1] | Description                                                                                    |

|-----------------|-----|----------|------------------------------------------------------------------------------------------------|

| INH             | P5  | 0        | inhibit output for voltage regulator control (active-HIGH, plain output (prog), low, VDD33_AO) |

| LOC_WAKE_IN     | N5  | I        | local wake input (active-HIGH, plain output (prog), low, VDD33_AO)                             |

| VDD33_AO        | M8  | Р        | 3.3 V always-on supply voltage                                                                 |

| VDDA25_VREG_OUT | H5  | AO       | 2.5 V analog regulator output voltage                                                          |

| VDDA33_VREG_IN  | H6  | P        | 3.3 V analog regulator supply voltage                                                          |

| WAKE_IN_OUT     | N4  | Ю        | wake in-out (open-drain) (active-HIGH, plain output (prog), low, VDD33_AO)                     |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AIO: analog input/output; AI: analog output; P: power; G: ground.

#### 6.2.3 Resets

Table 6. Resets

| Table 6. Itesets | able of Reserve |          |                                                                                                   |  |  |  |

|------------------|-----------------|----------|---------------------------------------------------------------------------------------------------|--|--|--|

| Symbol           | Pin             | Type [1] | Description                                                                                       |  |  |  |

| RST_CORE_N       | G4              |          | digital core reset (not including always-on domain) (active-LOW, pull-up (prog), low, VDDIO_HOST) |  |  |  |

| RST_N            | P4              |          | device reset (including always-on domain) (active-LOW, pull-up (prog), low, VDD33_AO)             |  |  |  |

[1] IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog output; P: power; G: ground.

#### 6.2.4 SGMII

#### 6.2.4.1 SGMII Port 1

#### Table 7. SGMII Port 1

| Symbol        | Pin | Type [1] | Description                                   |

|---------------|-----|----------|-----------------------------------------------|

| SGMII1_RXN    | N15 | Al       | SGMII negative receiver terminal              |

| SGMII1_RXP    | N16 | Al       | SGMII positive receiver terminal              |

| SGMII1_TXN    | P15 | AO       | SGMII negative transmit terminal              |

| SGMII1_TXP    | P16 | AO       | SGMII positive transmit terminal              |

| VDDA11_SGMII1 | N14 | Р        | 1.1 V SGMII transceiver analog supply voltage |

| VDDA33_SGMII1 | P14 | Р        | 3.3 V SGMII transceiver analog supply voltage |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog input; AO: analog output; P: power; G: ground.

#### 6.2.4.2 SGMII Port 2

#### Table 8. SGMII Port 2

| Symbol        | Pin | Type [1] | Description                                   |

|---------------|-----|----------|-----------------------------------------------|

| SGMII2_RXN    | P2  | Al       | SGMII negative receiver terminal              |

| SGMII2_RXP    | P1  | Al       | SGMII positive receiver terminal              |

| SGMII2_TXN    | N2  | AO       | SGMII negative transmit terminal              |

| SGMII2_TXP    | N1  | AO       | SGMII positive transmit terminal              |

| VDDA11_SGMII2 | N3  | Р        | 1.1 V SGMII transceiver analog supply voltage |

| VDDA33_SGMII2 | P3  | Р        | 3.3 V SGMII transceiver analog supply voltage |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AIO: analog input/output; AI: analog input; AO: analog output; P: power; G: ground.

# 6.2.4.3 SGMII Port 3

Table 9. SGMII Port 3

| Symbol        | Pin | Type [1] | Description                                   |

|---------------|-----|----------|-----------------------------------------------|

| SGMII3_RXN    | K15 | Al       | SGMII negative receiver terminal              |

| SGMII3_RXP    | K16 | Al       | SGMII positive receiver terminal              |

| SGMII3_TXN    | L15 | AO       | SGMII negative transmit terminal              |

| SGMII3_TXP    | L16 | AO       | SGMII positive transmit terminal              |

| VDDA11_SGMII3 | L14 | P        | 1.1 V SGMII transceiver analog supply voltage |

| VDDA33_SGMII3 | K14 | Р        | 3.3 V SGMII transceiver analog supply voltage |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog input; AO: analog output; P: power; G: ground.

#### 6.2.4.4 SGMII Port 4

#### Table 10. SGMII Port 4

| Symbol     | Pin | Type [1] | Description                      |

|------------|-----|----------|----------------------------------|

| SGMII4_RXN | L2  | Al       | SGMII negative receiver terminal |

SJA1110

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

Table 10. SGMII Port 4...continued

| Symbol        | Pin | Type [1] | Description                                   |

|---------------|-----|----------|-----------------------------------------------|

| SGMII4_RXP    | L1  | Al       | SGMII positive receiver terminal              |

| SGMII4_TXN    | K2  | AO       | SGMII negative transmit terminal              |

| SGMII4_TXP    | K1  | AO       | SGMII positive transmit terminal              |

| VDDA11_SGMII4 | L3  | Р        | 1.1 V SGMII transceiver analog supply voltage |

| VDDA33_SGMII4 | K3  | Р        | 3.3 V SGMII transceiver analog supply voltage |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AIO: analog input/output; AI: analog input; AO: analog output; P: power; G: ground.

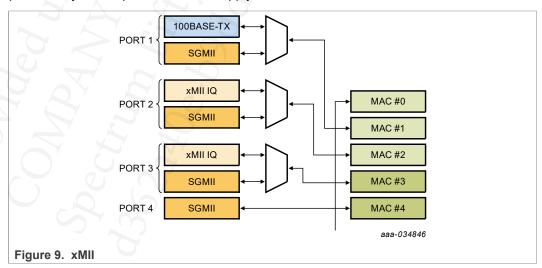

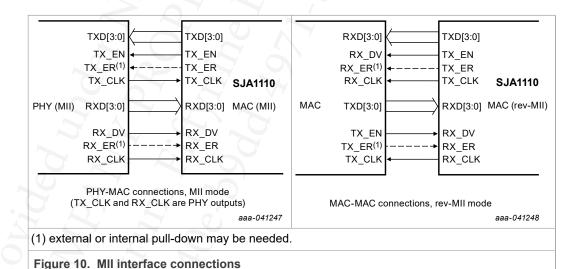

#### 6.2.5 xMII

### 6.2.5.1 xMII Port 2

Table 11. xMII Port 2

| Symbol      | Pin | Type [1] | Description                                                                                                                                                                                                                             |

|-------------|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MII2_RXD0   | A5  | I        | MII/RMII/RGMII interface receive data input, bit 0 (active-HIGH, plain input (prog), high, VDDIO_MII2)                                                                                                                                  |

| MII2_RXD1   | B4  | I        | MII/RMII/RGMII interface receive data input, bit 1 (active-HIGH, plain input (prog), high, VDDIO_MII2)                                                                                                                                  |

| MII2_RXD2   | A4  | I        | MII/RGMII interface receive data input, bit 2 (active-HIGH, plain input (prog), high, VDDIO_MII2)                                                                                                                                       |

| MII2_RXD3   | В3  | I        | MII/RGMII interface receive data input, bit 3 (active-HIGH, plain input (prog), high, VDDIO_MII2)                                                                                                                                       |

| MII2_RX_CLK | B5  | Ю        | RX_CLK: MII interface receive clock (also configurable as output) REF_CLK: RMII interface reference clock (also configurable as input) RXC: RGMII interface receive clock (active-HIGH, plain input (prog), high (prog), VDDIO_MII2)    |

| MII2_RX_DV  | A3  | 900      | RX_DV: MII interface receive data valid input CRS_DV: RMII interface carrier sense/data valid input RX_CTL: RGMII interface receive control input (active-HIGH, plain input (prog), high, VDDIO_MII2)                                   |

| MII2_RX_ER  | D6  |          | MII/RMII interface receive error input (active-HIGH, plain input (prog), high, VDDIO_MII2)                                                                                                                                              |

| MII2_TXD0   | A8  | 0        | MII/RMII/RGMII interface transmit data output, bit 0 (active-HIGH, plain output (prog), fast (prog), VDDIO_MII2)                                                                                                                        |

| MII2_TXD1   | B8  | 0        | MII/RMII/RGMII interface transmit data output, bit 1 (active-HIGH, plain output (prog), fast (prog), VDDIO_MII2)                                                                                                                        |

| MII2_TXD2   | A7  | 0        | MII/RGMII interface transmit data output, bit 2 (active-HIGH, plain output (prog), fast (prog), VDDIO_MII2)                                                                                                                             |

| MII2_TXD3   | B7  | 0        | MII/RGMII interface transmit data output, bit 3 (active-HIGH, plain output (prog), fast (prog), VDDIO_MII2)                                                                                                                             |

| MII2_TX_CLK | B6  | Ю        | TX_CLK: MII interface transmit clock (also configurable as output) REF_CLK: RMII interface reference clock (also configurable as input) TXC: RGMII interface transmit clock (active-HIGH, plain output (prog), fast (prog), VDDIO_MII2) |

Table 11. xMII Port 2...continued

| Symbol     | Pin    | Type [1] | Description                                                                                                                                           |  |  |  |  |

|------------|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MII2_TX_EN | A6     | 0        | TX_EN: MII/RMII interface transmit enable output TX_CTL: RGMII interface transmit control output (active-HIGH, plain output (fast (prog), VDDIO_MII2) |  |  |  |  |

| MII2_TX_ER | D7     | 0        | Port 2 MII/RMII interface transmit coding error output (active-HIGH, plain output (prog), fast (prog), VDDIO_MII2)                                    |  |  |  |  |

| VDDIO_MII2 | C5, C7 | Р        | MII/RMII/RGMII I/O supply voltage port 2 (1.8 V, 2.5 V, 3.3 V)                                                                                        |  |  |  |  |

| VSSIO_MII2 | C4, C6 | Р        | /III2 supply ground                                                                                                                                   |  |  |  |  |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog input; AO: analog output; P: power; G: ground.

#### 6.2.5.2 xMII Port 3

Table 12. xMII Port 3

| Symbol      | Pin | Type [1] | Description                                                                                                                                                                                                                             |

|-------------|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MII3_RXD0   | A11 | I        | MII/RMII/RGMII interface receive data input, bit 0 (active-HIGH, plain input (prog), high, VDDIO_MII3)                                                                                                                                  |

| MII3_RXD1   | B10 | I        | MII/RMII/RGMII interface receive data input, bit 1 (active-HIGH, plain input (prog), high, VDDIO_MII3)                                                                                                                                  |

| MII3_RXD2   | A10 | I        | MII/RGMII interface receive data input, bit 2 (active-HIGH, plain input (prog), high, VDDIO_MII3)                                                                                                                                       |

| MII3_RXD3   | В9  | I        | MII/RGMII interface receive data input, bit 3 (active-HIGH, plain input (prog), high, VDDIO_MII3)                                                                                                                                       |

| MII3_RX_CLK | B11 | Ю        | RX_CLK: MII interface receive clock (also configurable as output) REF_CLK: RMII interface reference clock (also configurable as input) RXC: RGMII interface receive clock (active-HIGH, plain input (prog), fast (prog), VDDIO_MII3)    |

| MII3_RX_DV  | A9  | 400      | RX_DV: MII interface receive data valid input CRS_DV: RMII interface carrier sense/data valid input RX_CTL: RGMII interface receive control input (active-HIGH, plain input (prog), high, VDDIO_MII3)                                   |

| MII3_RX_ER  | D10 |          | MII/RMII interface receive error input (active-HIGH, plain input (prog), high, VDDIO_MII3)                                                                                                                                              |

| MII3_TXD0   | A14 | 0        | MII/RMII/RGMII interface transmit data output, bit 0 (active-HIGH, plain output (prog), fast (prog), VDDIO_MII3)                                                                                                                        |

| MII3_TXD1   | B14 | 0        | MII/RMII/RGMII interface transmit data output, bit 1 (active-HIGH, plain output (prog), fast (prog), VDDIO_MII3)                                                                                                                        |

| MII3_TXD2   | A13 | 0        | MII/RGMII interface transmit data output, bit 2 (active-HIGH, plain output (prog), fast (prog), VDDIO_MII3)                                                                                                                             |

| MII3_TXD3   | B13 | 0        | MII/RGMII interface transmit data output, bit 3 (active-HIGH, plain output (prog), fast (prog), VDDIO_MII3)                                                                                                                             |

| MII3_TX_CLK | B12 | Ю        | TX_CLK: MII interface transmit clock (also configurable as output) REF_CLK: RMII interface reference clock (also configurable as input) TXC: RGMII interface transmit clock (active-HIGH, plain output (prog), fast (prog), VDDIO_MII3) |

Table 12. xMII Port 3...continued

| Table 12. XIMIT Of SContinued |          |          |                                                                                                                                                             |  |  |  |

|-------------------------------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol                        | Pin      | Type [1] | Description                                                                                                                                                 |  |  |  |

| MII3_TX_EN                    | A12      | 0        | TX_EN: MII/RMII interface transmit enable output TX_CTL: RGMII interface transmit control output (active-HIGH, plain output (prog) fast (prog), VDDIO_MII3) |  |  |  |

| MII3_TX_ER                    | D11      | 0        | MII/RMII interface transmit coding error output (active-HIGH, plain output (prog), fast (prog), VDDIO_MII3)                                                 |  |  |  |

| VDDIO_MII3                    | C10, C12 | Р        | MII/RMII/RGMII I/O supply voltage port 3 (1.8 V, 2.5 V, 3.3 V)                                                                                              |  |  |  |

| VSSIO_MII3                    | C11, C13 | Р        | MII3 supply ground                                                                                                                                          |  |  |  |

|                               |          |          |                                                                                                                                                             |  |  |  |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog input; AO: analog output; P: power; G: ground.

### 6.2.6 100BASE-T1

#### 6.2.6.1 100BASE-T1 common

Table 13. 100BASE-T1 common

| Symbol            | Pin | Type [1] | Description                                                      |

|-------------------|-----|----------|------------------------------------------------------------------|

| VDDA11_100BT1     | M9  | Р        | 1.1 V 100BASE-T1 analog supply voltage                           |

| VDDA25_RX_100BT1  | P8  | Р        | 2.5 V receiver analog supply voltage; connect to VDDA25_VREG_OUT |

| VSSA11_100BT1     | L9  | Р        | digital 100BASE-T1 supply ground                                 |

| VSSA25_100BT1_RXM | P9  | Р        | analog 100BASE-T1 receiver supply ground                         |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog input; AO: analog output; P: power; G: ground.

### 6.2.6.2 100BASE-T1 pinstrap options

Table 14. 100BASE-T1 pinstrap options

| Symbol               | Pin | Type [1] | Description                                                                    |

|----------------------|-----|----------|--------------------------------------------------------------------------------|

| PHY_ADDR0            | N9  | 1        | PHY Address Bit 0 (active-HIGH, low, VDDIO_HOST)                               |

| PHY_ADDR1            | N10 |          | PHY Address Bit 1 (active-HIGH, low, VDDIO_HOST)                               |

| PHY_ADDR2            | M10 | L /      | PHY Address Bit 2 (active-HIGH, low, VDDIO_HOST)                               |

| PHY_ADDR3            | N8  | 1        | PHY Address Bit 3 (active-HIGH, low, VDDIO_HOST)                               |

| PHY_ADDR4            | P10 | I        | PHY Address Bit 4 (active-HIGH, low, VDDIO_HOST)                               |

| PHY_AUTO_MODE        | N12 | 1        | PHY Autonomous mode selection (active-HIGH, low, VDDIO_HOST)                   |

| PHY_AUTO_POL_<br>DET | P12 |          | PHY automatic polarity detection and correction (active-HIGH, low, VDDIO_HOST) |

| PHY_M_S5             | N11 | I        | PHY 5 Master/Slave setting (active-HIGH, low, VDDIO_HOST)                      |

| PHY_M_S6             | P11 | 1        | PHY 6 Master/Slave setting (active-HIGH, low, VDDIO_HOST)                      |

| PHY_M_S7             | N13 | 1 2      | PHY 7 Master/Slave setting (active-HIGH, low, VDDIO_HOST)                      |

| PHY_M_S8             | P13 | 1        | PHY 8 Master/Slave setting (active-HIGH, low, VDDIO_HOST)                      |

| PHY_M_S9             | M13 | I        | PHY 9 Master/Slave setting (active-HIGH, low, VDDIO_HOST)                      |

| PHY_M_S10            | M12 | I        | PHY 10 Master/Slave setting (active-HIGH, low, VDDIO_HOST)                     |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AIO: analog input/output; AI: analog output; P: power; G: ground.

SJA1110

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

DRAF1

#### 6.2.6.3 100BASE-T1 Port 5

#### Table 15. 100BASE-T1 Port 5

| Symbol             | Pin | Type [1] | Description                                                         |

|--------------------|-----|----------|---------------------------------------------------------------------|

| 100BT1_TRX_M5      | T4  | AIO      | negative MDI terminal                                               |

| 100BT1_TRX_P5      | T3  | AIO      | positive MDI terminal                                               |

| VDDA25_100BT1_TXM5 | R4  | Р        | 2.5 V transmitter analog supply voltage; connect to VDDA25_VREG_OUT |

| VSSA25_100BT1_TXM5 | R3  | Р        | analog transmitter supply ground                                    |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog input; AO: analog output; P: power; G: ground.

#### 6.2.6.4 100BASE-T1 Port 6

#### Table 16. 100BASE-T1 Port 6

| Symbol             | Pin | Type [1] | Description                                                         |

|--------------------|-----|----------|---------------------------------------------------------------------|

| 100BT1_TRX_M6      | T6  | AIO      | negative MDI terminal                                               |

| 100BT1_TRX_P6      | T5  | AIO      | positive MDI terminal                                               |

| VDDA25_100BT1_TXM6 | R6  | Р        | 2.5 V transmitter analog supply voltage; connect to VDDA25_VREG_OUT |

| VSSA25_100BT1_TXM6 | R5  | Р        | analog transmitter supply ground                                    |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AIO: analog input/output; AI: analog output; P: power; G: ground.

#### 6.2.6.5 100BASE-T1 Port 7

#### Table 17. 100BASE-T1 Port 7

| Symbol             | Pin | Type [1] | Description                                                         |  |

|--------------------|-----|----------|---------------------------------------------------------------------|--|

| 100BT1_TRX_M7      | T8  | AIO      | negative MDI terminal                                               |  |

| 100BT1_TRX_P7      | T7  | AIO      | positive MDI terminal                                               |  |

| VDDA25_100BT1_TXM7 | R8  | Р        | 2.5 V transmitter analog supply voltage; connect to VDDA25_VREG_OUT |  |

| VSSA25_100BT1_TXM7 | R7  | Р        | analog transmitter supply ground                                    |  |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog input; AO: analog output; P: power; G: ground.

### 6.2.6.6 100BASE-T1 Port 8

Table 18. 100BASE-T1 Port 8

| Symbol             | Pin | Type [1] | Description                                                         |

|--------------------|-----|----------|---------------------------------------------------------------------|

| 100BT1_TRX_M8      | T10 | AIO      | negative MDI terminal                                               |

| 100BT1_TRX_P8      | Т9  | AIO      | positive MDI terminal                                               |

| VDDA25_100BT1_TXM8 | R10 | Р        | 2.5 V transmitter analog supply voltage; connect to VDDA25_VREG_OUT |

| VSSA25_100BT1_TXM8 | R9  | Р        | analog transmitter supply ground                                    |

[1] IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog input, AO: analog output; P: power; G: ground.

SJA1110

#### 6.2.6.7 100BASE-T1 Port 9

Table 19. 100BASE-T1 Port 9

| Symbol             | Pin | Type [1] | Description                                                         |

|--------------------|-----|----------|---------------------------------------------------------------------|

| 100BT1_TRX_M9      | T12 | AIO      | negative MDI terminal                                               |

| 100BT1_TRX_P9      | T11 | AIO      | positive MDI terminal                                               |

| VDDA25_100BT1_TXM9 | R12 | Р        | 2.5 V transmitter analog supply voltage; connect to VDDA25_VREG_OUT |

| VSSA25_100BT1_TXM9 | R11 | Р        | analog transmitter supply ground                                    |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog input; AO: analog output; P: power; G: ground.

#### 6.2.6.8 100BASE-T1 Port 10

Table 20. 100BASE-T1 Port 10

| Symbol              | Pin | Type [1] | Description                                                         |

|---------------------|-----|----------|---------------------------------------------------------------------|

| 100BT1_TRX_M10      | T14 | AIO      | negative MDI terminal                                               |

| 100BT1_TRX_P10      | T13 | AIO      | positive MDI terminal                                               |

| VDDA25_100BT1_TXM10 | R14 | Р        | 2.5 V transmitter analog supply voltage, connect to VDDA25_VREG_OUT |

| VSSA25_100BT1_TXM10 | R13 | Р        | analog transmitter supply ground                                    |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AIO: analog input/output; AI: analog output; P: power; G: ground.

#### 6.2.7 100BASE-TX

Table 21. 100BASE-TX

| Table 21. TOOBAGE | 170                        |          |                                                    |

|-------------------|----------------------------|----------|----------------------------------------------------|

| Symbol            | Pin                        | Type [1] | Description                                        |

| 100BTX_EXTRES     | J15                        | Р        | external calibration resistor (6.5k, 1%) to ground |

| 100BTX_RX_M       | G16                        | AIO      | 100BASE-TX negative receiver terminal              |

| 100BTX_RX_P       | G15                        | AIO      | 100BASE-TX positive receiver terminal              |

| 100BTX_TX_M       | H16                        | AIO      | 100BASE-TX negative transmit terminal              |

| 100BTX_TX_P       | H15                        | AIO      | 100BASE-TX positive transmit terminal              |

| VDDA11_100BTX     | H14                        | Р        | 1.1 V 100BASE-TX analog supply voltage             |

| VDDA33_100BTX     | G14                        | Р        | 3.3 V 100BASE-TX analog transceiver supply voltage |

| VSSA11_100BTX     | F14, F15,<br>F16, J14, J16 | Р        | 100BASE-TX analog supply ground                    |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog output; P: power; G: ground.

# 6.2.8 Clock Interfaces

### 6.2.8.1 Analog clock interface

Table 22. Analog clock interface

| Symbol  | Pin | Type [1] | Description                 |

|---------|-----|----------|-----------------------------|

| OSC_IN  | C1  | AIO      | crystal oscillator input    |

| OSC_OUT | D1  | AIO      | crystal oscillator feedback |

SJA1110

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

Table 22. Analog clock interface...continued

| Symbol     | Pin | Type [1] | Description                            |  |  |  |

|------------|-----|----------|----------------------------------------|--|--|--|

| VDDA11_OSC | C2  | Р        | 1.1 V analog oscillator supply voltage |  |  |  |

| VDDA11_PLL | E2  | Р        | 1.1 V analog PLL supply voltage        |  |  |  |

| VSSA_OSC   | D2  | Р        | analog oscillator ground               |  |  |  |

| VSSA_PLL   | E1  | Р        | analog PLL ground                      |  |  |  |

[1] IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog input; AO: analog output; P: power; G: ground.

#### 6.2.8.2 Digital clock interface 1

Table 23. Digital clock interface 1

| Symbol            | Pin | Type [1] | Description                                                                                                |

|-------------------|-----|----------|------------------------------------------------------------------------------------------------------------|

| REFCLK_OUT1       | G2  | 0        | digital 25 MHz reference clock 1 output (active-HIGH, plain output (prog), high (prog), VDDIO_REFCLK_OUT1) |

| VDDIO_REFCLK_OUT1 | G1  | Р        | reference clock 1 I/O supply voltage (1.8 V, 2.5 V, 3.3 V)                                                 |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AIO: analog input/output; AI: analog input; AO: analog output; P: power; G: ground.

#### 6.2.8.3 Digital clock interface 2

Table 24. Digital clock interface 2

| Symbol            | Pin | Type [1] | Description                                                                                                |

|-------------------|-----|----------|------------------------------------------------------------------------------------------------------------|

| REFCLK_OUT2       | H2  | 0        | digital 25 MHz reference clock 2 output (active-HIGH, plain output (prog), high (prog), VDDIO_REFCLK_OUT2) |

| VDDIO_REFCLK_OUT2 | H1  | Р        | reference clock 2 I/O supply voltage (1.8 V, 2.5 V, 3.3 V)                                                 |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AIO: analog input/output; AI: analog input; AO: analog output; P: power; G: ground.

#### 6.2.8.4 Digital clock interface 3

Table 25. Digital clock interface 3

| Table 25. Digital Clock litter | able 25. Digital clock interface 5 |          |                                                                                                      |  |  |

|--------------------------------|------------------------------------|----------|------------------------------------------------------------------------------------------------------|--|--|

| Symbol                         | Pin                                | Type [1] | Description                                                                                          |  |  |

| REFCLK_OUT3                    | D15                                | 0        | digital 25 MHz REFCLK_OUT3 output (active-HIGH, plain output (prog), high (prog), VDDIO_REFCLK_OUT3) |  |  |

| VDDIO_REFCLK_OUT3              | D16                                | Р        | reference clock 3 I/O voltage supply (1.8 V, 2.5 V, 3.3 V)                                           |  |  |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog input; AO: analog output; P: power; G: ground.

# 6.2.8.5 Digital clock interface 4

Table 26. Digital clock interface 4

| Symbol            | Pin | Type [1] | Description                                                                                          |

|-------------------|-----|----------|------------------------------------------------------------------------------------------------------|

| REFCLK_OUT4       | E15 | 0        | digital 25 MHz REFCLK_OUT4 output (active-HIGH, plain output (prog), high (prog), VDDIO_REFCLK_OUT4) |

| VDDIO_REFCLK_OUT4 | E16 | Р        | reference clock 4 I/O voltage supply (1.8 V, 2.5 V, 3.3 V)                                           |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AIO: analog input/output; AI: analog input; AO: analog output; P: power; G: ground.

SJA1110

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

# 6.2.8.6 Digital clock interface common

Table 27. Digital clock interface common

| Symbol         | Pin | Type [1] | Description                           |  |  |

|----------------|-----|----------|---------------------------------------|--|--|

| VSSIO_REFCLK12 | G3  | Р        | reference clock 1 and 2 supply ground |  |  |

| VSSIO_REFCLK34 | E14 | Р        | reference clock 3 and 4 supply ground |  |  |

[1] IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog input; AO: analog output; P: power; G: ground.

#### 6.2.9 Microcontroller

#### 6.2.9.1 Boot pinstrap options

Table 28. Boot pinstrap options

| Symbol       | Pin | Type [1] | Description                                                          |

|--------------|-----|----------|----------------------------------------------------------------------|

| BOOT_OPTION0 | N7  | I        | pinstrap boot option selection, bit 0 (active-HIGH, low, VDDIO_HOST) |

| BOOT_OPTION1 | P7  | I        | pinstrap boot option pin 1 (active-HIGH, low, VDDIO_HOST)            |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AIO: analog input/output; AI: analog input; AO: analog output; P: power; G: ground.

#### 6.2.9.2 Quad SPI Flash Interface

Table 29. Quad SPI Flash Interface

| Symbol      | Pin | Type [1] | Description                                             |

|-------------|-----|----------|---------------------------------------------------------|

| QSPI_IO0    | E12 | Ю        | QSPI IO pin 0 (active-HIGH, high (prog), VDDIO_FLASH)   |

| QSPI_IO1    | E13 | Ю        | QSPI IO pin 1 (active-HIGH, high (prog), VDDIO_FLASH)   |

| QSPI_IO2    | D13 | Ю        | QSPI IO pin 2 (active-HIGH, high (prog), VDDIO_FLASH)   |

| QSPI_IO3    | F13 | Ю        | QSPI IO pin 3 (active-HIGH, high (prog), VDDIO_FLASH)   |

| QSPI_SCLK   | F12 | 0        | QSPI SCLK (active-HIGH, high (prog), VDDIO_FLASH)       |

| QSPI_SS_N   | D12 | 0        | QSPI chip select (active-LOW, high (prog), VDDIO_FLASH) |

| VDDIO_FLASH | G11 | Р        | QSPI I/O voltage supply (1.8 V, 2.5 V, 3.3 V)           |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AIO: analog input/output; AI: analog input; AO: analog output; P: power; G: ground.

#### 6.2.9.3 SMI peripheral interface

Table 30. SMI peripheral interface

| Symbol        | Pin | Type [1] | Description                                                                              |

|---------------|-----|----------|------------------------------------------------------------------------------------------|

| SMI_OUT_MDC   | C15 | 0        | SMI_OUT (Master SMI) MDC (active-HIGH, plain output (prog), high (prog), VDDIO_SMI_OUT)  |

| SMI_OUT_MDIO  | C16 |          | SMI_OUT (Master SMI) MDIO (active-HIGH, plain output (prog), high (prog), VDDIO_SMI_OUT) |

| VDDIO_SMI_OUT | C14 | P C      | SMI_OUT I/O voltage supply (1.8 V, 2.5 V, 3.3 V)                                         |

[1] IO: digital input/output; I: digital input; O: digital output; AIO: analog input/output; AI: analog input; AO: analog output; P: power; G: ground.

### 6.2.9.4 SPI peripheral interface

Table 31. SPI peripheral interface

| Symbol        | Pin | Type [1] | Description                                                                                    |

|---------------|-----|----------|------------------------------------------------------------------------------------------------|

| SPI_PER_MISO  | G13 | Ю        | SPI_PER MISO (active-HIGH, plain output (prog), high (prog), VDDIO_SPI_PER)                    |

| SPI_PER_MOSI  | G12 | Ю        | SPI_PER MOSI (active-HIGH, plain output (prog), high (prog), VDDIO_SPI_PER)                    |

| SPI_PER_SCLK  | H12 | Ю        | SPI_PER SCLK (active-HIGH, pull-up (prog), high (prog), VDDIO_SPI_PER)                         |

| SPI_PER_SS0_N | H13 | Ю        | SPI_PER general purpose chip select 0 (active-LOW, pull-up (prog), high (prog), VDDIO_SPI_PER) |

| SPI_PER_SS1_N | J13 | Ю        | SPI_PER general purpose chip select 1 (active-LOW, pull-up (prog), high (prog), VDDIO_SPI_PER) |

| VDDIO_SPI_PER | H11 | Р        | SPI_PER I/O voltage supply (1.8 V, 2.5 V, 3.3 V)                                               |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog input, AO: analog output; P: power; G: ground.

#### 6.2.9.5 GPIO Interface 1

Table 32. GPIO Interface 1

| Symbol      | Pin | Type [1] | Description                                                        |

|-------------|-----|----------|--------------------------------------------------------------------|

| GPIO0       | E7  | Ю        | GPIO pin 0 (active-HIGH, pull-up (prog), high (prog), VDDIO_GPIO1) |

| GPIO1       | C8  | Ю        | GPIO pin 1 (active-HIGH, pull-up (prog), high (prog), VDDIO_GPIO1) |

| GPIO2       | D8  | Ю        | GPIO pin 2 (active-HIGH, pull-up (prog), high (prog), VDDIO_GPIO1) |

| GPIO3       | E8  | Ю        | GPIO pin 3 (active-HIGH, pull-up (prog), high (prog), VDDIO_GPIO1) |

| VDDIO_GPIO1 | F8  | P        | GPIO Group 1 I/O supply voltage (1.8 V, 2.5 V, 3.3 V)              |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog input; AO: analog output; P: power; G: ground.

#### 6.2.9.6 GPIO Interface 2

Table 33. GPIO Interface 2

| able 33. Of 10 litterface 2 |     |          |                                                                    |  |  |

|-----------------------------|-----|----------|--------------------------------------------------------------------|--|--|

| Symbol                      | Pin | Type [1] | Description                                                        |  |  |

| GPIO4                       | C9  | Ю        | GPIO pin 4 (active-HIGH, pull-up (prog), high (prog), VDDIO_GPIO2) |  |  |

| GPIO5                       | D9  | 10       | GPIO pin 5 (active-HIGH, pull-up (prog), high (prog), VDDIO_GPIO2) |  |  |

| GPIO6                       | E9  | Ю        | GPIO pin 6 (active-HIGH, pull-up (prog), high (prog), VDDIO_GPIO2) |  |  |

| GPIO7                       | E10 | Ю        | GPIO pin 7 (active-HIGH, pull-up (prog), high (prog), VDDIO_GPIO2) |  |  |

| VDDIO_GPIO2                 | F9  | Р        | GPIO Group 2 I/O supply voltage (1.8 V, 2.5 V, 3.3 V)              |  |  |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog input; AO: analog output; P: power; G: ground.

### 6.2.9.7 GPIO Interface 3

Table 34. GPIO Interface 3

| Symbol | Pin | Type [1] | Description                                                         |

|--------|-----|----------|---------------------------------------------------------------------|

| GPIO8  | J4  | Ю        | GPIO pin 8 (active-HIGH, pull-up (prog), high (prog), VDDIO_GPIO3)  |

| GPIO9  | K4  | Ю        | GPIO pin 9 (active-HIGH, pull-up (prog), high (prog), VDDIO_GPIO3)  |

| GPIO10 | J5  | Ю        | GPIO pin 10 (active-HIGH, pull-up (prog), high (prog), VDDIO_GPIO3) |

SJA1110

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

Table 34. GPIO Interface 3...continued

| Symbol      | Pin | Type [1] | Description                                                         |

|-------------|-----|----------|---------------------------------------------------------------------|

| GPIO11      | K5  | Ю        | GPIO pin 11 (active-HIGH, pull-up (prog), high (prog), VDDIO_GPIO3) |

| VDDIO_GPIO3 | J6  | Р        | GPIO Group 3 I/O supply voltage (1.8 V, 2.5 V, 3.3 V)               |

[1] IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog input; AO: analog output; P: power; G: ground.

#### 6.2.9.8 GPIO Interface 4

Table 35. GPIO Interface 4

| Symbol      | Pin | Type [1] | Description                                                         |

|-------------|-----|----------|---------------------------------------------------------------------|

| GPIO12      | L4  | Ю        | GPIO pin 12 (active-HIGH, pull-up (prog), high (prog), VDDIO_GPIO4) |

| GPIO13      | M4  | Ю        | GPIO pin 13 (active-HIGH, pull-up (prog), high (prog), VDDIO_GPIO4) |

| GPIO14      | L5  | Ю        | GPIO pin 14 (active-HIGH, pull-up (prog), high (prog), VDDIO_GPIO4) |

| GPIO15      | M5  | Ю        | GPIO pin 15 (active-HIGH, pull-up (prog), high (prog), VDDIO_GPIO4) |

| VDDIO_GPIO4 | M6  | Р        | GPIO Group 4 I/O supply voltage (1.8 V, 2.5 V, 3.3 V)               |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog input; AO: analog output; P: power; G: ground.

# 6.2.10 Functional safety interface

Table 36. Functional safety interface

| Symbol     | Pin | Type [1] | Description                                                 |

|------------|-----|----------|-------------------------------------------------------------|

| ERR_N      | B1  | 0        | fail-safe error output (active-LOW, low, VDDIO_FUSA)        |

| FSI1       | A2  | I        | fail-safe input 1 (active-HIGH, pull-down, low, VDDIO_FUSA) |

| FSI2       | B2  | 1        | fail-safe input 2 (active-HIGH, pull-down, low, VDDIO_FUSA) |

| VDDIO_FUSA | C3  | Р        | FUSA I/O supply voltage (1.8 V, 2.5 V, 3.3 V)               |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog input; AO: analog output; P: power; G: ground.

#### 6.2.11 General

#### 6.2.11.1 OTP

Table 37. OTP

| Symbol         | Pin | Type [1] | Description                                                                                                                              |

|----------------|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------|

| VDDA18_OTP_IN  | НЗ  | Р        | 1.8 V analog supply voltage. Connect to VDDA18_OTP_OUT and filter externally. Connect to ground, if in-field OTP programming not needed. |

| VDDA18_OTP_OUT | H4  | AO       | 1.8 V analog OTP supply output                                                                                                           |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog input; AO: analog output; P: power; G: ground.

#### 6.2.11.2 PTP interface

#### Table 38. PTP interface

| Symbol  | Pin | Type [1] | Description                                                                                  |

|---------|-----|----------|----------------------------------------------------------------------------------------------|

| PTP_CLK | B15 | 0        | programmable PTP clock output (active-HIGH, plain output (prog), high (prog), VDDIO_PTP_CLK) |

SJA1110

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

# Table 38. PTP interface...continued

| Symbol        | Pin | Type [1] | Description                                      |

|---------------|-----|----------|--------------------------------------------------|

| VDDIO_PTP_CLK | B16 | Р        | PTP_CLK I/O supply voltage (1.8 V, 2.5 V, 3.3 V) |

[1] IO: digital input/output; I: digital input; O: digital output; AIO: analog input/output; AI: analog input; AO: analog output; P: power; G: ground.

#### 6.2.11.3 Sync interface

#### Table 39. Sync interface

| Symbol      | Pin | Type [1] | Description                                                                                |

|-------------|-----|----------|--------------------------------------------------------------------------------------------|

| DEVICE_SYNC | F2  | I        | cascading time synchronization (active-HIGH, plain output (prog), high (prog), VDDIO_SYNC) |

| VDDIO_SYNC  | F1  | Р        | sync I/O supply voltage (1.8 V, 2.5 V, 3.3 V)                                              |

[1] IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog input; AO: analog output; P: power; G: ground.

#### 6.2.12 External host

### 6.2.12.1 SMI access point

#### Table 40. SMI access point

| Symbol      | Pin | Type [1] | Description                                                                                   |

|-------------|-----|----------|-----------------------------------------------------------------------------------------------|

| SMI_AP_MDC  | N6  | I        | MDC of the SMI_AP slave interface (active-HIGH, plain input, low, VDDIO_HOST)                 |

| SMI_AP_MDIO | P6  | Ю        | MDIO of the SMI_AP slave interface (active-HIGH, plain input/output, high (prog), VDDIO_HOST) |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog input; AO: analog output; P: power; G: ground.

#### 6.2.12.2 Host access point

#### Table 41. Host access point

| Symbol        | Pin    | Type [1] | Description                                                                               |

|---------------|--------|----------|-------------------------------------------------------------------------------------------|

| DEVICE_CFG_N  | G5     | 0        | device completed configuration (active-LOW, plain output (prog), high (prog), VDDIO_HOST) |

| INT_N         | D5     | 0        | interrupt output open-drain (active-LOW, plain output (prog), high (prog), VDDIO_HOST)    |

| SPI_HAP_SCLK  | E4     | I        | serial clock (active-HIGH, pull-up (prog), low, VDDIO_HOST)                               |

| SPI_HAP_SDI   | E5     | 1,       | serial data in (active-HIGH, pull-up (prog), low, VDDIO_HOST)                             |

| SPI_HAP_SDO   | D4     | T        | serial data out (plain output (prog), high (prog), VDDIO_HOST)                            |

| SPI_HAP_SS0_N | F4     |          | chip select to select SPI_AP (active-LOW, pull-up (prog), low, VDDIO_HOST)                |

| SPI_HAP_SS1_N | F5     | D        | chip select to select SPI_HOST (active-LOW, pull-up (prog), low, VDDIO_HOST)              |

| VDDIO_HOST    | E3, M7 | Р        | host supply voltage (1.8 V, 2.5 V, 3.3 V)                                                 |

[1] IO: digital input/output; I: digital input; O: digital output; AIO: analog input/output; AI: analog input; AO: analog output; P: power; G: ground.

DRAFT

# 6.2.13 Test and debug interface

Table 42. Test and debug interface

| Symbol      | Pin | Type [1] | Description                                                                                 |

|-------------|-----|----------|---------------------------------------------------------------------------------------------|

| TCK         | J12 | I        | JTAG TCK/Serial Wire Debug SWCLK (active-HIGH, pull-up, low, VDDIO_DEBUG)                   |

| TDI         | K12 | I        | JTAG TDI (active-HIGH, pull-up, low, VDDIO_DEBUG)                                           |

| TDO         | L12 | 0        | JTAG TDO/Single Wire Debug SWO (active-HIGH, plain output (prog), high (prog), VDDIO_DEBUG) |

| TMS         | K13 | I        | JTAG TMS/Single Wire Debug SWDIO (active-HIGH, pull-up, high (prog), VDDIO_DEBUG)           |

| TRST_N      | L13 | I        | JTAG TRST_N (active-LOW, pull-up, low, VDDIO_DEBUG)                                         |

| VDDIO_DEBUG | J11 | Р        | DEBUG I/O supply voltage (1.8 V, 2.5 V, 3.3 V)                                              |

<sup>[1]</sup> IO: digital input/output; I: digital input; O: digital output; AlO: analog input/output; Al: analog input; AO: analog output; P: power; G: ground.

# 6.2.14 Pinning Legend

Table 43. Digital pin legend

| Qualifier           | Description                                        |  |

|---------------------|----------------------------------------------------|--|

| plain output (prog) | default at plain output, pull-up/down configurable |  |

| plain input (prog)  | default at plain input, pull-up/down configurable  |  |

| pull-up             | fixed at weak pull-up                              |  |

| pull-down           | fixed at weak pull-down                            |  |

| pull-up (prog)      | default weak pull-up, configurable                 |  |

| pull-down (prog)    | default at weak pull-down, configurable            |  |

Table 44. Digital pin output speed

| Qualifier     | Description                                           |  |

|---------------|-------------------------------------------------------|--|

| low           | fixed at very low noise/low speed                     |  |

| medium        | fixed at low noise/medium speed                       |  |

| fast          | fixed at medium noise/fast speed                      |  |

| high          | fixed at high noise/igh speed                         |  |

| low (prog)    | programmable with default at very low noise/low speed |  |

| medium (prog) | programmable with default at low noise/medium speed   |  |

| fast (prog)   | programmable with default at medium noise/fast speed  |  |

| high (prog)   | programmable with default at high noise/high speed    |  |

# Functional description

#### 7.1 100BASE-T1

The subsystem contains up to six IEEE 802.3bw compliant 100BASE-T1 PHYs. Each PHY module provides the functions needed to meet IEEE Std 802.3bw.

PHY configuration is managed via IEEE Std 802.3 Clause 45 register access. The registers can be accessed by the internal embedded processor via the internal APB or by an external processor via either the SPI\_AP or a dedicated SMI\_AP interface. The SMI interface supports Clause 45 transactions, as well as Clause 22 transactions. However, it does not support access to Clause 22 registers, except for accessing the Clause 45 register space using indirect addressing.

The 100BASE-T1 subsystem controller also includes an initialization controller that fetches configuration data from both pin-strapped IOs and one-time programmable (OTP) memory and applies it to the PHYs. This only occurs during the power-up boot process.

This subsystem handles support for OPEN Alliance TC-10 Wake/Sleep logic with the option to indicate via INH whether the device needs a power supply, or whether power supplies (except the always-on supply) can be switched off.

#### 7.2 100BASE-TX

The 100BASE-TX is an Ethernet PHY transceiver compliant to IEEE 802.3 standard. The typical use case of this interface in automotive applications is to connect to an external diagnostic port with 100 Mb/s fast Ethernet connection.

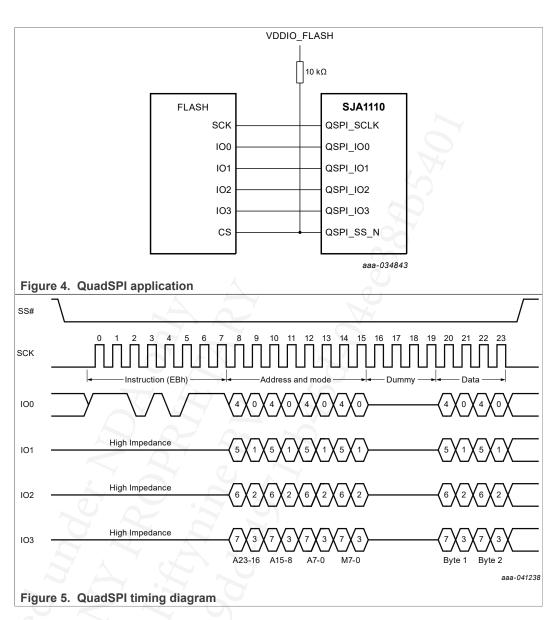

### 7.3 Quad Serial Peripheral Interface (QuadSPI)

QuadSPI is a 6-signal interface used to connect a single serial NOR-flash or EEPROM to the SJA1110. QuadSPI supports SDR serial NOR-flash devices to a maximum size of 1 Gbit (128 Mbyte). This enables the user to select from a wide range of flash types and vendors. QuadSPI supports the following features:

- Support for a serial clock frequency of 5 MHz (default), 10 MHz, 25 MHz or 50 MHz

- Execute in Place (XiP) not supported

- On-the-fly decryption not supported

- Single Data Rate (SDR) mode of operation (DDR mode not supported)

- Internally generated sampling (Data Strobe Sampling (DQS) supported)

- · SDR half-speed access mode not supported

**Note:** An external pull-up is required on  $\overline{CS}$ .

# SJA1110 AFT DRAFT

DRAF1

Table 45. External (QSPI) Flash and EEPROM chip requirements

| Table 45. External (QS      | PI) Flash and EEPROM chip requil | ements                |                       |

|-----------------------------|----------------------------------|-----------------------|-----------------------|

|                             | QuadSPI flash                    | SPI flash             | EEPROM                |

| Speed (MHz) <sup>[1]</sup>  | ≥ 25                             | ≥ 25                  | ≥ 5                   |

| Addressing                  | 3-byte                           | 3-byte                | 3-byte                |

| Supply                      | 1.8 V, 2.5 V or 3.3 V            | 1.8 V ,2.5 V or 3.3 V | 1.8 V, 2.5 V or 3.3 V |

| SFDP support <sup>[2]</sup> | read in 4-4-4 or 1-1-1 mode      | _                     | _                     |

| SFDP revisions              | 1.0, 1.5 or 1.6                  | _                     | _                     |

<sup>[1]</sup> The bootstrap pins determine the type of NVM connected at startup. The default operating speed of the interface is 25 MHz for a flash (QuadSPI or SPI flash) and 5 MHz for an EEPROM. The NVM needs to support the minimum operating speed. If desired, the speed can be lowered or increased after booting up.

**NXP Semiconductors**

<sup>[2]</sup> opcode – address – data

# 7.4 Host Access Point (SPI HAP)

The SPI\_HAP can be used to interface with and control the SJA1110 over the SPI at a maximum frequency of 25 MHz. This interface multiplexes the SPI Access Point (SPI AP) and the SPI Host Access (SPI HOST) with shared SDI, SDO and SCK signal lines but dedicated chip select lines.

SPI AP is an SPI slave device used to control internal device registers such as switch core, SGMII, internal PHYs and other peripherals. Internally, the AP acts as an AHB master.

SPI HOST is an SPI slave interface that enables communication between an external host and the internal host. It can be used to allow an external host to selectively access internal blocks. It can also be used by the external host to download firmware for execution by the internal host. In this configuration, a dedicated external NVM may be optional.

SPI\_HAP provides access to either SPI\_AP or SPI\_HOST, depending on the levels on pins SPI\_HAP\_SSx\_N (see Table 41).

Pin SPI HAP SS1 N maps to SPI HOST and pin SPI HAP SS0 N to SPI AP.

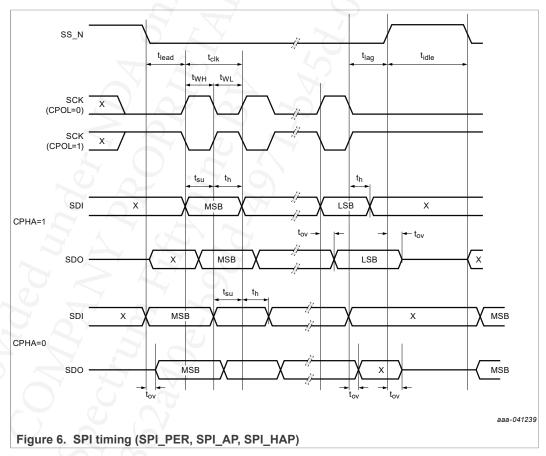

### 7.5 SPI PER

The SPI PER interface is connected to the internal low-power SPI (LPSPI) core, which can operate in master or slave configuration. The interface can operate at up to 50 MHz in master mode and up to 25 MHz in slave mode.

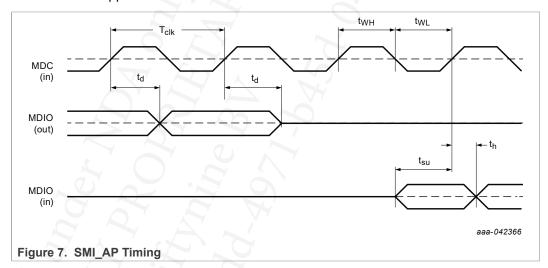

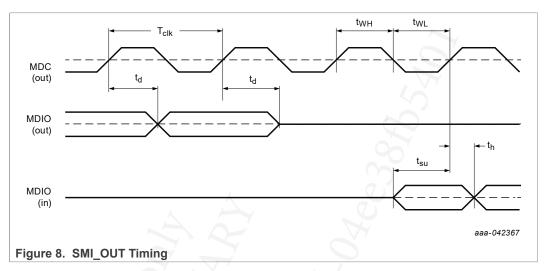

Two active-LOW chip select pins are provided for controlling peripheral devices (SPI\_PER configured as master). The chip select pins are inputs in slave mode.