# 13.6.9 Calibration value register (ADCx\_CAL)

Contains calibration information that is generated by the calibration function. This register contains a calibration value of four bits(CAL[3:0]); this is automatically set once the self calibration sequence is done (ADC\_SC[CAL] bit is cleared). If this register is written to by the user after calibration, the linearity error specifications may not be met.

Address: Base address + 28h offset Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 3 2 1 0 0 R CAL CODE W 0 0 0 0 0 0 0 0 0 0 0

## ADCx\_CAL field descriptions

| Field            | Description                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------|

| 31–4<br>Reserved | This read-only field is reserved and always has the value 0.                                          |

| CAL_CODE         | Calibration Result Value<br>This value is automatically loaded and updated at the end of calibration. |

# 13.7 Memory map and register definition

The ADC-Digital contains 32-bit, word aligned, byte enables registers; byte or half word access are not supported. All configuration registers are accessible via 32-bit access bus Interface. Write access to reserved locations have no impact while read access to reserved locations always return 0.

## NOTE

No protection or indication mechanism is available (for example, 32-bit access starting with address offset value 0x01 or 0x02 or 0x03). The ADC does not check for correctness of the programmed values in the registers and the programmer must ensure that correct values are being written.

### ADC memory map

| Absolute<br>address<br>(hex) | Register name                                    | Width<br>(in bits) | Access | Reset value | Section/<br>page |  |

|------------------------------|--------------------------------------------------|--------------------|--------|-------------|------------------|--|

| 0                            | Control register for hardware triggers (ADC_HC0) | 32                 | R/W    | 0000_001Fh  | 13.7.1/412       |  |

Table continues on the next page...

| Absolute<br>address<br>(hex) | Register name                                    | Width<br>(in bits) | Access         | Reset value | Section/<br>page |

|------------------------------|--------------------------------------------------|--------------------|----------------|-------------|------------------|

| 4                            | Control register for hardware triggers (ADC_HC1) | 32                 | R/W            | 0000_001Fh  | 13.7.2/413       |

| 8                            | Control register for hardware triggers (ADC_HC2) | 32                 | R/W            | 0000_001Fh  | 13.7.2/413       |

| С                            | Control register for hardware triggers (ADC_HC3) | 32                 | R/W            | 0000_001Fh  | 13.7.2/413       |

| 10                           | Control register for hardware triggers (ADC_HC4) | 32                 | R/W            | 0000_001Fh  | 13.7.2/413       |

| 14                           | Status register for HW triggers (ADC_HS)         | 32                 | R (reads<br>0) | 0000_0000h  | 13.7.3/415       |

| 18                           | Data result register for HW triggers (ADC_R0)    | 32                 | R/W            | 0000_0000h  | 13.7.4/416       |

| 1C                           | Data result register for HW triggers (ADC_R1)    | 32                 | R/W            | 0000_0000h  | 13.7.5/417       |

| 20                           | Data result register for HW triggers (ADC_R2)    | 32                 | R/W            | 0000_0000h  | 13.7.5/417       |

| 24                           | Data result register for HW triggers (ADC_R3)    | 32                 | R/W            | 0000_0000h  | 13.7.5/417       |

| 28                           | Data result register for HW triggers (ADC_R4)    | 32                 | R/W            | 0000_0000h  | 13.7.5/417       |

| 2C                           | Configuration register (ADC_CFG)                 | 32                 | R/W            | 0000_0200h  | 13.7.6/418       |

| 30                           | General control register (ADC_GC)                | 32                 | R/W            | 0000_0000h  | 13.7.7/420       |

| 34                           | General status register (ADC_GS)                 | 32                 | R/W            | 0000_0000h  | 13.7.8/422       |

| 38                           | Compare value register (ADC_CV)                  | 32                 | R/W            | 0000_0000h  | 13.7.9/423       |

| 3C                           | Offset correction value register (ADC_OFS)       | 32                 | R/W            | 0000_0000h  | 13.7.10/424      |

| 40                           | Calibration value register (ADC_CAL)             | 32                 | R/W            | 0000_0000h  | 13.7.11/425      |

## ADC memory map (continued)

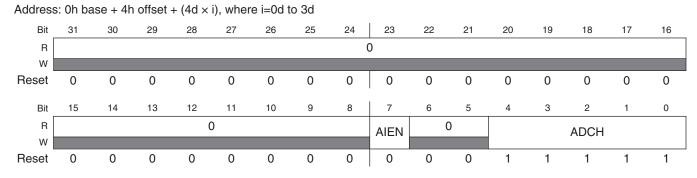

# 13.7.1 Control register for hardware triggers (ADC\_HC0)

ADC\_HC0 can be used for both software and hardware trigger mode. Other ADC\_HCn (n = 1...) are for use only in hardware trigger mode. The ADC\_HC0 to ADC\_HCn (n = 0,1) registers have identical fields, and are used to control ADC operation. At any one point in time, only one of the ADC\_HC0 to ADC\_HCn (n = 0,1) registers is actively controlling ADC conversions. Updating ADC\_HC0 while ADC\_HCn (n = 0,1) is actively controlling a conversion is allowed (and vice-versa for any of the ADC\_HCn (n = 0,1) registers). Writing ADC\_HC0 while ADC\_HC0 is actively controlling a conversion. In software trigger mode (ADTRG=0), writes to ADC\_HC0 subsequently initiates a new conversion (if the ADCH bits are equal to a value other than all 1s). Similarly, writing any of the ADC\_HCn (n = 0,1) registers while that specific ADC\_HC register is actively controlling a conversion aborts the current writes to any of the ADC\_HC1 register is not used for software trigger operation and therefore writes to any of them do not initiate a new conversion.

Address: 0h base + 0h offset = 0h

| Bit   | 31 | 30 | 29       | 28 | 27 | 26   | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|-------|----|----|----------|----|----|------|----|----|----|----|----|----|----|----|----|----|

| R     |    |    |          |    |    |      |    | 0  |    |    |    |    |    |    |    |    |

| w     |    |    |          |    |    |      |    |    |    |    |    |    |    |    |    |    |

| Reset | 0  | 0  | 0        | 0  | 0  | 0    | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Bit   | 15 | 14 | 13       | 12 | 11 | 10   | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| R     |    |    | 0 AIEN 0 |    | )  | ADCH |    |    |    |    |    |    |    |    |    |    |

| W     |    |    |          |    |    |      |    |    |    |    |    |    |    |    |    |    |

| Reset | 0  | 0  | 0        | 0  | 0  | 0    | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 1  |

| Field            | Description                                                                                                                                                                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–8<br>Reserved | This read-only field is reserved and always has the value 0.                                                                                                                                                  |

| 7<br>AIEN        | Conversion Complete Interrupt Enable/Disable Control                                                                                                                                                          |

|                  | An interrupt is generated whenever ADC_HS[COCO0]=1 (conversion ADC_HC0 completed), provided the corresponding interrupt is enabled.                                                                           |

|                  | 1 Conversion complete interrupt enabled                                                                                                                                                                       |

|                  | 0 Conversion complete interrupt disabled                                                                                                                                                                      |

| 6–5<br>Reserved  | This read-only field is reserved and always has the value 0.                                                                                                                                                  |

| ADCH             | Input Channel Select                                                                                                                                                                                          |

|                  | This 5-bit field selects one of the input channels. The successive approximation converter subsystem is turned off when the channel select bits are all set (ADCH = 11111b). This feature allows for explicit |

ADC\_HC0 field descriptions

Table continues on the next page ....

| Field | Description |                                                                                                                                                         |  |  |  |  |  |  |  |  |  |  |

|-------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|       | •           | e ADC and isolation of the input channel from all sources. Terminating continuous is way prevents an additional single conversion from being performed. |  |  |  |  |  |  |  |  |  |  |

|       | 00000-01111 | External channels 0 to 15.                                                                                                                              |  |  |  |  |  |  |  |  |  |  |

|       | 10000-10111 | Reserved                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |

|       | 11000       | Reserved.                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |

|       | 11001       | VREFSH = internal channel, for ADC self-test, hard connected to VRH internally                                                                          |  |  |  |  |  |  |  |  |  |  |

|       | 11010       | Reserved.                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |

|       | 11011       | Reserved.                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |

|       | 11100-11110 | Reserved.                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |

|       | 11111       | Conversion Disabled. Hardware Triggers will not initiate any conversion.                                                                                |  |  |  |  |  |  |  |  |  |  |

#### ADC\_HC0 field descriptions (continued)

## 13.7.2 Control register for hardware triggers (ADC\_HCn)

ADC\_HCn are for use only in hardware trigger mode. The ADC\_HC0 to ADC\_HCn registers have identical fields, and are used to control ADC operation. At any one point in time, only one of the ADC\_HC0 to ADC\_HCn registers is actively controlling ADC conversions. Updating ADC\_HC0 while ADC\_HCn is actively controlling a conversion is allowed (and vice-versa for any of the ADC\_HCn registers). Writing any of the ADC\_HCn registers while that specific ADC\_HCn register is actively controlling a conversion aborts the current conversion. Any of the ADC\_HC1 - ADC\_HCn registers are not used for software trigger operation and therefore writes to any of them do not initiate a new conversion.

### ADC\_HCn field descriptions

| Field            | Description                                                  |  |  |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 31–8<br>Reserved | This read-only field is reserved and always has the value 0. |  |  |  |  |  |  |  |  |

Table continues on the next page ...

| Field           |                                                                                                                                                                                                                                                                                                                                                                                                                            | Description                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 7<br>AIEN       | An interrupt is g<br>corresponding i<br>1 Conversion                                                                                                                                                                                                                                                                                                                                                                       | mplete Interrupt Enable/Disable Control<br>generated whenever ADC_HS[COCO0]=1(conversion ADC_HC0 completed), provided the<br>nterrupt is enabled.                                                                                                        |  |  |  |  |  |  |  |  |

| 6–5<br>Reserved | 0 Conversion complete interrupt disabled<br>This read-only field is reserved and always has the value 0.                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| ADCH            | Input Channel Select<br>This 5-bit field selects one of the input channels. The successive approximation converter subsys<br>turned off when the channel select bits are all set (ADCH =11111b). This feature allows for explic<br>disabling of the ADC and isolation of the input channel from all sources. Terminating continuous<br>conversions this way prevents an additional single conversion from being performed. |                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

|                 | 00000-01111<br>10000-10111<br>11000<br>11001<br>11010<br>11011<br>11100-11110<br>11111                                                                                                                                                                                                                                                                                                                                     | External channels 0 to 15.<br>Reserved<br>Reserved.<br>VREFSH = internal channel, for ADC self-test, hard connected to VRH internally<br>Reserved.<br>Reserved.<br>Reserved.<br>Conversion Disabled. Hardware Triggers will not initiate any conversion. |  |  |  |  |  |  |  |  |

## ADC\_HCn field descriptions (continued)

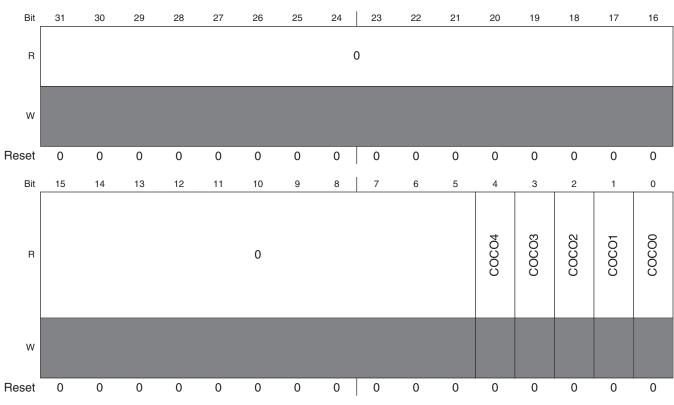

# 13.7.3 Status register for HW triggers (ADC\_HS)

Bit 0 is used for both software and hardware trigger modes of operation. Bit 1 to bit (n-1) indicate the rest of the HW triggers' statuses similar to bit 0, potentially corresponding to multiple ADC\_HC registers (for use only in hardware trigger mode).

### **ADC\_HS field descriptions**

| Field            | Description                                                  |

|------------------|--------------------------------------------------------------|

| 31–5<br>Reserved | This read-only field is reserved and always has the value 0. |

| 4<br>COCO4       | See description for COCO0.                                   |

| 3<br>COCO3       | See description for COCO0.                                   |

| 2<br>COCO2       | See description for COCO0.                                   |

| 1<br>COCO1       | See description for COCO0.                                   |

| 0<br>COCO0       | Conversion Complete Flag                                     |

Table continues on the next page ...

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | The COCOn flag is a read-only bit that is set each time a conversion is completed when the compare function is disabled (ADC_GC[ACFE]=0) and the hardware average function is disabled (ADC_GC[AVGE]=0). When the compare function is enabled (ADC_GC[ACFE]=1), the COCOn flag is set upon completion of a conversion only if the compare result is true. When the hardware average function is enabled (ADC_GC[AVGE]=1), the COCOn flag is set upon completion of the selected number of conversions (determined by the ADC_CFG[AVGS] field). The COCO0 flag will also set at the completion of a Calibration and Test sequence. A COCOn bit is cleared when the respective ADC_HCn is written or when the respective ADC_Rn is read. |

### ADC\_HS field descriptions (continued)

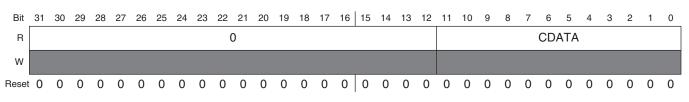

## 13.7.4 Data result register for HW triggers (ADC\_R0)

Contains the result of an ADC conversion of the channel selected by the respectivehardware trigger and channel control register (ADC\_HC0:ADC\_HCn). For every ADC\_HC0:ADC\_HCn status and channel control register, there is a respective ADC\_R0:ADC\_Rn data result register. Unused bits in the ADC\_Rn register are cleared in unsigned right justified modes. For example when configured for 10-bit single-ended mode, D[31:10] are cleared. The table below describes the behavior of the data result registers in the different modes of operation.

| Table 13-11. | <b>Data Result Register Description</b> |

|--------------|-----------------------------------------|

|              |                                         |

|                    |     | Data Result Register bits |   |     |     |     |            |    |    |    |    |    |    |    |    |    |                          |  |

|--------------------|-----|---------------------------|---|-----|-----|-----|------------|----|----|----|----|----|----|----|----|----|--------------------------|--|

| Conversion<br>Mode | D31 | D30                       |   | D12 | D11 | D10 | 6 <b>D</b> | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO | Format                   |  |

| 12b single-ended   | 0   | 0                         | 0 | 0   | D   | D   | D          | D  | D  | D  | D  | D  | D  | D  | D  | D  | unsigned right justified |  |

| 10b single-ended   | 0   | 0                         | 0 | 0   | 0   | 0   | D          | D  | D  | D  | D  | D  | D  | D  | D  | D  | unsigned right justified |  |

| 8b single-ended    | 0   | 0                         | 0 | 0   | 0   | 0   | 0          | 0  | D  | D  | D  | D  | D  | D  | D  | D  | unsigned right justified |  |

#### Address: 0h base + 18h offset = 18h

### ADC\_R0 field descriptions

| Field             | Description                                                  |

|-------------------|--------------------------------------------------------------|

| 31–12<br>Reserved | This read-only field is reserved and always has the value 0. |

| CDATA             | Data (result of an ADC conversion)                           |

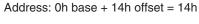

# 13.7.5 Data result register for HW triggers (ADC\_Rn)

Contains the result of an ADC conversion of the channel selected by the respective Hardware Trigger and channel control register (ADC\_HC0:ADC\_HCn). For every ADC\_HC0:ADC\_HCn status and channel control register, there is a respective ADC\_R0 to ADC\_Rn data result register. Unused bits in the ADC\_Rn register are cleared in unsigned right justified modes. For example when configured for 10-bit single-ended mode, D[31:10] are cleared. The table below describes the behavior of the data result registers in the different modes of operation.

|                    |     |     | - | _   |     | Da  | ta Re      | sult | Regi | ster I | bits | -  |    |    | _  |    |                          |  |  |  |

|--------------------|-----|-----|---|-----|-----|-----|------------|------|------|--------|------|----|----|----|----|----|--------------------------|--|--|--|

| Conversion<br>Mode | D31 | D30 |   | D12 | D11 | D10 | 6 <b>D</b> | D8   | D7   | D6     | D5   | D4 | D3 | D2 | D1 | DO | Format                   |  |  |  |

| 12b single-ended   | 0   | 0   | 0 | 0   | D   | D   | D          | D    | D    | D      | D    | D  | D  | D  | D  | D  | unsigned right justified |  |  |  |

| 10b single-ended   | 0   | 0   | 0 | 0   | 0   | 0   | D          | D    | D    | D      | D    | D  | D  | D  | D  | D  | unsigned right justified |  |  |  |

| 8b single-ended    | 0   | 0   | 0 | 0   | 0   | 0   | 0          | 0    | D    | D      | D    | D  | D  | D  | D  | D  | unsigned right justified |  |  |  |

Table 13-12. Data Result Register Description

#### Address: 0h base + 1Ch offset + (4d $\times$ i), where i=0d to 3d

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6   | 5   | 4 | 3 | 2 | 1 | 0 |

|-------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|-----|-----|---|---|---|---|---|

| R     |    |    |    |    |    |    |    |    |    | (  | )  |    |    |    |    |    |    |    |    |    |    |    |   |   |   | CDA | ٩ΤΑ |   |   |   |   |   |

| W     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |     |     |   |   |   |   |   |

| Reset | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0   | 0   | 0 | 0 | 0 | 0 | 0 |

### ADC\_Rn field descriptions

| Field             | Description                                                  |

|-------------------|--------------------------------------------------------------|

| 31–12<br>Reserved | This read-only field is reserved and always has the value 0. |

| CDATA             | Data (result of an ADC conversion)                           |

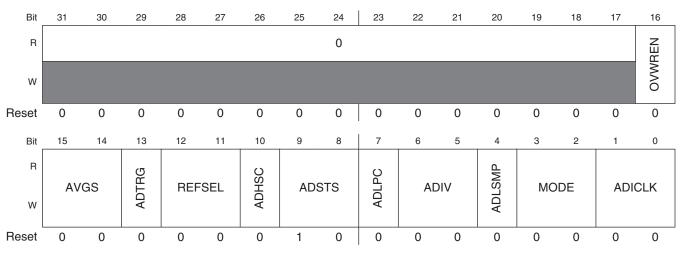

# 13.7.6 Configuration register (ADC\_CFG)

Selects the mode of operation, clock source, clock divide, configure for low power, long sample time, high speed configuration and selects the sample time duration.

#### Address: 0h base + 2Ch offset = 2Ch

### ADC\_CFG field descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–17<br>Reserved | This read-only field is reserved and always has the value 0.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 16<br>OVWREN      | <ul> <li>Data Overwrite Enable</li> <li>Controls the overwriting of the next converted Data onto the existing (previous) unread data into the Data result register.</li> <li>1 Enable the overwriting.</li> <li>0 Disable the overwriting. Existing Data in Data result register will not be overwritten by subsequent converted data.</li> </ul>                                                                                                                                                   |

| 15–14<br>AVGS     | Hardware Average select         Determines how many ADC conversions will be averaged to create the ADC average result. This functionality is activated when ADC_GC[AVGE] = 1.                                                                                                                                                                                                                                                                                                                       |

|                   | <ul> <li>4 samples averaged</li> <li>8 samples averaged</li> <li>16 samples averaged</li> <li>32 samples averaged</li> </ul>                                                                                                                                                                                                                                                                                                                                                                        |

| 13<br>ADTRG       | Conversion Trigger Select<br>Selects the type of trigger used for initiating a conversion. Two types of trigger are selectable: software<br>trigger and hardware trigger. When software trigger is selected, a conversion is initiated following a write<br>to ADC_HC0. When hardware trigger is selected, a conversion is initiated following the assertion of a<br>pulse on Alternate Hardware trigger input along with the assertion of the enable of respective the<br>hardware Triggers input. |

Table continues on the next page ...

## ADC\_CFG field descriptions (continued)

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | 0 Software trigger selected                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|              | 1 Hardware trigger selected                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 12–11        | Voltage Reference Selection                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| REFSEL       | Selects the voltage reference source used for conversions.                                                                                                                                                                                                                                                                                                                                                                                                               |

|              | 00 Selects VREFH/VREFL as reference voltage.                                                                                                                                                                                                                                                                                                                                                                                                                             |

|              | 01 Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|              | 10 Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|              | 11 Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10           | High Speed Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ADHSC        | This bit configures the ADC for high speed operation. The internal ADC clock is higher than normal.                                                                                                                                                                                                                                                                                                                                                                      |

|              | 0 Normal conversion selected.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|              | 1 High speed conversion selected.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 9–8<br>ADSTS | Defines the sample time duration. This has two modes, short and long. When long sample time is select (ADLSMP=1) this works for long sample time otherwise this works for short sample. This allows higher impedance inputs to be accurately sampled or to maximize conversion speed for lower impedance input Longer sample times can also be used to lower overall power consumption when continuous conversion are enabled if high conversion rates are not required. |

|              | 00 Sample period (ADC clocks) = 2 if ADLSMP=0b                                                                                                                                                                                                                                                                                                                                                                                                                           |

|              | Sample period (ADC clocks) = 12 if ADLSMP=1b                                                                                                                                                                                                                                                                                                                                                                                                                             |

|              | 01 Sample period (ADC clocks) = 4 if ADLSMP=0b                                                                                                                                                                                                                                                                                                                                                                                                                           |

|              | Sample period (ADC clocks) = 16 if ADLSMP=1b                                                                                                                                                                                                                                                                                                                                                                                                                             |

|              | <sup>10</sup> Sample period (ADC clocks) = 6 if ADLSMP=0b                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | Sample period (ADC clocks) = 20 if ADLSMP=1b                                                                                                                                                                                                                                                                                                                                                                                                                             |

|              | 11 Sample period (ADC clocks) = 8 if ADLSMP=0b                                                                                                                                                                                                                                                                                                                                                                                                                           |

|              | Sample period (ADC clocks) = 24 if ADLSMP=1b                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7            | Low-Power Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ADLPC        | Puts the ADC hard block into low power mode and reduces the comparator enable period by controlling                                                                                                                                                                                                                                                                                                                                                                      |

|              | timing in the SAR controller block towards the anlong hard block.<br>The signal indicating low power mode to the Analog block is asserted when this bit is set.                                                                                                                                                                                                                                                                                                          |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|              | 0 ADC hard block not in low power mode.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|              | 1 ADC hard block in low power mode.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6–5<br>ADIV  | Clock Divide Select                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|              | Selects the divide ratio used by the ADC to generate the internal clock ADCK.                                                                                                                                                                                                                                                                                                                                                                                            |

|              | 00 Input clock                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|              | 01 Input clock / 2                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|              | 10 Input clock / 4                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|              | 11 Input clock / 8                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4            | Long Sample Time Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Table continues on the next page ...

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | Selects between different sample times based on the ADC_CFG[ADSTS] field. This bit adjusts the sample period to allow higher impedance inputs to be accurately sampled or to maximize conversion speed for lower impedance inputs. If high conversion rates are not required, longer sample times can also be used to lower overall power consumption when continuous conversions are enabled. When ADLSMP=1, the Long Sample Time mode is selected and the time is defined by ADSTS[1:0] of the ADC_CFG register. |

|             | 0 Short sample mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             | 1 Long sample mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3–2<br>MODE | Conversion Mode Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             | Used to set the ADC resolution mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             | 00 8-bit conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             | 01 10-bit conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             | 10 12-bit conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             | 11 Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ADICLK      | Input Clock Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|             | Selects the input clock source to generate the internal clock ADCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             | 00 IPG clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|             | 01 IPG clock divided by 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             | 10 Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             | 11 Asynchronous clock (ADACK)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

## ADC\_CFG field descriptions (continued)

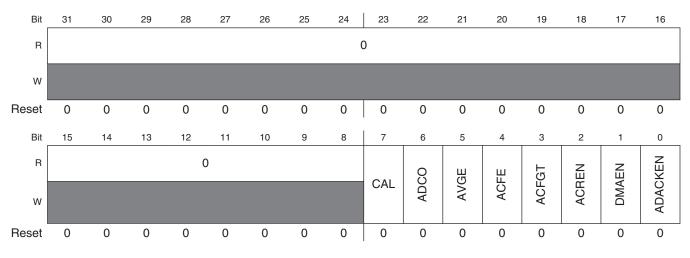

# 13.7.7 General control register (ADC\_GC)

Controls the calibration, continuous convert, hardware averaging functions, conversion active, hardware/software trigger select, compare function and voltage reference select of the ADC module.

Address: 0h base + 30h offset = 30h

## ADC\_GC field descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                     |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–8<br>Reserved | This read-only field is reserved and always has the value 0.                                                                                                                                                                                                                                                                                                    |

| 7<br>CAL         | Calibration<br>CAL begins the calibration sequence when set. This bit stays set while the calibration is in progress and i                                                                                                                                                                                                                                      |

|                  | cleared when the calibration sequence is complete. The ADC_GS[CALF] bit must be checked to determine the result of the calibration sequence. Once started, the calibration routine cannot be interrupted by writes to the ADC registers or the results will be invalid and the ADC_GS[CALF] bit will set Setting the CAL bit will abort any current conversion. |

| 6<br>ADCO        | Continuous Conversion Enable                                                                                                                                                                                                                                                                                                                                    |

|                  | Enables continuous conversions.                                                                                                                                                                                                                                                                                                                                 |

|                  | 0 One conversion or one set of conversions if the hardware average function is enabled (AVGE=1) after initiating a conversion.                                                                                                                                                                                                                                  |

|                  | 1 Continuous conversions or sets of conversions if the hardware average function is enabled (AVGE=1 after initiating a conversion.                                                                                                                                                                                                                              |

| 5<br>AVGE        | Hardware average enable                                                                                                                                                                                                                                                                                                                                         |

|                  | Enables the hardware average function of the ADC.                                                                                                                                                                                                                                                                                                               |

|                  | 0 Hardware average function disabled                                                                                                                                                                                                                                                                                                                            |

| 4                | 1 Hardware average function enabled                                                                                                                                                                                                                                                                                                                             |

| 4<br>ACFE        | Compare Function Enable<br>Enables the compare function.                                                                                                                                                                                                                                                                                                        |

|                  |                                                                                                                                                                                                                                                                                                                                                                 |

|                  | <ul><li>0 Compare function disabled</li><li>1 Compare function enabled</li></ul>                                                                                                                                                                                                                                                                                |

| 3                | Compare Function Greater Than Enable                                                                                                                                                                                                                                                                                                                            |

| ACFGT            |                                                                                                                                                                                                                                                                                                                                                                 |

|                  | Configures the compare function to check the conversion result relative to the compare value register (ADC_CV) based upon the value of ACREN (bit 2 in ADC_GC register). The ACFE bit must be set for ACFGT to have any effect.                                                                                                                                 |

|                  | 0 Configures "Less Than Threshold, Outside Range Not Inclusive and Inside Range Not Inclusive"<br>functionality based on the values placed in the ADC_CV register.                                                                                                                                                                                              |

|                  | 1 Configures "Greater Than Or Equal To Threshold, Outside Range Inclusive and Inside Range Inclusive" functionality based on the values placed in the ADC_CV registers.                                                                                                                                                                                         |

| 2<br>ACREN       | Compare Function Range Enable                                                                                                                                                                                                                                                                                                                                   |

|                  | Configures the compare function to check the conversion result of the input being monitored is either between or outside the range formed by the compare values in register (ADC_CV) determined by the value of ACFGT. The ACFE bit must be set for ACFGT to have any effect.                                                                                   |

|                  | 8 Range function disabled. Only the compare value 1 of ADC_CV register (CV1) is compared.                                                                                                                                                                                                                                                                       |

|                  | 1 Range function enabled. Both compare values of ADC_CV registers (CV1 and CV2) are compared.                                                                                                                                                                                                                                                                   |

|                  | DMA Enchia                                                                                                                                                                                                                                                                                                                                                      |

| 1<br>DMAEN       | DMA Enable                                                                                                                                                                                                                                                                                                                                                      |

Table continues on the next page ...

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | 0 DMA disabled (default)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              | 1 DMA enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0<br>ADACKEN | Asynchronous clock output enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|              | Enables the ADC's asynchronous clock source and the clock source output regardless of the conversion<br>and input clock select (ADC_CFG[ADICLK]) settings of the ADC. Based on MCU configuration, the<br>asynchronous clock may be used by other modules (see module introduction section). Setting this bit<br>allows the clock to be used even while the ADC is idle or operating from a different clock source. Also,<br>latency of initiating a single or first-continuous conversion with the asynchronous clock selected is reduced<br>since the ADACK clock is already operational. |

|              | 0 Asynchronous clock output disabled; Asynchronous clock only enabled if selected by ADICLK and a conversion is active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|              | 1 Asynchronous clock and clock output enabled regardless of the state of the ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## ADC\_GC field descriptions (continued)

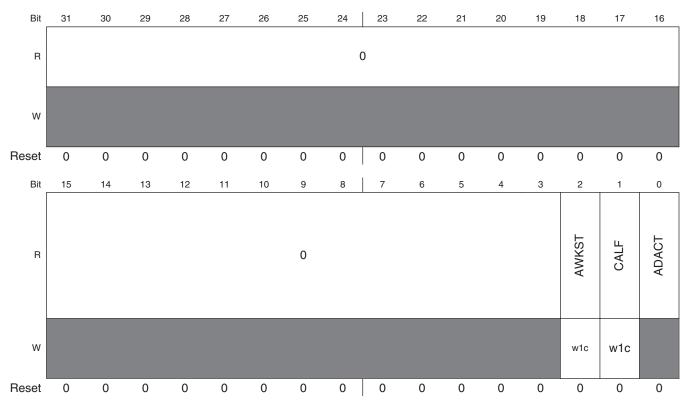

# 13.7.8 General status register (ADC\_GS)

Controls the calibration, continuous convert, hardware averaging functions, conversion active, hardware/software trigger select, compare function and voltage reference select of the ADC module.

Address: 0h base + 34h offset = 34h

#### ADC\_GS field descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–3<br>Reserved | This read-only field is reserved and always has the value 0.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2<br>AWKST       | <ul> <li>Asynchronous wakeup interrupt status</li> <li>Holds the status of asynchronous interrupt status that occured during stop mode. This bit is set when ipg_stop is deasserted and ipg_clk has started. It is cleared by writing '1' to it. Clearing this bit also deasserts the Asynchronous interrupt to CPU.</li> <li>1 Asynnchronous wake up interrupt occured in stop mode.</li> <li>0 No asynchronous interrupt.</li> </ul>                                        |

| 1<br>CALF        | <ul> <li>Calibration Failed Flag</li> <li>Displays the result of the calibration sequence. The calibration sequence will fail ifHardware Trigger is selected (i.e. ADC_CFG[ADTRG] = 1), or any ADC register is written, or any stop mode is entered before the calibration sequence completes. The CALF bit is cleared by writing a 1 to it.</li> <li>Calibration completed normally.</li> <li>Calibration failed. ADC accuracy specifications are not guaranteed.</li> </ul> |

| 0<br>ADACT       | <ul> <li>Conversion Active</li> <li>Indicates that a conversion or hardware averaging is in progress. ADACT is set when a conversion is initiated and cleared when a conversion is completed or aborted.</li> <li>Conversion not in progress.</li> <li>Conversion in progress.</li> </ul>                                                                                                                                                                                     |

## 13.7.9 Compare value register (ADC\_CV)

Contains compare values used to compare with the conversion result when the compare function is enabled (ADC\_GC[ACFE]=1). The compare values are right justified. Therfore, the compare function only uses the compare value register bits that are related to the ADC mode of operation. (e.g. in 8 bit mode,  $CV1 = ADC_CV[7:0]$  and  $CV2 = ADC_CV[23:16]$ , similarly in 10 bit mode,  $CV1 = ADC_CV[9:0]$  and  $CV2 = ADC_CV[25:16]$  etc.) The compare value 2 in this register is utilized only when the compare range function is enabled (ADC\_GC[ACREN]=1).

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6  | 5  | 4 | 3 | 2 | 1 | 0 |

|-------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|----|----|---|---|---|---|---|

| R     |    | (  | )  |    |    |    |    |    |    | C١ | /2 |    |    |    |    |    |    | (  | )  |    |    |    |   |   |   | C١ | /1 |   |   |   |   |   |

| W     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |    |    |   |   |   |   |   |

| Reset | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0  | 0  | 0 | 0 | 0 | 0 | 0 |

Address: 0h base + 38h offset = 38h

| Field             | Description                                                                                                                                                                                |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–28<br>Reserved | This read-only field is reserved and always has the value 0.                                                                                                                               |

| 27–16<br>CV2      | Compare Value 2<br>Contains a compare value used to compare with the conversion result when the compare function and compare range function are enabled (ADC_GC[ACFE]=1, ADC_GC[ACREN]=1). |

| 15–12<br>Reserved | This read-only field is reserved and always has the value 0.                                                                                                                               |

| CV1               | Compare Value 1<br>Contains a compare value used to compare with the conversion result when the compare function ais enabled (ADC_GC[ACFE]=1).                                             |

### ADC\_CV field descriptions

## 13.7.10 Offset correction value register (ADC\_OFS)

Contains the user-defined offset error correction value. This register is 13 bits wide. The value in the most significant bit (13th bit) is the operation bit. If this bit is '0' then the value in the other 12 bits is added with the converted result value to generate final result to be loaded into ADC\_Rn; if this bit is '1' then this field is subtracted from converted value to generate final result (ADC\_Rn).