Excerpt from i.MX 7 Dual Applications Processor Reference Manual

## 6.2.4.3 Power mode transitions

## Table 6-8. Power mode transitions

| Power mode                     | Configuration with external PMIC                                                                                                                                                                                                          | Configuration with internal PMIC                                                                                                                                                                                                                                 |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ON, first time                 | <ol> <li>Either coin cell or SoC power supply is<br/>connected to SNVS.</li> <li>When button is pressed, PMIC powers<br/>on.</li> </ol>                                                                                                   | <ol> <li>Either coin cell or SoC power supply is<br/>connected to SNVS.</li> <li>When button is pressed, 'state' goes ON,<br/>PMIC_ON_REQ goes '1'.</li> <li>External regulator is enabled.</li> </ol>                                                           |

| Normal ON to OFF,<br>by button | <ol> <li>Button is pressed for a short duration on<br/>the external PMIC.</li> <li>Interrupt request (irq) is sent to SoC from<br/>external PMIC.</li> <li>SoC is programming PMIC for power off<br/>when standby is asserted.</li> </ol> | <ol> <li>SoC button is pressed for a short duration.</li> <li>Interrupt request (irq) is sent to SoC from FSM.</li> <li>Alarm timer is set up by software routine and<br/>started.</li> <li>Upon alarm_in assertion to '1',<br/>PMIC_ON_REQ goes '0'.</li> </ol> |

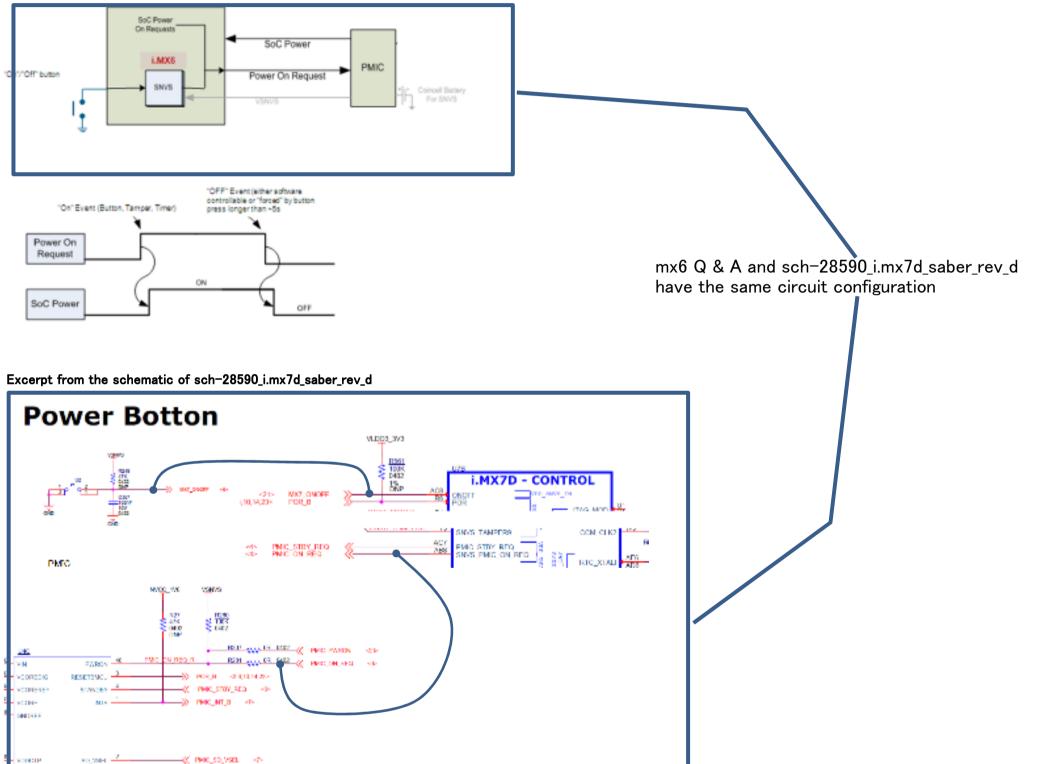

## Excerpt from Q&A: How is mx6 PMIC\_ON\_REQ under SW control?