# **PCI Express Test Report**

**Overall Result: PASS**

| Test Configuration Details |                                |  |  |  |  |

|----------------------------|--------------------------------|--|--|--|--|

| Device Description         |                                |  |  |  |  |

| Device ID                  | Device 1                       |  |  |  |  |

| Preset Type                | None                           |  |  |  |  |

| Test Session Details       |                                |  |  |  |  |

| Infiniium SW Version       | 04.20.0008                     |  |  |  |  |

| Infiniium Model Number     | DSO91304A                      |  |  |  |  |

| Infiniium Serial Number    | MY50140158                     |  |  |  |  |

| Application SW Version     | 3.34                           |  |  |  |  |

| Debug Mode Used            | No                             |  |  |  |  |

| Last Test Date             | 2015-01-13 17:03:16 UTC +02:00 |  |  |  |  |

# **Summary of Results**

| Test Statistics |    |  |  |  |  |

|-----------------|----|--|--|--|--|

| Failed          | 0  |  |  |  |  |

| Passed          | 17 |  |  |  |  |

| Total           | 17 |  |  |  |  |

| Margin Thresholds |       |  |  |  |  |

|-------------------|-------|--|--|--|--|

| Warning           | < 2 % |  |  |  |  |

| Critical          | < 0 % |  |  |  |  |

| Pass        | #<br>Failed | #<br>Trials | Test Name                                                                   | Actual<br>Value | Margin     | Pass Limits                            |

|-------------|-------------|-------------|-----------------------------------------------------------------------------|-----------------|------------|----------------------------------------|

| <b>✓</b>    | 0           | 1           | System Board Tx, Unit Interval (PCIE 1.1)                                   | 400.0730 ps     | 19.6 %     | 399.8800 ps <= VALUE <=<br>400.1200 ps |

| <b>✓</b>    | 0           | 1           | System Board Tx, Template Tests (PCIE 1.1)                                  | Pass            | 100.0<br>% | Pass/Fail                              |

| >           | 0           | 1           | System Board Tx, Median to Max Jitter (PCIE 1.1)                            | 26.94 ps        | 65.0 %     | VALUE <= 77.00 ps                      |

| 1           | 0           | 1           | System Board Tx, Eye-Width (PCIE 1.1)                                       | 333.89 ps       | 35.7 %     | VALUE >= 246.00 ps                     |

| <b>&gt;</b> | 0           | 1           | System Board Tx, Peak Differential Output Voltage (Transition)(PCIE 1.1)    | 665.8 mV        | 42.3 %     | 274.0 mV <= VALUE <= 1.2000<br>V       |

| 1           | 0           | 1           | System Board Tx, Peak Differential Output Voltage (NonTransition)(PCIE 1.1) | 683.4 mV        | 45.4 %     | 253.0 mV <= VALUE <= 1.2000<br>V       |

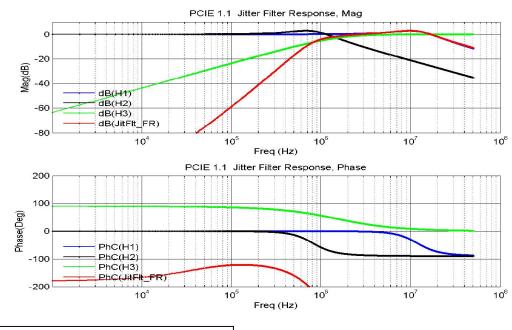

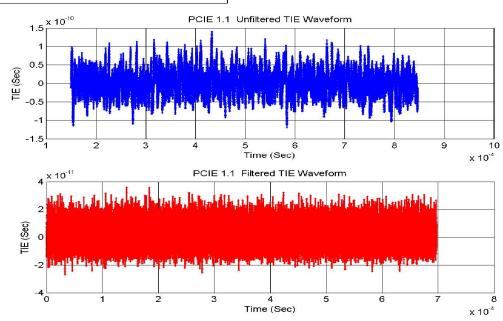

| /           | 0           | 1           | Reference Clock, Phase Jitter (PCIE 1.1)                                    | 63.04 ps        | 26.7 %     | VALUE <= 86.00 ps                      |

| <b>√</b>    | 0           | 1           | Reference Clock, Rising Edge Rate (PCIE 1.1)                                | 750 mV/ns       | 4.4 %      | 600 mV/ns <= VALUE <= 4.00<br>V/ns     |

| <b>✓</b>    | 0           | 1           | Reference Clock, Falling Edge Rate (PCIE 1.1)                               | 770 mV/ns       | 5.0 %      | 600 mV/ns <= VALUE <= 4.00<br>V/ns     |

| 1           | 0           | 1           | Reference Clock, Differential Input High Voltage (PCIE 1.1)                 | 291 mV          | 94.0 %     | VALUE >= 150 mV                        |

| 1           | 0           | 1           | Reference Clock, Differential Input Low Voltage (PCIE 1.1)                  | -296 mV         | 97.3 %     | VALUE <= -150 mV                       |

| >           | 0           | 1           | Reference Clock, Average Clock Period (PCIE 1.1)                            | 77 ppm          | 37.2 %     | -300 ppm <= VALUE <= 300<br>ppm        |

| 1           | 0           | 1           | Reference Clock, Duty Cycle (PCIE 1.1)                                      | 51.0 %          | 45.0 %     | 40.0 % <= VALUE <= 60.0 %              |

| 1           | 0           | 1           | Reference Clock, Variation of VCross (PCIE 1.1)                             | 33.8 mV         | 75.9 %     | VALUE <= 140.0 mV                      |

| 1           | 0           | 1           | Reference Clock, Absolute Max Input Voltage (PCIE 1.1)                      | 233.5 mV        | 79.7 %     | VALUE <= 1.1500 V                      |

| 1           | 0           | 1           | Reference Clock, Absolute Min Input Voltage (PCIE 1.1)                      | -68.3 mV        | 77.2 %     | VALUE >= -300.0 mV                     |

| 1           | 0           | 1           | Reference Clock, Rise-Fall Matching (PCIE 1.1)                              | 7.15 %          | 64.3 %     | VALUE <= 20.00 %                       |

### **Report Detail**

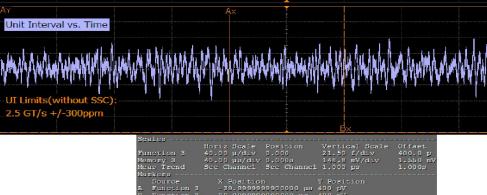

### System Board Tx, Unit Interval (PCIE 1.1) Reference: This test is not required. It is informative only Test Description: A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. The worst case Test Summary: recovered TX UI is reported here. The UI range is NOT specified for this test point. It is provided here as informative data only. Pass Limits: [399.8800 ps to 400.1200 ps] Worst Case UI (ps) 400.0730 ps **Result Details** Data Lane (no value) Note: Non-SSC Limits Used: 2.5 GT/s +/-300ppm #3500 UI Blocks Measured 996.417 k Min UI 399.9870 ps Max UI 400.0730 ps Mean UI 400.0330 ps Worst Case Data Rate 2.499543833250 Gbits/sec Mean Data Rate 2.499793767014 Gbits/sec Connection Type Chan 1,3 - 2 Single Ended Probes Trial 1 Trial 1: Mean Data Rate

Top Previous Next

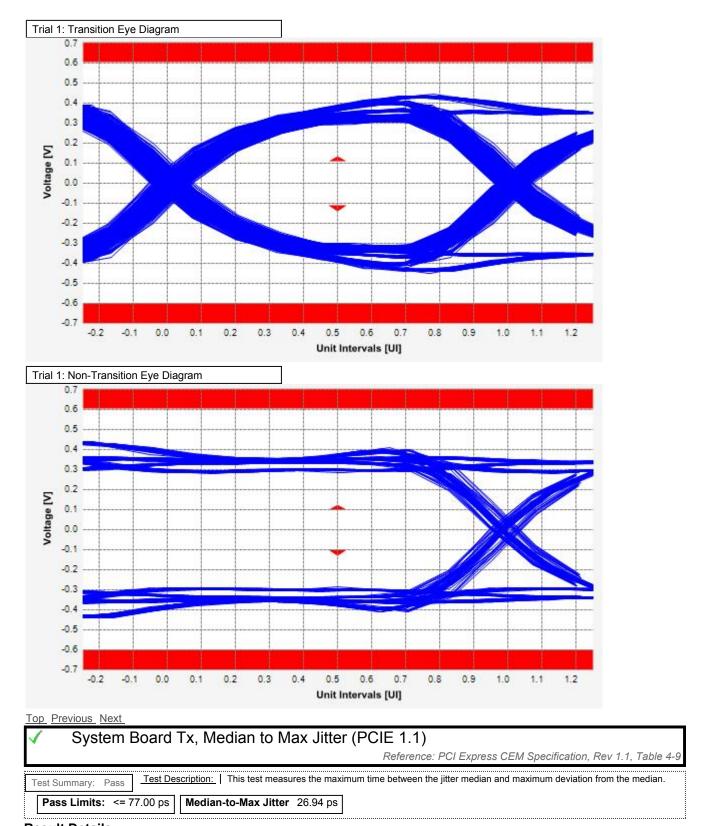

# System Board Tx, Template Tests (PCIE 1.1)

Reference: PCI Express CEM Specification, Rev 1.1, Section 4.7.3, Figure 4-10

Test Summary: Pass Test Description: System boards must meet the System Board Transmitter Path Compliance Eye Requirements specified in table 4-8 of section 4.7.3 of the PCI Express Card Electromechanical (CEM) Specification, Rev 1.1, as measured after the connector with an ideal load.

Pass Limits: Pass/Fail Total # Failures Pass

### **Result Details**

Transition Eye Diagram

(See image)

Transition Failures

0.000

Non-Transition Eye Diagram

(See image)

Non-Transition Failures

0.000

Total #UI Measured

1.000000000 M

Reference Clock

Clean

Data Lane

(no value)

Requested Sample Rate (GSa/s)

20.0

**Result Details**

Data Lane (no value) Connection Type Chan 1,3 - 2 Single Ended Probes

Top Previous Next

System Board Tx, Eye-Width (PCIE 1.1)

Reference: PCI Express CEM Specification, Rev 1.1, Table 4-9

Test Summary: Pass Test Description: This test measures the eye-width of the compliance eye. The eye-width is computed as the [mean unit interval] - [peak-to-peak jitter].

Pass Limits: >= 246.00 ps Eye-Width 333.89 ps

#### **Result Details**

Data Lane (no value) Connection Type Chan 1,3 - 2 Single Ended Probes

Top Previous Next

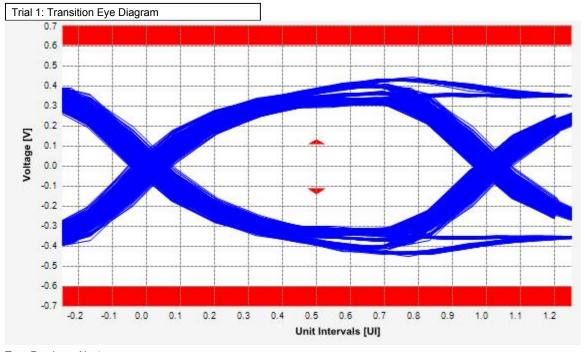

# System Board Tx, Peak Differential Output Voltage (Transition)(PCIE 1.1)

Reference: PCI Express CEM Specification, Rev 1.1, Table 4-5

Test Summary: Pass Test Description: This test verifies that the Differential Peak Differential Output Voltage for transition bits is within the allowed range.

Pass Limits: [274.0 mV to 1.2000 V] PeakVoltage 665.8 mV

#### **Result Details**

Total #UI Measured 1.000000000 M | Largest Transition Amplitude (Outer eye) 892.3 mV

Smallest Transition Amplitude (Inner eye) 592.8 mV Data Lane (no value) Transition Eye Diagram (See image)

Connection Type Chan 1,3 - 2 Single Ended Probes

#### Trial 1

Top Previous Next

# System Board Tx, Peak Differential Output Voltage (NonTransition)(PCIE 1.1)

Reference: PCI Express CEM Specification, Rev 1.1, Table 4-

Test Summary: Pass Test Description: This test verifies that the Differential Peak Differential Output Voltage for non transition bits is within the allowed range.

Pass Limits: [253.0 mV to 1.2000 V] PeakVoltage 683.4 mV

#### **Result Details**

Total #UI Measured 1.000000000 M Largest Non Transition Amplitude (Outer eye) 819.3 mV

Connection Type Chan 2,4 - 2 Single Ended Probes

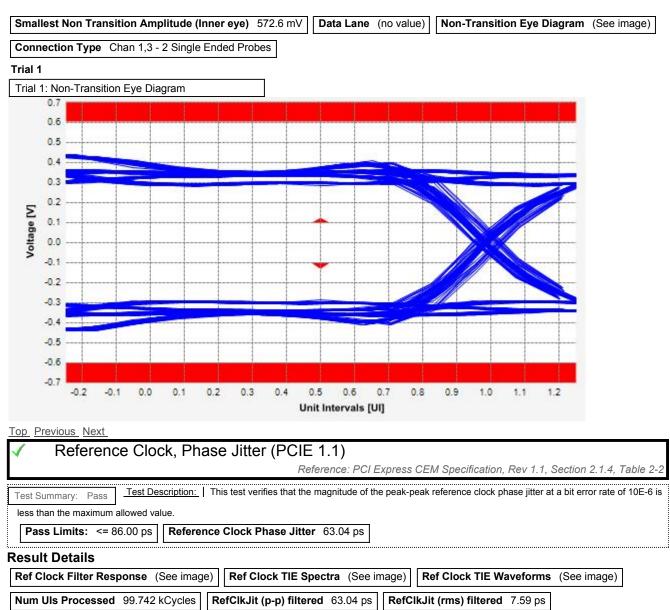

### Trial 1: Ref Clock TIE Spectra

Top Previous Next

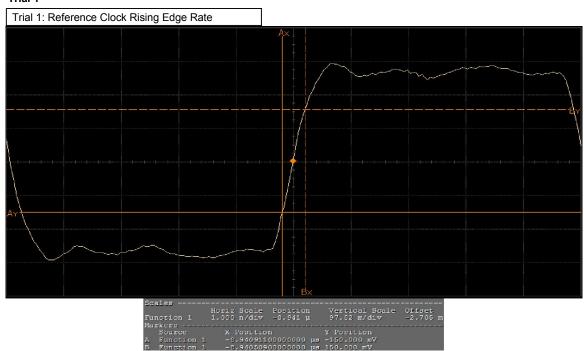

# Reference Clock, Rising Edge Rate (PCIE 1.1)

Reference: PCI Express CEM Specification, Rev 1.1, Section 2.1.3, Table 2-7

Test Summary: Pass Test Description: This test verifies that the rising edge rate of the waveform is within the allowed range. The value is measured from -150mV to +150mV on the differential waveform and the measurement window is centered on the differential zero crossing.

Pass Limits: [600 mV/ns to 4.00 V/ns] | Reference Clock Rising Edge Rate 750 mV/ns

#### **Result Details**

Connection Type Chan 2,4 - 2 Single Ended Probes

### Trial 1

Top Previous Next

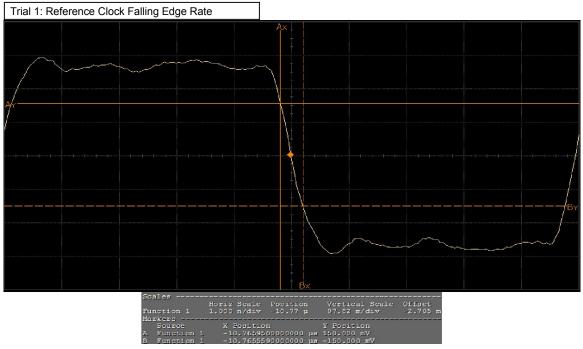

### Reference Clock, Falling Edge Rate (PCIE 1.1)

Reference: PCI Express CEM Specification, Rev 1.1, Section 2.1.3, Table 2-7

Test Summary: Pass Test Description: This test verifies that the falling edge rate of the waveform is within the allowed range. The value is measured from -150mV to +150mV on the differential waveform and the measurement window is centered on the differential zero crossing.

Pass Limits: [600 mV/ns to 4.00 V/ns] | Reference Clock Falling Edge Rate 770 mV/ns

#### **Result Details**

**Connection Type** Chan 2,4 - 2 Single Ended Probes

#### Trial 1

Top Previous Next

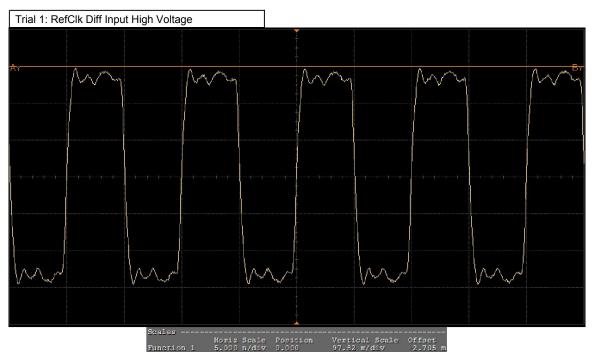

# Reference Clock, Differential Input High Voltage (PCIE 1.1)

Reference: PCI Express CEM Specification, Rev 1.1, Section 2.1.3, Table 2-1

Test Summary: Pass Test Description: This test verifies that the high voltage of the reference clock differential waveform is greater than the minimum allowed value.

Pass Limits: >= 150 mV RefClk Diff Input High Voltage 291 mV

### **Result Details**

Connection Type Chan 2,4 - 2 Single Ended Probes

Top Previous Next

# Reference Clock, Differential Input Low Voltage (PCIE 1.1)

Reference: PCI Express CEM Specification, Rev 1.1, Section 2.1.3, Table 2-1

Test Summary: Pass

allowed value.

Pass Limits: <= -150 mV

Test Description: | This test verifies that the low voltage of the reference clock differential waveform is less than the maximum reference clock differential waveform is less than the maximum reference clock differential waveform is less than the maximum reference clock differential waveform is less than the maximum reference clock differential waveform is less than the maximum reference clock differential waveform is less than the maximum reference clock differential waveform is less than the maximum reference clock differential waveform is less than the maximum reference clock differential waveform is less than the maximum reference clock differential waveform is less than the maximum reference clock differential waveform is less than the maximum reference clock differential waveform is less than the maximum reference clock differential waveform is less than the maximum reference clock differential waveform is less than the maximum reference clock differential waveform is less than the maximum reference clock differential waveform is less than the maximum reference clock differential waveform is less than the maximum reference clock differential waveform is less than the maximum reference clock difference clock dif

### **Result Details**

Connection Type Chan 2,4 - 2 Single Ended Probes

#### Trial 1

Top Previous Next

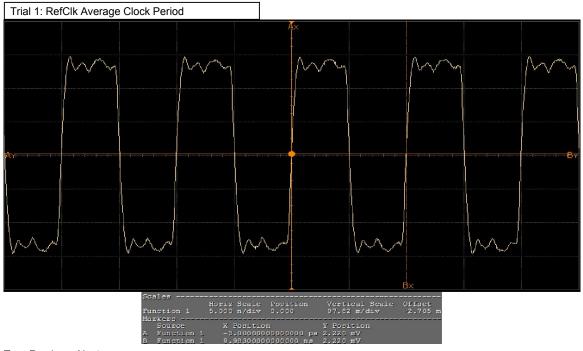

### Reference Clock, Average Clock Period (PCIE 1.1)

Reference: PCI Express CEM Specification, Rev 1.1, Section 2.1.3, Table 2-7

Test Summary: Pass Test Description: The average clock period accuracy of the differential waveform is measured in PPM (parts per million) where 1

PPM equals 100Hz. A requirement of +/- 300 PPM applies to systems that do NOT employ SSC or that use a common clock source. For systems employing SSC there is an additional 2500 PPM nominal shift in the maximum period resulting in a maximum average period specification of +2800 PPM.

Pass Limits: [-300 ppm to 300 ppm] RefClk Average Clock Period 77 ppm

#### **Result Details**

Average Clock Frequency 99.992280200000 MHz Average Clock Period 10.00078570 ns

Note: Non-SSC Limits Used: 100MHz +/-300ppm Connection Type Chan 2,4 - 2 Single Ended Probes

#### Trial 1

Top Previous Next

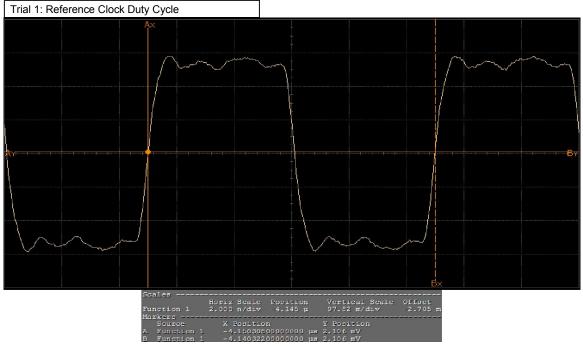

# Reference Clock, Duty Cycle (PCIE 1.1)

Reference: PCI Express CEM Specification, Rev 1.1, Section 2.1.3, Table 2-1

Test Summary: Pass Test Description: This test verifies that the duty cycle of the reference clock differential waveform is within the allowed range.

Pass Limits: [40.0 % to 60.0 %] Reference Clock Duty Cycle 51.0 %

#### **Result Details**

Duty Cycle Mean50.7 %Duty Cycle Min50.3 %Duty Cycle Max51.0 %

Connection Type Chan 2,4 - 2 Single Ended Probes

Top Previous Next

### Reference Clock, Variation of VCross (PCIE 1.1)

Reference: PCI Express CEM Specification, Rev 1.1, Section 2.1.3, Table 2-1

Test Summary: Pass Test Description: This test verifies that the variation of VCross over all rising clock edges is within the allowed range.

Pass Limits: <= 140.0 mV VCross Delta 33.8 mV

#### **Result Details**

Rising Edge VCross Max 97.2 mV | Rising Edge VCross Min 63.4 mV | Connection Type Chan 2,4 - 2 Single Ended Probes

Top Previous Next

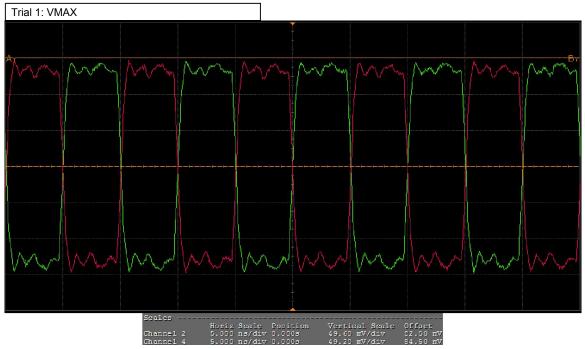

# Reference Clock, Absolute Max Input Voltage (PCIE 1.1)

Reference: PCI Express CEM Specification, Rev 1.1, Section 2.1.3, Table 2-1

Test Summary: Pass Test Description: This test verifies that the absolute maximum input voltage of the reference clock is within the allowed range.

Pass Limits: <= 1.1500 V VMAX 233.5 mV

### **Result Details**

REFCLK+ VMax 230.7 mV REFCLK- VMin 233.5 mV Connection Type Chan 2,4 - 2 Single Ended Probes

Top Previous Next

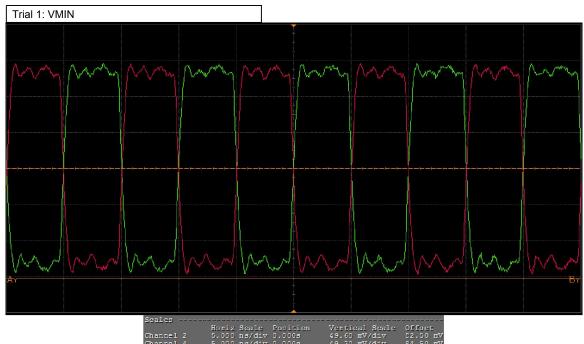

# Reference Clock, Absolute Min Input Voltage (PCIE 1.1)

Reference: PCI Express CEM Specification, Rev 1.1, Section 2.1.3, Table 2-1

Test Summary: Pass Test Description: | This test verifies that the absolute minimum input voltage of the reference clock is within the allowed range.

Pass Limits: >= -300.0 mV VMIN -68.3 mV

#### **Result Details**

REFCLK+ VMin -68.3 mV REFCLK- VMin -65.1 mV Connection Type Chan 2,4 - 2 Single Ended Probes

#### Trial 1

Top Previous Next

Reference Clock, Rise-Fall Matching (PCIE 1.1)

Top Previous