# **PCI Express Test Report**

Overall Result: PASS

| Test Configuration Details |                                |  |  |  |  |  |

|----------------------------|--------------------------------|--|--|--|--|--|

| Device Description         |                                |  |  |  |  |  |

| Device ID                  | evice ID Device 1              |  |  |  |  |  |

| Preset Type                | None                           |  |  |  |  |  |

| Test Session Details       |                                |  |  |  |  |  |

| Infiniium SW Version       | 04.20.0008                     |  |  |  |  |  |

| Infiniium Model Number     | DSO91304A                      |  |  |  |  |  |

| Infiniium Serial Number    | MY50140158                     |  |  |  |  |  |

| Application SW Version     | 3.34                           |  |  |  |  |  |

| Debug Mode Used            | No                             |  |  |  |  |  |

| Last Test Date             | 2015-01-28 13:44:03 UTC +02:00 |  |  |  |  |  |

### **Summary of Results**

| Test Statistics |    |  |  |  |  |

|-----------------|----|--|--|--|--|

| Failed          | 0  |  |  |  |  |

| Passed          | 16 |  |  |  |  |

| Total           | 16 |  |  |  |  |

| Margin Thresholds |       |  |  |  |  |  |

|-------------------|-------|--|--|--|--|--|

| Warning           | < 2 % |  |  |  |  |  |

| Critical          | < 0 % |  |  |  |  |  |

| Pass     | #<br>Failed | #<br>Trials | Test Name                                                                                  | Actual<br>Value | Margin     | Pass Limits                            |

|----------|-------------|-------------|--------------------------------------------------------------------------------------------|-----------------|------------|----------------------------------------|

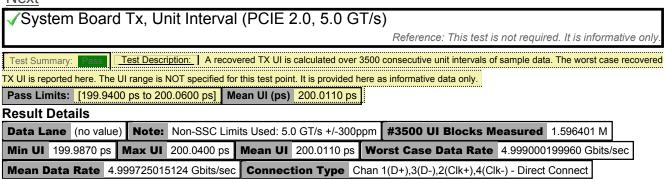

| 1        | 0           | 1           | System Board Tx, Unit Interval (PCIE 2.0, 5.0 GT/s)                                        | 200.0110<br>ps  | 40.8 %     | 199.9400 ps <= VALUE <=<br>200.0600 ps |

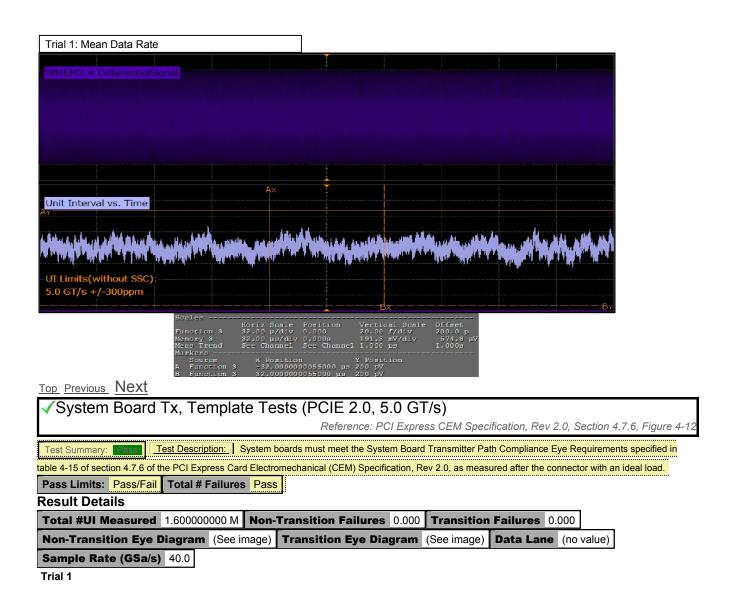

| 1        | 0           | 1           | System Board Tx, Template Tests (PCIE 2.0, 5.0 GT/s)                                       | Pass            | 100.0<br>% | Pass/Fail                              |

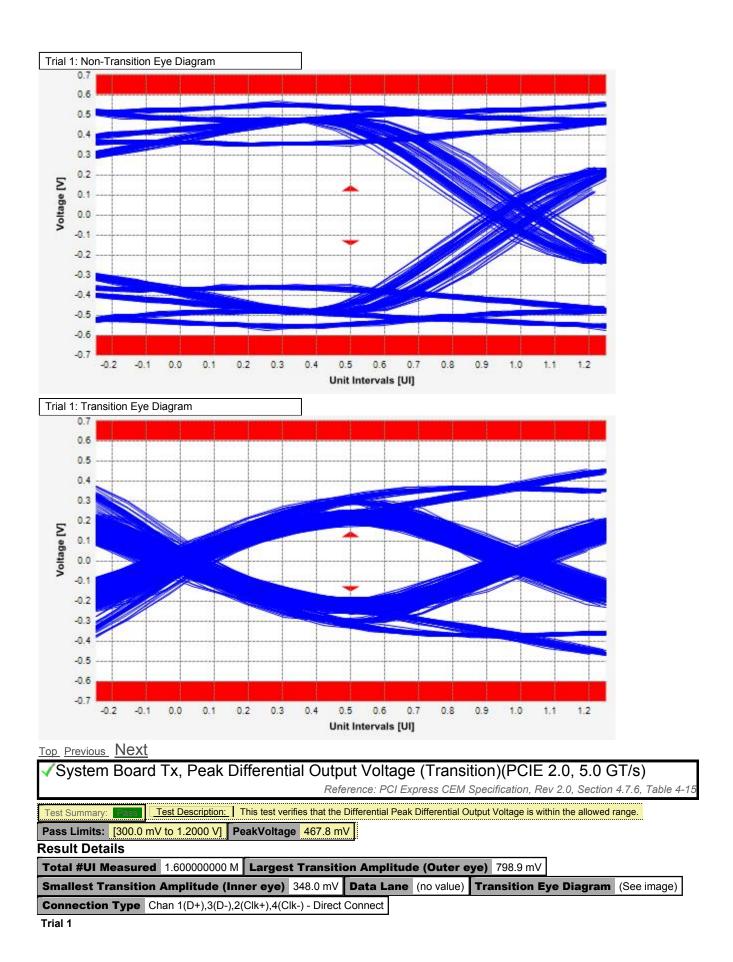

| ✓        | 0           | 1           | System Board Tx, Peak Differential Output Voltage (Transition) (PCIE 2.0, 5.0 GT/s)        | 467.8 mV        |            | 300.0 mV <= VALUE <=<br>1.2000 V       |

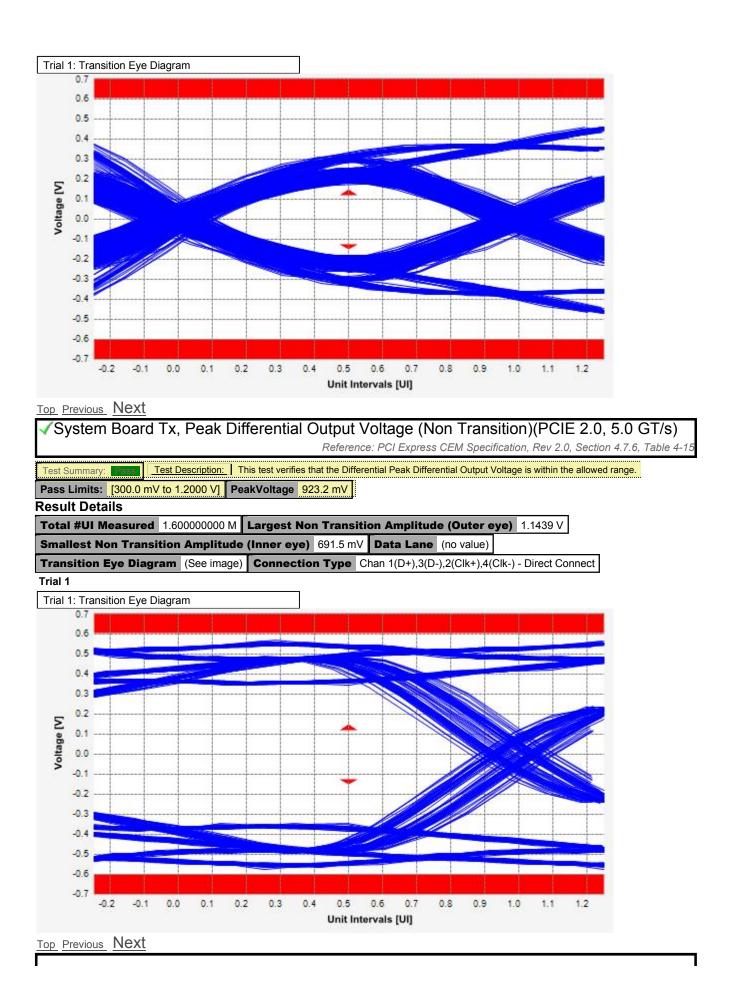

| 1        | 0           | 1           | System Board Tx, Peak Differential Output Voltage (Non Transition)(PCIE 2.0, 5.0 GT/s)     | 923.2 mV        | 30.8 %     | 300.0 mV <= VALUE <=<br>1.2000 V       |

| 1        | 0           | 1           | System Board Tx, Eye-Width with crosstalk (PCIE 2.0, 5.0 GT/s)                             | 133.56 ps       | 40.6 %     | VALUE >= 95.00 ps                      |

| <b>√</b> | 0           | 1           | System Board Tx, RMS Random Jitter with crosstalk (PCIE 2.0, 5.0 GT/s)                     | 3.006 ps        | 93.7 %     | VALUE <= 48.000 ps                     |

| <b>√</b> | 0           | 1           | System Board Tx, Maximum Deterministic Jitter with crosstalk (PCIE 2.0, 5.0 GT/s)          | 24.148 ps       | 57.6 %     | VALUE <= 57.000 ps                     |

| 1        | 0           | 1           | System Board Tx, Total Jitter at BER-12 with crosstalk (PCIE 2.0, 5.0 GT/s)                | 66.443 ps       | 36.7 %     | VALUE <= 105.000 ps                    |

| <b>✓</b> | 0           | 1           | System Board Tx, Eye-Width without crosstalk (PCIE 2.0, 5.0 GT/s)                          | 133.56 ps       | 23.7 %     | VALUE >= 108.00 ps                     |

| 1        | 0           | 1           | System Board Tx, RMS Random Jitter without crosstalk (PCIE 2.0, 5.0 GT/s)                  | 3.006 ps        | 93.7 %     | VALUE <= 48.000 ps                     |

| 1        | 0           | 1           | System Board Tx, Maximum Deterministic Jitter without crosstalk (PCIE 2.0, 5.0 GT/s)       | 24.148 ps       | 45.1 %     | VALUE <= 44.000 ps                     |

| 1        | 0           | 1           | System Board Tx, Total Jitter at BER-12 without crosstalk (PCIE 2.0, 5.0 GT/s)             | 66.443 ps       | 27.8 %     | VALUE <= 92.000 ps                     |

| 1        | 0           | 1           | Reference Clock, High frequency > 1.5MHz RMS Jitter (Common Clk) (PCIE 2.0, 5.0 GT/s)      | 1.77 ps         | 42.9 %     | VALUE <= 3.10 ps                       |

| 1        | 0           | 1           | Reference Clock, Low frequency 10kHz - 1.5MHz RMS Jitter (Common Clk) (PCIE 2.0, 5.0 GT/s) | 480 fs          | 84.0 %     | VALUE <= 3.00 ps                       |

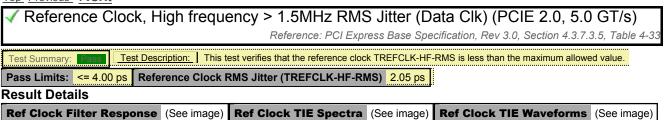

| <b>✓</b> | 0           | 1           | Reference Clock, High frequency > 1.5MHz RMS Jitter (Data Clk) (PCIE 2.0, 5.0 GT/s)        | 2.05 ps         | 48.8 %     | VALUE <= 4.00 ps                       |

| 1        | 0           | 1           | Reference Clock, Low frequency 10kHz - 1.5MHz RMS Jitter (Data Clk) (PCIE 2.0, 5.0 GT/s)   | 460 fs          | 93.9 %     | VALUE <= 7.50 ps                       |

## **Report Detail**

Nevi

Trial 1

```

√System Board Tx, Eye-Width with crosstalk (PCIE 2.0, 5.0 GT/s)

Reference: PCI Express CEM Specification, Rev 2.0, Section 4.7.6, Table 4-1

Test Description: This test measures the eye-width of the compliance eye. The eye-width is computed as the [mean unit interval]

Test Summary:

[peak-to-peak jitter]

Pass Limits: >= 95.00 ps Eye-Width 133.56 ps

Result Details

Total #UI Measured 1.600000000 M TJ at BER-12 66.443 ps

Worst Filter Info PLL Damping Factor = 0.54, PLL Frequency = 16000000Hz Worst Transport Delay 3.0 ns

Data Lane (no value) Connection Type Chan 1(D+),3(D-),2(Clk+),4(Clk-) - Direct Connect

Top Previous Next

√System Board Tx, RMS Random Jitter with crosstalk (PCIE 2.0, 5.0 GT/s)

Reference: This test is not required. It is informative only

<u>Test Description:</u> The RJ(rms) range is NOT specified for this test point. It is provided here as informative data only.

Pass Limits: <= 48.000 ps Rj_rms 3.006 ps

Result Details

Total #UI Measured 1.600000000 M | Worst Filter Info | PLL Damping Factor = 0.54, PLL Frequency = 16000000Hz

Worst Transport Delay 3.0 ns Data Lane (no value) Sample Rate (GSa/s) 40.0

Top Previous Next

✓System Board Tx, Maximum Deterministic Jitter with crosstalk (PCIE 2.0, 5.0 GT/s)

Reference: PCI Express CEM Specification, Rev 2.0, Section 4.7.7, Table 4-16

Test Description: System boards must meet the System Board Transmitter Path Compliance Eye Requirements specified in

table 4-16 of section 4.7.6 of the PCI Express Card Electromechanical (CEM) Specification, Rev 2.0, as measured after the connector with an ideal load.

Pass Limits: <= 57.000 ps | Dj_dd 24.148 ps |

Result Details

Total #UI Measured 1.600000000 M | Worst Filter Info | PLL Damping Factor = 0.54, PLL Frequency = 16000000Hz

Worst Transport Delay 3.0 ns Data Lane (no value) Sample Rate (GSa/s) 40.0

<u>Top Previous Next</u>

✓System Board Tx, Total Jitter at BER-12 with crosstalk (PCIE 2.0, 5.0 GT/s)

Reference: PCI Express CEM Specification, Rev 2.0, Section 4.7.2, Table 4-16

Pass Test Description: | System boards must meet the System Board Transmitter Path Compliance Eye Requirements specified in

table 4-16 of section 4.7.6 of the PCI Express Card Electromechanical (CEM) Specification, Rev 2.0, as measured after the connector with an ideal load.

Pass Limits: <= 105.000 ps Tj at BER 10E-12 66.443 ps

Result Details

Total #UI Measured 1.600000000 M Worst Filter Info PLL Damping Factor = 0.54, PLL Frequency = 16000000Hz

Worst Transport Delay 3.0 ns Data Lane (no value) Sample Rate (GSa/s) 40.0

Top Previous Next

√System Board Tx, Eye-Width without crosstalk (PCIE 2.0, 5.0 GT/s)

Reference: PCI Express CEM Specification, Rev 2.0, Section 4.7.6, Table 4-1

Test Description: This test measures the eye-width of the compliance eye. The eye-width is computed as the [mean unit interval]

Test Summary:

[peak-to-peak jitter]

Pass Limits: >= 108.00 ps Eye-Width 133.56 ps

Result Details

Total #UI Measured 1.600000000 M TJ at BER-12 66.443 ps

Worst Filter Info PLL Damping Factor = 0.54, PLL Frequency = 16000000Hz Worst Transport Delay 3.0 ns

```

```

Data Lane (no value) Connection Type Chan 1(D+),3(D-),2(Clk+),4(Clk-) - Direct Connect

Top Previous Next

√System Board Tx, RMS Random Jitter without crosstalk (PCIE 2.0, 5.0 GT/s)

Reference: This test is not required. It is informative only

Test Description: The RJ(rms) range is NOT specified for this test point. It is provided here as informative data only.

Pass Limits: <= 48.000 ps | Rj_rms | 3.006 ps |

Result Details

Total #UI Measured 1.600000000 M Worst Filter Info PLL Damping Factor = 0.54, PLL Frequency = 16000000Hz

Worst Transport Delay 3.0 ns Data Lane (no value) Sample Rate (GSa/s) 40.0

Top Previous Next

✓System Board Tx, Maximum Deterministic Jitter without crosstalk (PCIE 2.0, 5.0 GT/s)

Reference: PCI Express CEM Specification, Rev 2.0, Section 4.7.6, Table 4-1

Test Description: System boards must meet the System Board Transmitter Path Compliance Eye Requirements specified in

table 4-16 of section 4.7.6 of the PCI Express Card Electromechanical (CEM) Specification, Rev 2.0, as measured after the connector with an ideal load.

Pass Limits: <= 44.000 ps Dj_dd 24.148 ps

Result Details

Total #UI Measured 1.600000000 M | Worst Filter Info | PLL Damping Factor = 0.54, PLL Frequency = 16000000Hz

Worst Transport Delay 3.0 ns Data Lane (no value) Sample Rate (GSa/s) 40.0

Top Previous Next

√System Board Tx, Total Jitter at BER-12 without crosstalk (PCIE 2.0, 5.0 GT/s).

Reference: PCI Express CEM Specification, Rev 2.0, Section 4.7.2, Table 4-16

Test Description: System boards must meet the System Board Transmitter Path Compliance Eye Requirements specified in

table 4-16 of section 4.7.6 of the PCI Express Card Electromechanical (CEM) Specification, Rev 2.0, as measured after the connector with an ideal load.

Pass Limits: <= 92.000 ps Tj at BER 10-12 66.443 ps

Result Details

Total #UI Measured 1.600000000 M Worst Filter Info PLL Damping Factor = 0.54, PLL Frequency = 16000000Hz

Worst Transport Delay 3.0 ns Data Lane (no value) Sample Rate (GSa/s) 40.0

Top Previous Next

✓Reference Clock, High frequency > 1.5MHz RMS Jitter (Common Clk) (PCIE 2.0, 5.0

GT/s)

Reference: PCI Express Base Specification, Rev 3.0, Section 4.3.7.3.3, Table 4-31

<u>Test Description:</u> This test verifies that the reference clock TREFCLK-HF-RMS is less than the maximum allowed value.

Pass Limits: <= 3.10 ps Reference Clock RMS Jitter (TREFCLK-HF-RMS) 1.77 ps

Result Details

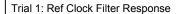

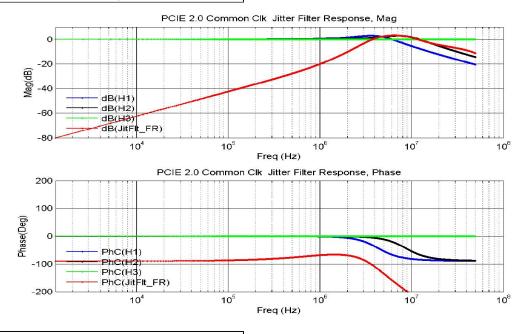

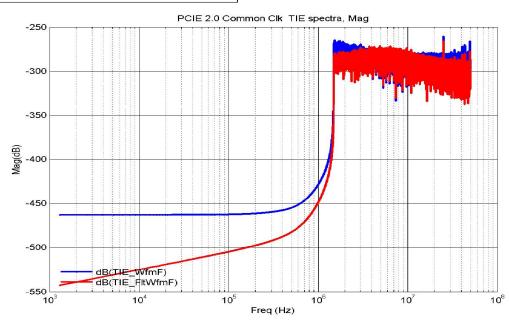

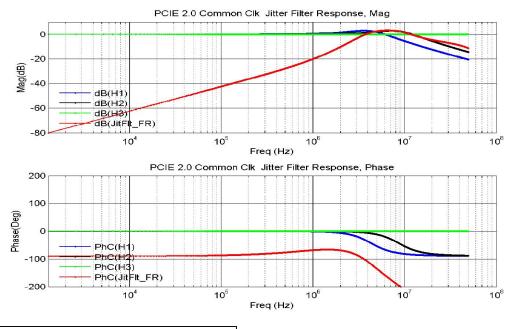

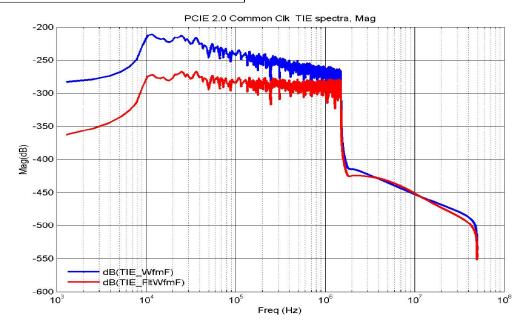

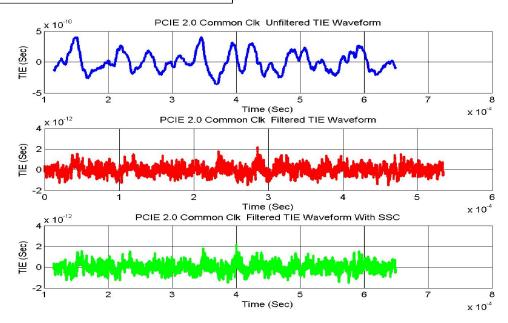

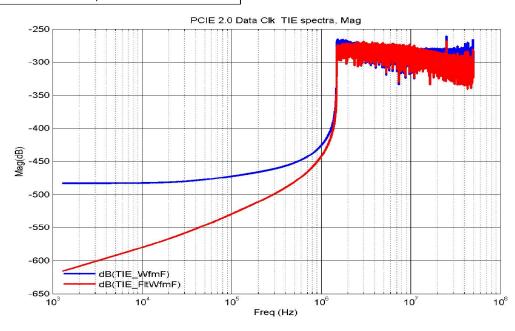

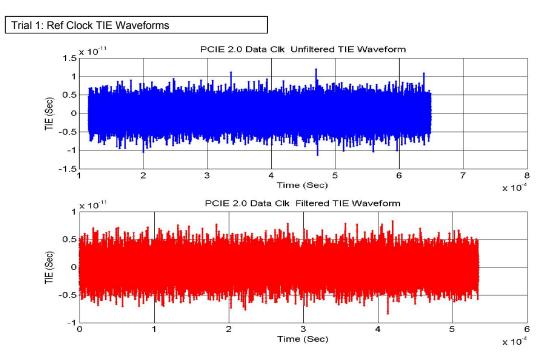

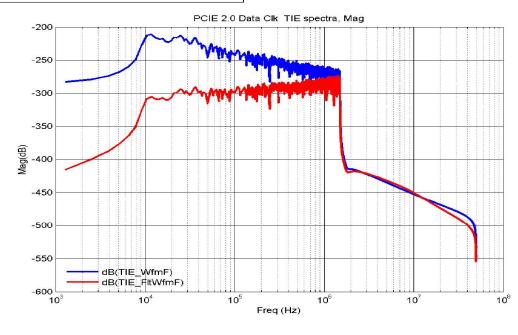

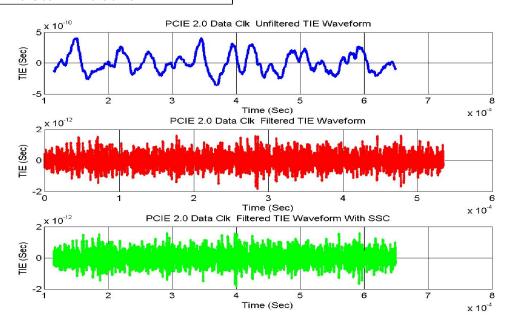

Ref Clock Filter Response (See image) Ref Clock TIE Spectra (See image) Ref Clock TIE Waveforms (See image)

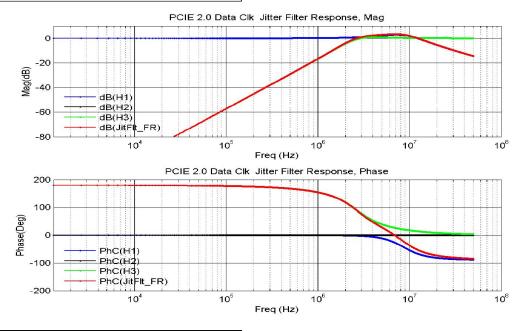

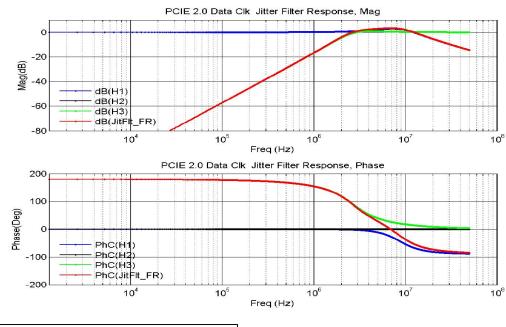

Transfer Function H1: 8MHz, 3.0dB peaking | H2: 16MHz, 3.0dB peaking | Num UIs Processed 95.446 kCycles

RefClkJit (p-p) filtered 14.48 ps RefClkJit (rms) filtered 1.77 ps Connection Type Chan 2,4 - Direct Connect

Trial 1

```

Reference Clock, Low frequency 10kHz - 1.5MHz RMS Jitter (Common Clk) (PCIE 2.0, 5.0 GT/s)

\*\*Reference: PCI Express Base Specification, Rev 3.0, Section 4.3.7.3.3, Table 4-3

\*\*Test Summary: Pass Test Description: This test verifies that the reference clock TREFCLK-LF-RMS is less than the maximum allowed value.

\*\*Pass Limits: <= 3.00 ps Reference Clock RMS Jitter (TREFCLK-LF-RMS) 480 fs Result Details

\*\*Ref Clock Filter Response\*\* (See image) Ref Clock TIE Spectra\*\* (See image) Ref Clock TIE Waveforms\*\* (See image) Transfer Function H1: 8MHz, 3.0dB peaking | H2: 16MHz, 3.0dB peaking | Num Uls Processed 95.446 kCycles RefClkJit (p-p) filtered 3.74 ps RefClkJit (rms) filtered 480 fs Connection Type Chan 2,4 - Direct Connect Trial 1

Top Previous Next

Num Uls Processed 95.446 kCycles RefClkJit (p-p) filtered 16.70 ps RefClkJit (rms) filtered 2.05 ps

Connection Type Chan 2,4 - Direct Connect

Trial 1

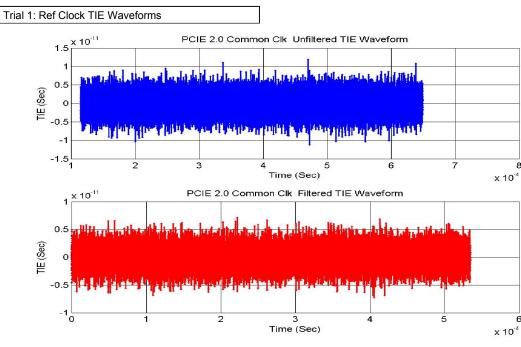

#### Trial 1: Ref Clock Filter Response

Reference Clock, Low frequency 10kHz - 1.5MHz RMS Jitter (Data Clk) (PCIE 2.0, 5.0 GT/s)

Reference: PCI Express Base Specification, Rev 3.0, Section 4.3.7.3.5, Table 4-33

Test Summary: Pass Test Description: This test verifies that the RMS reference clock phase jitter at a bit error rate of 10E-6 is less than the maximum allowed value.

Pass Limits: <= 7.50 ps Reference Clock RMS Jitter (TREFCLK-LF-RMS) 460 fs

Result Details

Ref Clock Filter Response (See image) Ref Clock TIE Spectra (See image) Ref Clock TIE Waveforms (See image)

Num Uls Processed 95.446 kCycles RefClkJit (p-p) filtered 3.46 ps RefClkJit (rms) filtered 460 fs

Connection Type Chan 2,4 - Direct Connect

Trial 1

#### Trial 1: Ref Clock TIE Waveforms

Top Previous