# THE INS AND OUTS OF I<sup>2</sup>C BUS BUFFERS

### **TF-DES-N1916**

EMMANUEL NANA FTF-DES-N1916 JUNE 7, 2016

PUBLIC USE

# AGENGA

- History of I<sup>2</sup>C BUS

- General I<sup>2</sup>C BUS Protocol and transaction

- What is a I<sup>2</sup>C BUS Buffer

- Why I<sup>2</sup>C BUS Buffer is needed

- How to use a I<sup>2</sup>C BUS Buffer

### History of I<sup>2</sup>C BUS

- The I<sup>2</sup>C BUS was developed in the early 1982 by Philips Semiconductors (now NXP Semiconductors). Its original purpose was to provide an easy way to connect a CPU to peripheral chips in a TV-set

- 1992 Philips Semiconductor released the I<sup>2</sup>C BUS Specification Version 1.0

East mode (Em), with I<sup>2</sup>C transfere rate up to 400 Kbit/a

- Fast-mode (Fm) with I<sup>2</sup>C transfers rate up to 400 Kbit/s

- -7-bit addressing and 10-bit addressing to allow additional 1024 slave addresses

- 1998 Philips Semiconductor released the I<sup>2</sup>C BUS Specification Version 2.0

High-speed mode (Hs) with I<sup>2</sup>C transfers rate up to 3.4 Mbit/s

- 2006, Philips Semiconductors CEO Frans van Houten revealed that the company will move forward as NXP Semiconductors

- I<sup>2</sup>C specification were published under NXP Semiconductors

### History of I<sup>2</sup>C BUS

- 2007 NXP Semiconductors released the Version 3 of I<sup>2</sup>C specification

Fast-mode Plus (Fm+) with I<sup>2</sup>C transfers rate up to 1 Mbit/s.

- 2013, NXP Semiconductors released the I<sup>2</sup>C BUS Specification Version 4

Ultra Fast-mode (UFm) speed up to 5 Mbit/s

- Today, the I<sup>2</sup>C BUS is used in many other application fields than just audio and video equipment. The bus is generally accepted in the industry as a de-facto standard

- Latest version of the I<sup>2</sup>C BUS Specification is 6. Download at NXP website: <u>http://www.nxp.com/documents/user\_manual/um10204.pdf</u>

### General I<sup>2</sup>C BUS Protocol and Transaction

- I<sup>2</sup>C BUS can have:

- Multiple masters

- Multiple slaves

- Only one master talks to one slave at a time

- All the slaves on the same bus must have different address

- Slow speed device cannot understand higher speed transfer

### **General I<sup>2</sup>C BUS Protocol and Transaction**

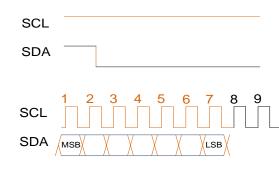

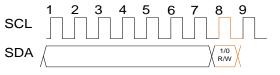

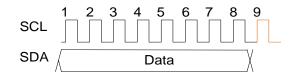

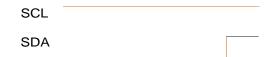

#### I<sup>2</sup>C BUS constructs off 9 bit block

START condition: When SCL is HIGH then SDA goes from HIGH to LOW

Address bit 7 bit after START condition

Read or Write bit After 7 bit address, the  $8^{th}$  bit is Read or Write bit. 1 = Read cycle or 0 = Write cycle

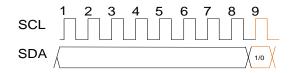

ACK Synchronization bit between master and slave 0 = ACK and 1 = NACK

#### Data Byte

8-bit after address byte is data byte from master or slave

STOP condition: When clock line (SCL) is HIGH then the data line (SDA) goes LOW to HIGH

All slaves on this bus pay attention !!!

Master wants to talk slave with this address

Master wants to read or write 0: Write cycle 1: Read cycle

Slave or master: 0: I am here or data received 1: not me or data not received

Data byte Master sends data when write cycle Slave sends data when read cycle

Master notifies the slave this is the end of transaction

5 PUBLIC USE FTF-DES-N1916

### **General I<sup>2</sup>C BUS Protocol and Transaction**

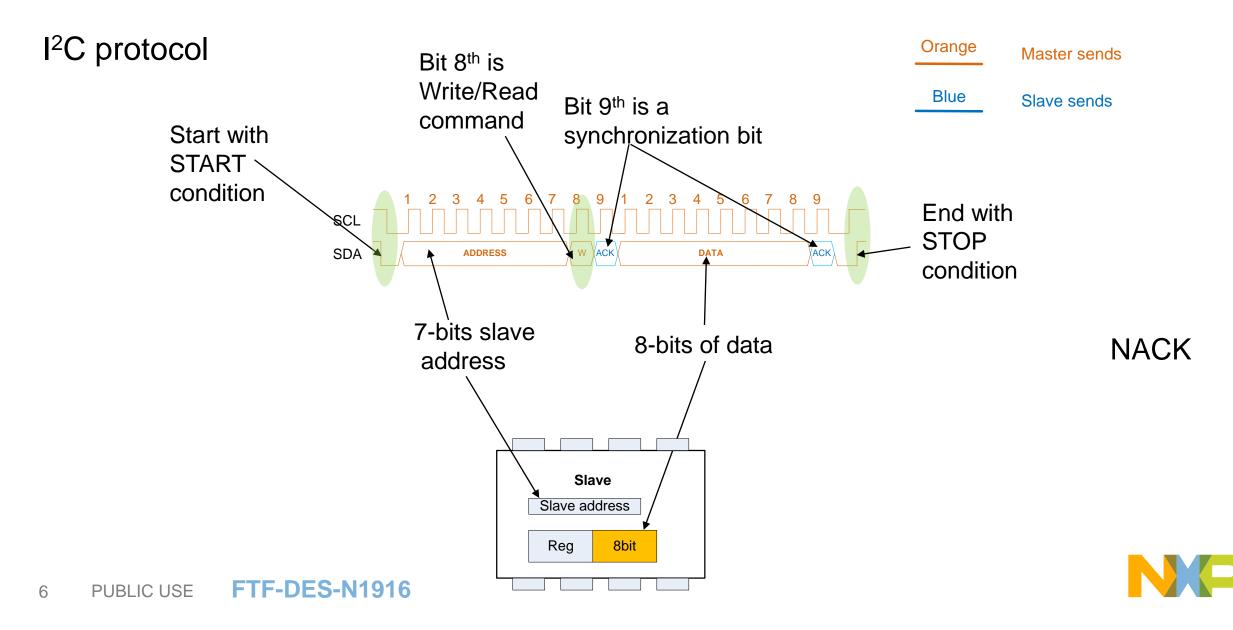

Bus buffer is for:

Divide Capacitive load of I<sup>2</sup>C BUS in half (Bus isolation)

### Bus buffer is for:

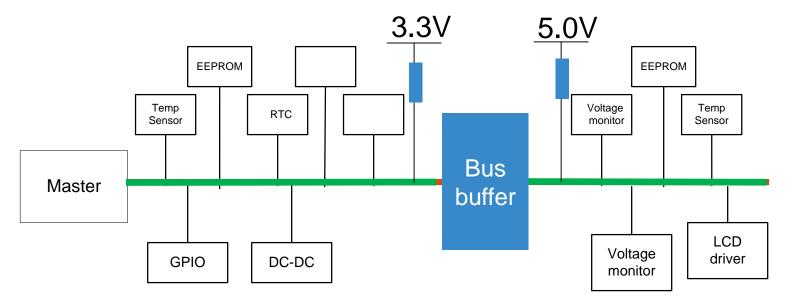

- Divide Capacitive load of I<sup>2</sup>C BUS in half (Bus isolation)

- Connect two different bus voltage together (Level translation)

- Voltage range from 0.8 V to 5.5V

### Bus buffer is for:

- Divide Capacitive load of I<sup>2</sup>C BUS in half (Bus isolation)

- Connect two different bus voltage together (Level translation)

- Voltage range from 0.8 V to 5.5V

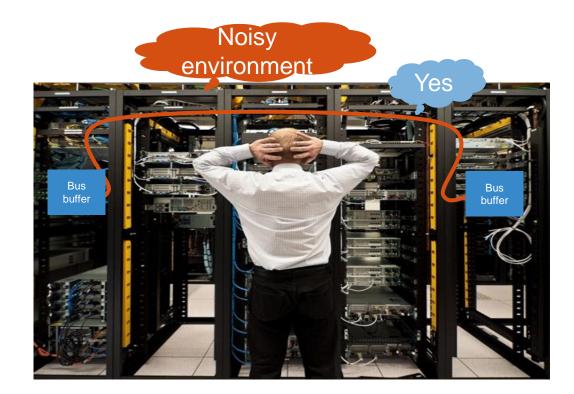

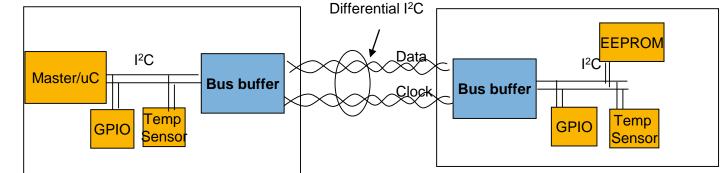

- Increate long range connection (Extend longer bus)

### **DVDR/STB**

### Bus buffer is for:

- Divide Capacitive load of I<sup>2</sup>C BUS in half (Bus isolation)

- Connect two different bus voltage together (Level translation)

- Voltage range from 0.8 V to 5.5V

- Increate long range connection (Extend longer bus)

- Avoid system noise (differential I<sup>2</sup>C BUS)

### Why I<sup>2</sup>C BUS Buffer Is Needed?

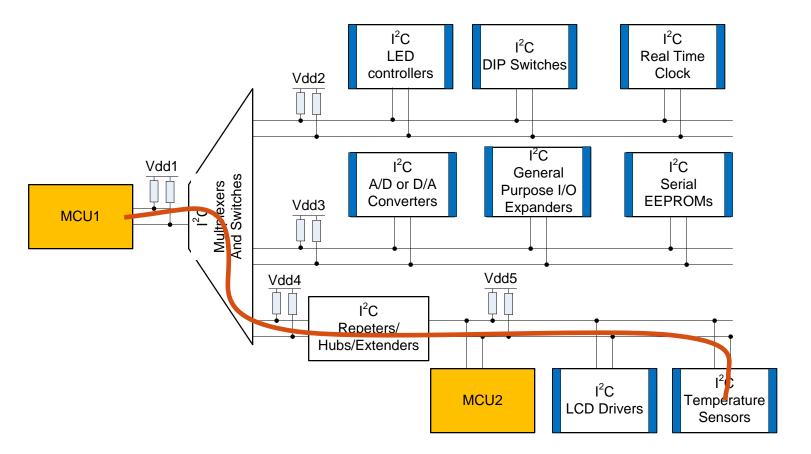

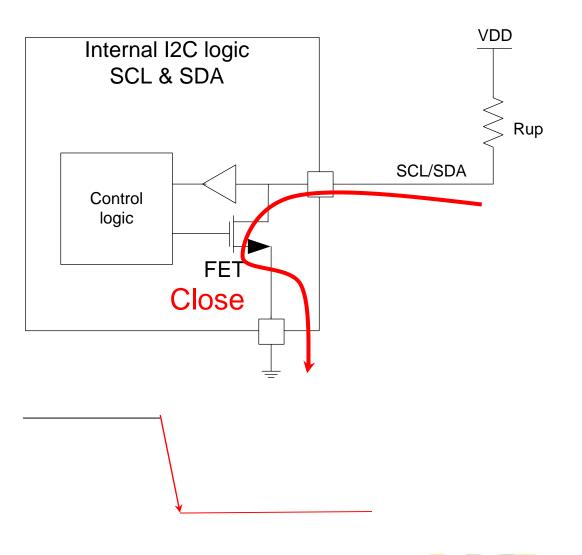

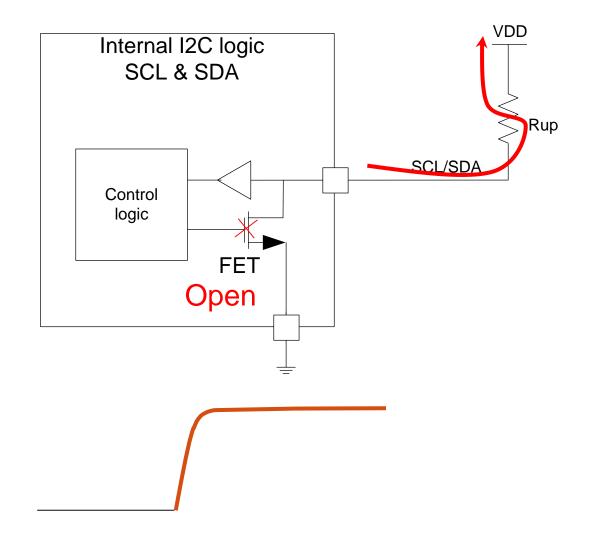

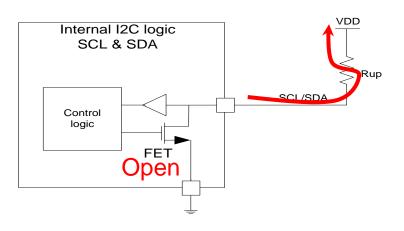

I<sup>2</sup>C internal block diagram

How I<sup>2</sup>C BUS works

When master or slave output LOW:

- FET is active and pull the output to ground

- If Rup value is small the ground offset will be higher

### Why I<sup>2</sup>C BUS Buffer Is Needed?

I<sup>2</sup>C internal block diagram

#### How I<sup>2</sup>C BUS works

When master/slave output LOW:

• FET is active and pull the output to ground

When master/slave output is HIGH

• FET open and Rup will pull SCL/SDA to VDD

Max drive strength of CPU for I<sup>2</sup>C is 3mA or 400pF

Number of slave devices are depended on:

- Drive strength of FET

- Capacitance of PCB trace length

- Capacitance load of each pin connect to the bus

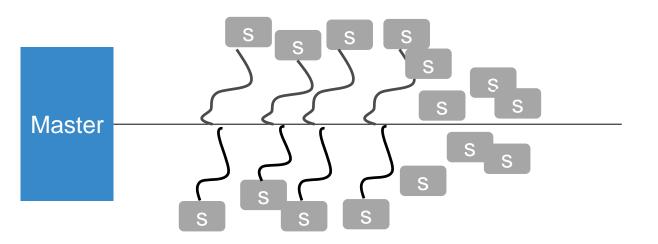

# Why I<sup>2</sup>C BUS Buffer Is Needed?

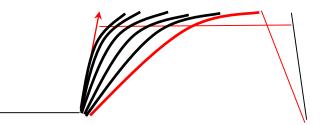

What happens when the bus has too many slave devices

- Longer trace length

- More capacitance load

- Distort rise and fall time

System needs bus buffers to improve quality of the signals

| Mode          | standard | Fm    | Fm+   |

|---------------|----------|-------|-------|

| Rise time max | 1000ns   | 300ns | 120ns |

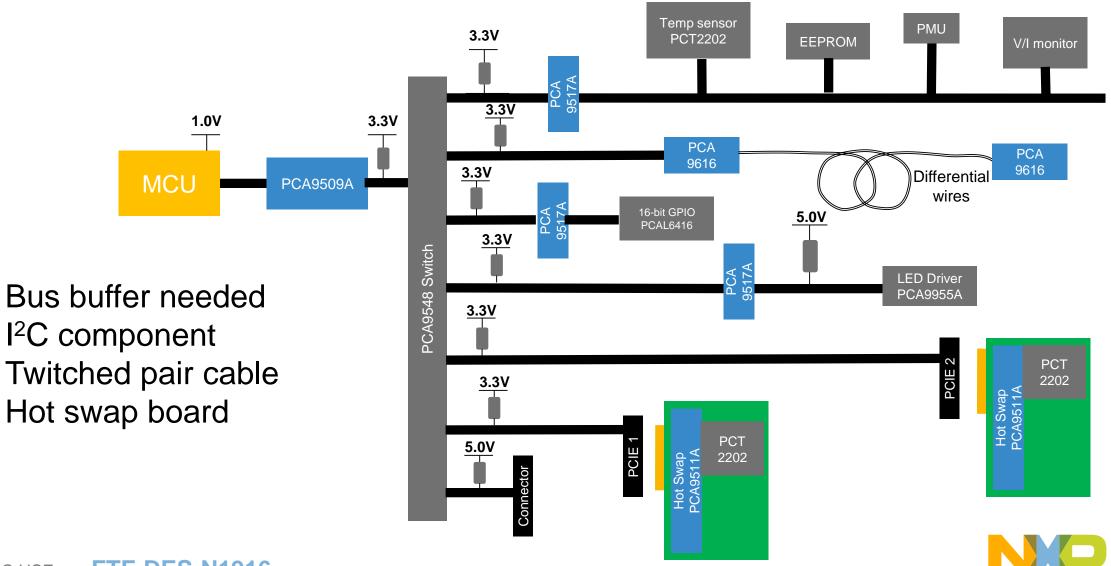

### **Example for Bus Buffers**

(

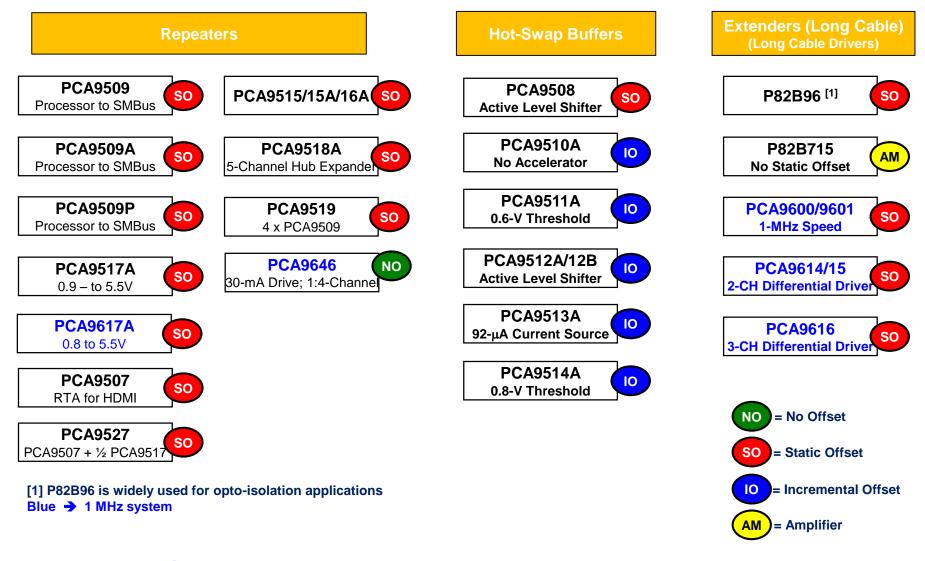

### I<sup>2</sup>C BUS Buffer Family

15 PUBLIC USE FTF-DES-N1916

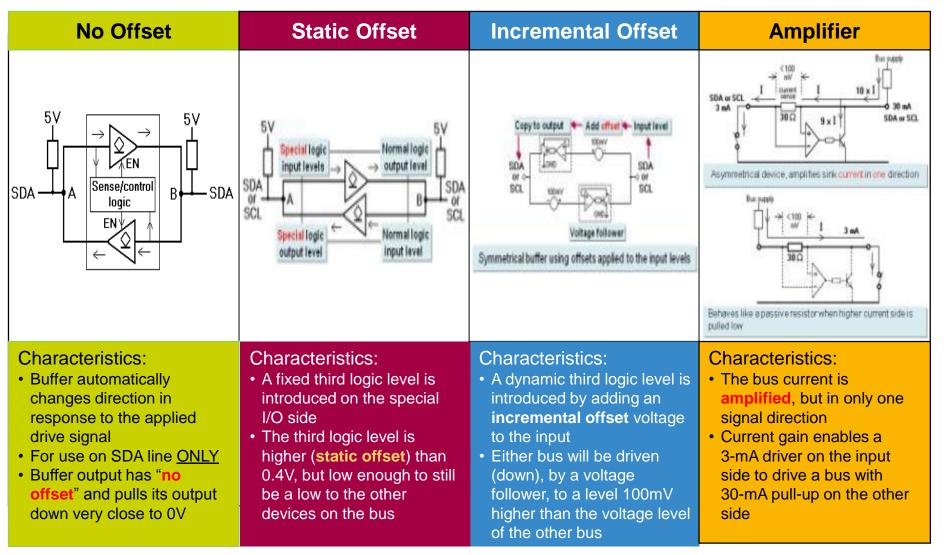

### **Understanding I<sup>2</sup>C BUS Buffer Technologies**

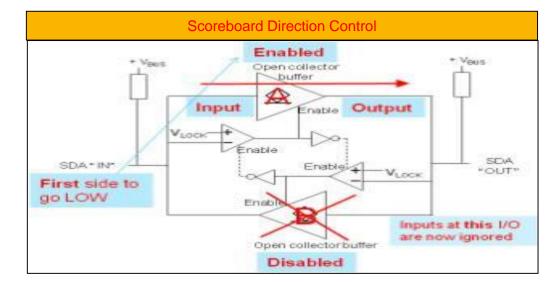

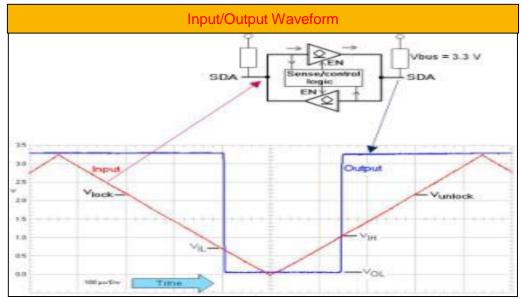

### **No Offset Buffer Characteristics**

- Compatible (but not compliant) with I<sup>2</sup>C BUS or similar buses

- Uni-directional clock depend on direction setting

- The first one to score (first input to go low) takes control of the bus and the other is disabled

- Compatible (but not compliant) with I<sup>2</sup>C BUS or similar buses

- When an input falls below Vlock, the buffer becomes enabled and the other buffer is disabled. When the controlling input signal rises above Vunlock, the buffer is disabled and the device is ready to process any side that goes low next or may be already low, but was unable to take control

- To prevent lock-up, Buffers A and B must never be enabled at the same time

- clock stretching is not allowed and a true multi-master system cannot be implemented

- Both buffers are able to drive their outputs fully low, near 0V

- Devices with "No Offset" are PCA9525, PCA9605 and PCA9646

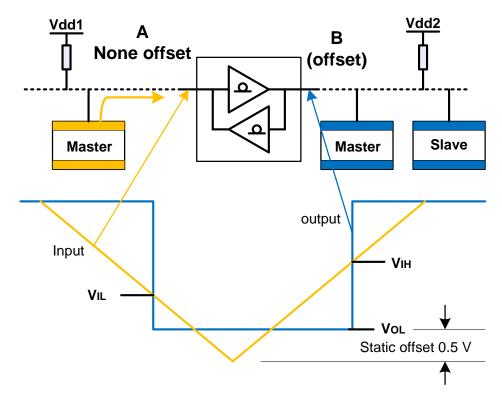

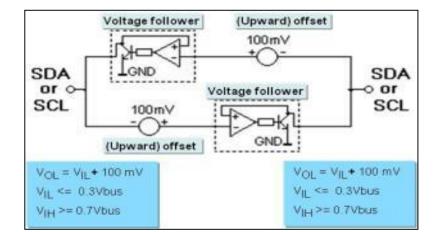

### **Static Offset Buffer Characteristics**

- Compatible (but not compliant) with I<sup>2</sup>C BUS or similar buses

- Fully bi-directional

- Support multi-master operation, including clock stretching

- Isolates the bus

- The resistive and capacitive load will be independent on each side of the bus

- Non offset side drives (A side)

- When A input goes below VIL, the B output will be pulled LOW to the static offset

- When A input goes above VIH, the B output will be released to Vdd2

- Devices with "Static Offset are PCA9507, PCA9508, PCA9509, PCA9515A, PCA9516A, PCA9517A, PCA9518A, PCA9519, PCA9614, PCA9615, PCA9616, PCA9527, PCA9600, PCA9601, P82B96

### None offset side driving the bus

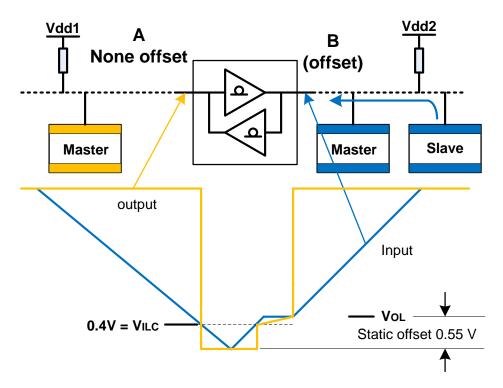

### **Static Offset Buffer Characteristics**

- Compatible (but not compliant) with I<sup>2</sup>C BUS or similar buses

- Fully bi-directional

- Support multi-master operation, including clock stretching

- Isolates the bus

- The resistive and capacitive load will be independent on each side of the bus

- Offset side drives (B side)

- When B input goes below VILC, the A output will be pulled LOW to ground

- When B input goes above VILC, the A output will be released

- And the B side will wait at 0.55V until A side above VOL (offset 0.55V)

- Devices with "Static Offset are PCA9507, PCA9508, PCA9509, PCA9515A, PCA9516A, PCA9517A, PCA9518A, PCA9519, PCA9614, PCA9615, PCA9616, PCA9527, PCA9600, PCA9601, P82B96

### Offset side driving the bus

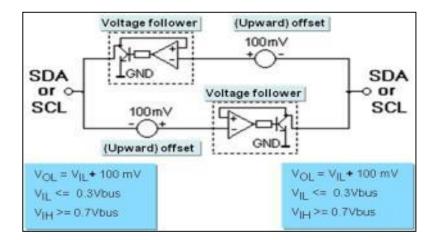

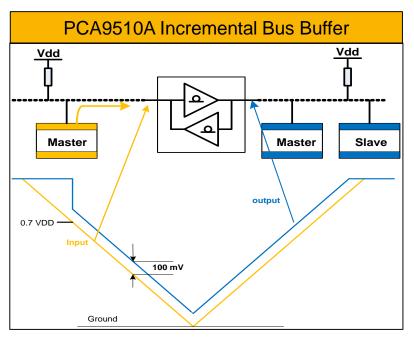

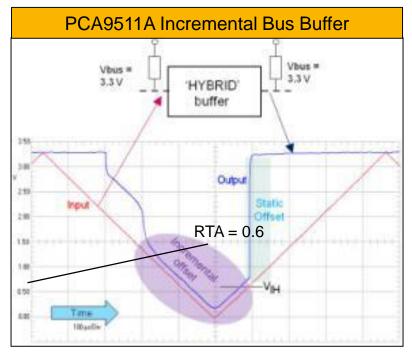

### **Incremental Offset Buffer Characteristics**

- Compatible with I<sup>2</sup>C BUS or similar buses

- -Fully bi-directional

- The  $V_{\text{IL}}$  and  $V_{\text{IH}}$  levels are I²C BUS compliant

- Support multi-master operation, including clock stretching

- The output will be 100 mV lower then the input signal

- Pre-charge I<sup>2</sup>C BUS before make connection

- Check bus condition before make connection for hot-swap application

### **Incremental Offset Buffer Characteristics**

- Compatible with I<sup>2</sup>C BUS or similar buses

- Fully bi-directional

- The  $V_{\text{IL}}$  and  $V_{\text{IH}}$  levels are I²C BUS compliant

- Isolates the bus

- Support multi-master operation, including clock stretching

- The output will be 100 mV lower then the input signal

- Pre-charge I<sup>2</sup>C BUS before make connection

- Check bus condition before make connection for hot-swap application

- Rise Time Acceleration

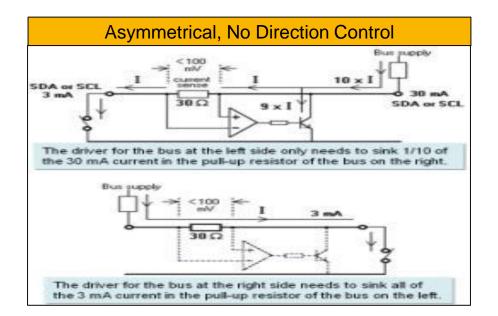

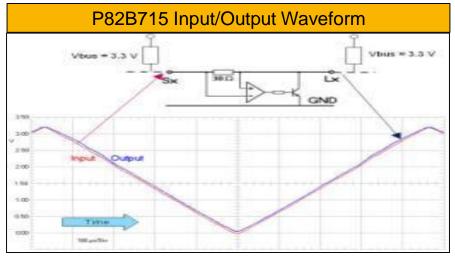

### **Amplifier Buffer Characteristics**

- Compatible (and compliant) with I<sup>2</sup>C BUS or similar buses

- Fully bi-directional

- P82B715 has a current gain of 10x in one direction and allows connection of a bus with its pull-up resistor scaled for 30-mA sink current

- Because the two I/Os are joined internally by a 30Ω resistor, there can never be a voltage difference greater than 100mV between them. Typically, it's about 70mV. Logic voltage shifting is not possible for this part

- Capacitive loading is also scaled. 4000pF on the 30-mA bus is equivalent to 400-pF on the 3-mA bus

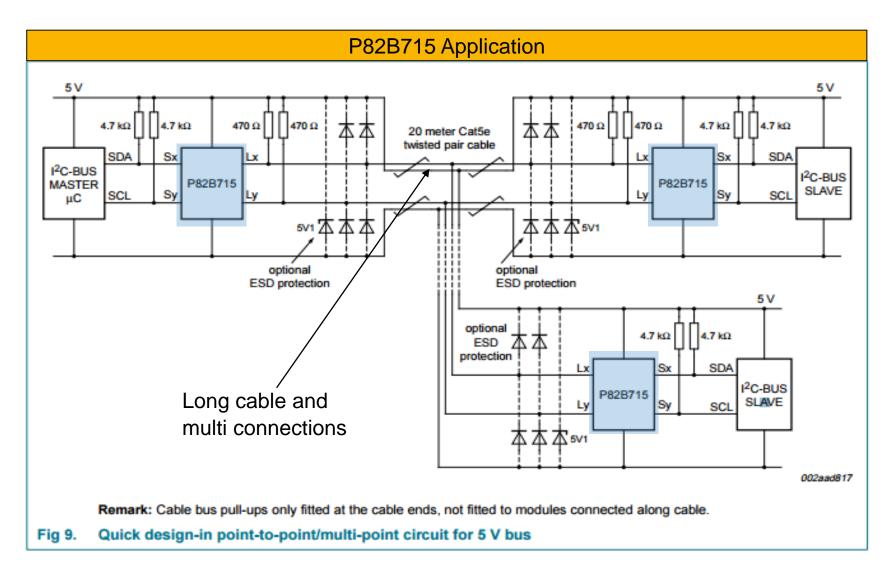

### **Amplifier Buffer Application**

### **I<sup>2</sup>C BUS Information**

If you have any questions regard to I<sup>2</sup>C BUS. Please email to <u>i2csupport@nxp.com</u>

For more information about I<sup>2</sup>C bus buffer products go to <u>www.nxp.com/i2c</u>

or

http://www.nxp.com/products/interface-and-connectivity/interface-and-systemmanagement/i2c/i2c-bus-repeaters-hubs-extenders:mc\_41849

# Thank you very much

### SECURE CONNECTIONS FOR A SMARTER WORLD

#### ATTRIBUTION STATEMENT

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, CoolFlux, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE, MIFARE Classic, MIFARE DESFire, MIFARE Plus, MIFARE FleX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TrenchMOS, UCODE, Freescale, the Freescale logo, AltiVec, C 5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. ARM, AMBA, ARM Powered, Artisan, Cortex, Jazelle, Keil, SecurCore, Thumb, TrustZone, and µVision are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. ARM7, ARM9, ARM11, big.LITTLE, CoreLink, CoreSight, DesignStart, Mali, mbed, NEON, POP, Sensinode, Socrates, ULINK and Versatile are trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2015–2016 NXP B.V.