## CAN FLEXIBLE DATA (FD)

REBECA DELGADO / BERND ELEND FIELD APPLICATIONS ENGINEER / PRINCIPAL ENGINEER FTF-AUT-N1784 MAY, 2016

PUBLIC USE

# AGENDA

- CAN FD Protocol Overview

- FlexCAN3 FD

- MCAN FD

- Flexible Data and Partial Networking Impact on CAN Physical Layer

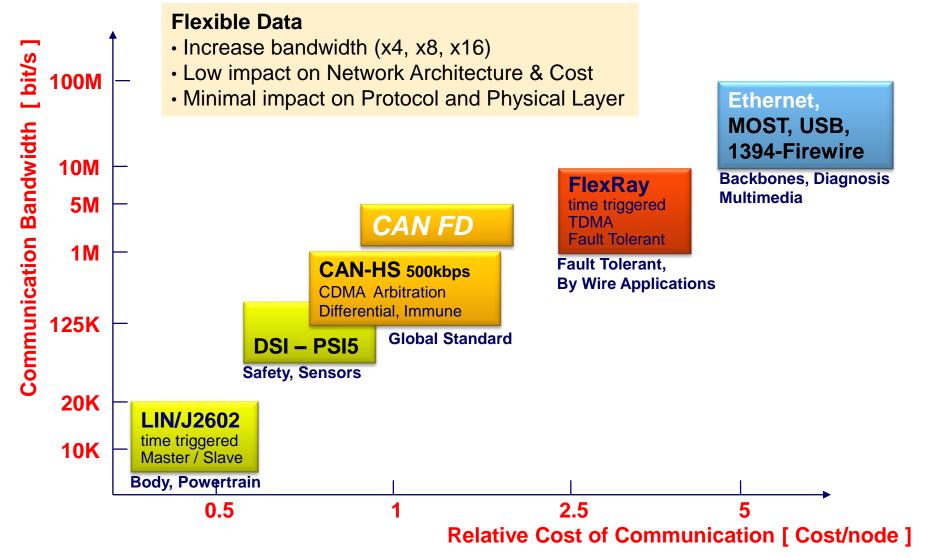

#### **Increasing Bandwidth at Limited Cost**

## CAN FD

- CAN FD stands for CAN with Flexible Data-Rate

- CAN FD was a proposal by Bosch to

- Increase the baud rate of the data portion of a CAN message

- Increase the number of data bytes that can be sent in a single CAN message to up to 64

- No changes to arbitration field allow for existing physical layers to be used

#### **Gradual transition**

- Classical CAN nodes can't listen to CAN FD frames.

- CAN FD nodes can send and receive Classical CAN frames.

- Are Classical CAN and CAN FD nodes able to coexist?

- Option 1)

Introduction phase: CAN FD use only in specific operation modes

E.g. software download at end of line programming with non CAN FD nodes in standby or sleep, managed by CAN FD tolerant partial networking transceivers.

#### - Option 2)

Use of CAN FD shield transceivers that make Classical CAN nodes deaf for CAN FD frames (-> details will be disclosed in "FTF-AUT-N1775 Enabling Hybrid CAN Network: FD shield")

#### **Basic Concepts**

- Bit rate

- Two bit rates in a CAN FD system, ne for the arbitration phase and one for the data phase.

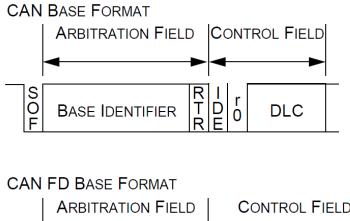

- Frame format:

- CAN BASE FRAME FORMAT (CBFF):

- CAN EXTENDED FRAME FORMAT (CEFF):

- CAN FD BASE FRAME FORMAT (FBFF):

- T): 11 bit long identifier and optional dual bit rate

11 bit long identifier and constant bit rate

29 bit long identifier and constant bit rate

- CAN FD EXTENDED FRAME FORMAT (FEFF): 29 bit long identifier and optional dual bit rate

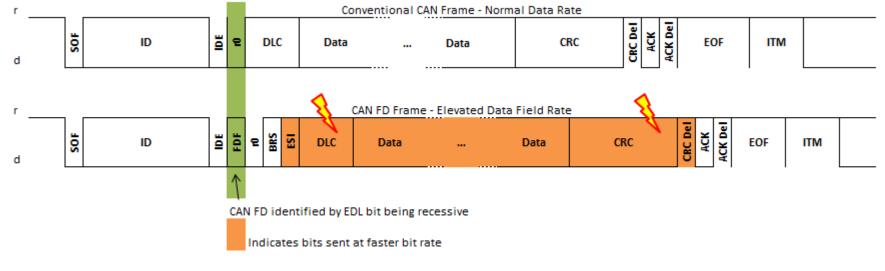

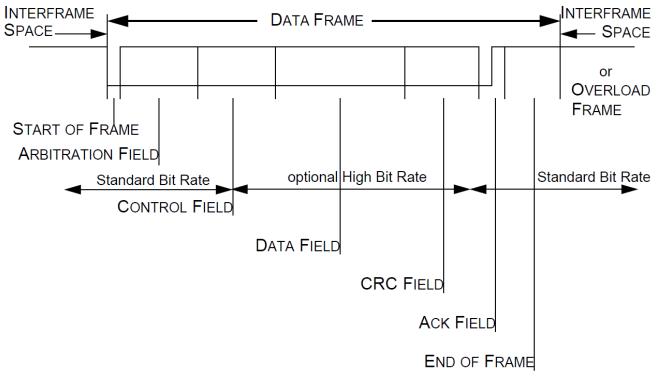

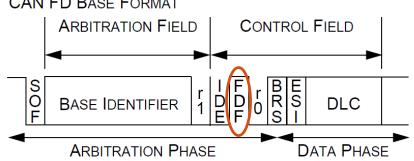

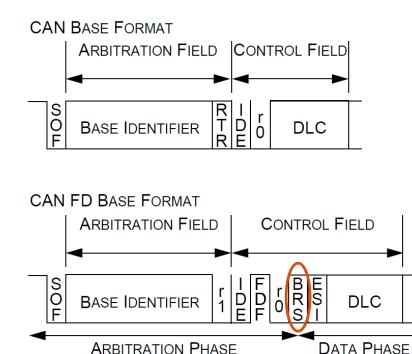

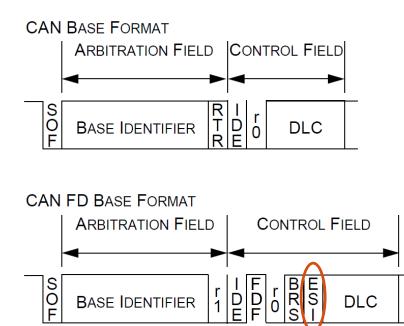

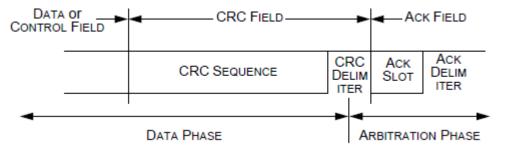

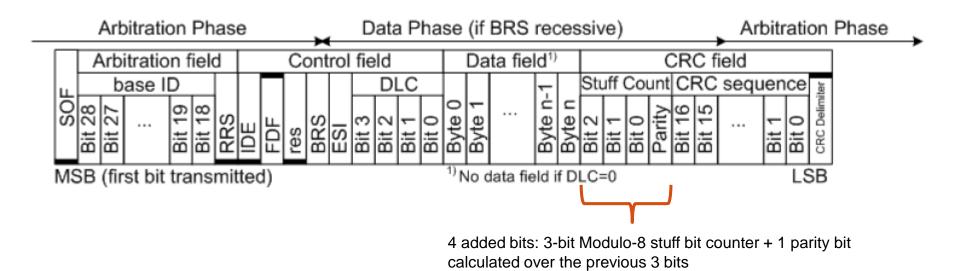

#### Frame fields

START OF FRAME, ARBITRATION FIELD, CONTROL FIELD, DATA FIELD, CRC FIELD, ACK FIELD, END OF FRAME

7 PUBLIC USE **#NXPFTF**

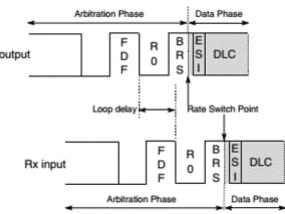

The FD FRAME FORMAT (FDF) bit is recessive. It only exists in CAN FD format frames, it distinguishes between CAN format and CAN FD format frames

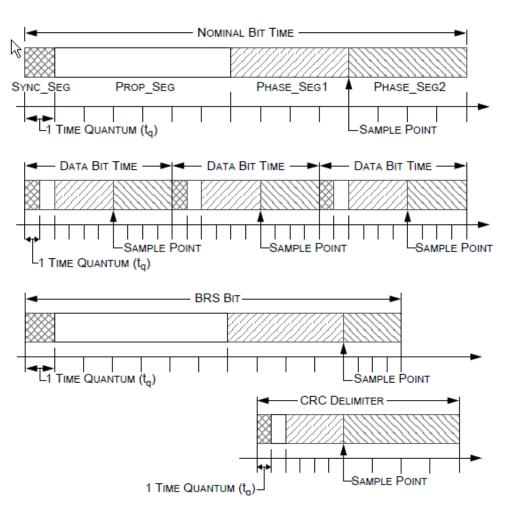

The BIT RATE SWITCH (BRS) bit decides whether the bit rate is switched inside a CAN FD format frame. If recessive, the bit rate is switched immediately at the sample point of the BRS Switching back to arbitration speed happens in this case at the sample point of the CRC delimiter. Thus the BRS and the CRC delimiter are so called "mixed-bits".

• The ERROR STATE INDICATOR (ESI) flag is transmitted *dominant by error active nodes,* recessive by error passive nodes.

DATA PHASE

**ARBITRATION PHASE**

#### **Data Payload**

• CAN:

-0 to 8 bytes

- CAN FD

- 0 to 64 bytes

|                      | # of<br>Data Bytes | DLC3 | DLC2 | DLC1 | DLC0 |

|----------------------|--------------------|------|------|------|------|

|                      | 0                  | 0    | 0    | 0    | 0    |

| and                  | 1                  | 0    | 0    | 0    | 1    |

| Format               | 2                  | 0    | 0    | 1    | 0    |

|                      | 3                  | 0    | 0    | 1    | 1    |

| in CAN<br>CAN FD     | 4                  | 0    | 1    | 0    | 0    |

| CAN                  | 5                  | 0    | 1    | 0    | 1    |

| DLC                  | 6                  | 0    | 1    | 1    | 0    |

|                      | 7                  | 0    | 1    | 1    | 1    |

| CAN<br>format        | 8                  | 1    | x    | x    | x    |

|                      | 8                  | 1    | 0    | 0    | 0    |

| mat                  | 12                 | 1    | 0    | 0    | 1    |

| For                  | 16                 | 1    | 0    | 1    | 0    |

| ED                   | 20                 | 1    | 0    | 1    | 1    |

| CAN                  | 24                 | 1    | 1    | 0    | 0    |

| DLC in CAN FD Format | 32                 | 1    | 1    | 0    | 1    |

| DLC                  | 48                 | 1    | 1    | 1    | 0    |

|                      | 64                 | 1    | 1    | 1    | 1    |

#### Frame Format – CRC

• CAN: CRC\_15 0xC599

$(x^{15} + x^{14} + x^{10} + x^8 + x^7 + x^4 + x^3 + 1) = (x+1) \cdot (x^7 + x^3 + 1) \cdot (x^7 + x^3 + x^2 + x + 1)$

• CAN FD < 16 bytes of data: CRC\_17 0x3685B

$(x^{17}+x^{16}+x^{14}+x^{13}+x^{11}+x^6+x^4+x^3+x^1+1)$ = (x+1) · (x^{16}+x^{13}+x^{10}+x^9+x^8+x^7+x^6+x^3+1)

• CAN FD > 16 bytes of data: CRC\_21 0x302899

$(x^{21}+x^{20}+x^{13}+x^{11}+x^7+x^4+x^3+1)$ = (x+1) \cdot (x^{10}+x^3+1) \cdot (x^{10}+x^3+x^2+x^1+1)

• All CRCs with Hamming Distance of HD = 6.

#### **CAN FD CRC Issue**

- When Bosch invented CAN, the CRC calculation did not consider bit stuffing.

- The initialization vector was chosen to be "0" (zero)

- Later it was recognized that the bit stuffing impacts the Hamming distance

- In Classical CAN : HD=2 and not HD=6

- With CAN FD Bosch included the stuff bits in the CRC calculation to overcome this problem

- However, in conjunction with the initialization vector of "0" (zero) it became worse!

## **CAN FD CRC Fixes**

- Fix1:

- Change CRC initial value to use "1" followed by "0"s as the CRC polynomial seed

- Fix2:

- Add stuff bit 3-bit count , gray coded with additional parity bit at LSB, in front of CRC

#### **Implications of CAN FD Fixes**

- There are now two versions of CAN FD

- non ISO CAN FD (original Bosch proposal)

- ISO CAN FD (ISO11898-1:2015) including the two fixes

#### **CAN-FD Errata - CAN FD Errata Background**

- Errata will be released shortly for a number of products that have the "non ISO CAN FD" capabilities on them.

- These errata include:

- ERR008759 (for devices with FlexCAN3 (non ISO FD CRC ))

- ERR008860 (for devices with MCAN and a FSL wrapper (non ISO FD CRC ))

- ERR008923 (for devices with MCAN and a ST wrapper (non ISO FD CRC ))

- This errata was driven by this flaw in the CRC definition of the original CAN FD specification that resulted in a need for a late change in the ISO 11898-1.

- This is not a bug in the controller silicon!

#### **Other OEM Requirements**

- Requirements

- Enhanced CRC that includes stuff bit count (ISO 11898-1:2015)

- GM, Ford, VW, Daimler AG, Renault, PSA have documented that they require full ISO conformance

- Interleaving Classic CAN frames and CAN FD frames

- GM, Ford, VW have stated that they require ability to interleave classical and FD frame for series productions.

#### **Bit Rates**

- Two bit rates:

- ARBITRATION-PHASE

- Ionger bit time = NOMINAL BIT RATE

- DATA PHASE

- same or shorter bit time <= NOMINAL BIT RATE</li>

- → Two bit rate register sets

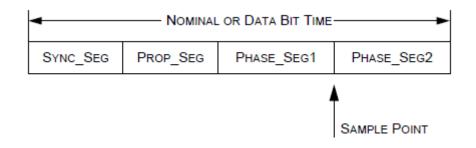

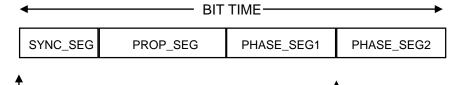

#### **Bit Time Segments**

- Two prescalers  $\rightarrow$  two TIME QUANTUM

- m(N) for the NOMINAL BIT TIME

- m(D) for the DATA BIT TIME

- The number of TIME QUANTA in a bit time shall be programmable at least from 8 to 25.

| Bit Time<br>Segment | NOMINAL BIT RATE<br>TIME QUANTA(N) | DATA BIT RATE<br>TIME QUANTA(D) |

|---------------------|------------------------------------|---------------------------------|

| SYNC_SEG            | 1                                  | 1                               |

| PROP_SEG            | 1, 2,, 32 or more                  | 0, 1, 2,, 8                     |

| PHASE_SEG1          | 1, 2,, 32 or more                  | 0, 1, 2,, 8                     |

| PHASE_SEG2          | Max(PHASE_SEG1(N), IPT)            | Max(PHASE_SEG1(D), IPT)         |

#### **CAN FD Bit Rate Example**

- NOMINAL BIT TIME prescaler m(N) = 2

- DATA BIT TIME prescaler m(D) = 1

Keep both prescaler values equal whenever possible!!

Make SJW in data phase not bigger than mandated by the precision of the clock sources.

Make SJW in arbitration phase big to allow for phase shifts at loss of arbitration

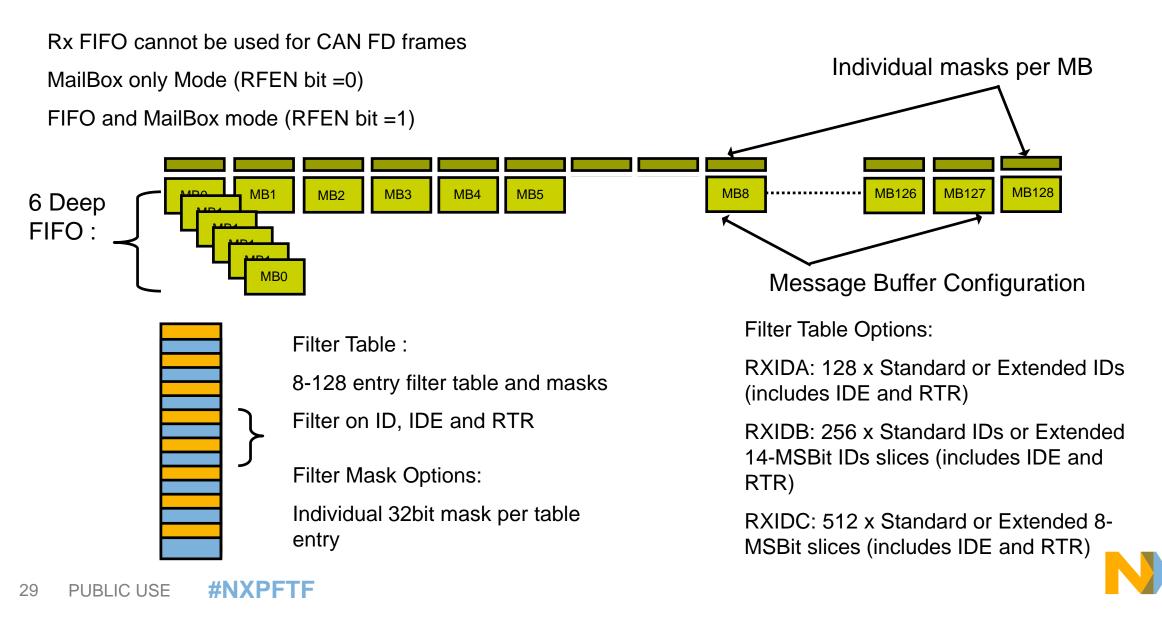

# USING FLEXCAN3\_FD

# FEATURES

- FlexCAN3-FD Module Features:

- Up to 128 Message buffers configurable as Tx or Rx

- Standard and Extended ID frames and Remote Frames\* (not for FD)

- Payload: 0 to 64 bytes data length

- Programmable bit rate up to 8 Mb/sec

- Individual Rx Mask Registers per Message Buffer

- Full featured Rx FIFO

- Storage capacity for 6 frames and internal pointer handling with DMA support

- Powerful Rx FIFO ID filtering

- Capable of matching incoming IDs against 128 extended, 256 standard or 512 partial (8 bits) IDs, with individual masking capability

- Programmable acceptance filters for receive message buffers

- 16-bit time Stamp, optional source

- Low Power operation via pretended networking feature

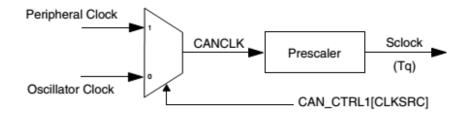

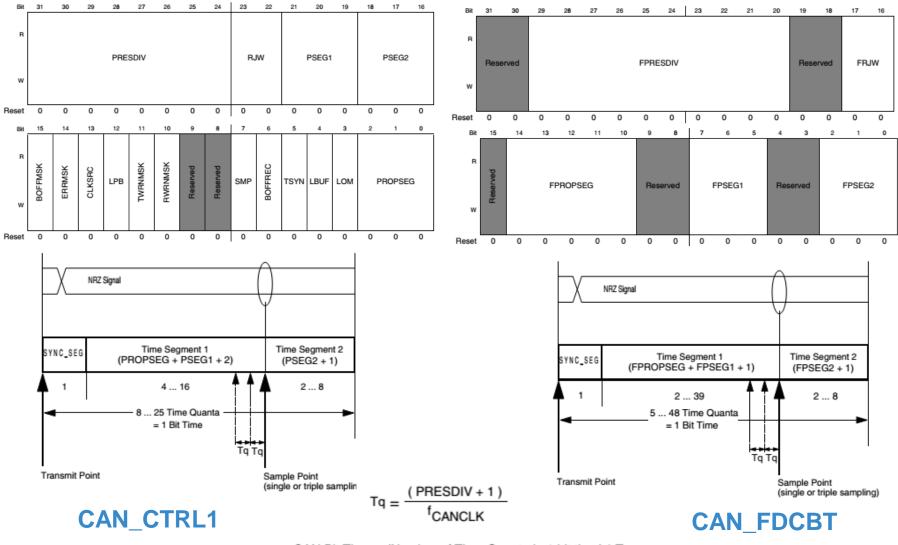

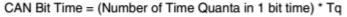

## **Protocol Bit Timing**

• FlexCAN supports either oscillator or peripheral clock as CAN timing source

- Recall, FD frame requires two bit rates Arbitration and data phase

- Bit timing parameters are achieved by setting up the following registers:

- Control register 1 (CTRL1): "Classical" CAN (equivalent FlexCAN2)

- CAN bit timing reg (CBT): Extended version of above register

- CAN FD bit timing reg (FDCBT): Bit time associated with FD data phase

- Bit time consists of following elements which are comprised from a variable number of time quanta

#### FlexCAN FD Bit Timing Examples

24 PUBLIC USE **#NXPFTF**

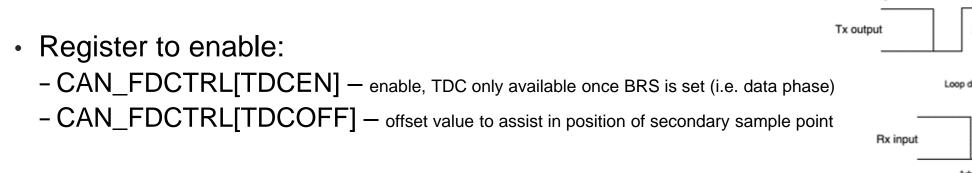

#### **Transceiver Delay Compensation**

- CAN transmitters are required to check for errors in their transmitted bits between their CAN\_Tx and CAN\_Rx pins

- ISO11898 defines this delay at maximum of 255ns

- When higher bit rate data phase occurs in FD frame, the bit time that elapses until the sample point can be shorter than the transceivers loop delay impeding correct comparison.

- A secondary sample point is defined where the transmitted bit is correctly compared with the received bit to check for bit errors.

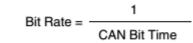

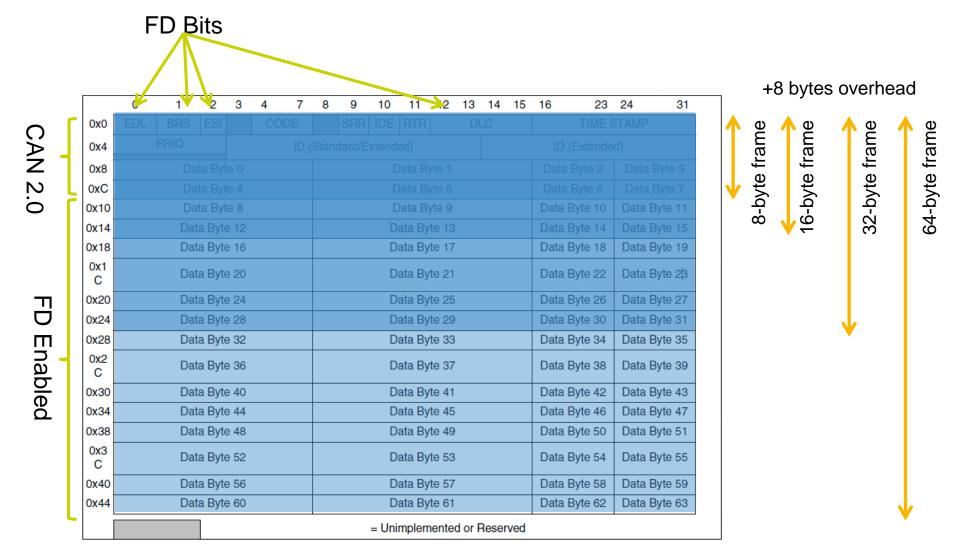

#### FlexCAN3 FD Message buffer structure

#### **FlexCAN3 FD Memory Partitioning**

**#NXPFTF**

27

PUBLIC USE

|     |         |                                                                                                                                                                                                                                                                     | <i>,</i> , | titioned in 4 block<br>yload buffers can be |                                   |                      |   |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------|-----------------------------------|----------------------|---|

| 80  |         | SoC can instantiate 1 to 4 blocks                                                                                                                                                                                                                                   |            |                                             |                                   |                      |   |

| 280 | Block 0 | <ul> <li>Each block is composed by the memory space equivalent to 32 x 16-byte MBs or 512-<br/>bytes (0x200)</li> </ul>                                                                                                                                             |            |                                             |                                   |                      |   |

| 480 | Block 1 | <ul> <li>Each block can be configured to have message buffers (MBs) of a defined size in order to<br/>store messages with payload of 8-byte, 16-byte, 32-byte or 64-bytes. Message buffer data<br/>size region bit field:</li> <li>FDCTRL[MBDSRn] = 0bxx</li> </ul> |            |                                             |                                   |                      |   |

|     | Block 2 | <ul> <li>The number of message buffers in a block depends upon payload size. Each block can be<br/>configured (by software) as follows:</li> </ul>                                                                                                                  |            |                                             |                                   |                      |   |

| 680 |         |                                                                                                                                                                                                                                                                     | RAM block  | Payload size                                | Number of MBs in the RAM<br>block | Message Buffer range |   |

|     |         |                                                                                                                                                                                                                                                                     | 0          | CAN_FDCTRL[MBDSR0]=00,<br>8 bytes payload   | 32                                | 0 to 31              | İ |

|     | Block 3 |                                                                                                                                                                                                                                                                     | 1          | CAN_FDCTRL[MBDSR1]=01,<br>16 bytes payload  | 21                                | 32 to 52             |   |

| 880 |         |                                                                                                                                                                                                                                                                     | 2          | CAN_FDCTRL[MBDSR2]=10,<br>32 bytes payload  | 12                                | 53 to 64             |   |

|     |         |                                                                                                                                                                                                                                                                     | 3          | CAN_FDCTRL[MBDSR3]=11,                      | 7                                 | 65 to 71             | 1 |

64 bytes payload

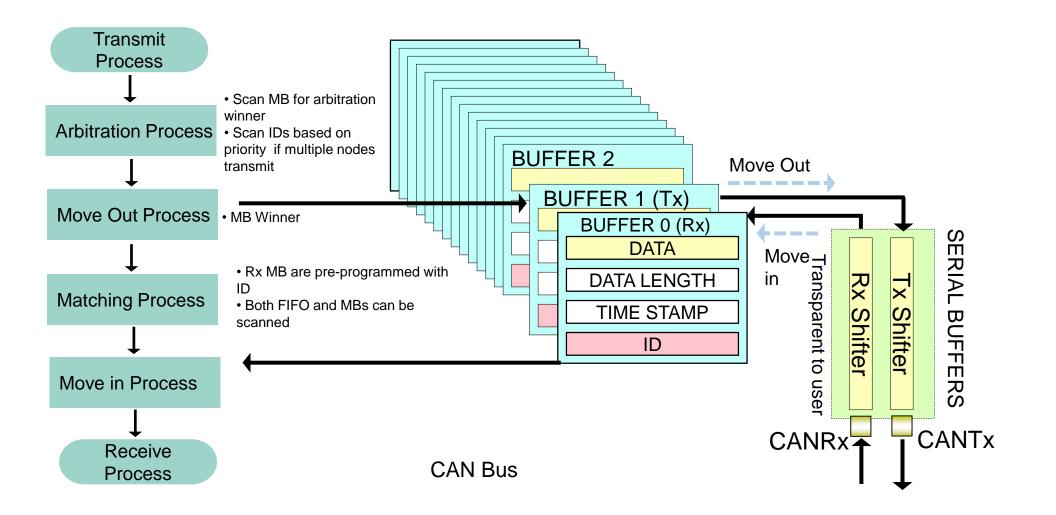

#### Transmit, Arbitrate, Move, Match and Receive!

#### **FlexCAN Rx FIFO**

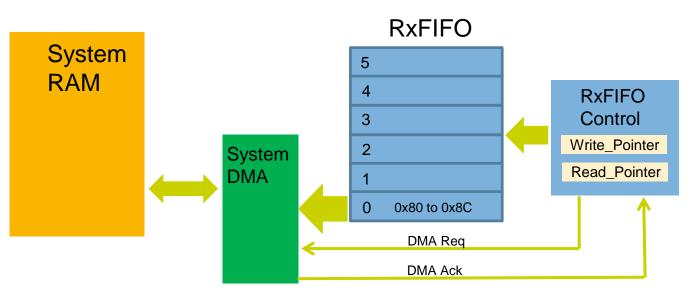

### **Rx FIFO Under DMA Operation**

Enhanced Feature

#### - DMA Request added to FlexCAN RxFIFO

- Allows CPU longer time to service the received CAN messages. With the DMA connected the depth of the FIFO should also be able to be relatively small

- Enabled via the MCR[DMA]

- DMA Request asserted when any frame in FIFO

- DMA reads head of FIFO (0x80 to 0x8C). 8C must be read last to update for next FRAME

# **USING MCAN FD**

#### **MCANs Features and user point**

- Debug over M\_CAN

- FD-Enabled

- 20kB shared message Random Access Memory (RAM)

- 128 Filter elements

- 2 configurable receive First In First Out registers (FIFO) for each module

- 64 dedicated receive and 32 dedicated transmit buffers

- 11 bit or 29 bit ID lengths

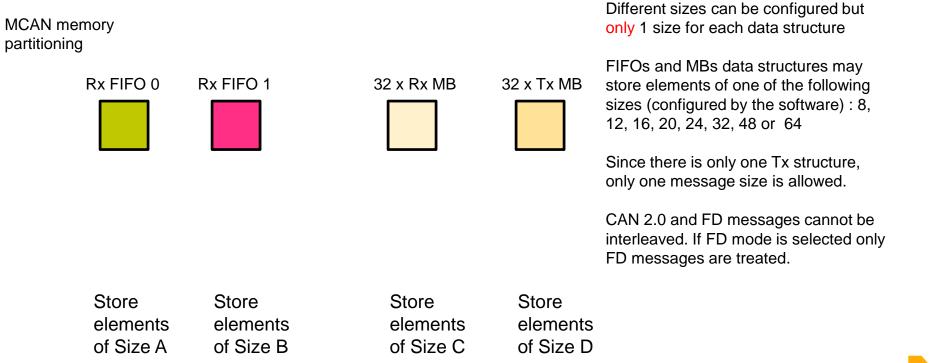

#### **MCAN FD Memory Partitioning**

- The MCAN FD provides several data structures to store Messages, such as FIFOs and MBs (Message Buffers). The data payload size for each data structure is fixed for a given module configuration (configured by the software).

- For example: if the Rx FIFO 0 is defined to store 32-byte payload messages, it only stores messages with size of up to 32-bytes payload.

33 PUBLIC USE **#NXPFTF**

## **CAN Module Comparison**

|                                           | FlexCAN3_FD                                          | MCAN_3                | TTCAN_2                                 |  |

|-------------------------------------------|------------------------------------------------------|-----------------------|-----------------------------------------|--|

| Functional Differentiator                 | Flexible Data Structure<br>(mail box + FIFO)         | Shared RAM            | Shared RAM +<br>Message Time scheduling |  |

| FD Support                                | Yes                                                  | Yes                   | Yes/Partial                             |  |

| MBs and FIFO                              | Yes                                                  | Yes                   | Yes                                     |  |

| Message RAM                               | 2k RAM:<br>Partitioned into<br>4 x 512 byte blocks** | Shared 20k RAM block* |                                         |  |

| ID Acceptance Filtering                   | Yes                                                  | Yes                   | Yes                                     |  |

| Debug over CAN                            | No                                                   | Yes                   | Yes                                     |  |

| DMA support                               | Yes                                                  | No                    | No                                      |  |

| Pretended Networking<br>(low pwr support) | Yes                                                  | No                    | No                                      |  |

| Optional ext timestamp with clock         | Yes                                                  | No                    | No                                      |  |

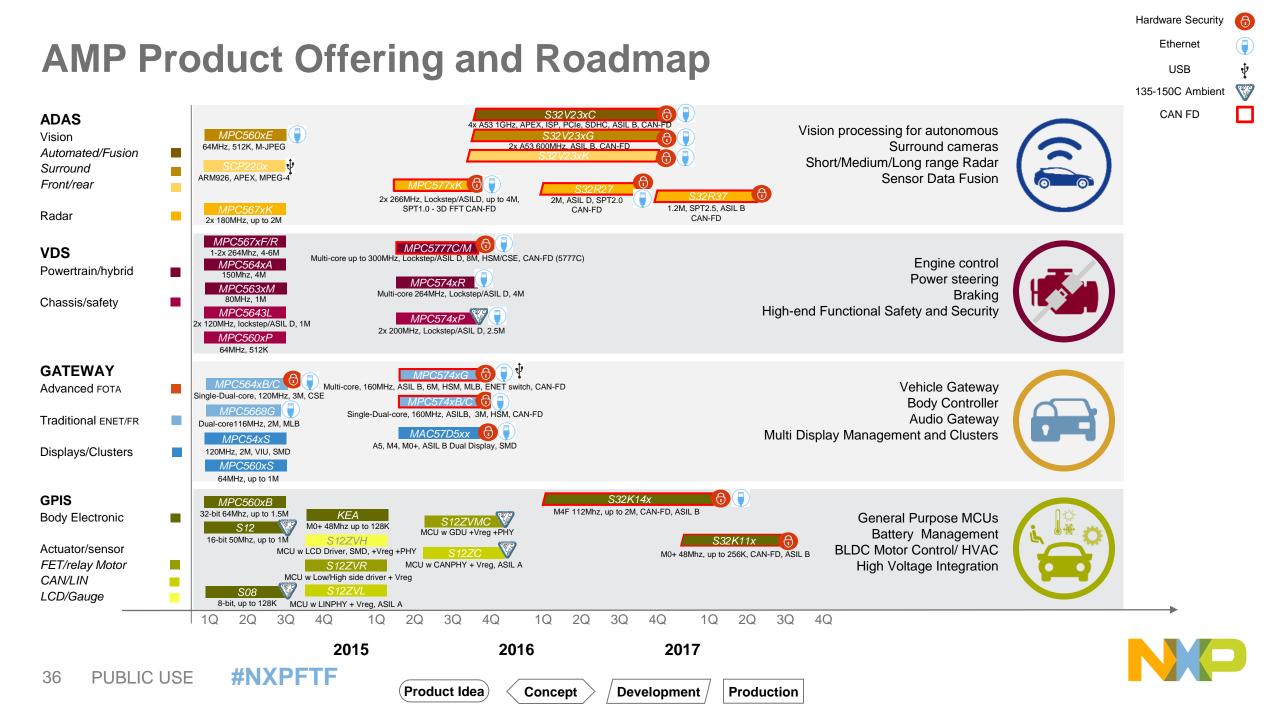

# AMP CAN FD ROADMAP

## FLEXIBLE DATA AND PARTIAL NETWORKING IMPACT ON CAN PHYSICAL LAYER

### **ISO Standards Applicable to CAN Physical Layer**

- CAN Flexible Data and Partial Networking

- Flexible data has been incorporated into the new ISO11898-1 specification

- ISO11898 -2, -5, and -6 will be merged into a new ISO11898-2 specification

- EMC/ESD target levels and limits may get tighter

- Additional testing will be required for Partial Networking

- Requires better intrinsic Physical Layer performance and functionality

| Standards  | XCVR mode                                                 | Operation                                                       |

|------------|-----------------------------------------------------------|-----------------------------------------------------------------|

| ISO11898-2 | Transmit-Receive (Normal mode)                            | Bi-directional interface to the physical bus                    |

| ISO11898-5 | Low power mode and wake up                                | Wake up on any CAN frame                                        |

| ISO11898-6 | Partial Networking, selective wake up (frame detect mode) | Wake up on a dedicated frame (ISO11898-1).<br>Error management. |

38 PUBLIC USE **#NXPFTF**

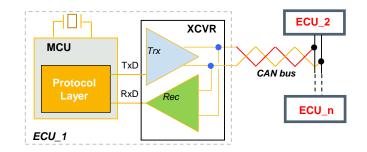

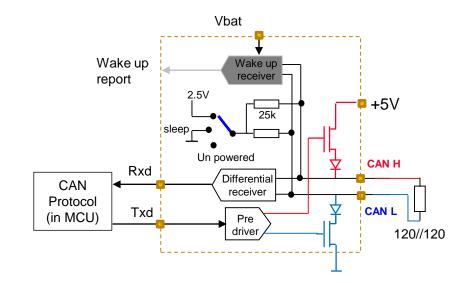

#### High Speed CAN Physical Layer Simplified Architecture – ISO11898-2 and -5

39 PUBLIC USE **#NXPFTF**

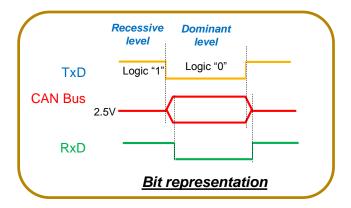

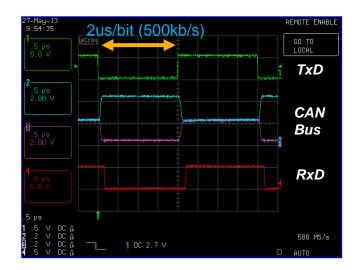

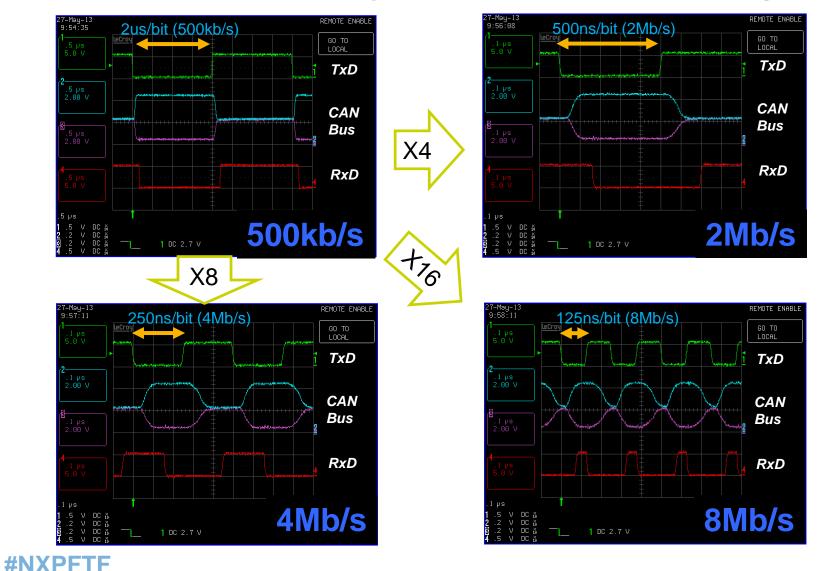

#### Signals at 500 kb/s, 2, 4 and 8 Mb/s

(ISO11898-2 Test Conditions: 60 ohms / 100 pF – "lab conditions" according to ISO11898-2)

NP

40 PUBLIC USE

#### **New Timing Definition**

#### Ensure a minimum duration of the recessive level

More bit timing requirements are given in ISO11898-2 for 2Mbit/s and 5MBit/s

41 PUBLIC USE **#NXPFTF**

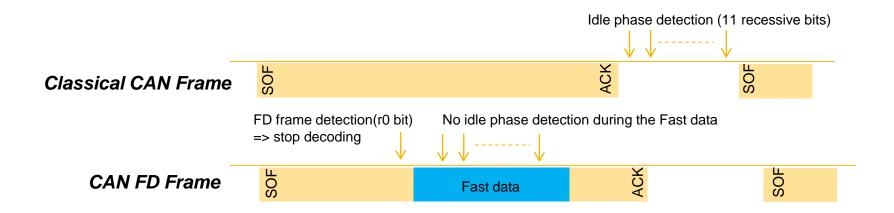

#### **CAN Flexible Data Impact on ISO11898-6 Physical Layer**

#### Partial networking begin FD passive means:

- CAN Flexible Data frame shall not "disturb" Partial Networking transceiver:

- The circuitry must be designed to avoid "Error Detection" and to prevent the Frame Error Counter from increasing and falsely waking up the transceiver

- Proper detection of "End of frame / Idle detection"

42 PUBLIC USE **#NXPFTF**

#### Conclusion

- Industry trend is increased bandwidth and EMC robustness combined with energy savings

- CAN Network is evolving with emergence of CAN Partial Networking and CAN Flexible Data standards to support these needs, alone or combined together

- At Physical Layer there are conflicting challenges:

- Improving bandwidth, reduce immunity to power injection and increase noise emission level

- Reducing quiescent current, improving noise immunity, EMC, and ESD continue to be extremely important.

- -Need to sustain performance without need for common mode choke

- NXP is focusing analog innovations to support High Speed CAN, CAN FD and Partial Networking

## SECURE CONNECTIONS FOR A SMARTER WORLD

#### ATTRIBUTION STATEMENT

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, CoolFlux, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE, MIFARE Classic, MIFARE DESFire, MIFARE Plus, MIFARE FleX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TrenchMOS, UCODE, Freescale, the Freescale logo, AltiVec, C 5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. ARM, AMBA, ARM Powered, Artisan, Cortex, Jazelle, Keil, SecurCore, Thumb, TrustZone, and µVision are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. ARM7, ARM9, ARM11, big.LITTLE, CoreLink, CoreSight, DesignStart, Mali, mbed, NEON, POP, Sensinode, Socrates, ULINK and Versatile are trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2015–2016 NXP B.V.