## HOW TO USE AUTOMOTIVE MCU VIRTUAL MODELS

#### FTF-AUT-N1799

MANFRED THANNER, NXP SYSTEMS MODELING EXPERT CURT HILLIER, NXP APPLICATIONS ENGINEER MOJIN KOTTARATHIL, SYNOPSYS ANEESH BHASIN, SYNOPSYS MAY 18, 2016

PUBLIC USE

## AGENDA

- Course Overview

- Introduction to Virtual Prototypes

- Demos:

- -Linux boot

- A53 Test Software

- Hands on labs:

- Modifying source code

- -Using debugger run control

- Conclusion

## **COURSE OVERVIEW**

#### **Course Overview**

- Introduction to Virtual Prototypes

- -What are Virtual Prototypes?

- -Why are they useful?

- Explain the NXP and Synopsys COE

- Demos

- -See next slide

- Hands-on Labs

- -See next slide

#### **Today's Demo and Hands-on Lab Sessions**

- DEMO: Startup the S32V234 Virtual Prototype in the Synopsys Virtual Development Kit (VDK) environment

- **DEMO: Boot Linux** on the S32V234 based on ARM® Cortex®-A53. Observe boot process in the Linux console window

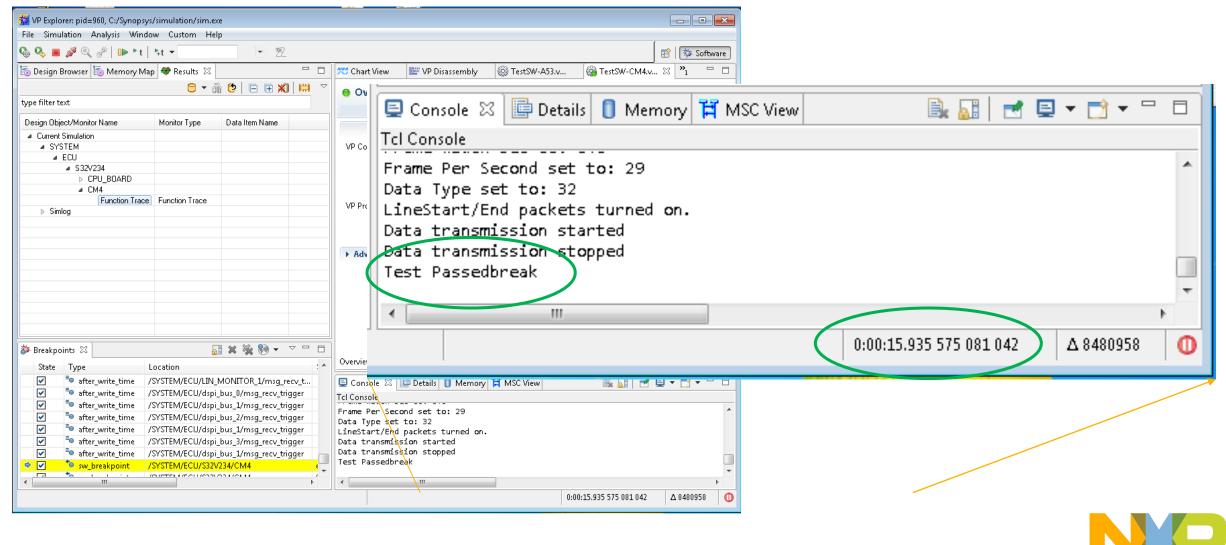

- **DEMO: Execute Test Software** on the S32V234 processor based on Cortex-M4.

- HANDS-ON: Configure Function and Context tracing, display in the VP Explorer

- HANDS-ON: Bring up a Lauterbach debugger and control the run-time operation of the virtual model just like you would control a real Hardware EVB

- HANDS-ON: Modify code, recompile, and see your changes in action

# INTRODUCTION TO VIRTUAL PROTOTYPES

#### NXP and Synopsys – Virtual Prototyping

#### Virtual Prototyping

Accelerate Innovation with Earlier and Faster Software Development

**SYNOPSYS**<sup>®</sup>

Silicon to Software"

#### <TO DO: Insert slide on the Synopsys + NXP COE agreement.>

#### Introduction

- What is a virtual prototype?

- "Virtual Prototyping is the use of computer models to develop and test a process or component without having to physically build or run it." FLUXTROL, Inc.

- Why do I need to know?

- Virtual Prototyping is becoming more commonplace in engineering environments as the demands for performance modeling and early software development and testing continue to increase.

- What can I do with a virtual prototype?

- "Virtual prototyping results in faster time-to-market through earlier and faster software development and improved communication throughout the supply chain. They enable software engineers to start development months before the hardware design is complete, enabling full system bring-up to occur within days of silicon availability. Virtual prototypes are fast, fully functional software models of complete systems that execute unmodified production code and provide unparalleled debug efficiency.

- See more at: <u>http://www.synopsys.com/prototyping/virtualprototyping/Pages/default.aspx#sthash.5y7mdELS.dpuf</u>

#### **Introduction to the Class**

We will analyze the S32V234 vision processor shown on the next slides.

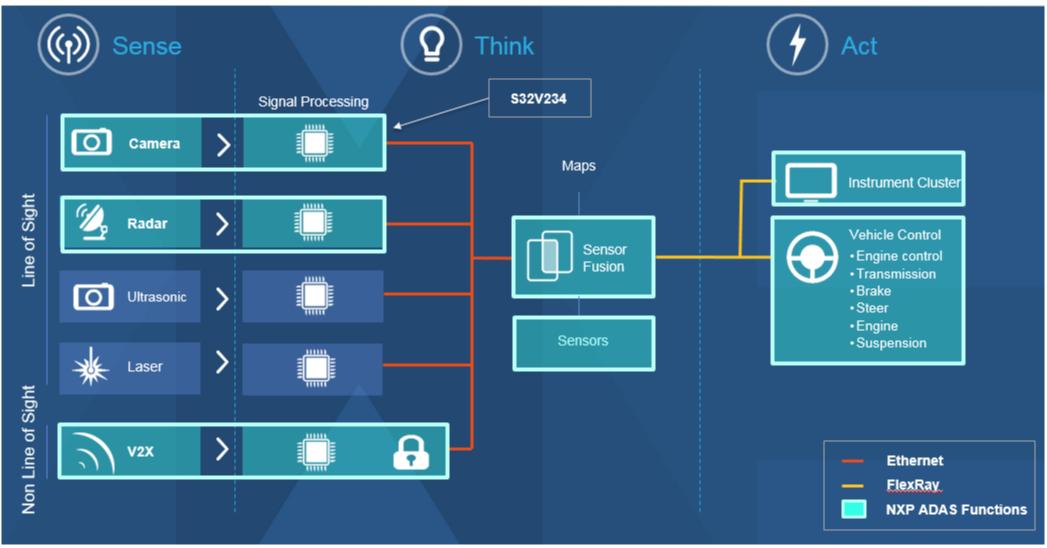

#### **ADAS System Solution**

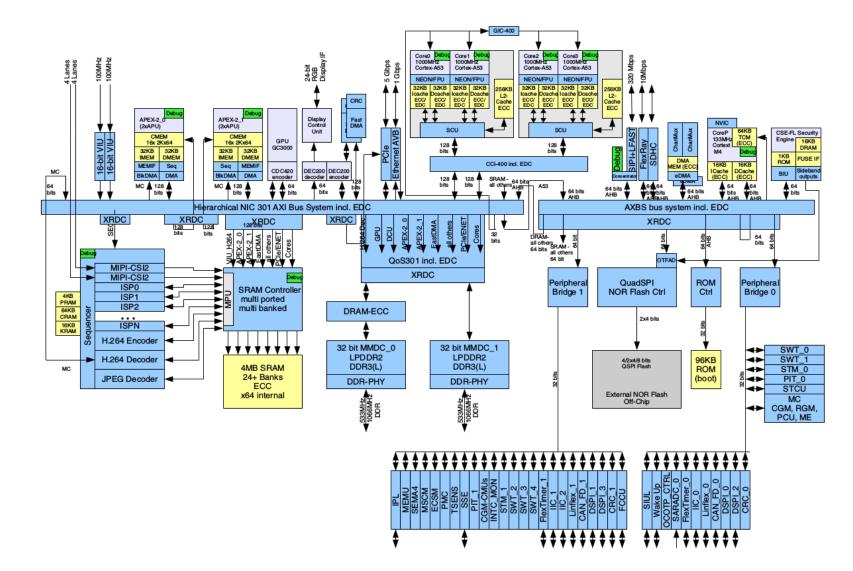

#### S32V234 Block Diagram

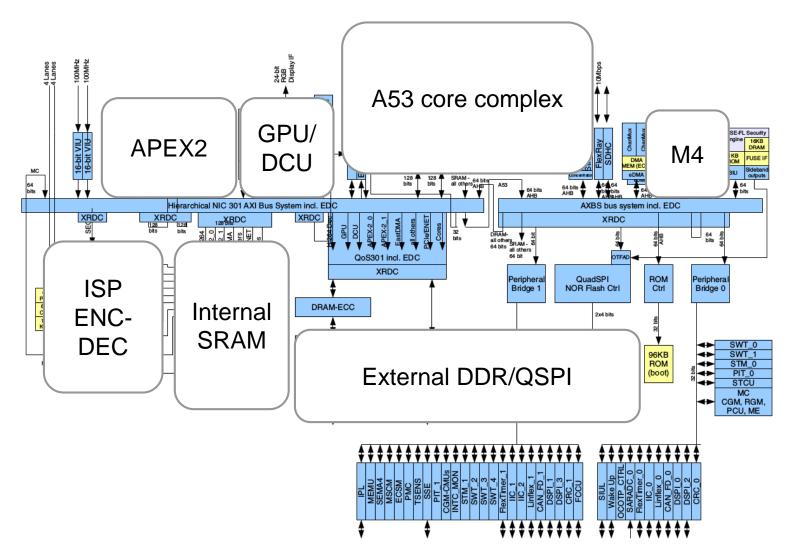

#### S32V234 Block Diagram

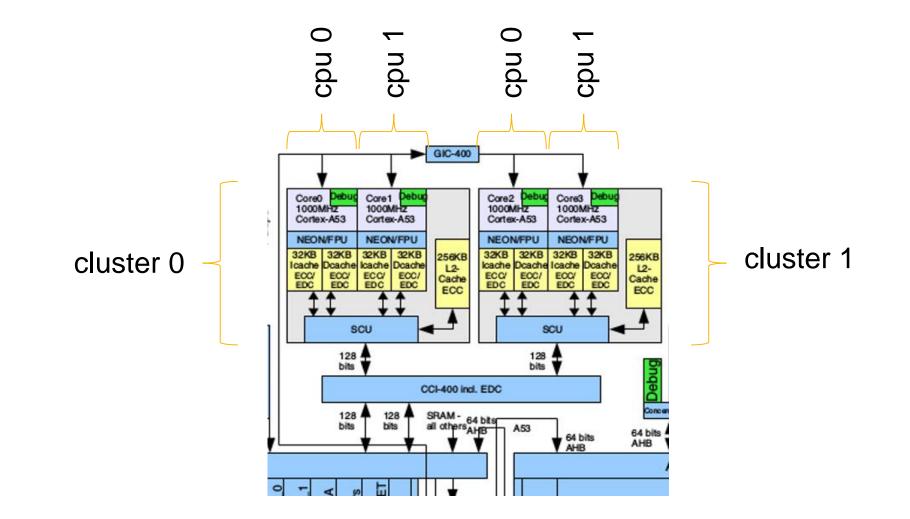

#### S32V234 based on -A53 Cluster Definition

## DEMOS AND HANDS ON LABS

#### GETTING STARTED WITH YOUR S32V234 VIRTUAL PROTOTYPE

#### SECURE CONNECTIONS FOR A SMARTER WORLD

#### <TO DO: Get slides from Mojin and Aneesh for Linux boot>

#### Launch VP Explorer

• Double click this icon

### **VP Explorer**

- VP Explorer (vpx) is launched by default and starts the virtual prototype simulation.

- VP Explorer is primarily intended to:

- Run and debug SystemC based simulations in depth.

- Control simulation execution.

- Trace and analyze simulation output during or after simulation.

- The VP Explorer controls the execution of the virtual prototype, like, suspending the entire virtual prototype. In this case, the entire platform state is frozen, including all timers and clocks. On resuming the execution, the virtual prototype continues from that exact point. As suspending the simulation has no impact on the platform state, it is called non-intrusive.

#### A53 Test SW

- Select the TestSW-A53 skin from the VP Config: drop down box

- Click OK

| 🚰 Open VP Config 🔤 |                                           |  |  |

|--------------------|-------------------------------------------|--|--|

| Select the         | /P Project and VP Config                  |  |  |

| VP Project:        | C:\Synopsys\simulation                    |  |  |

|                    | TestSW-A53                                |  |  |

|                    | Launch simulation after opening VP Config |  |  |

| Details            |                                           |  |  |

| VP Config:         | TestSW-A53                                |  |  |

|                    |                                           |  |  |

| VP Project:        | system                                    |  |  |

| _                  |                                           |  |  |

|                    |                                           |  |  |

|                    |                                           |  |  |

|                    |                                           |  |  |

|                    |                                           |  |  |

|                    | OK Cancel                                 |  |  |

|                    |                                           |  |  |

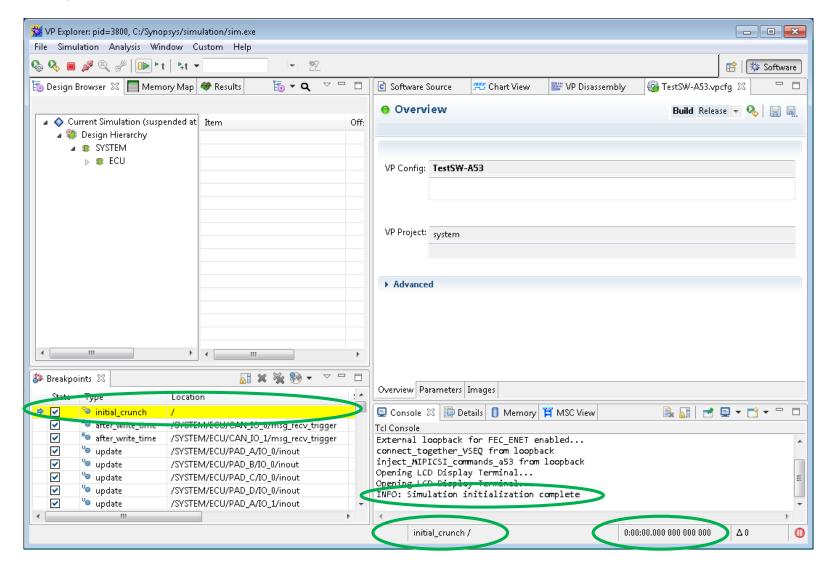

#### **Check Your System**

#### **VP Explorer: Important Tool Buttons**

| Toolbar icons |         | Description                                                                            |

|---------------|---------|----------------------------------------------------------------------------------------|

|               | Resume  | Resumes suspended simulation.                                                          |

|               | Pause   | Pauses a running simulation.                                                           |

|               | Stop    | Stops a simulation. All cores and all peripherals are frozen. Simulation resets        |

| 69            | Restart | Restarts the simulation. In this virtual prototype skin, all images are also reloaded. |

|               |         |                                                                                        |

#### **Description and Location of Tool Bar Buttons**

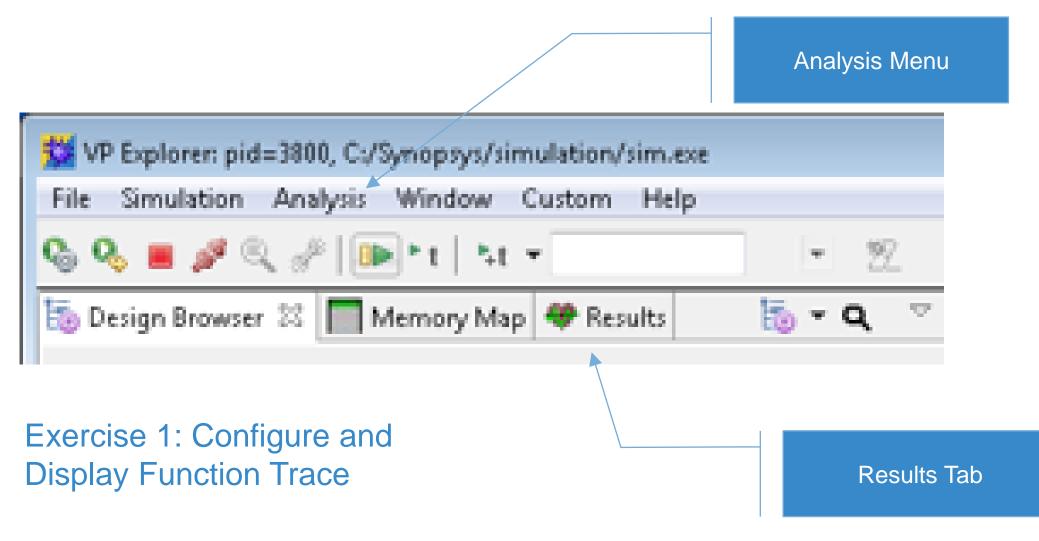

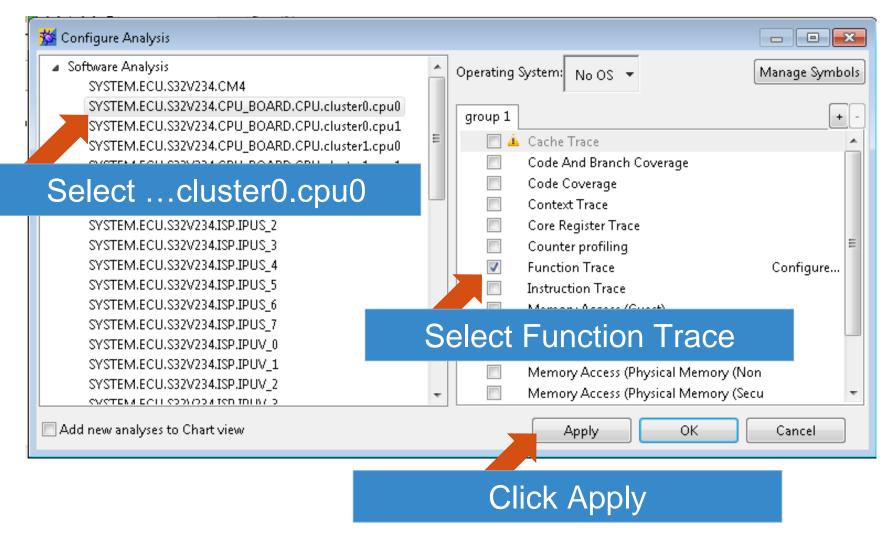

#### **Set Up Function Trace**

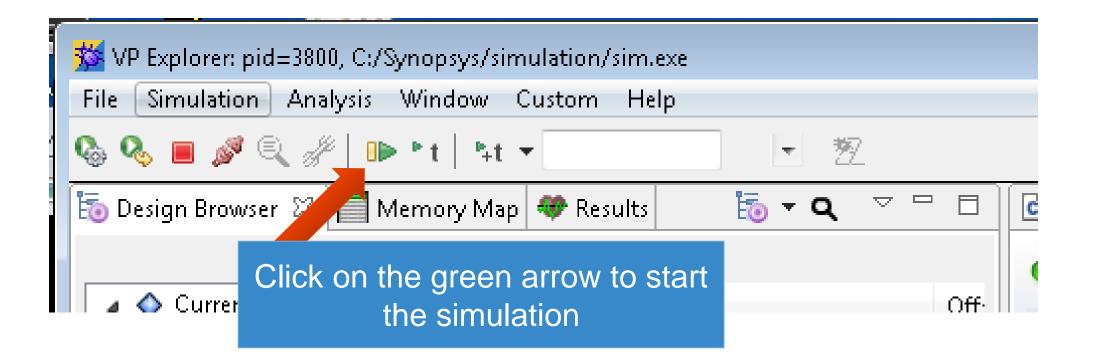

#### **Run the Simulation**

#### **Check Your System**

#### **Next Steps: Hands-on**

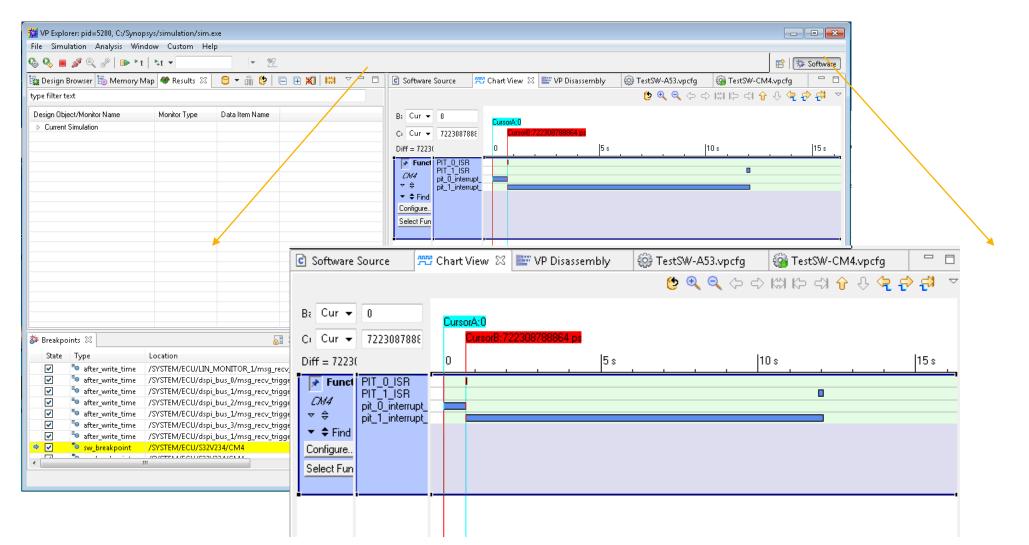

- Exercise 2: Configure the Results window

- Send results to Function Trace

- Filter function trace results for Programmable Interval Timer (PIT\_0) and PIT\_1 functions:

- PIT\_0\_ISR

- PIT\_1\_ISR

- pit\_0\_interrupt\_test

- pit\_1\_interrupt\_test

- Measure PIT\_0 and PIT\_1 elapsed time

- PIT\_0 elapsed time = \_\_\_\_\_

- PIT\_1 elapsed time = \_\_\_\_\_

- Show how to reduce PIT\_1 timer from 12 seconds to 700 ms

#### **Check Function Trace**

HANDS-ON LAB: STARTING LAUTERBACH TRACE32 DEBUGGER

2.1

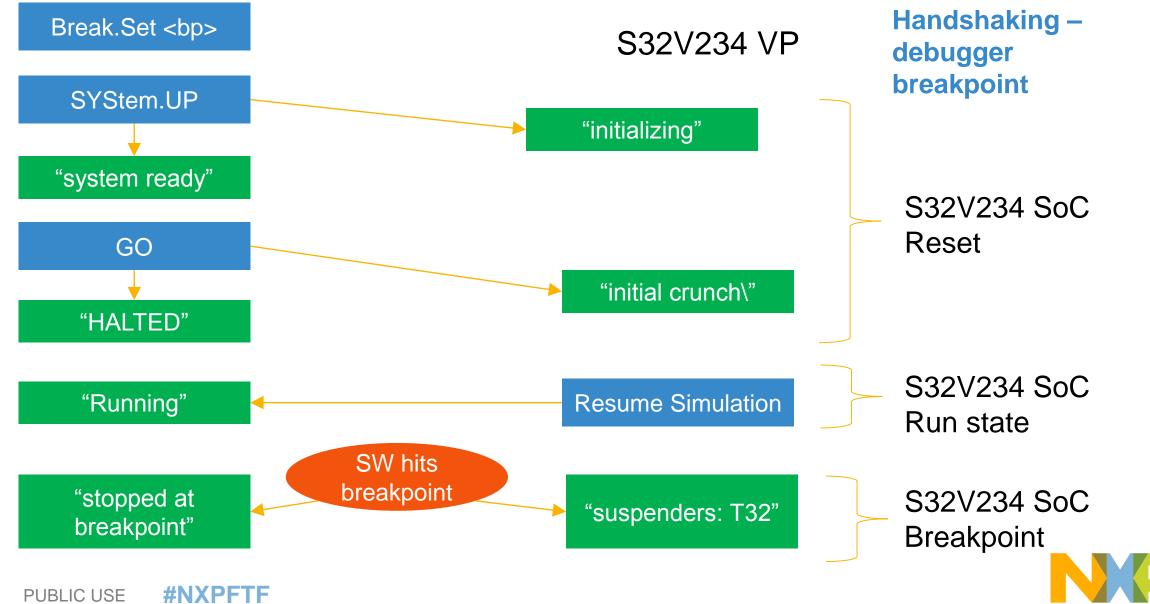

### **Debugger Operation: Goals**

- Startup Lauterbach TRACE32 debugger

- Operate debugger and Virtual Prototype in tandem

- Set a breakpoint

- Run to breakpoint

- Modify S32V234 Vision Processor values from the debugger

### Handshaking

= user action blue "green" = status TRACE32 Debugger • S32V234 VP SYStem.UP "system ready" "initializing" S32V234 SoC Reset GO "initial crunch\" "HALTED" S32V234 SoC **Resume Simulation** "Running" Run state

### **TRACE32 Debugger**

31

#### **Exercise 3:**

- Break.set <function name> run to the pit\_0\_timer and pit\_1\_timer interrupt routines, break at the start of the routines

- Inspect the code how is it configuring the load value?

#### **Exercise 4**

- Reduce test time from 12 seconds to 2 seconds

- Option 1: Debugger run-time control halt, modify, resume

- Option 2: Debugger patch of code at start-time

- Option 3: Use a precompiled \*.elf file with the change from 0x0FFF\_FFFF to 0x00FF\_FFFF. Rerun the test with the new elf file and confirm PIT\_1 elapsed time changes from 12 seconds to 700 ms

## Exercise XYZ: Create a New Skin & Run APEX-CV and/or ISP Demo

- Startup APEX-CV or ISP demo.

- Need Aneesh to port it over to VDK.

- Need Mojin to show steps for creating new VDK skin

- -Run sobel filter

- -Run test of all filters

- <TO DO: Add slides for creating a new skin>

### **APEX-CV Example Code**

\* Main function int main(int, char\*\*) { //... test apexcv filter(); test apexcv color conversion(); test apexcv arithmetic(); test apexcv interpolation(); test apexcv histogram(); test apexcv integral image();

return 0;

}

35

#### **APEX-CV Code Example**

```

#include <apexcv_base_integral_image.h> //header for apexcv integral image

using namespace apexcv; //optional if not using apexcv::

int test_integral_image(const unsigned char *src, int w, int h)

{

int lRetVal = 0;

apexcv::IntegralImage i; //create class object

DataDescriptor srcImg(w, h, DATATYPE_08U); //create src buffer

memcpy(srcImg.GetDataPtr(), src, w*h); //copy external content into src buffer

DataDescriptor dstImg(w, h, DATATYPE_32U); //create dst buffer

if ( srcImg.IsOK() && dstImg.IsOK() ) {

lRetVal |= i.exec(srcImg, dstImg); //run implementation

} else {

|| RetVal | = 1;

}

//TO SOMETHING WITH dstImg

srcImg.SetFreeOnExit(true); //free buffers on exit

```

```

dstImg.SetFreeOnExit(true); //free buffers on exit

dstImg.SetFreeOnExit(true); //free buffers on exit

```

```

return lRetVal;

```

## CONCLUSION

#### Conclusion

- In today's class, you learned:

- Definition and benefits of a Virtual Prototype

- How to start the Synopsys VDK and configure / view function trace

- How to run VDK demos

- Linux boot

- A53

- ISP/APEX

- How to modify code and re-test

- How to create a new VDK skin for an existing Vision SDK demo

#### Conclusion

The S32V234 Virtual Development Kit speeds your time to market for vision processing solutions:

1) Developers can start early, develop full chip software

2) In tandem, programmers can develop comprehensive regression test suites

3) This results in very rapid porting of highquality code once hardware evaluation systems become available

NXP: FUELING AUTOMOTIVE INNOVATION

The second of the second of the second

m

RINSPEED

### SECURE CONNECTIONS FOR A SMARTER WORLD

#### ATTRIBUTION STATEMENT

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, CoolFlux, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE, MIFARE Classic, MIFARE DESFire, MIFARE Plus, MIFARE FleX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TrenchMOS, UCODE, Freescale, the Freescale logo, AltiVec, C 5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. ARM, AMBA, ARM Powered, Artisan, Cortex, Jazelle, Keil, SecurCore, Thumb, TrustZone, and µVision are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. ARM7, ARM9, ARM11, big.LITTLE, CoreLink, CoreSight, DesignStart, Mali, mbed, NEON, POP, Sensinode, Socrates, ULINK and Versatile are trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2015–2016 NXP B.V.