Industrial Networking: Leverage QorlQ Communications Processors for PROFIBUS, PROFINET, EtherNet/IP, CAN, etc.

APF-IND-T0049

Hao Sun

JAN.2015

External Use

Presentie, the Pressoure tops, ANNec, C-6, CodeTEST, CodeWarrov, ColdPine, ColdPine, O-Nere, the Energy Efficient Solutions tops, Kinetis, Magnik, mobiledT, FEG, PowerGLOG, Processer Expent, CavID, Gardi Camerage, Cavine, Ready Pale, SaleAsaev, the SaleAsaev tops, SterCore, Styrphinov, VortiCa, VyOrk and Xinnels are tradomarks of Presented Semiconductor, Inc, Reg. U.S. Pat. & Thr. O.H. Antal, BeeKS, Bardistan, Caminet, Field, Expensate, MXX, Partonni e Postage, QUEC Engine, SMARTMOS, Tawer, Tartolula and UMEMS are tradomarks of Presental Demiconductor, Inc. All other product or service normal and their resperty of their teaperchards (2015) Freescale Demiconductor, Inc.

## Agenda

- Protocols

- Serial Based Protocols

- Ethernet

### **Protocols and Physical Interfaces**

|           |                                                    |                                                | *****                                                    |                               |

|-----------|----------------------------------------------------|------------------------------------------------|----------------------------------------------------------|-------------------------------|

|           | IEEE 802.11                                        | IEEE 802.3                                     | RS485                                                    | CAN                           |

| Interface | PCIe/USB/SPI/I <sup>2</sup> C                      | MII/RMII/RGMII/SGMII                           | UART/QE UCC                                              | CAN                           |

| Topology  | Multi Point                                        | Point to Point                                 | Multi Drop                                               | Multi Drop                    |

| Distance  | 70 – 250m                                          | 100m                                           | 100 – 1,200m                                             | 40 – 1,000m                   |

| Protocol  | profit <sup>®</sup>                                | ppop p <sup>®</sup><br>Dait                    | PROFU®<br>IBUSI                                          |                               |

|           | Modbus TCP/IP                                      | Modbus TCP/IP                                  | Modbus                                                   |                               |

|           | EtherNet/IP                                        | EtherNet/IP                                    |                                                          | DeviceNet                     |

|           | POWERLINK                                          | POWERLINK                                      |                                                          |                               |

|           | CANopen                                            | CANopen                                        |                                                          | CANopen                       |

|           |                                                    | EtherCAT. Master                               |                                                          | J1939                         |

|           | P-Series<br>T-Series<br>MPC8309 (PCI)<br>LS-Series | P-Series<br>T-Series<br>MPC8306/9<br>LS-Series | P1025/16/21/16<br>T1040/42/20/22<br>MPC8306/9<br>LS102xA | P1010<br>MPC8306/9<br>LS102xA |

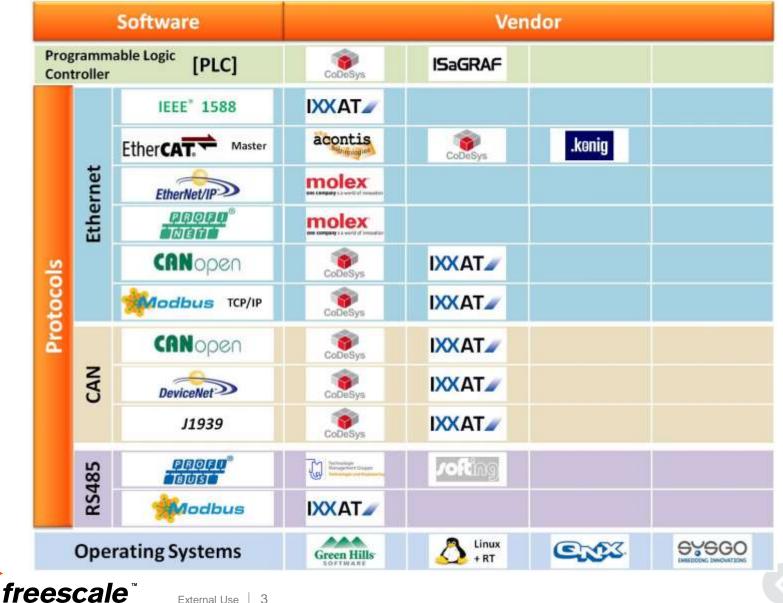

### **Industrial Support Software**

# **Serial Based Protocols**

UART CAN PROFIBUS

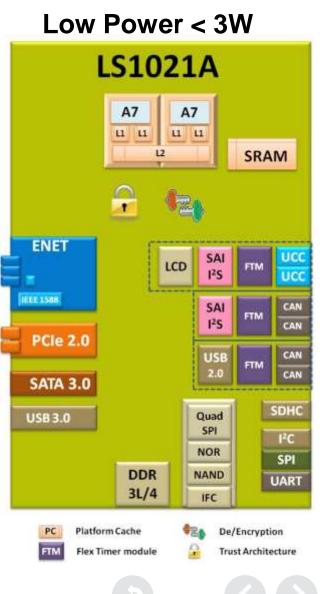

### **Example Device that Covers Most of the Protocols**

|        |                           | LS1021A                                                     | LS1020A            | LS1022A                              |  |

|--------|---------------------------|-------------------------------------------------------------|--------------------|--------------------------------------|--|

|        | Core Type                 | ARM Cortex <sup>™</sup> -A7 MPCore <sup>™</sup> + NEON      |                    |                                      |  |

| owered | Cores/Threads             | 2/2                                                         |                    |                                      |  |

|        | Frequency                 | Up to 1GHz                                                  |                    | Up to 600MHz                         |  |

| RM     | L1 I/D                    |                                                             | 32kB / 32kB with E | ECC                                  |  |

|        | L2 (Unified)              | 512kB Shared with ECC                                       |                    |                                      |  |

|        | SRAM                      | 128kB with ECC                                              |                    |                                      |  |

|        | DDR                       | 1x(16/32B it+ECC) DDR3L/4 up to<br>1.3GT/s                  |                    | 1x( 16bit+ECC)<br>DDR3Lup to 1.0GT/s |  |

|        | SerDes                    | 4 up to 6.0GHz                                              |                    | 1 up to                              |  |

|        | Ethernet                  | 3 x 1GE                                                     |                    | 2 x 1GE                              |  |

|        | PCle                      | 2 x Gen 2.0 (up to 5.0GT/s)                                 |                    | 1 x Gen 2.0 (up to<br>5.0GT/s)       |  |

|        | SATA 3.0                  | 1 up to 6.0GHz                                              |                    | No                                   |  |

|        | USB                       | 1 x USB 3.0,1 x USB 2.0                                     |                    | 1 x USB 2.0                          |  |

|        | CAN                       | Up to 4                                                     | 0                  | Up to 4                              |  |

|        | TDM/HDLC                  | 2                                                           |                    | No                                   |  |

|        | UART/I <sup>2</sup> C/SPI | Up to 8 / 3 / 2                                             |                    |                                      |  |

|        | l²S                       | Up to 4                                                     |                    |                                      |  |

|        | LCD                       | 1 x Controller                                              |                    | No                                   |  |

|        | Acceleration              | SEC,QE                                                      |                    | No                                   |  |

|        |                           | Trusted architecture<br>Pin Compatible 19x19mm, 0.8mm pitch |                    |                                      |  |

|        |                           |                                                             |                    |                                      |  |

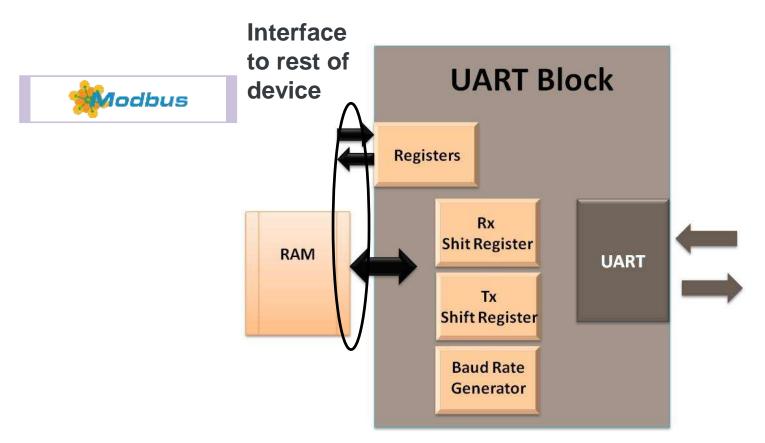

### **Simplified UART Hardware Block**

Hardware block to perform the UART function

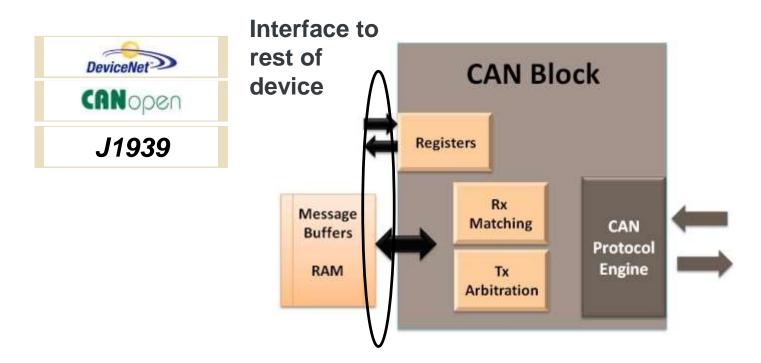

### **Simplified CAN Hardware Block**

The CAN 2.0 B protocol specification is performed in a hardware block

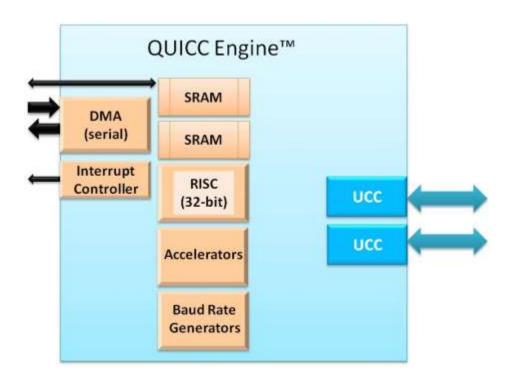

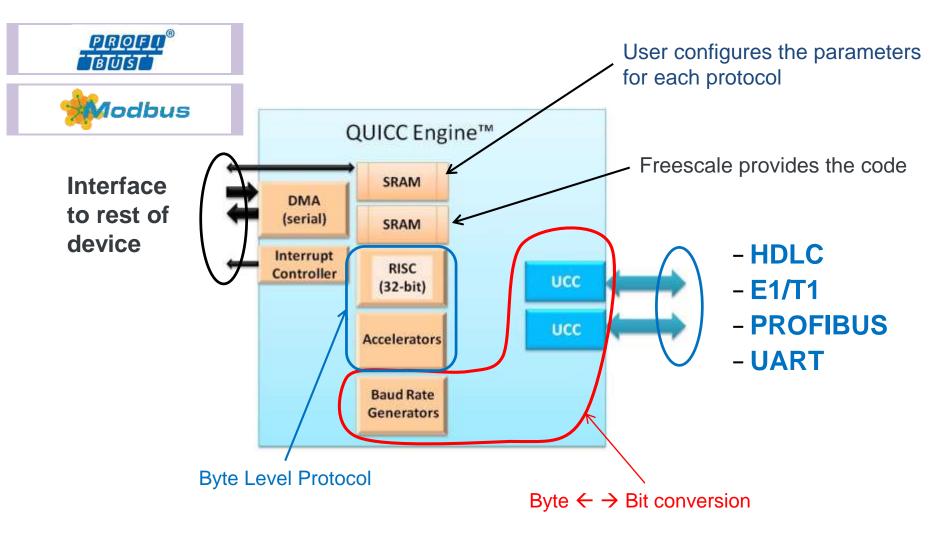

## Simplified QUICC Engine Block Diagram

### **Protocols**

- Ethernet

- ATM

- HDLC

- E1/T1

- PROFIBUS

- UART

### Simplified QUICC Engine Block Diagram

### **Example Protocol PROFIBUS**

#### www.freescale.com/profibusQorIQ

Single-chip PROFIBUS Reference Platform for QorlQ and PowerQUICC Processors 🕸

#### Descenantation: Software & Tools Day / Parametrics Overview

#### Big

With over 20 million mutated notes. PROFIBUS is the sortf's most successful fieldius (communication) technology used in industrial automation systems. Ongoing proofs of alound 10 percent per year is forecasted and this expansion is aided by the addition of PROFIEUS functionality to Fraescale's PowerQUICC and QorlQ communications processors. The integration of PROFIBUE Layer 2 stearies a single-chip solution with a situal convection to a H3482 transceiver. This eliminates the total and Scard space Associated with an external PROFIBUE ADIC, which is otherwise required

Building on the versatility and long-term success of QUICC Ergine technology, Pressoale offers PROPIBUS Lever 2 Remnare for PowerGLICC and DorfD processors with a GUICE Digne controller. This actuation not only removies the least for a costly PROFIBUE ADC. It also leaves the processor core aimost artively Tree for application processing.

GoriQ processors can also provide simultaneous support for industrial Ethernel protocole like PROFINET, EtherCA78 and Strattlet1P\*\*

#### Features

- . FROFIELD Reference Platform suggests

- · PROFIBUE Stave certified by ComDec. a PROPIBUS certification lab heated by Semana AG FROFIEUS Master

- · Eliminates coarty PROPIEUS PROA or ARIG by running PROFIELDS Layer 2 (PDL) on QUICE Engine controller Randourre integrated inside the MPU

- · Protocol and oustomiar control application can run simultaneously us one chip

- Conversal PROFIEUS slave stack available from Tasimologia Managament Grussei (TMO)

MPCIDDE PaverGL/ICIC presenant

900 MHz or 1920 DMRPG per core) GarlQ P1 processors can also provide simultaneous eupport for industrial Ethernel platadols like PROFINET.

EtharCAT and EtharNet/IPTe Prese/QUICCC MPCERIP processor delivers at munazarua 835 CMIPS core performance for less than

- Evaluate using Towar System motives (7WH-P1025-417)

- Bothware and hardware developed on TWR-P1025 can be

riptions which integrate Prover Antitutanture® notes (up to

- Suppost on a range of Gorld P1 processors, including the P1G12 P1G21 P1G18 and P1G25 as well as the

- GortQ P1 processor family includes single- and dual-core

THIS TE Great **Peptared Video** PROFIDUE Solutions on Clerko and PowerQUICC The second second (22 Thirty and

**Feetured Partners**

Freestain and TMS T2 Develop First PROFIBUE interface Centred an Presentale Silvert White Paper, Managing Machine Ballery and Ptathotovity with

QuiriQ Multisary Processors Cannect with Us

Sign ob today to receive more information about industrial asiations.

QUICC Engine<sup>14</sup> SPARE TIMA inerial 12044 852 (12-64) Accelerates Band Sats fairwration

### For more information contact

T. R. watte

### iain.davidson@freescale.com or profibus@freescale.com

External Use 10

MPCEDDE Low-Power PowerGLICC II Pro Processor with DDH2, #80H40, 128-ch, HBLC/TDM, 10/100 Ethernet, USE I GolQ Computications Processors Value-Performance Ter-PROFILISES PROFILISES PROFILIS or Gold and

PowerGUICC Processors - Fast Sheet Jump Start Your Design

Getting Started With Pressure PROFIBUS for PasserQUICC a Pressoale offers PROFIBUS Layer 2 formers for PoweGUICE

#### Kit-Contoine

201

TWE-PUZZ-AIT SERVER

Supported Devices

Featured Documentation

100210 1108

- Towar System Davater Metale

- CortO PT MPU Taser System Medule

- Industrial I/D Timesr Dynam Mutule

- . An image of the complete PROFUELS sieve rundome asthuse including the layer 7 stack from TMG TR)

# Ethernet

External Use | 11

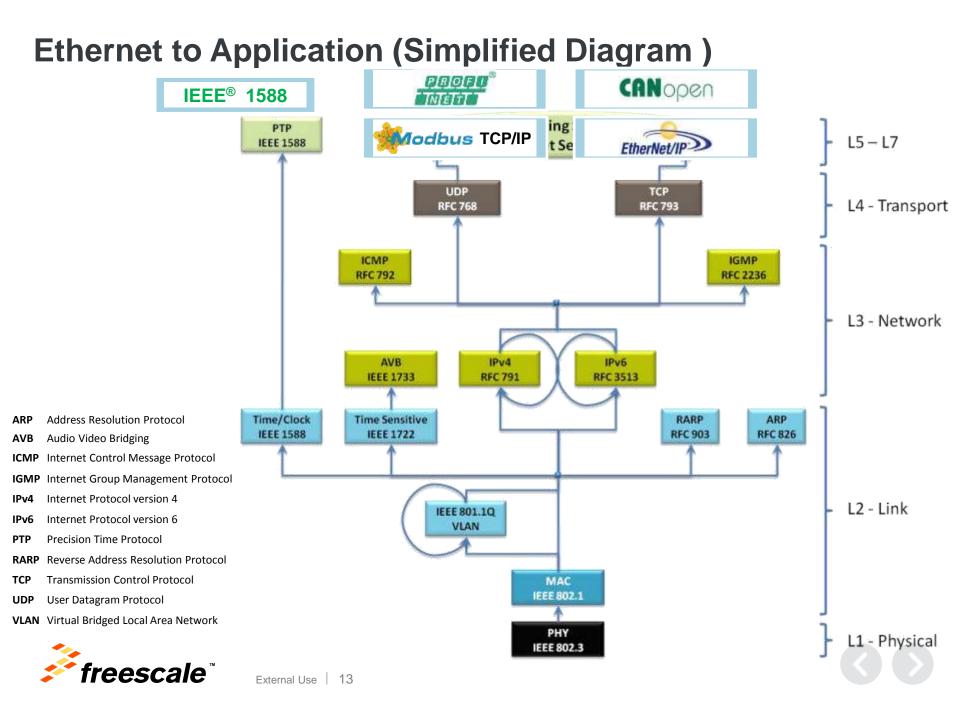

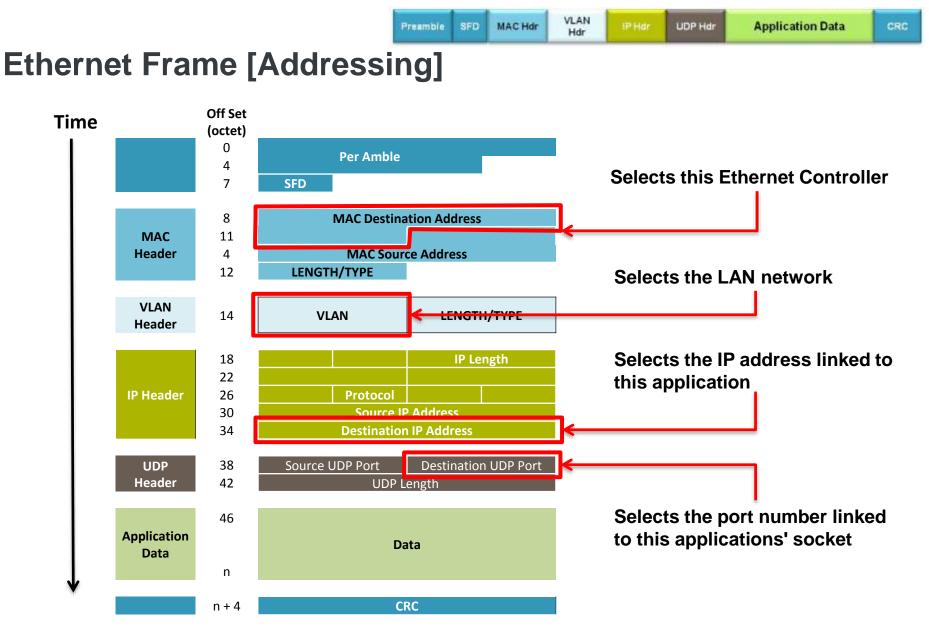

### **Internet Protocol / Ethernet**

- Machines (devices) are now using Internet Protocol (IP) over Ethernet more and more.

- To connect, you need an Ethernet controller with at least the capabilities of doing the low level media access control (MAC) linked to a physical interface (PHY).

- Applications do not generally directly "talk" IP. They normally use a software abstracted method, like sockets.

- So how do you get from the Ethernet to the application layer?

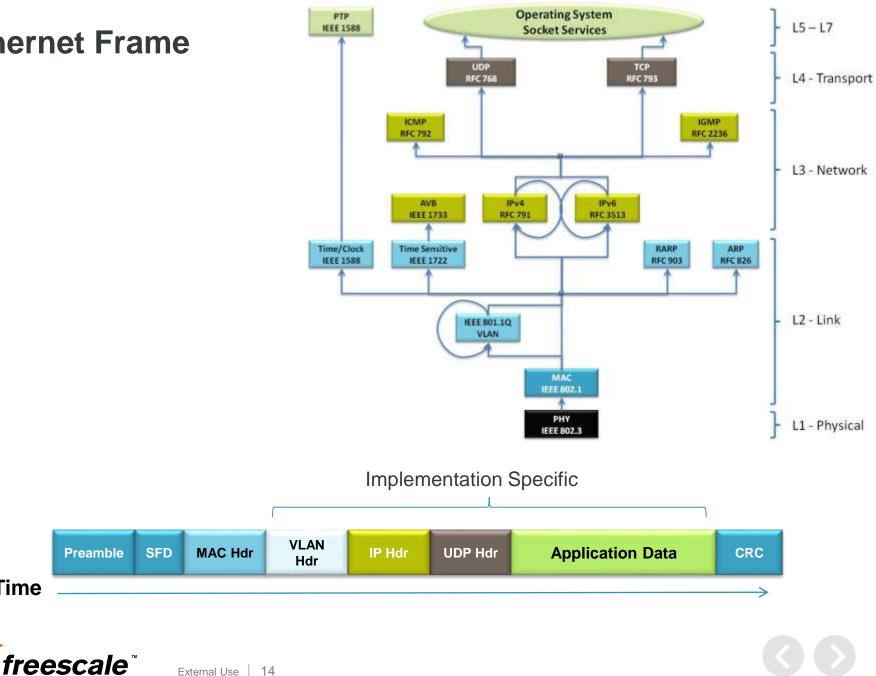

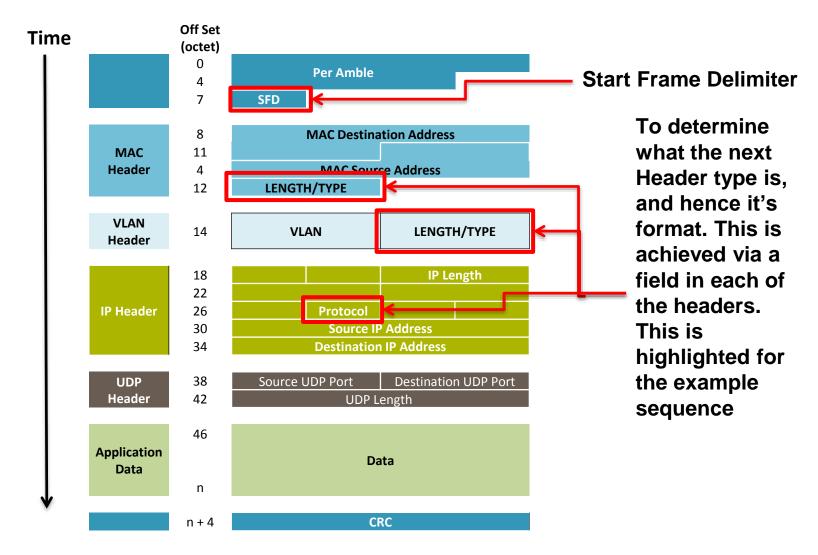

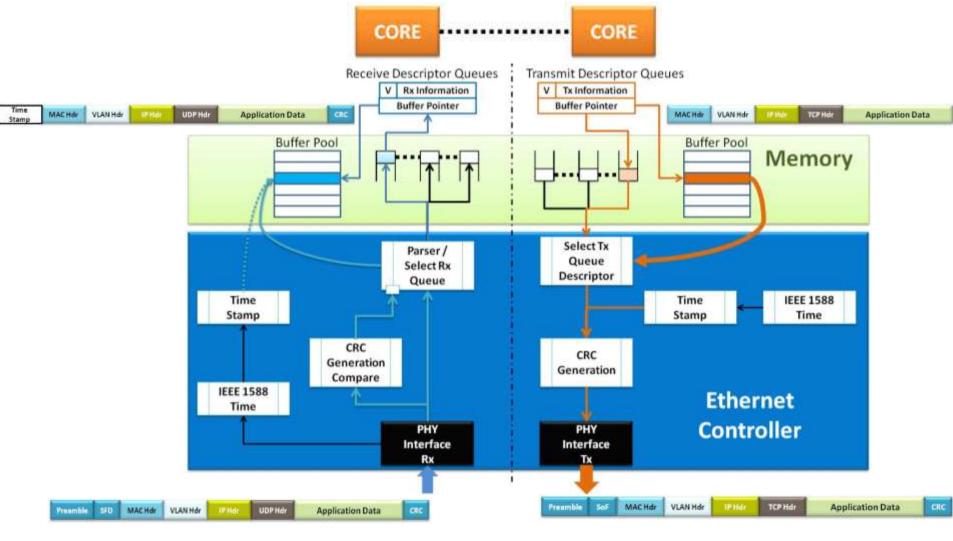

### **Ethernet Frame**

Time

Preamble SFD

IP Hdr

### **Ethernet Frame [Protocols]**

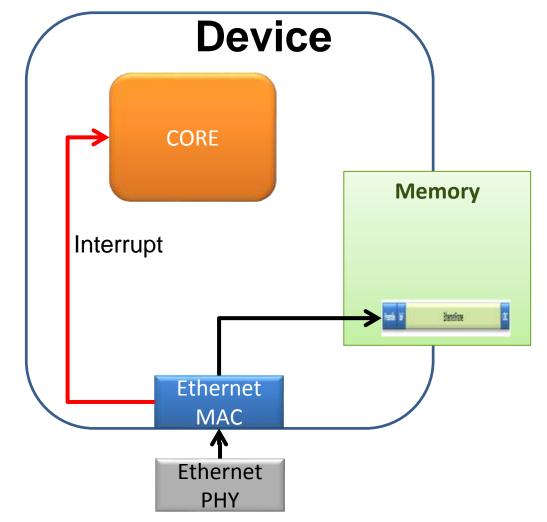

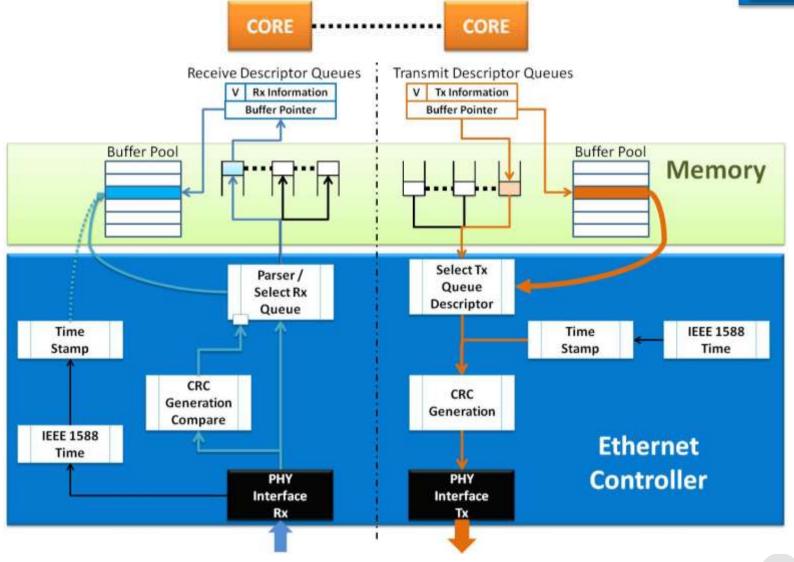

### **Basic Ethernet Controller**

### Ethernet Media Access Control (MAC) (Hardware)

- 1. On Receive detects Ethernet Frame and places it into memory

- 2. On Transmit takes the contents of memory and sends it to the PHY

External Use | 17

### **Different Types of Ethernet Controllers**

### **SIMPLE Controller**

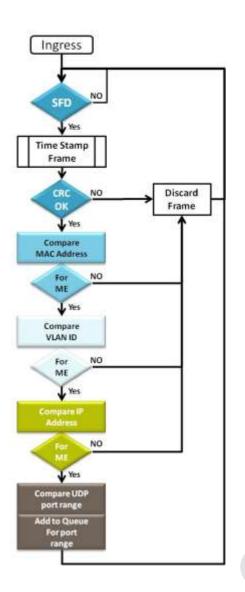

#### Ingress

This takes each of the received frames from the PHY and places them into a buffer and informs the CORE/CPU Checks CRC to see if the frame is valid

#### Egress

CORE passes a buffer containing the frame to be transmitted and the controller DMAs it to the PHY Generates the CRC for the frame being transmitted

#### **IEEE 1588 Assist**

In addition to the functions performed by SIMPLE controller, it performs:

#### Ingress

Copies the value of the IEEE 1588 clock when SFD is detected and the value is passed to the CORE/CPU referenced to this received frame

#### Egress

If the frame is flagged to have the IEEE 1588 time stamp included, the controller copies the value of the IEEE 1588 clock to the time stamp field

### **QUEUE** Assist

In addition to the functions performed by IEEE 1588 Assist controller, it performs:

#### Ingress

There is a comparison performed on fields in the frame being received, to determine which queue that the information about this frame is placed in for the CORE/CPU

#### Egress

A round robin or some other selection method is used to check the transmit queues to obtain the next frame to be transmitted

Hdr

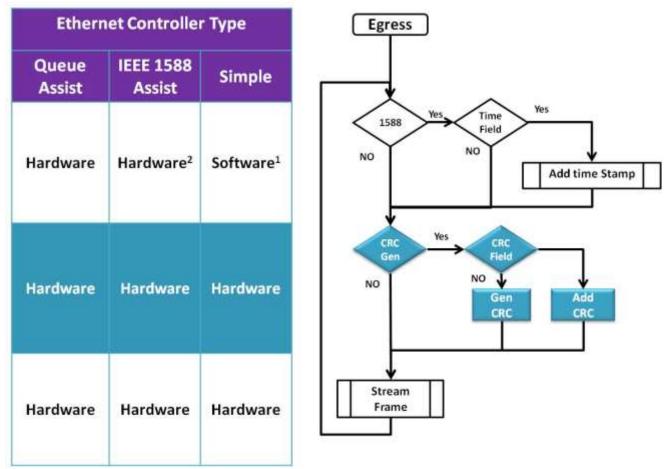

### **Features of Ethernet Controllers (INGRESS)**

| Ethernet Controller Type |                     |          |  |  |

|--------------------------|---------------------|----------|--|--|

| Queue<br>Assist          | IEEE 1588<br>Assist | Simple   |  |  |

| Hardware                 | Hardware            | Hardware |  |  |

| Hardware                 | Hardware            | n/a      |  |  |

| Hardware                 | Hardware            | Hardware |  |  |

| Hardware                 | Software            | Software |  |  |

| Hardware                 | Software            | Software |  |  |

| Hardware                 | Software            | Software |  |  |

| Hardware                 | Software            | Software |  |  |

UDP Har

### **Features of Ethernet Controllers (EGRESS)**

- 1. Software has to generate the frame, then pass it to the Ethernet Controller, hence for PTP the time stamp will have a larger jitter than a hardware implementation

- 2. Will be required to generate the checksums for UDP/TCP/IP if they are required by the system

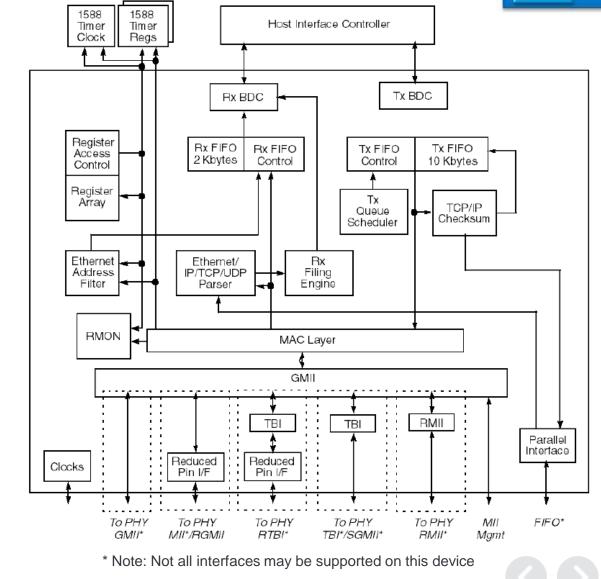

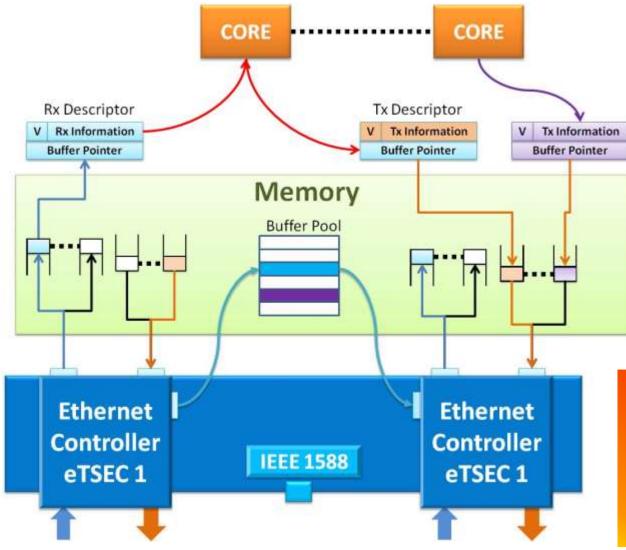

## **Ethernet Controller in Value-Performance QorlQ**

This is called the Enhanced Three-Speed Ethernet Controller (eTSEC).

eTSEC falls into the Queue Assist category of Ethernet controllers.

There is also virtualization support in the latest versions.

ENET

**IEEE 1588**

### Simplified View of Ethernet Controller (eTSEC) **IEEE 1588**

ENET

-

## Frame Flow through the eTSEC

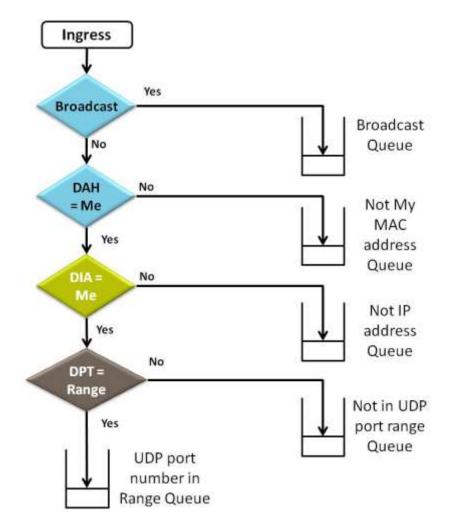

### **Simple Parsing Flow**

|       | IEEE 1588                                                             |  |  |

|-------|-----------------------------------------------------------------------|--|--|

|       |                                                                       |  |  |

|       |                                                                       |  |  |

| Field | Description                                                           |  |  |

| MASK  | Generic MASK                                                          |  |  |

| DAH   | Destination MAC address most significant 24 bits                      |  |  |

| SAH   | Source MAC address, most significant 24 bits                          |  |  |

| SAL   | Source MAC address, least significant 24 bits                         |  |  |

| ETY   | Ethertype of next layer protocol                                      |  |  |

| VID   | VLAN network identifier (as per IEEE Std 802.1Q)                      |  |  |

| PRI   | VLAN user priority (as per IEEE Std 802.1p)                           |  |  |

| TOS   | IPv4 header Type Of Service field or IPv6 Traffic Class field         |  |  |

| L4P   | Layer 4 protocol identifier as per published IANA specification       |  |  |

| DIA   | Destination IP address (IPv4 or IPv6 header) 32 most significant bits |  |  |

| SIA   | Source IP address (IPv4 or IPv6 header) 32 most significant bits      |  |  |

| DPT   | Destination port number for TCP or UDP headers                        |  |  |

| SPT   | Source port number for TCP or UDP headers                             |  |  |

Parser also knows protocol header definitions and the user can instruct a decision tree

ENET

### **Simple Switch Application**

Parser places in Switch Queue if not for this device, excluding broadcast frames

Core only needs to move pointer to Tx queue

f**reescale**"

This shows some of the capabilities of the eTSEC used in the QorlQ family of communications processors from Freescale.

Note the eTSEC Ethernet controller is just the junior member of the Ethernet controllers used in the QorlQ family, in both hardware acceleration and line rate performance.

For more information go to http://www.freescale.com/QorlQ

## Introducing The QorlQ LS2 Family

Breakthrough, software-defined approach to advance the world's new virtualized networks New, high-performance architecture built with ease-of-use in mind Groundbreaking, flexible architecture that abstracts hardware complexity and enables customers to focus their resources on innovation at the application level

#### **Optimized for software-defined networking applications**

Balanced integration of CPU performance with network I/O and C-programmable datapath acceleration that is right-sized (power/performance/cost) to deliver advanced SoC technology for the SDN era

#### Extending the industry's broadest portfolio of 64-bit multicore SoCs

Built on the ARM® Cortex®-A57 architecture with integrated L2 switch enabling interconnect and peripherals to provide a complete system-on-chip solution

### **QorlQ LS2 Family**

**Key Features**

.....

200302 \*\*\*\*

Unprecedented performance and ease of use for smarter, more capable networks

SDN/NFV

Switching

Data

Center

Wireless

Access

# High performance cores with leading interconnect and memory bandwidth

- 8x ARM Cortex-A57 cores, 2.0GHz, 4MB L2 cache, w Neon SIMD

- 1MB L3 platform cache w/ECC

- 2x 64b DDR4 up to 2.4GT/s

# A high performance datapath designed with software developers in mind

- New datapath hardware and abstracted acceleration that is called via standard Linux objects

- 40 Gbps Packet processing performance with 20Gbps acceleration (crypto, Pattern Match/RegEx, Data Compression)

- Management complex provides all init/setup/teardown tasks

### Leading network I/O integration

- 8x1/10GbE + 8x1G, MACSec on up to 4x 1/10GbE

- Integrated L2 switching capability for cost savings

- 4 PCIe Gen3 controllers, 1 with SR-IOV support

- 2 x SATA 3.0, 2 x USB 3.0 with PHY

### See the LS2 Family First in the Tech Lab!

### 4 new demos built on QorlQ LS2 processors:

Leave the Packet Processing To Us

Combining Ease of Use with Performance

External Use

29

Tools for Every Step of Your Design

www.Freescale.com

© 2015 Freescale Semiconductor, Inc. | External Use