# Design with QorlQ T2081 and T1040 Processor Families APF-SNT-T1360

Xiaobo Xie Chun Chang | Application Engineer A U G . 2 0 1 5

External Use

Presents, the Pressure top, AllVec, C-8, Code/TEST, Code/Verror, ColdPire, Co-New, the Energy Efficient Solutions top, Kinetis, Magn/K mobileDT, PED, PowerQLGG, Processer Expert, Carlo, Carlo Commerg, Dorive, Newly Pier, SelbAsane, the SalaAssare top, Sterbine, Styrephory, VertiCa, Vytol and Kineto are todernarks of Pressula Semiconductor, Inv., Reg, U.S. Pat, & Tm. Off, Antal, BeeKG, BeeStack, Danklet, Field, Layerscape, MXC, Partorn in a Package, QUEC Engine, SMAPTINOS, Tawer, TartoLink and UMEUS are trademarks of Pressula Demiconductor, Inc. All later product or service normal and the property of their sepacetion service. B 2015 Pressula Beniconductor, Inc.

## **Session Introduction**

- This session is relevant for customers designing with

Freescale T2081 and T1040 family of QorlQ processors

- Details the commonalities and differences

- Examines the problems and solutions of common board design and migration from T1040 to T2081

- Provides practical examples based on existing Freescale designs

## **Session Objectives**

- After completing this session you will be able to:

- Identify the design collateral that exists to assist with T1040 and T2081 designs

- Recognize the major design issues for the common board design and how they can be overcome

- Use our design tips for high-speed interface design (eSDHC and SerDes)

- Know where to go for assistance

## Agenda

- T1040 and T2081 Overview

- Hardware Compatibility

- Software Compatibility

- Pinout Comparison

- Supporting Tools

External Use

3

Reference Documentation

## Agenda

- T1040 and T2081 Overview

- T1040 Block Diagram

- T2081 Block Diagram

- Device Comparison

- Commonalities and Differences

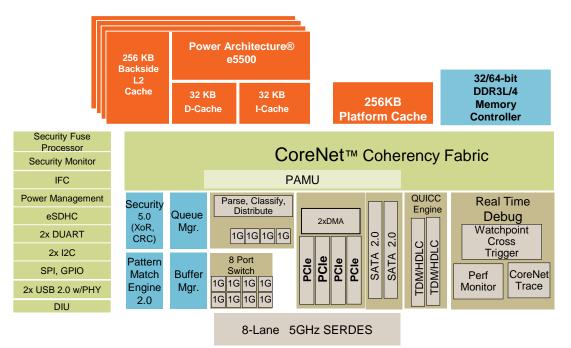

### T1040

#### Device

- 780-pin FC-PBGA package

- 23x23mm, 0.8mm pitch

#### **Power targets**

Enable Convection cooled system design

#### **Datapath Acceleration**

- SEC- crypto acceleration

- PME- Reg-ex Pattern Matcher

#### Processor

- 4x e5500, 64b, up to 1.4GHz

- Each with 256KB backside L2 cache

- 256KB Shared Platform Cache w/ECC

- Supports up to 64GB addressability (36 bit physical addressing)

#### Memory Subsystem

32/64b DDR3L/4 Controller up to 1600MHz

#### CoreNet Switch Fabric High Speed Serial IO

- 4x PCIe Gen2 (5Gbps) Controllers

- 2x SATA 2.0, 3Gbps

- 2x USB 2.0 with PHY

#### **Network IO**

- FMan packet Parse/Classify/Distribute

- Lossless Flow Control, IEEE 1588

- Up to 4x 10/100/1000 Ethernet Controllers

- 8-Port Gigabit Ethernet Switch

- QUICC Engine

- HDLC, 2x TDM

#### **Green Energy Operation**

- Fanless operation quad-core 1.4GHz

- Packet lossless deepsleep

- Programmable wake-on-packet

- Wake-on-timer/GPIO/USB/IRQ

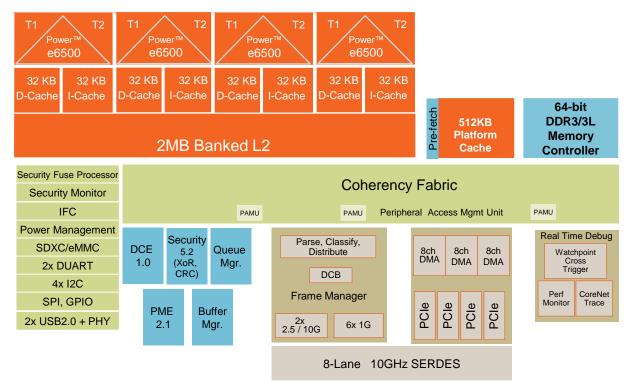

## **QorlQ T2081 Block Diagram**

#### **Datapath Acceleration**

- SEC- crypto acceleration 10Gbps

- DCE Data Compression Engine 17.5Gbps

- PME Pattern Matching Engine to 10Gbps

#### Processor

- 4x e6500, 64b, 1.5 1.8GHz

- Dual threaded, with 128b AltiVec

- 2MB shared L2; 256KB per thread

#### Memory Subsystem

- 512KB Platform Cache w/ECC

- 1x DDR3/3L Controllers up to 2.1GHz

- Up to 1TB addressability (40 bit physical addressing)

- · HW Data Pre-fetching

#### Switch Fabric

#### **High Speed Serial IO**

- 4 PCIe Controllers: one at Gen3, three at Gen2

- 1 with SR-IOV support

- x8 Gen2

- 2 USB 2.0 with PHY

#### **Network IO**

- Up to 25Gbps Simple PCD each direction

- 8 MACs multiplexed over:

- 2x 10GE, 2x 2.5Gb/s SGMII, 7x GE

- XFI, 10GBase-KR, SGMII, RGMII, 1000Base-KX

#### Device

- TSMC 28HPM Process

- 23x23mm, 780pins, 0.8mm pitch, pin compatible with T1042

- Power estimated at 18.7–24.4W (thermal) depending on frequency

Schedule: samples: 2H-2014; qual Q1-15

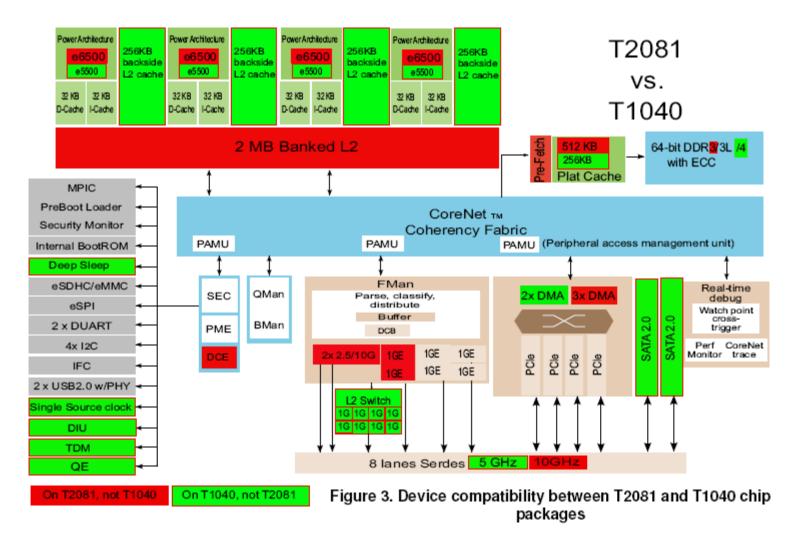

## **Device Comparison – T1040 and T2081**

## **Commonalities and Differences**

| Features                    | T2081                                            | T1040                           | T1042                           |  |  |  |  |

|-----------------------------|--------------------------------------------------|---------------------------------|---------------------------------|--|--|--|--|

|                             | Cores                                            |                                 |                                 |  |  |  |  |

| Number of cores             | 4 × e6500 dual<br>threaded Power<br>Architecture | 4 × e5500 Power<br>Architecture | 4 × e5500 Power<br>Architecture |  |  |  |  |

| Architecture width          | 64-bit                                           | 64-bit                          | 64-bit                          |  |  |  |  |

| Max frequency (MHz)         | 1800                                             | 1400                            | 1400                            |  |  |  |  |

| DMIPS/MHz                   | 6                                                | 3                               | 3                               |  |  |  |  |

|                             | Memo                                             | ry Size                         |                                 |  |  |  |  |

| L1 Cache                    | 32KB I/D                                         | 32KB I/D                        | 32KB I/D                        |  |  |  |  |

| L2 Cache                    | 2 MB shared                                      | 256KB / core backside           | 256KB / core backside           |  |  |  |  |

| CPC                         | 512KB frontside                                  | 256KB frontside                 | 256KB front side                |  |  |  |  |

| Cache line size             | 64 Bytes                                         | 64 Bytes                        | 64 Bytes                        |  |  |  |  |

| Memory Type                 | DDR3/3L @2133 MT/s                               | DDR3L/4 @1600 MT/s              | DDR3L/4 @1600 MT/s              |  |  |  |  |

| Maximum size of main memory | 32 GB (1Gbit x8<br>device)                       | 32 GB (1Gbit x8<br>device)      | 32 GB (1Gbit x8<br>device)      |  |  |  |  |

## **Commonalities and Differences (contd...)**

| Features                   | T2081                                              | T1040                                                   | T1042                                                    |  |  |  |  |  |

|----------------------------|----------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------|--|--|--|--|--|

|                            | I/O                                                |                                                         |                                                          |  |  |  |  |  |

| Ethernet controllers       | 2× XFI<br>6x SGMII<br>2x 2.5Gbps SGMII<br>2x RGMII | 2× 5Gbps QSGMII<br>6x 1Gbps SGMII<br>2x RGMII<br>1x MII | 6x 1Gbps SGMII<br>2x 2.5Gbps SGMII<br>2x RGMII<br>1x MII |  |  |  |  |  |

| SerDes lanes               | 8 lanes at up to 10GHz                             | 8 lanes at up to 5 GHz                                  | 8 lanes at up to 5 GHz                                   |  |  |  |  |  |

| PCI Express<br>controllers | 3 × Gen 2.0 controllers<br>1 × Gen 3.0 controllers | 4 × Gen 2.0 controllers                                 | 4 × Gen 2.0 controllers                                  |  |  |  |  |  |

| SATA                       | None                                               | 2 x SATA controllers                                    | 2 x SATA controllers                                     |  |  |  |  |  |

| ТDМ                        | None                                               | Full duplex serial                                      | Full duplex serial                                       |  |  |  |  |  |

| DIU                        | None                                               | 12 bit RGB                                              | 12 bit RGB                                               |  |  |  |  |  |

| CoreNet                    | 700MHz at 256 bits                                 | 600MHz at 128 bits                                      | 600MHz at 128 bits                                       |  |  |  |  |  |

| Ethernet switch            | None                                               | 8 port                                                  | None                                                     |  |  |  |  |  |

| QE                         | None                                               | HDLC, UART, TDM/SI                                      | HDLC, UART, TDM/SI                                       |  |  |  |  |  |

## **Commonalities and Differences (contd...)**

| Features                             | T2081                                         | T1040                                                   | T1042                                         |  |  |  |  |  |

|--------------------------------------|-----------------------------------------------|---------------------------------------------------------|-----------------------------------------------|--|--|--|--|--|

|                                      | I/O                                           |                                                         |                                               |  |  |  |  |  |

| Integrated Flash<br>Controller (IFC) | 8-/16-bit data width,<br>32-bit address width | 8-/16-bit data width,<br>32-bit address width           | 8-/16-bit data width,<br>32-bit address width |  |  |  |  |  |

|                                      | Clocking                                      |                                                         |                                               |  |  |  |  |  |

| Single source clocking None          |                                               | Diff_SYSCLK/DIFF_S<br>YSCLK_B supported VSCLK_B support |                                               |  |  |  |  |  |

|                                      | Power Ma                                      | inagement                                               |                                               |  |  |  |  |  |

| Deep Sleep None                      |                                               | Supported                                               | Supported                                     |  |  |  |  |  |

| Package                              |                                               |                                                         |                                               |  |  |  |  |  |

| 780 FC-PBGA 23 mm x 23 mm            |                                               | 23 mm x 23 mm                                           | 23 mm x 23 mm                                 |  |  |  |  |  |

## Agenda

- T1040 and T2081 Overview

- Hardware Compatibility

- Identical Interfaces

- DDR Controller

- eSDHC Controller

- TEST\_SEL \_B pin

- Sense Pins

- Power Sequencing

- Power Supply

- Clock Difference

# Identical Interfaces

The following interfaces are identical between the T2081 and T1040:

Integrated Flash Controller (IFC)

Enhanced SPI Controller (eSPI)

**DUART Controller**

External Use

## **DDR Controller**

- T2081 supports DD3/3L DDR controller.

- T1040 supports DDR3L/4.

- As DDR3L is common to both devices, it should be used for the common board design.

#### **DDR Calibration Resistor Values**

|       | MDIC [0]   | MDIC[1]    |

|-------|------------|------------|

| T1040 | 162 ohm 1% | 162 ohm 1% |

| T2081 | 187 ohm 1% | 187 ohm 1% |

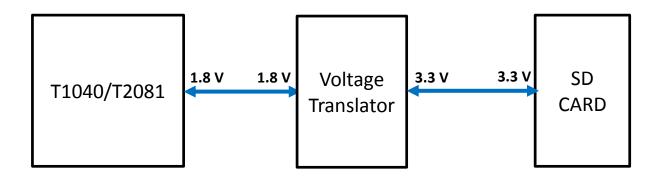

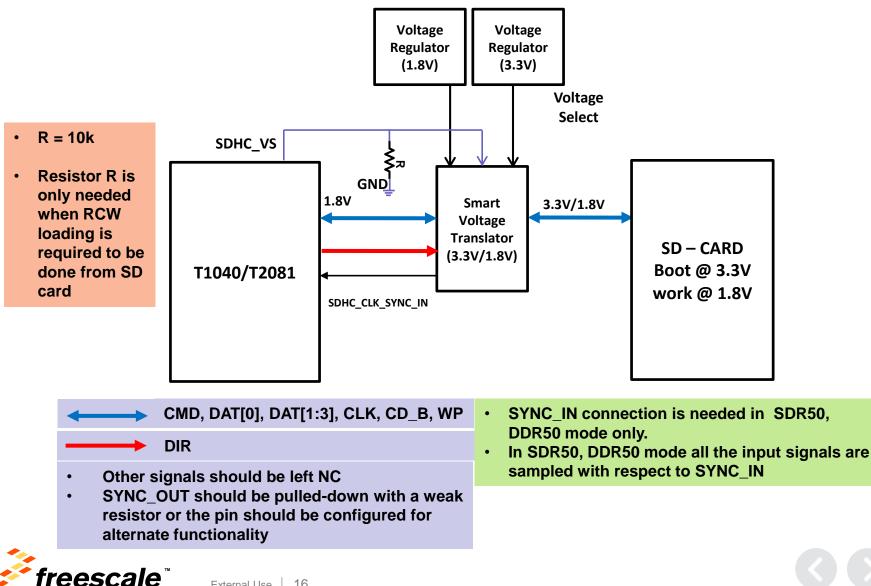

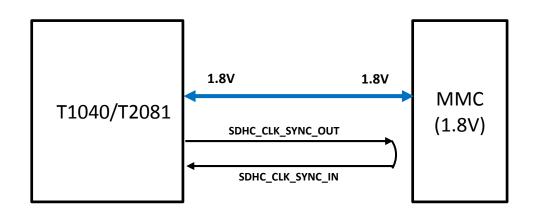

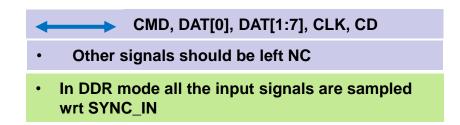

### **eSDHC** Controller

eSDHC Controller Recommendations

External Use

- Both T1 and T2 supports SD 3.0 specification introducing higher capacity up to 2 TB and frequency up to 208 MHz.

- A dynamic switching of I/O voltage from 3.3 V to 1.8V is required.

- T2081 doesn't support the dynamic switch, so the board level shifters are required for common board design.

# SD Card Connections for T1/T2 Compatibility (DS and HS Modes)

**CMD**, DAT[0], DAT[1:3], CLK, CD\_B, WP

Other signals should be left NC

External Use | 15

• SYNC\_OUT should be pulled-down with a weak resistor or the pin should be configured for alternate functionality

## SD Connections for T1/T2 Compatibility (SDR12, 25, 50, 104 and DDR50 Modes)

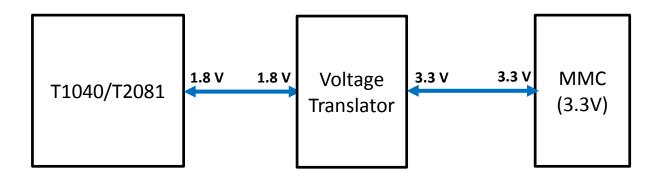

# MMC Card Connections for T1/T2 Compatibility (DS, HS, HS200 Modes)

Other signals should be left NC

External Use | 17

- SYNC\_OUT should be pulled-down with a weak resistor or the pin should be configured for alternate functionality

- Voltage translator is not needed for 1.8V MMC.

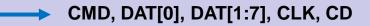

# MMC (3.3V) Connections for T1/T2 Compatibility (DDR Mode)

- SYNC\_OUT should be pulled-down with a weak resistor or the pin should be configured for alternate functionality

- Voltage translator is not needed for 1.8V MMC.

# MMC (1.8V) Connections for T1/T2 Compatibility (DDR Mode)

## **TEST\_SEL\_B** Pin

• The requirement is different for T1040 and T2081.

| Device       | TEST_SEL_B Requirement |

|--------------|------------------------|

| T1040, T1042 | Pull up to O1VDD       |

| T1020, T1022 | Pull down to GND       |

| T2081        | Pull up to OVDD        |

External Use | 20

#### **Sense Pins**

• If the sense pins are used for the regulators, SENSEVDD should be used. SENSEVDDC can be left floating.

| Ball Location | T2081    | T1040     |

|---------------|----------|-----------|

| G19           | SENSEVDD | SENSEVDD  |

| AB9           | RSVD28   | SENSEVDDC |

External Use 21

#### **Power sequencing requirements**

- T1040 requires its power rails to rampup in a specific sequence, whereas T2081 has no such requirement.

- Common board should follow T1040 hardware specification for the Power sequencing requirements.

#### **Case: Power ON**

- Step 1 I/O supplies should ramp up (1.8V, 2.5V, 3.3V).

- PORESET should be asserted when VDDC/VDD rampup

- Step 2 Core supplies (1.0V), USB\_SVDD

- I/O power should ramp before core power

- Step 3 DDR supplies (G1VDD, X1VDD)

- VDD should ramp before G1VDD

## **Power Supply for Core**

- Core Power Island Requirements

- T1040 has VDD and VDDC power domains for core and platform.

- T2081 has only VDD power domain for core and platform.

23

External Use

The common board design should use a single rail for VDD and VDDC in T1040.

| T2081 | T1040     | Recommendation                                          |

|-------|-----------|---------------------------------------------------------|

| VDD   | VDD, VDDC | VDD and VDD should<br>be connected to a<br>common rail. |

#### **Power Supply for I/O**

| Supply            | T2081         | T1040                | Recommendation for a<br>common board design                                                                | Interface wise recommendation                                                                                                                                                                                                         | Interfaces                                                                                                  |

|-------------------|---------------|----------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| O1V <sub>DD</sub> | _             | 1.8V                 | Use Single regulator for OV <sub>DD</sub>                                                                  | eSDHC interface of T2081 is on                                                                                                                                                                                                        | Common: MPIC, GPIO,                                                                                         |

| OV <sub>DD</sub>  | 1.8V          | 1.8V                 | and O1V <sub>DD</sub> on T1040 at 1.8V                                                                     | $OV_{DD}$ supply while IO power<br>supply of eSDHC in T1040 is fed<br>by $EV_{DD}$ . If eSDHC is used, $EV_{DD}$<br>and $OV_{DD}$ should be connected to<br>1.8V. On board level shifters are<br>required to support SD 3.0<br>modes. | System Control, Debug,<br>Clocks, JTAG I/O, IFC,<br>RTC and power<br>management I/O's,<br>T2081 only: eSDHC |

| DV <sub>DD</sub>  | 2.5V<br>1.8V  | 3.3V<br>2.5V<br>1.8V | Use 2.5V or 1.8V only for DV <sub>DD</sub> supply                                                          | DIU and TDM are supported at<br>3.3V so voltage translators may<br>be required on a common board.<br>QE interface is supported at 2.5V<br>and 3.3V, restricting DV <sub>DD</sub> to 2.5V<br>for common board.                         | Common: DUART, I2C,<br>DMA, MPIC<br>T1040 only: QE, TDM,<br>DIU                                             |

| CVDD              | 2.5V<br>1.8V  | 3.3V<br>1.8V         | Use 1.8V for CV <sub>DD</sub> supply                                                                       | _                                                                                                                                                                                                                                     | Common: eSPI,<br>SDHC_DAT[4:7]                                                                              |

| EV <sub>DD</sub>  | _             | 3.3V<br>1.8V         | Use OV <sub>DD</sub> supply for EV <sub>DD</sub>                                                           | SDHC_DAT[0:3], SDHC_CMD<br>and SDHC_CLK are the signals<br>on $EV_{DD}$ supply in T1040. These<br>signals are on $OV_{DD}$ supply in<br>T2081. See $OV_{DD}$ supply for<br>details.                                                   | Common: eSDHC<br>See Note                                                                                   |

| G1V <sub>DD</sub> | 1.5V<br>1.35V | 1.35V<br>1.2V        | Use G1V <sub>DD</sub> at 1.35V                                                                             | Use DDR3L only                                                                                                                                                                                                                        | Common:DDR3L<br>T1040: DDR4<br>T2081: DDR3                                                                  |

| L1V <sub>DD</sub> | _             | 3.3V<br>2.5V<br>1.8V | Use Single regulator for LV <sub>DD</sub><br>and L1V <sub>DD</sub> on T1040<br>It can support 2.5V or 1.8V | Use RGMII interface at 2.5V only.                                                                                                                                                                                                     | Common:GPIO,<br>RGMII@2.5V<br>T1040: MII, RGMII@1.8V                                                        |

| LV <sub>DD</sub>  | 2.5V<br>1.8V  | 3.3V<br>2.5V<br>1.8V |                                                                                                            |                                                                                                                                                                                                                                       |                                                                                                             |

## **Clocking Difference**

T1040 supports the differential pair of SYSCLK, the common board design leaves it as floating or connect through 10K Ohm resistor to GND.

| Clocking scheme               | T2081 | T1040 | Recommendation                                                                                                              |

|-------------------------------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------|

| Single Reference clock mode   | No    | Yes   | T1040: Supported through<br>DIFF_SYSCLK/DIFF_SYSCLK_B clock input pair                                                      |

| Multiple reference clock mode | Yes   | Yes   | Through separate oscillators for SYSCLK,<br>DDRCLK, USBCLK, SDREF_CLKn inputs.<br>Recommended mode for common board design. |

### **Exceptions**

| Product | PCle              | MII<br>on<br>EC1 | QE<br>(TDM<br>HDLC) | Starlite<br>TDM | QSGMII | GE<br>Switch | XFI | SATA | DIU | Deep<br>Sleep |

|---------|-------------------|------------------|---------------------|-----------------|--------|--------------|-----|------|-----|---------------|

| T1040   | 4 Gen 2           | Yes              | Yes                 | Yes             | Yes    | Yes          | No  | Yes  | Yes | Yes           |

| T2081   | 1 Gen3<br>3 Gen 2 | NO               | NO                  | NO              | NO     | NO           | Yes | NO   | NO  | NO            |

## Agenda

- T1040 and T2081 Overview

- Hardware Compatibility

- Software Compatibility

- e6500 and e5500 Compatibility

- RGMII

- SerDes Configuration

- RCW

- Difference in driver

External Use

27

## e6500 and e5500 Compatibility

- User code runs equally well on e6500 or e5500

- Interrupts per thread

- Soft reset per thread (hard reset per core only)

- Debug state per thread

- Changes are hidden by OS

- L2 initialization uses a different register

- Cache locking controlled differently

- Additional enablement for new features not present on e5500:

- 64b, drowsy power manager, Altivec

### e5500/e6500 Caching Structure Differences

|    | e5500                   | e6500                   | Implication                                                                    |

|----|-------------------------|-------------------------|--------------------------------------------------------------------------------|

| L1 | 32KB. Can lock per core | 32kB. Can lock per core | e6500 doesn't lock per thread                                                  |

| L2 | 128KB per core          | 2MB shared              | There will be a somewhat different latency profile, overall improved for e6500 |

| L3 | 256KB                   | 512kB                   | prome, overall improved for e6500                                              |

- Cache changes are transparent to user application

- L1 locking is less granular in e6500

#### RGMII

- The two RGMII interfaces are pin compatible, the configurations for RGMII mode are different between the T2081 and T1040 devices.

- T1040 also supports MII interface on EC1 Interface. When using MII interface, L1VDD and LVDD are restricted to 3.3V and RGMII cannot be supported on EC1 or EC2.

| Configuration   | RGMII assignment |           |                     |  |

|-----------------|------------------|-----------|---------------------|--|

| conngulation    | T2081            | 081 T1040 |                     |  |

| RCW[EC1] = 0b00 | FMan MAC3        | FMan MAC4 | MAC2_GMII_SEL = 0b0 |  |

|                 |                  | FMan MAC2 | MAC2_GMII_SEL = 0b1 |  |

| RCW[EC2] = 0b00 | FMan MAC4        | FMan MAC5 | _                   |  |

| RCW[EC2] = 0b01 | FMan MAC10       | —         |                     |  |

### T1/T2 compatible Serdes Configurations

| T1040<br>SRDS_PRCTL_S1                 | A                                       | В               | с                | D                | E                 | F               | G               | н                                         | T2081<br>SRDS_PRTCL_S1                    |  |

|----------------------------------------|-----------------------------------------|-----------------|------------------|------------------|-------------------|-----------------|-----------------|-------------------------------------------|-------------------------------------------|--|

| 0x00<br>(2 RGMII; FMAN<br>MAC4 & MAC5) |                                         |                 | X1<br>2/5)       |                  | PEX2<br>(5/2.5)   |                 |                 |                                           | 0xAA<br>(2 RGMII; FMAN<br>MAC3 & MAC4/10) |  |

|                                        | PEX3<br>(5/2.5)                         |                 |                  |                  | PEX4<br>(8/5/2.5) |                 |                 |                                           | MACS & MAC4/10/                           |  |

| 0x40<br>(2 RGMII; FMAN                 |                                         | EX1<br>2.5)     | sg.m1<br>(1.25)  | sg.m2<br>(1.25)  | PEX2<br>(5/2.5)   |                 |                 | 0xBC<br>(2 RGMII; FMAN<br>MAC3 & MAC4/10) |                                           |  |

| MAC4 & MAC5)                           |                                         | X3<br>2.5)      | SG1<br>(1.25)    | SG2<br>(1.25)    | PEX4<br>(8/5/2.5) |                 |                 |                                           |                                           |  |

| 0xA5<br>(0 RGMII)                      | PEX1<br>(5/2.5)                         | sg.m3<br>(1.25) | sg.m1<br>(3.125) | sg.m2<br>(3.125) |                   | X2<br>2.5)      | sg.m4<br>(1.25) | sg.m5<br>(1.25)                           | 0xC8                                      |  |

|                                        | PEX3 SG10 SG1<br>(5/2.5) (1.25) (3.125) |                 | SG1<br>(3.125)   | SG2<br>(3.125)   | PE<br>(5/2        |                 | SG5<br>1.25)    | SG6<br>(1.25)                             | (2 RGMII; FMAN<br>MAC3 & MAC4)            |  |

| 0xAA<br>(0 RGMII)                      | PEX1<br>(5/2.5)                         | sg.m3<br>(1.25) | sg.m1<br>(3.125) | sg.m2<br>(3.125) | PEX2<br>(5/2.5)   | PEX3<br>(5/2.5) | sg.m4<br>(1.25) | sg.m5<br>(1.25)                           | 0xFA<br>(2 RGMII; FMAN                    |  |

|                                        | PEX3<br>(5/2.5)                         | SG10<br>(1.25)  | SG1<br>(3.125)   | SG2<br>(3.125)   | PEX4<br>(5/2.5)   | PEX1<br>(5/2.5) | SG5<br>(1.25)   | SG6<br>(1.25)                             | MAC3 & MAC4)                              |  |

| 0x85<br>(0 RGMII)                      | PEX1<br>(5/2.5)                         | sg.m3<br>(1.25) | sg.m1<br>(1.25)  | sg.m2<br>(1.25)  |                   | X2<br>2.5)      | sg.m4<br>(1.25) | sg.m5<br>(1.25)                           | 0xD6<br>(2 RGMII; FMAN                    |  |

|                                        | PEX3<br>(5/2.5)                         | SG10<br>(1.25)  | SG1<br>(1.25)    | SG2<br>(1.25)    | PE<br>(8/5/       |                 | SG5<br>(1.25)   | SG6<br>(1.25)                             | MAC3 & MAC4)                              |  |

## T1/T2 compatible SerDes Configurations (continue)

| T1040<br>SRDS_PRCTL_S1                                       | Α               | В               | с                | D                 | E                 | F               | G               | н                                 | T2081<br>SRDS_PRTCL_S1                 |

|--------------------------------------------------------------|-----------------|-----------------|------------------|-------------------|-------------------|-----------------|-----------------|-----------------------------------|----------------------------------------|

| 0x87<br>(1 RGMII; FMAN<br>MAC4)                              | PEX1<br>(5/2.5) | sg.m3<br>(1.25) | sg.m1<br>(1.25)  | sg.m2<br>(1.25)   | PEX2<br>(5/2.5)   | PEX3<br>(5/2.5) | PEX4<br>(5/2.5) | sg.m5<br>(1.25)                   | 0xF2<br>(2 RGMII; FMAN<br>MAC3 & MAC4) |

|                                                              | PEX3<br>(5/2.5) | SG10<br>(1.25)  | SG1<br>(1.25)    | SG2<br>(1.25)     | PEX4<br>(8/5/2.5) | PEX1<br>(5/2.5) | PEX2<br>(5/2.5) | SG6<br>(1.25)                     |                                        |

| 0xA7<br>(1 RGMII; FMAN<br>MAC4)                              | PEX1<br>(5/2.5) | sg.m3<br>(1.25) | sg.m1<br>(3.125) | sg.m2<br>(3.125)  | PEX2<br>(5/2.5)   | PEX3<br>(5/2.5) | PEX4<br>(5/2.5) | sg.m5<br>(1.25)                   | 0xF8<br>(2 RGMII; FMAN<br>MAC3 & MAC4) |

|                                                              | PEX3<br>(5/2.5) | SG10<br>(1.25)  | SG1<br>(3.125)   | SG2<br>(3.125)    | PEX4<br>(5/2.5)   | PEX1<br>(5/2.5) | PEX2<br>(5/2.5) | SG6<br>(1.25)                     |                                        |

| 0x8D*<br>(Using L2 switch)<br>(2 RGMII; FMAN<br>MAC4 & MAC5) | PEX1<br>(5/2.5) | sg.s3<br>(1.25) | sg.s1<br>(1.25)  | sg.s2<br>(1.25)   | PEX2<br>(5/2.5)   | sg.s6<br>(1.25) | sg.s4<br>(1.25) | sg.s5<br>(1.25)                   | 0xCA<br>(1 RGMII; FMAN<br>MAC3)        |

|                                                              | PEX3<br>(5/2.5) | SG10<br>(1.25)  | SG1<br>(3.125)   | SG2<br>(3.125)    | PEX4<br>(5/2.5)   | SG4<br>(1.25)   | SG5<br>1.25)    | SG6<br>(1.25)                     |                                        |

| 0x06*<br>(2 RGMII; FMAN<br>MAC4 & MAC5)                      | PEX1<br>(5/2.5) |                 |                  |                   | PEX2<br>(5/2.5)   | PEX3<br>(5/2.5) | PEX4<br>(5/2.5) | SATA1                             | 0x DE                                  |

|                                                              | PEX3<br>(5/2.5) |                 |                  |                   | PEX4<br>(8/5/2.5) | PEX1<br>(5/2.5) | PEX2<br>(5/2.5) | SG6<br>(1.25)                     | (2 RGMII; FMAN<br>MAC3 & MAC4/10)      |

| 0x08*<br>(2 RGMII; FMAN<br>MAC4 & MAC5)                      | PEX1<br>(5/2.5) |                 |                  |                   | PEX2<br>(5/2.5)   | PEX3<br>(5/2.5) | SATA2           | SATA1                             | 0xE0                                   |

|                                                              | PEX3<br>(5/2.5) |                 |                  | PEX4<br>(8/5/2.5) | PEX1<br>(5/2.5)   | SG5<br>(1.25)   | SG6<br>(1.25)   | (2 RGMII; FMAN<br>MAC3 & MAC4/10) |                                        |

## **Reset Configuration Word**

- RCW are mostly compatible. Detail listed in T1040 and T2080 reference manual.

| RCW bits | T1                   | T2       | Notes                                                                                        |  |  |

|----------|----------------------|----------|----------------------------------------------------------------------------------------------|--|--|

| 10-15    | MEM_PLL_CFG          |          | Cutoff frequencies for the T1 and T2 differ.<br>24:1 async mode setting is available for T1. |  |  |

| 176-177  | SRDS_DIV_PEX         |          | T1: 00 Train up to 5G<br>T2: 00 Train up to 8G                                               |  |  |

| 190-191  | DDR_FDBK_<br>MUL     | Reserved |                                                                                              |  |  |

| 242      | SYS_PLL_SPD          | Reserved |                                                                                              |  |  |

| 321      | UC1_CTSB_<br>CDB_SEL | Reserved |                                                                                              |  |  |

| 418-419  | EC1                  |          | Using different MAC.<br>T1: MAC #4 and #2<br>T2: MAC #3                                      |  |  |

| 420-421  | EC2                  |          | Using different MAC.<br>T1: MAC #5<br>T2: MAC #4, #10                                        |  |  |

### **Difference in driver**

To limit driver configuration issues, take the following actions to simplifying the driver configuration.

- Number of cores

- T1040: 4 single-threaded e5500 cores running at 1000MHz/1200MHz/1400MHz

- T2080: 4 dual-threaded e6500 cores(8 virtual cores) running at 1200MHz/1533MHz/1800MHz

Using 1200MHz for both core

- CPC size

- T1040: 256-Kbyte, 8-way set associative, 64-byte coherency granule

- T2080: 512-Kbyte, 16-way set associative, 64-byte coherency granule Use 256-Kbyte, 8-way set associative, 64-byte coherency granule

- L2 size

- T1040: 256KB per e5500 core, total 1MB.

- T2080: 2MB shared by 4 e6500 cores

Use 256KB per thread

## **Difference in driver (continue...)**

- DDR

- T1040: one 32-/64-bit DDR3L/DDR4 SDRAM memory controller with ECC and interleaving support

- T2080: one 32-/64-bit DDR3/3L SDRAM memory controller with ECC and interleaving support and Memory pre-fetch engine

Select cfg\_dram\_type = 1 to choose DDR3L.

- Ethernet

- T1040: 4 MACs from FMan and 8 MAC from Ethernet Switch. It supports two RGMII ports using MAC4 & MAC5.

- T2080: 8 MACs from FMan(four 1G and four 1/2.5/10G) running with various combinations with different SerDes procotols. Two RGMII ports using MAC3 & MAC4, 4 XFI ports using MAC9,MAC10,MAC1,MAC2.

Using RGMII requires the software driver to remap the different MACs between T1 and T2,

choose a pin compatible configuration for SerDes option.

- · PCle

- T1040: four PCI Express 2.0 controllers/ports running at up to 2.5/5GHz.

- T2080: two PCI Express 2.0 running at 2.5/5GHz and two PCI Express 3.0 controllers/ports running at 2.5/5/8GHz.

Using 2.5/5GHz only.

## **Difference in driver (continue...)**

- SATA

- T1040 and T2080 have same two SATA controllers supporting 1.5 and 3.0 Gbps operation, there is no defference in software configuration.

- QE

- T1040: support QE with two TDM interfaces. u-boot doesn't support TDM.

- T2080: no support.

- DIU

- T1040: support LCD and HDMI interface (DIU) with 12 bit dual data rate.

- T2080: no support.

## **Difference in driver (continue...)**

- PAMU

- no changes in S/W.

- DMA

- 3 in T2081 vs 2 in T1040.

- GE switch

- if used on board add if config, only for T1040.

- IFC

- same so no changes.

- Single Source Clocking: USB considerations, only for T1040.

- Deep sleep: only for T1040.

## Agenda

- T1040 and T2081 Overview

- Hardware Compatibility

- Software Compatibility

- Pinout Comparision

- Supporting Tools

- Reference Documentation

38

External Use

This table details the differences in pinout between the T2081 and T1040 processor family and how to resolve this difference. Unless explicitly stated otherwise, the pins on the T2081 can be connected as if a T1040 is populated.

| Pin                                                                       | T2081     | T1040         | Compatible connection                                                                                                                                   |  |  |  |  |

|---------------------------------------------------------------------------|-----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Ethernet MI 2 pins                                                        |           |               |                                                                                                                                                         |  |  |  |  |

| L6                                                                        | EMI2_MDC  | RSVD10        | All the Ethernet PHY's to be used with<br>T1040 should be managed through the<br>EMI1 interface.                                                        |  |  |  |  |

| M6                                                                        | EMI2_MDIO | RSVD11        |                                                                                                                                                         |  |  |  |  |

| Ethernet Cont. 1 pins                                                     |           |               |                                                                                                                                                         |  |  |  |  |

| AC4                                                                       | RSVD34    | EC1_TX_ER     | EC1 Interface on T1040 also supports<br>MII interface (see Section 3.8,<br>"Ethernet MACs options")This output<br>pin can be left floating if not used. |  |  |  |  |

| AC2                                                                       | RSVD33    | EC1_RX_ER     | Tie low through a 2-10 kohm resistor if not used.                                                                                                       |  |  |  |  |

| AC1                                                                       | RSVD32    | EC1_COL       |                                                                                                                                                         |  |  |  |  |

| Differential SYSCLK pins (see Section 4, "Internal clocking differences") |           |               |                                                                                                                                                         |  |  |  |  |

| G14                                                                       | RSVD07    | DIFF_SYSCLK   | Differential SYSCLK input is available<br>only in T1040. These can be left floating<br>or connected to GND if unused.                                   |  |  |  |  |

| F14                                                                       | RSVD05    | DIFF_SYSCLK_B |                                                                                                                                                         |  |  |  |  |

|                                                                           |           |               |                                                                                                                                                         |  |  |  |  |

|                |                                   | DMA/TDM pins                                              | •                                                                                                                                     |  |  |  |

|----------------|-----------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                |                                   |                                                           |                                                                                                                                       |  |  |  |

| U5             | DMA1_DACK0_B/GIPIO4_05            | DMA1_DACK0_B/GIPIO4_05/ <b>TDM_TFS</b>                    | Additional TDM functionality is available<br>in T1040 over DMA pins. When used,<br>software needs to manage the interface<br>on T2081 |  |  |  |

| R5             | DMA1_DDONE0_B/GPIO4_06            | DMA1_DDONE0_B/GPIO4_06/TDM_TCK                            |                                                                                                                                       |  |  |  |

| P5             | DMA1_DREQ0_B/GPIO4_04             | DMA1_DREQ0_B/GPIO4_04/TDM_TXD                             |                                                                                                                                       |  |  |  |

| AA5            | DMA2_DACK0_B/GIPIO4_08/E<br>VT7_B | DMA2_DACK0_B/GIPIO4_08/EVT7_B/ <b>TDM</b><br>_ <b>RFS</b> |                                                                                                                                       |  |  |  |

| Y5             | DMA2_DDONE0_B/GPIO4_09/<br>EVT8_B | DMA2_DDONE0_B/GPIO4_09/EVT8_B/ <b>TD</b><br>M_RCK         |                                                                                                                                       |  |  |  |

| V5             | DMA2_DREQ0_B/GPIO4_07             | DMA2_DREQ0_B/GPIO4_07/TDM_RXD                             | *                                                                                                                                     |  |  |  |

| I2C 3 & 4 pins |                                   |                                                           |                                                                                                                                       |  |  |  |

| V2             | IIC3_SCL/GPIO4_00                 | IIC3_SCL/GPIO4_00/QE_SI1_STROBE0                          | Additional QE functionality is available in<br>T1040 over I2C pins.                                                                   |  |  |  |

| WЗ             | IIC3_SDA/GPIO4_01                 | IIC3_SDA/GPIO4_01/QE_SI1_STROBE1                          |                                                                                                                                       |  |  |  |

| ААЗ            | IIC4_SCL/GPIO4_02/EVT5_B          | IIC4_SCL/GPIO4_02/EVT5_B/DIU_HSYNC                        | Additional DIU functionality is available<br>in T1040 over I2C pins.                                                                  |  |  |  |

| AB3            | IIC4_SDA/GPIO4_03/EVT6_B          | IIC4_SDA/GPIO4_03/EVT6_B/DIU_VSYNC                        |                                                                                                                                       |  |  |  |

| QE/DIU pins |        |                                              |                                                                 |  |  |  |  |

|-------------|--------|----------------------------------------------|-----------------------------------------------------------------|--|--|--|--|

| Pin         | T2081  | T1040                                        | Compatible connection                                           |  |  |  |  |

| P4          | RSVD15 | CLK09/GPIO4_15/BRG02/DIU_D10                 | QE and DIU are only available on                                |  |  |  |  |

| P3          | RSVD14 | CLK10/GPIO4_22/BRG03/DIU_D11                 | T1040. If unused, configure the pins as<br>GPIO and leave as NC |  |  |  |  |

| N4          | RSVD13 | CLK11/GPIO4_16/BRG04/DIU_DE                  | -                                                               |  |  |  |  |

| M4          | RSVD12 | CLK12/GPIO4_23/BRG01/DIU_CLK_OUT             |                                                                 |  |  |  |  |

| R2          | RSVD17 | TDMA_RQ/GPIO4_14/DIU_D4/UC1_CDB_<br>RXER     |                                                                 |  |  |  |  |

| U1          | RSVD23 | TDMA_RSYNC/GPIO4_11/DIU_D1/UC1_CT<br>SB_RXDV | -                                                               |  |  |  |  |

| U2          | RSVD24 | TDMA_RXD/GPIO4_10/DIU_D0/UC1_RXD7            |                                                                 |  |  |  |  |

| R1          | RSVD16 | TDMA_TSYNC/GPIO4_13/UC1_RTSB_TXE<br>N/DIU_D3 |                                                                 |  |  |  |  |

| T1          | RSVD20 | TDMA_TXD/GPIO4_12/UC1_TXD7/DIU_D2            | 1                                                               |  |  |  |  |

| R4          | RSVD19 | TDMB_RQ/GPIO4_21/DIU_D9/UC3_CDB_<br>RXER     |                                                                 |  |  |  |  |

| ТЗ          | RSVD21 | TDMB_RSYNC/GPIO4_18/DIU_D6/UC3_CT<br>SB_RXDV | -                                                               |  |  |  |  |

| U4          | RSVD25 | TDMB_RXD/GPIO4_17/DIU_D5/UC3_RXD7            | 1                                                               |  |  |  |  |

| R3          | RSVD18 | TDMB_TSYNC/GPIO4_20/UC3_RTSB_TXE<br>N/DIU_D8 | †                                                               |  |  |  |  |

| T4          | RSVD22 | TDMB_TXD/GPIO4_19/UC3_TXD7/DIU_D7            | Ť                                                               |  |  |  |  |

| LP_Trust pin    |                     |                |                                                                                                                                            |  |  |  |

|-----------------|---------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| R6              | LP_TMP_DETECT_B     | RSVD15         | LP_Trust is only supported by T2081<br>Connect LP_TMP_DETECT_B to<br>OVDD through a 10K resistor<br>Pull up through a 10K resistor to 1.0V |  |  |  |

| P6              | V <sub>DD</sub> _LP | RSVD13         |                                                                                                                                            |  |  |  |

| SENSE pins      |                     |                |                                                                                                                                            |  |  |  |

| AB9             | RSVD28              | SENSEVDDC      | Use SENSEV <sub>DD</sub> and SENSEGND                                                                                                      |  |  |  |

| AB10            | RSVD29              | SENSEGNDC      |                                                                                                                                            |  |  |  |

| por_config pins |                     |                |                                                                                                                                            |  |  |  |

| D13             | IFC_WE0_B           | cfg_eng_use[0] | Used in T1040 for selection of single<br>source clocking option. Do not use for<br>common board.                                           |  |  |  |

## Agenda

- T1040 and T2081 Overview

- Hardware Compatibility

- Software Compatibility

- Pinout Comparision

- Supporting Tools

## T1040/T2081 Software & Tools at a Glance

- Two Reference Design Boards

- T1040RDB

- T1042RDB

- Software Support

- Yocto based SDK

- SDK support includes

- Legacy features (refer SDK 1.4 release notes)

- New features

- FMAN and QE microcode

- Linux based QE drivers for TDM, UART and HDLC

- QorIQ Configuration Suite

- CodeWarrior based debugger, flash programmer

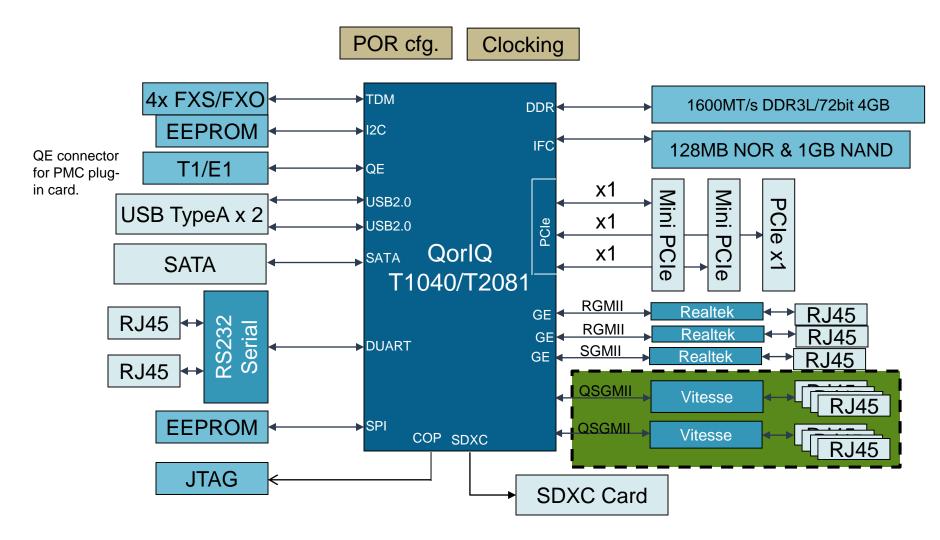

### T1040/T2081 RDB System

## T1040/T2081 RDB Block Diagram

46

## Agenda

- T1040 and T2081 Overview

- Hardware Compatibility

- Software Compatibility

- Pinout Comparision

- Supporting Tools

External Use

47

Reference Documentation

# **Reference Documentation**

**T1040 Hardware Specification and Reference Manual**

**T2081 Hardware Specification and Reference Manual**

Application Note (AN4733) T1040 to T2081 Migration Guide

T1040/T2081 Design Checklist

T1040 RDB User Manual

T1040 RDB Schematic

## **Session Closing**

• By now, you should be able to:

External Use

- Use Freescale's design collateral to aid your own T1040 and T2081 designs

- Understand the commonalities and differences between these devices

- Understand the unique challenges facing T1040 and T2081 common design and the solutions to overcome them

## Introducing The QorlQ LS2 Family

Breakthrough, software-defined approach to advance the world's new virtualized networks New, high-performance architecture built with ease-of-use in mind Groundbreaking, flexible architecture that abstracts hardware complexity and enables customers to focus their resources on innovation at the application level

### **Optimized for software-defined networking applications**

Balanced integration of CPU performance with network I/O and C-programmable datapath acceleration that is right-sized (power/performance/cost) to deliver advanced SoC technology for the SDN era

### Extending the industry's broadest portfolio of 64-bit multicore SoCs

Built on the ARM® Cortex®-A57 architecture with integrated L2 switch enabling interconnect and peripherals to provide a complete system-on-chip solution

External Use

50

## **QorlQ LS2 Family**

**Key Features**

.....

200302 \*\*\*\*

Wireless Access

SDN/NFV

Switching

Data

Center

Unprecedented performance and ease of use for smarter, more capable networks

# High performance cores with leading interconnect and memory bandwidth

- 8x ARM Cortex-A57 cores, 2.0GHz, 4MB L2 cache, w Neon SIMD

- 1MB L3 platform cache w/ECC

- 2x 64b DDR4 up to 2.4GT/s

# A high performance datapath designed with software developers in mind

- New datapath hardware and abstracted acceleration that is called via standard Linux objects

- 40 Gbps Packet processing performance with 20Gbps acceleration (crypto, Pattern Match/RegEx, Data Compression)

- Management complex provides all init/setup/teardown tasks

### Leading network I/O integration

- 8x1/10GbE + 8x1G, MACSec on up to 4x 1/10GbE

- Integrated L2 switching capability for cost savings

- 4 PCIe Gen3 controllers, 1 with SR-IOV support

- 2 x SATA 3.0, 2 x USB 3.0 with PHY

## **Use a Common Board**

- With the introduction of the T1040 and T2081, customers can now create common boards for both devices

- T1040 and T2081 are pin compatible

- One common board design would reduce design time and save cost

- Make migration much faster and easier

www.Freescale.com

© 2015 Freescale Semiconductor, Inc. | External Use