## PWM X signal of eFlexPWM module

The eFlexPWM module is integrated in DSC family, Kinetis KV family and MPC56xx family, it is an important module in motor control application, switch mode power supply or the other energy control application.

The eFlexPWM module has 4 sub-modules: SM0, SM1, SM2, SM3, each sub-module can output 3 PWM signal: PWM\_nA, PWM\_nB and PWM\_nX, the n is sub module index. The PWM\_nA, PWM\_nB can be independent or complementary, the PWM\_nX is an extended PWM channel. For example, this is the eFlexPWMA module PWM signal output pins of MC56F84789:

GPIOE1 PWMA\_OA

GPIOE0 PWMA\_OB

GPIOG8 PWMB\_OX PWMA\_OX

GPIOE3 PWMA\_1A

GPIOE2 PWMA\_1B

GPIOG9 PWMB\_1X PWMA\_1X

GPIOE5 PWMA 2A

GPIOE4 PWMA\_2B

GPIOG10 PWMB\_2X PWMA\_2X

GPIOE7 PWMA 3A

GPIOE6 PWMA\_3B

GPIOF6 PWMA\_3X PWMB\_3X

It is a question what is function of PWM\_nX, how to generate and control the timing of PWM\_nX, what is the restriction of PWM\_nX signal.

The documentation talks about the PWM\_nX signal, give the register setting to set up the duty cycle and tricks to control the waveform of PWM\_nX.

For the PWM\_nA and PWM\_nB, it is clear that PWM\_SMn\_VAL2 controls the rising edge of PWM\_nA, PWM\_SMn\_VAL3 controls the falling edge of PWM\_nA; that PWM\_SMn\_VAL4 controls the rising edge of PWM\_nB, PWM\_SMn\_VAL5 controls the falling edge of PWM\_nB. But for the PWM\_nX, it is confused

in RM, in fact the that PWM\_SMn\_VALO controls the rising edge of PWM\_nX, PWM\_SMn\_VAL1 controls the falling edge of PWM\_nX.

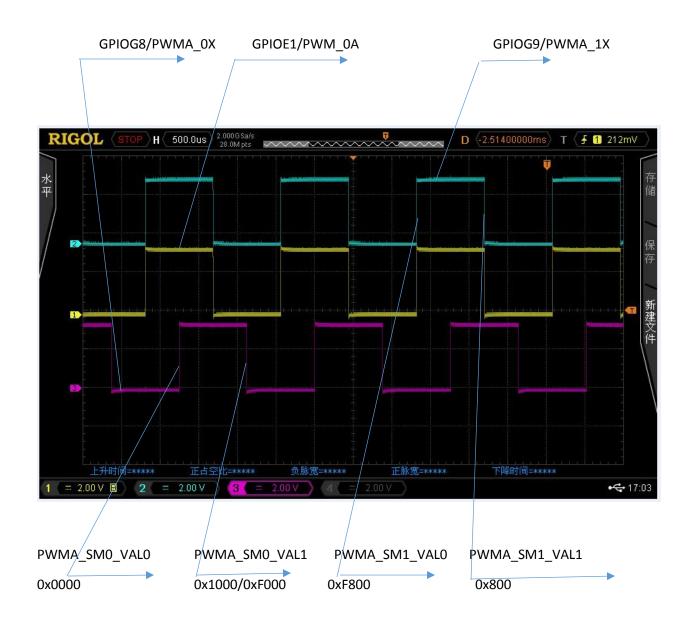

In general, all the PWM signals are synchronized, but of course, it is application by application. If all the PWM signals are required to be synchronized(of course, this is the generic case), we use the master sync signal from SM0 to synchronize all the other sub-module, in detail, the PWM\_SM0\_VAL1 generates the master sync signal to synchronize the SM0/SM1/SM2/SM3, in the case, PWM\_SM1\_VAL1/PWM\_SM3\_VAL1 are not used, they can be used to control the falling edge of the PWM\_1X, PWM\_2X, PWM\_3X. The rising edge of PWM\_1X, PWM\_2X, PWM\_3X are controlled by the PWM\_SM1\_VAL0/PWM\_SM2\_VAL0/PWM\_SM3\_VAL0.

For the PWM\_OX, because the PWM\_SMO\_VAL1 register is used to control the period of all PWM signal (the period is PWM\_SMO\_VAL1- PWM\_SMO\_INIT), so the PWM\_OX signal falling edge can NOT be controlled, in other words, the PWM\_OX waveform is restricted.

In conclusion, the eFlexPWM module can generate 2\*4+3=11 PWM signal with controllable edges, and one half-controllable PWM signal.

PWMA\_SM0VAL0=0x0000;

PWMA\_SM0VAL1=0x1000; generate signal PWMA\_0X yellow signal

PWMA\_SM1VAL0=0xF800;

PWMA\_SM1VAL1=0x800; generate signal PWMA\_1X blue signal

```

PWMA_SM0VAL2=0xF800;

PWMA SM0VAL3=0x800;

generate signal PWMA_0A pink signal

int main(void)

DisableWatchdog;

CLOCK init();

GPIOEG init();

PWMA_init();

//PWM ISR SETTING();

//PWMX Function();

PWMA_MCTRL = 0x0100; //enable the PWM module

PWMA_MCTRL|=0x0200; //enable the PWM module

PWMA_MCTRL = 0x0400; //enable the PWM module

PWMA MCTRL =0x0800; //enable the PWM module

//asm(bfclr #300,sr); //enable interrupt

for(;;)

{}

return(0);

}

void PWMA_init(void)

{

//SM0 initialization

PWMA SM0INIT=0xF000;

PWMA SMOVAL0=0x0000;

//the modulo is 256

PWMA SM0VAL1=0x1000;

PWMA_SM0VAL2=0xF800; //75% duty cycle

PWMA SMOVAL3=0x800;

PWMA_SMOVAL4=0xF800; //25% duty cycle

PWMA SMOVAL5=0x800;

PWMA SMOCTRL2=0x0000; //complementary mode for PWM0A and PWM0B, IP bus clock

PWMA SMOCTRL=0x3400; //4 PWM opportunity, PWM clock=Fclk

PWMA SM00CTRL=0x0000; //PWM does not inverter, PWM forced to logic 0 in fault

state

PWMA_SMOTCTRL=0x0002; //generate PWMA0_TRIG1 signal, it will be routed to

trigger PWMB0_EXT_SYNC, PWMB1_EXT_SYNC, PWMB2_EXT_SYNC

PWMA SMOINTEN=0x0000; //disable all interrupt

PWMA SMODISMAPO=0x0000; //Disable fault mask

PWMA SMODISMAP1=0x0000; //Disable fault mask

PWMA_SMODTCNT0=0x0000; //dead time is set to 0

PWMA SMODTCNT1=0x0000;

PWMA SMOCTRL =0 \times 04;

//SM1 module <u>initialization</u>

PWMA SM1INIT=0xF000;

PWMA SM1VAL0=0xF800; //set the PWMA 1X duty cycle

PWMA SM1VAL1=0x800; //the modulo is 256

PWMA SM1VAL2=0xF800; //75% duty cycle

```

```

PWMA SM1VAL3=0x800;

PWMA SM1VAL4=0xF800: //25% duty cycle

PWMA SM1VAL5=0x800;

PWMA SM1CTRL2=0x200; //complementary mode, IP bus clock, the INIT SEL should

be 10, which means

//that the SM0 synchronize thw SM1, PWMX INIT is set as a test

PWMA_SM1CTRL=0x3400; //4 PWM opportunity, PWM clock=Fclk

PWMA_SM10CTRL=0x0000; //PWM does not inverter, PWM forced to logic 0

PWMA SM1TCTRL=0x0000;

PWMA SM1INTEN=0x0000;

PWMA_SM1DISMAP0=0x0000; //Disable fault mask

PWMA_SM1DISMAP1=0x0000; //Disable fault mask

PWMA SM1DTCNT0=0x0000; //dead time is set to 0

PWMA SM1DTCNT1=0x0000;

PWMA_SM1CAPTCTRLX = 0x40; //PWMA1_X output

PWMA OUTEN = 0x0FF0; //enable PWM output

PWMA FCTRL)=0xF000; //fault logic setting

//

PWMA SM1CTRL =0x04;

//test PWM2 X output signal

//when the SM2 module of PWMA is synchronized by SM0 sync signal, the

PWM1_X/PWM2_X/PWM3_X can output arbitary

//waveform without any restriction because of PWMA SMxVAL1 register,

only PWMA_SMOVAL1 register is used to control the

//PWMA frequency

PWMA SM2INIT=0xF000;

PWMA SM2VAL0=0x0000;

PWMA SM2VAL1=0x1000;

//the modulo is 256

PWMA SM2VAL2=0xF800; //75% duty cycle

PWMA_SM2VAL3=0x800;

PWMA SM2VAL4=0xF800; //25% duty cycle

PWMA SM2VAL5=0x800;

PWMA SM2CTRL2=0x200; //complementary mode, IP bus clock, the INIT SEL

should be 10, which means

//that the SM0 synchronize the SM2 module

PWMA SM2CTRL=0x3400; //4 PWM opportunity, PWM clock=Fclk

PWMA SM2OCTRL=0x0000; //PWM does not inverter, PWM forced to logic 0

PWMA_SM2TCTRL=0x0000;

PWMA SM2INTEN=0x0000;

PWMA SM2DISMAP0=0x0000; //Disable fault mask

PWMA SM2DISMAP1=0x0000; //Disable fault mask

PWMA SM2DTCNT0=0x0000; //dead time is set to 0

PWMA SM2DTCNT1=0x0000;

PWMA SM2CTRL =0 \times 04;

//PWMA global register setting

PWMA_OUTEN = 0x0FF0; //enable PWM output

PWMA_MASK=0x0000; //disable PWM mask

PWMA_SWCOUT=0x0000; //determine dead time logic

PWMA_FCTRL)=0xF000; //fault logic setting

PWMA MCTRL = 0x0007; //must use the instruction, otherwise, the counter

will disorder, IPOL is cleared, PWM23 manipulate the duty cycle

PWMA OUTEN = 0x03; // enable PWMA 1X signal

return;

}

```

## Conclusiuon:

each eFlexPWM has 4 sub-modules:SM0, SM1,SM2, SM3, each sub-module can output three PWM signals:PWM\_nA, PWM\_nB, PWM\_nX. In the condition that all the PWM signal are synchronized, user can get 11 PWM signal with rising/falling edge controllable completely for PWM\_0A, PWM\_0B; PWM\_1A, PWM\_1B, PWM\_1X; PWM\_2A, PWM\_2B, PWM\_2X; PWM\_3A, PWM\_3B, PWM\_3X; But the PWM\_0X falling edge can not be controlled, in other words, it is half-controllable.