# ENABLING TECHNOLOGIES: DDR FUNDAMENTALS

JACQUES LANDRY FIELD APPLICATIONS ENGINEERING AUTOMOTIVE

AMF-AUT-T2785 | AUGUST 2017

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. © 2017 NXP B.V. PUBLIC

# AGENDA

- Industry Trends

- Basic DDR SDRAM Structure

- SDRAM Differences

- General Hardware and Software Design Guidelines and Tips

- i.MX DRAM Register Programming Aid

- Layerscape DRAM Configuration and Validation via QCVS Tools

# **Session Introduction**

- Understanding the DDR and memory controller fundamentals is key to a successful selection and design of a DDR interface

- In this session you will learn about:

- Industry trends and fundamentals

- DRAM Comparisons

- Factors to consider when deciding, designing and delivering DDR on your board

- Available DDR tools

- Who would benefit by attending this session?

- Hardware, software and system design engineers planning to implement a DDR interface in their design

- Session length is 2 hours

# **Two common types of DRAM Memory**

- **DDR DRAM** (focus on DDR4)

- Typically used in PCs, Servers and Embedded Applications

- Available in Discrete components and Modules

- Largest total capacity

- -ECC, CRC and parity protection for high reliability systems

- LPDDR DRAM (focus on LPDDR4)

- Used in Mobile and Automotive Applications (often battery powered)

- Discrete components (small packages)

- -Low Power

- Multi-Channel Architecture

- Highest Speed

- Configuration Flexibility

# Industry Trends

# **Industry Trend**

- DDR4 DRAM pricing is lower or same as DDR3\3L. The pricing crossover occurred around Q4 of 2015. Similarly, LPDDR4 is expected to crossover LPDDR3 in 2018.

- Production DDR4 DRAM, DIMMs and LPDDR4 are available from most DRAM vendors.

- The first NXP device with DDR4 support, T104x product, taped out in Q42013.The LS1043A also supports DDR4. <u>Nearly 4 years</u> of product experience with DDR4.

- Many current and all future QorIQ products including T1, LS1, and LS2 products will support DDR4.

- The first NXP device with LPDDR4 support is the i.MX8 Family.

# DDR3, DDR4 and LPDDR – Major Vendors

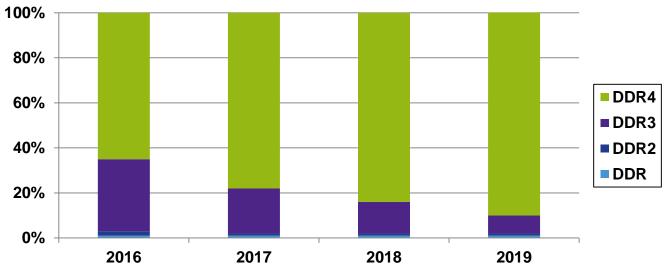

# **DRAM Migration Roadmap**

|      | 2016 | 2017 | 2018 | 2019 |

|------|------|------|------|------|

| DDR  | 1%   | 1%   | 1%   | 1%   |

| DDR2 | 2%   | 1%   | 1%   | 1%   |

| DDR3 | 32%  | 20%  | 14%  | 8%   |

| DDR4 | 65%  | 78%  | 84%  | 91%  |

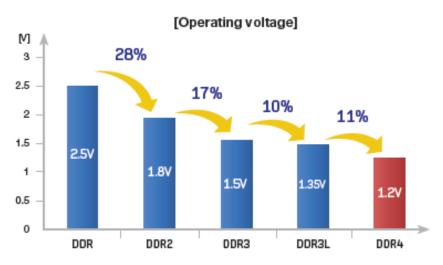

# DDR3/DDR3L/DDR4 Power Saving

- DDR3 DRAM provides 20% power savings over DDR2

- DDR3L DRAM provides 10% power savings over DDR3

- DDR4 DRAM provides 37% power savings over DDR3L

Figure 4. Reduced operating voltage requirements of DDR4 compared to DDR3L

[Normalized power consumption]

Figure 5. Reduced normalized power consumption requirements of DDR4 compared to DDR3L

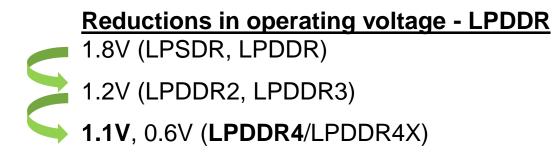

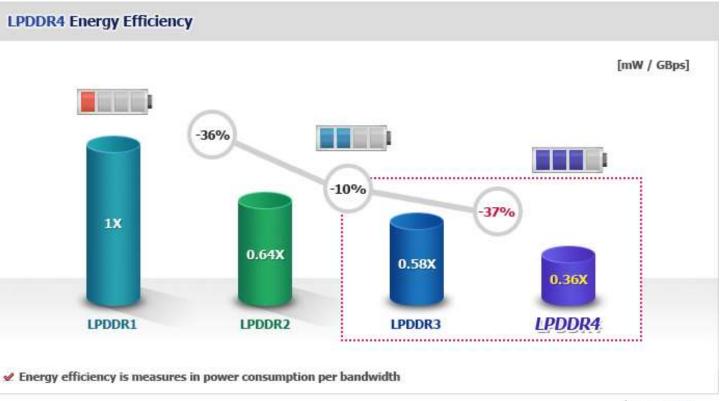

# LPDDR2/LPDDR3/LPDDR4 Power Saving

- LPDDR2 DRAM provides 36% power savings over LPDDR1

- LPDDR3 DRAM provides 10%

power savings over LPDDR2

- PLDDR4 DRAM provides 37%

power savings over LPDDR3

# **DDR SDRAM Highlights and Comparison**

| Feature/Category                                 | DDR3                                            | DDR4                                          | LPDDR4                                                |

|--------------------------------------------------|-------------------------------------------------|-----------------------------------------------|-------------------------------------------------------|

| Package                                          | BGA only                                        | BGA only                                      | BGA. PoP, Bare Die                                    |

| Densities                                        | 512Mb -8Gb                                      | 2Gb -16Gb                                     | 2Gb to 16Gb per channel                               |

| Data Bus Organization                            | x4, x8, x16                                     | x4, x8, x16                                   | x32, (2 channels, x16),<br>x64 (4 channels, x16)      |

| Voltage                                          | DDR3L:1.35V Core & I/O<br>DDR3: 1.5V Core & I/O | 1.2V Core<br>1.2V I/O, also 2.5V external VPP | LPDDR4: 1.1V, 1.8V Core & I/O<br>LPDDR4X: 0.6V        |

| Data I/O<br>CMD, ADDR I/O                        | Center Tab Termination (CTT)<br>CTT             | Pseudo Open Drain ( <mark>POD</mark> )<br>CTT | LVSTL<br>Programable voltage swing                    |

| Internal Memory Banks                            | 8                                               | 16 for x4/x8 (2 BG), 8 for x16                | 8 per channel                                         |

| Data Rate                                        | DDR3/3L:<br>up to2133/1866 MT/s                 | 1600–3200 MT/s                                | 1600-3200 MT/s<br>(possible 4266 MT/s)                |

| VREF                                             | VREFCA & VREFDQ external                        | VREFCA external<br>VREFDQ internal            | CA Vref Internally Generated,<br>Command Bus Training |

| Data Strobes/Prefetch/Burst<br>Length/Burst Type | Differential/8-bits/BC4, BL8/<br>Fixed, OTF     | Same as DDR3                                  | BL16, BL32                                            |

# **DDR SDRAM Highlights and Comparison (cont'd)**

| Feature/Category            | DDR3 | DDR4 | LPDDR4 |

|-----------------------------|------|------|--------|

| CRC Data Bus & C/A Parity   | No   | Yes  | No     |

| Connectivity test (TEN pin) | No   | Yes  | No     |

| Bank Grouping               | No   | Yes  | No     |

| Data Bus Inversion          | No   | Yes  | Yes    |

| Write Leveling / ZQ / Reset | Yes  | Yes  | Yes    |

| ACT_n new pin & command     | No   | Yes  | No     |

| Low power auto self-refresh | No   | Yes  | Yes    |

| VREFDQ calibration          | No   | Yes  | Yes    |

# **Basic DDR SDRAM Structure**

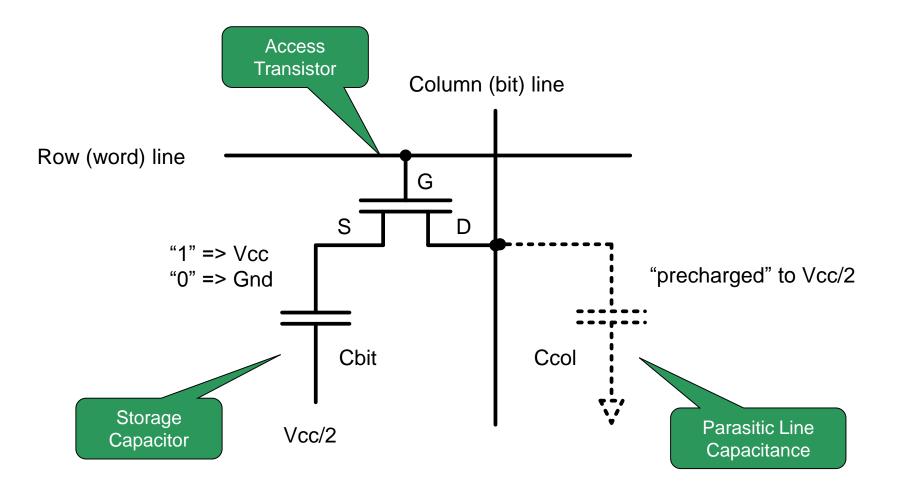

# **Single Transistor Memory Cell**

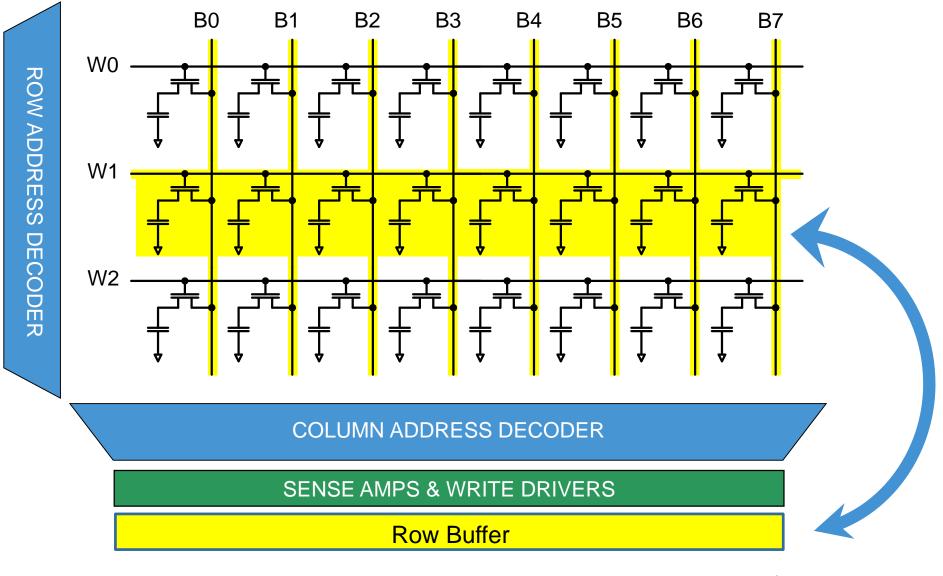

### **Memory Arrays**

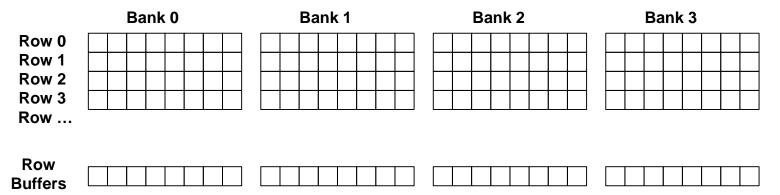

# **Internal Memory Banks**

- Multiple arrays organized into banks

- Multiple banks per memory device

- -DDR3 8 banks, and 3 bank address (BA) bits

- -DDR4 16 banks with 4 banks in each of 4 sub bank groups

- Can have one active row in each bank at any given time

- Concurrency

- Can be opening or closing a row in one bank while accessing another bank

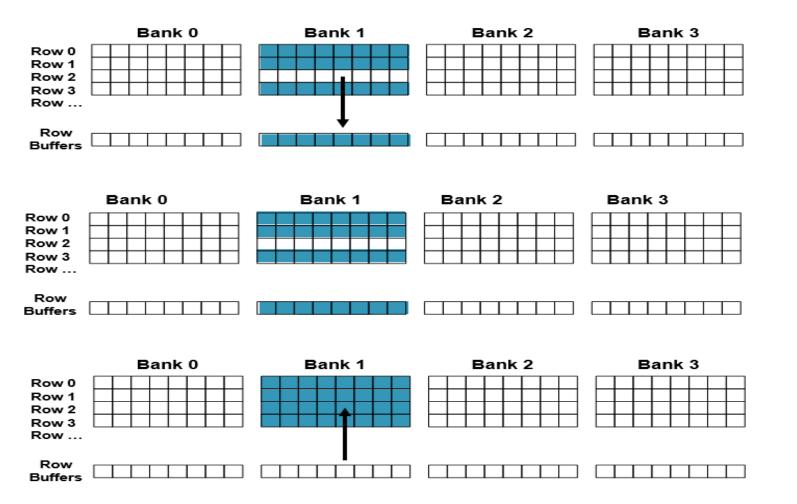

# **Memory Access**

- A requested row is ACTIVATED and made accessible through the bank's row buffers

- READ and/or WRITE are issued to the active row in the row buffers

- The row is **PRECHARGED** and is no longer accessible through the bank's row buffers

Example: DDR4-2133 Open Page = 2.133Gb/s maximum bandwidth Closed Page = 199Mb/s maximum bandwidth <u>10x performance</u> advantage to read and write from an <u>open page</u>

PUBLIC | 16

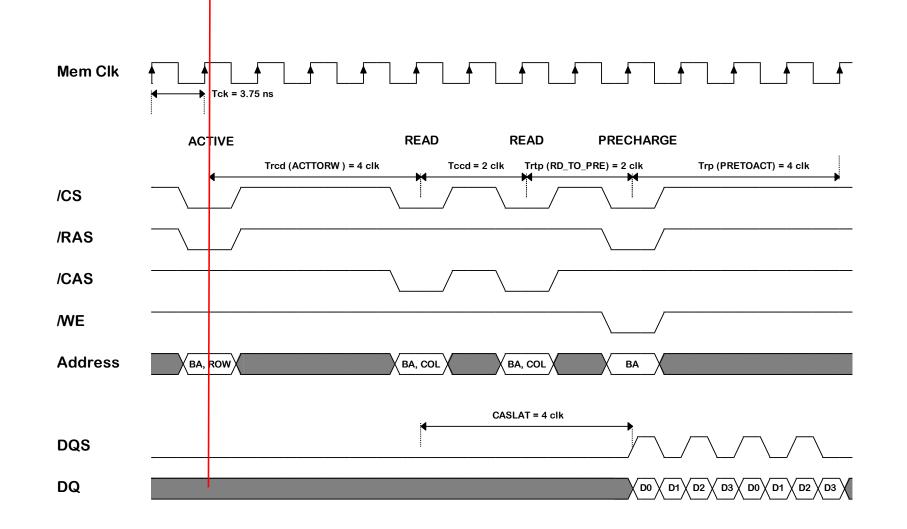

# **DDR2-533 Read Timing Example**

PUBLIC 17

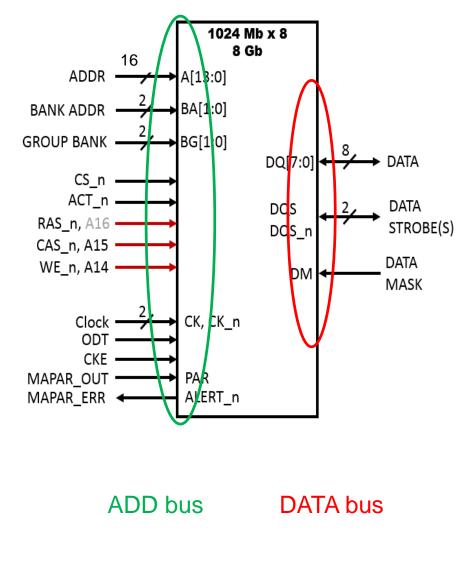

# Example – 8Gb DDR4 SDRAM

- Micron MT40A1G8

- 1024M x 8 (64M x 8 x 16 banks)

- 8 Gb total

- 16-bit row address

- 64K rows

- 10-bit column address

- 1K bits/row (1KB in x8 data with DRAM)

- 2-bit group and 2-bit bank address

- DATA bus: DQ, DQS, /DQS, DM (DBI)

- ADD bus: A, BA, GB, ACT, /CS, /RAS, /CAS, /WE, ODT, CKE, CK, /CK, PAR,

/ALERT

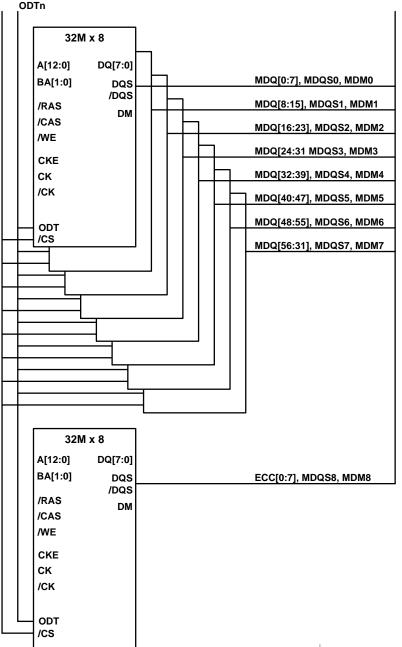

# Example – DDR4 UDIMM

- Micron MTA9ASF51272AZ

- 9 each 512M x 8 DRAM devices

- 512M x 72 overall

- 4 GB total, single "rank"

- 9 "byte lanes"

### **Two Signal Bus**

- 1- Address, command, control, and clock signals are shared among all 9 DRAM devices

- 2- Data, strobe, data mask not shared

/CSn

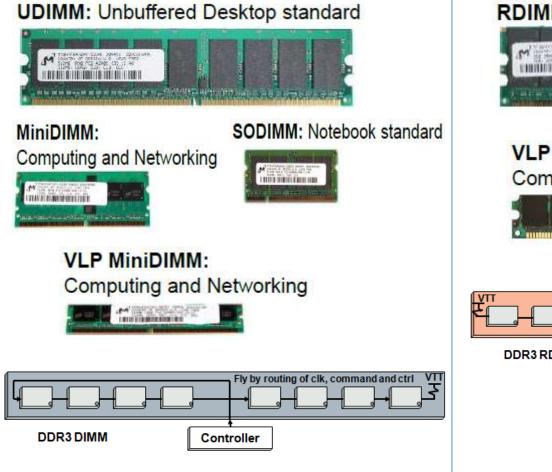

# **DRAM Module Type**

#### **RDIMM:** Registered Server standard

VLP RDIMM: Very Low Profile Computing and Networking

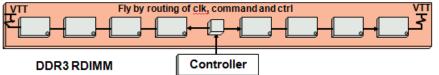

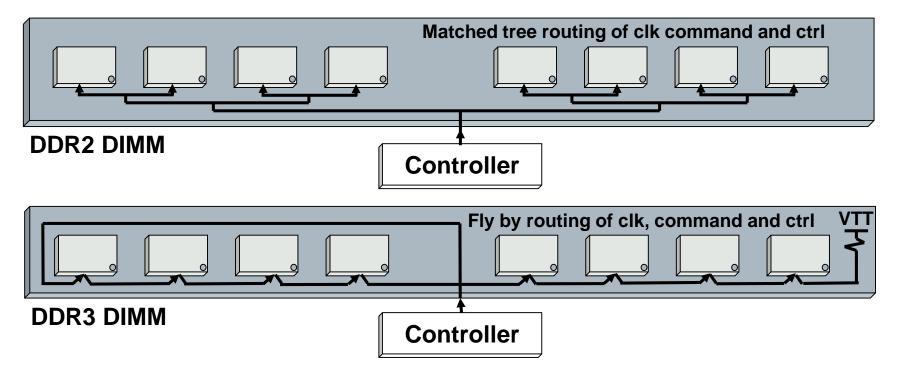

# **Fly-By Routing Topology**

### Introduction of "fly-by" architecture

- Address, command, control & clocks

- Data bus (not illustrated below) remains unchanged, ie, direct 1-to-1 connection between the Controller bus lanes and the individual DDR devices.

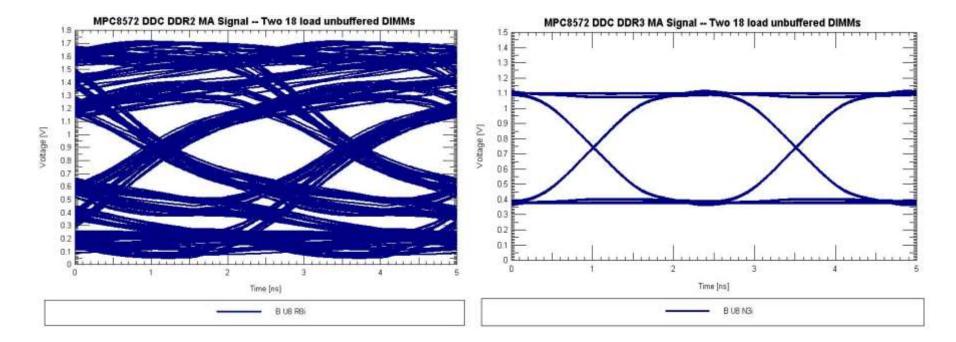

- Improved signal integrity...enabling higher speeds

- On module termination

# **Fly-By Routing Improved SI**

### **DDR2 Matched Tree Routing**

#### **DDR3 Fly By Routing**

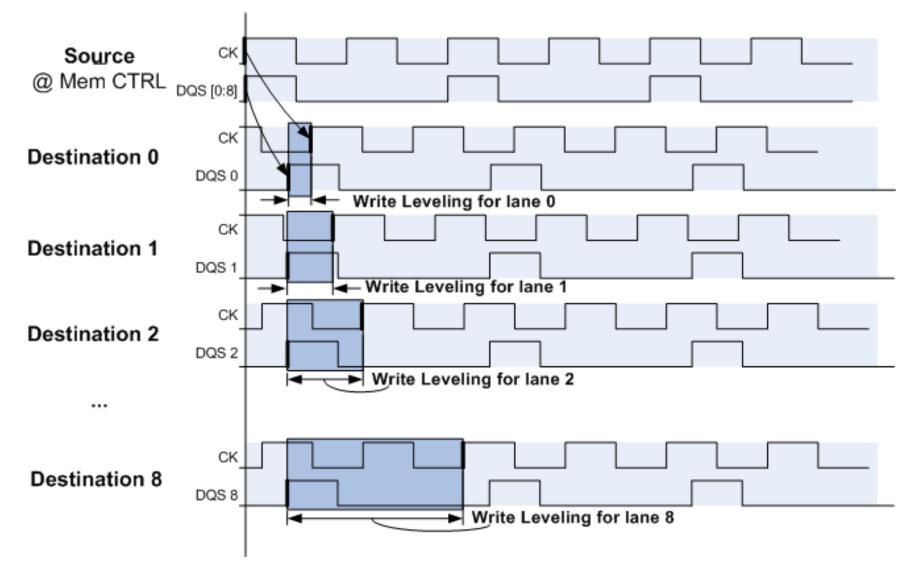

What Is Write Leveling?

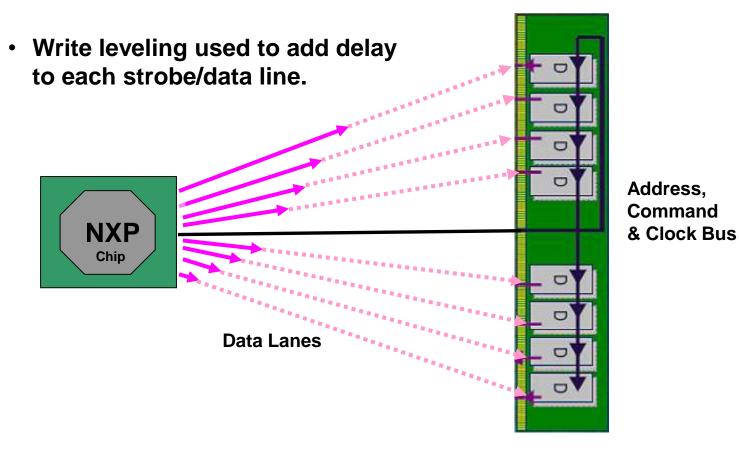

# Write Adjustment

Write leveling sequence during the initialization process will determine the appropriate delays to each data byte lane and add this delay for every write cycle.

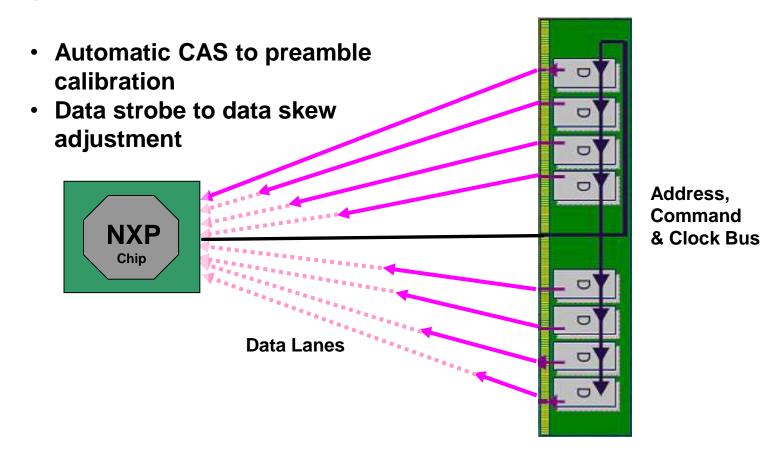

## **Read Adjustment**

Auto CPO will provide the expected arrival time of preamble for each strobe line of each byte lane during the read cycle to adjust for the delays cased by the fly-by topology.

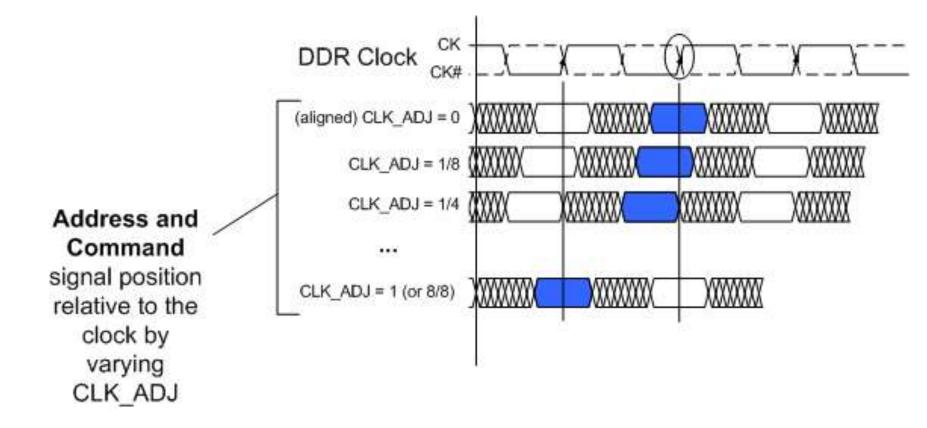

# CLK\_ADJ - Clock Adjust

CLK\_ADJ defines the timing of the address and command signals relative to the DDR clock.

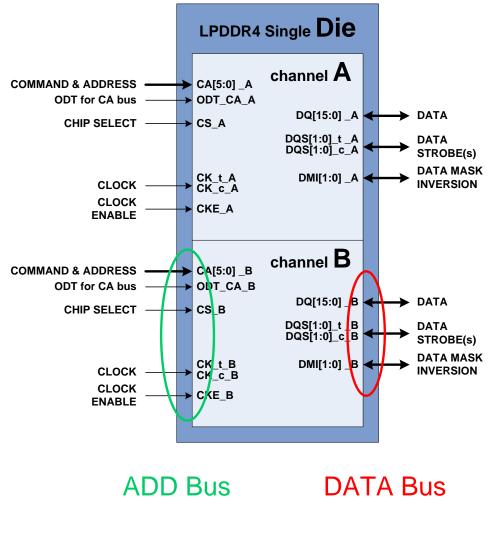

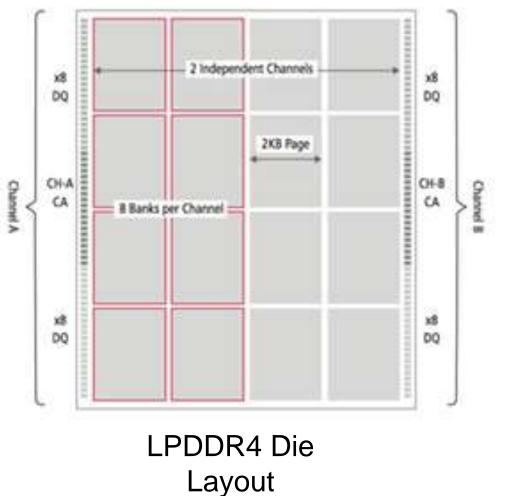

# **Example – generic LPDDR4 SDRAM**

- 2 Channels per die

- 1, 2 or 4 Die per package

- 8 Banks per channel

- 2Gb to 16Gb Density range per channel

- DATA bus: DQ, DQS\_t, DQS\_c, DMI

- ADD bus: CA, OTD\_CA, CS, CKE, CK\_t, CK\_c

# **Example – LPDDR4 Arrangements – Single Die (2 Channels)**

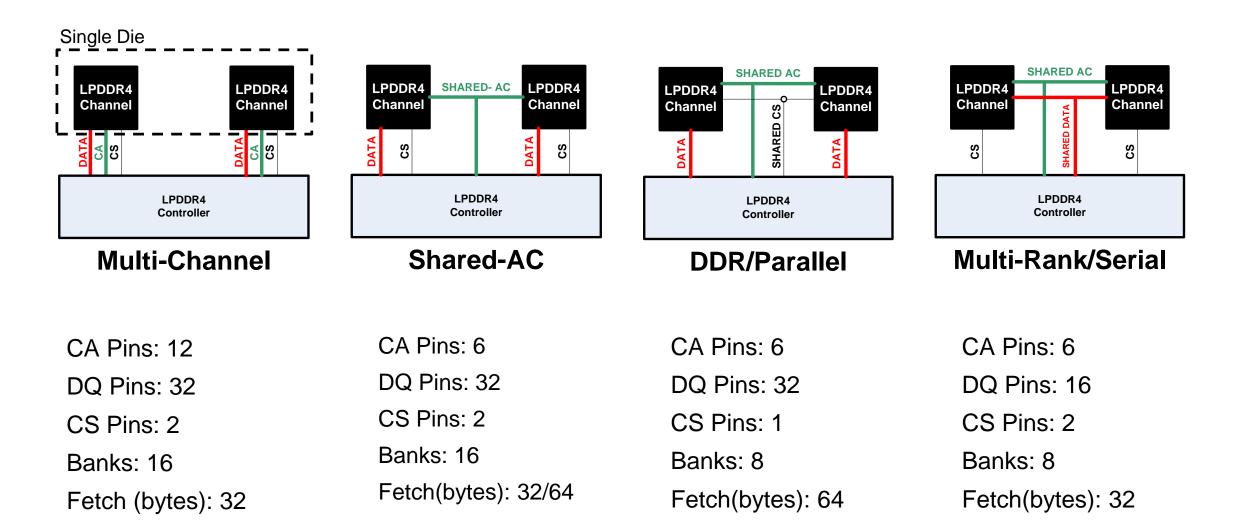

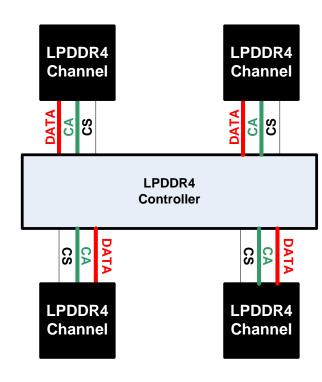

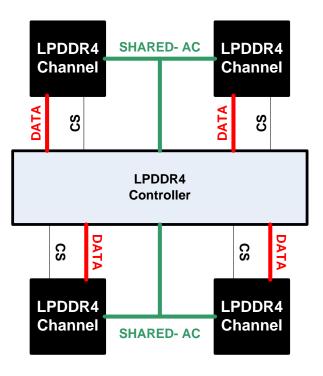

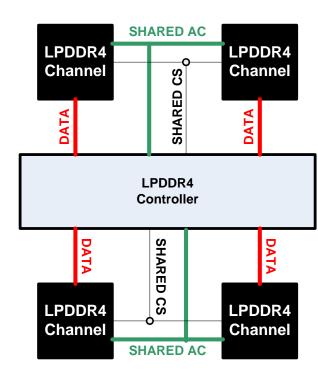

# Example – LPDDR4 Arrangements – 2 Die (4 Channels)

**Multi-Channel**

**Shared-AC**

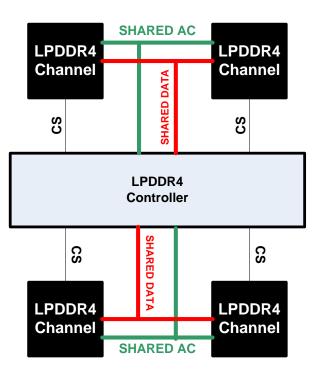

# Example – LPDDR4 Arrangements – 2 Die (4 Channels) cont'd

**DDR/Parallel**

### Multi-Rank/Serial

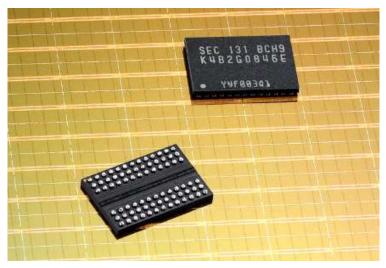

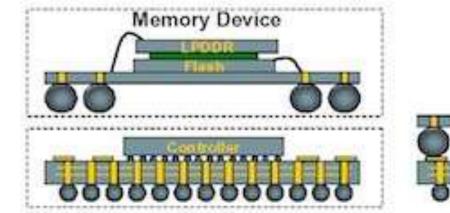

## LPDDR4 Package

### Micron LPDDR4

FLASH & LPDDR in PoP configuration

# **SDRAM Differences**

PUBLIC 32

# **DDR3 vs. DDR4 DRAM Pinouts**

- DDR4 Pins Added

- VDDQ (2) : 1.2V pins to DRAM

- VPP (2): 2.5V external voltage source for DRAM internal word line driver

- BG (2): Bank Group (2): pins to identify the bank groups

- DBI\_n: Data Bus Inversion

- ACT\_n: Active command

- PAR: Parity error signal for address bus

- ALERT\_n: Both, Parity error on C\A and CRC error on data bus

- TEN: Connectivity test mode

- DDR3 Pins Eliminated

- VREFDQ

- Bank Address (1): one less BA pin

- VDD (1), VSS (3), VSSQ (1)

| -           |              |       |                |               |             |

|-------------|--------------|-------|----------------|---------------|-------------|

| VDD         | VSSQ         |       | DM_n,<br>DBI_n | VSSQ          | VSS         |

| VPP         | VDDQ         | DQS_c | DQ1            | VDDQ          | ZQ          |

| VDDQ        | DQ0          | DQS_t | VDD            | VSS           | VDDQ        |

| VSSQ        | DQ4          | DQ2   | DQ3            | DQ5           | VSSQ        |

| VSS         | VDDQ         |       | DQ7            | VDDQ          | VSS         |

| VDDQ        |              | ODT   | CK_t           | CK_c          | VDD         |

| VSS         |              | CKE   | CS_n           |               | TEN         |

| VDD         | WE_n,<br>A14 | ACT_n | CAS_n,<br>A15  | RAS_n,<br>A16 | VSS         |

| VREFCA      | BGO          | A10   | A12            | BG1           | VDD         |

| VSS         | BAO          | A4    | A3             | BA1           | VSS         |

| RESET_<br>n | A6           | AO    | A1             | A5            | ALERT_<br>n |

| VDD         | A8           | A2    | A9             | A7            | VPP         |

| VSS         | A11          | PAR   | A17            | A13           | VDD         |

# New Pin: ACT\_n (Activate Command)

- ACT\_n is a single pin for Active command input

- When ACT\_n is low:

- -ACT Command is asserted

- -WE/CAS/RAS pins will be treated as address pins (A14:A16)

- When ACT\_n is high

- -WE/CAS/RAS pins will be treated as command pins

| VDD     | VSSQ |       | M_n, DBI | VSSQ | VSS     |

|---------|------|-------|----------|------|---------|

| VPP     | VDDQ | DQS_c | DQ1      | VDDQ | ZQ      |

| VDDQ    | DQO  | DQS_t | VDD      | VSS  | VDDQ    |

| VSSQ    | DQ4  | DQ2   | DQ3      | DQ5  | VSSQ    |

| VSS     | VDDQ |       | DQ7      | VDDQ | VSS     |

| VDDQ    |      | ODT   | CK_t     | CK_c | VDD     |

| VSS     |      | CKE   | CS_n     |      | TEN     |

| VDD     | A14  | ACT_n | A15      | A16  | VSS     |

| VREFCA  | BGO  | A10   | A12      | BG1  | VDD     |

| VSS     | BAO  | A4    | A3       | BA1  | VSS     |

| RESET_n | A6   | AO    | A1       | A5   | ALERT_n |

| VDD     | A8   | A2    | A9       | A7   | VPP     |

| VSS     | A11  | PAR   | A17      | A13  | VDD     |

| VDD     | VSSQ |       | M_n, DBI | VSSQ  | VSS     |

|---------|------|-------|----------|-------|---------|

| VPP     | VDDQ | DQS_c | DQ1      | VDDQ  | ZQ      |

| VDDQ    | DQO  | DQS_t | VDD      | VSS   | VDDQ    |

| VSSQ    | DQ4  | DQ2   | DQ3      | DQ5   | VSSQ    |

| VSS     | VDDQ |       | DQ7      | VDDQ  | VSS     |

| VDDQ    |      | ODT   | CK_t     | CK_c  | VDD     |

| VSS     |      | CKE   | CS_n     |       | TEN     |

| VDD     | WE_n | ACT_n | CAS_n    | RAS_n | VSS     |

| VREFCA  | BGO  | A10   | A12      | BG1   | VDD     |

| VSS     | BAO  | A4    | A3       | BA1   | VSS     |

| RESET_n | A6   | AO    | A1       | A5    | ALERT_n |

| VDD     | A8   | A2    | A9       | A7    | VPP     |

| VSS     | A11  | PAR   | A17      | A13   | VDD     |

# LPDDR3 vs. LPDDR4 DRAM Pinouts

- Change from a 10-bit DDR command/address bus to a 6-bit SDR bus

- Address and Commands are encoded on CA lines

- Addresses and Commands distributed over multiple cycle

- Change from one 32-bit wide bus to two independent 16-bit wide buses -x32, (2 channels, x16), x64 (4 channels, x16)

#### **DRAM Densities DDR3 vs. DDR4**

- 16 Banks for x4 and x8 DRAM DDR4, 8 Banks for x16

- 8Gb is DRAMs vendors choice for starting DDR4 density

- Larger memory size is one reason to use x4 vs. x8 vs. x16 DRAM

- Data mask or data bus inversion (DBI), not available in x4 DRAM

|    | Density        | 1Gb |    |     |     | 2Gb |     |     | 4Gb |     |     | 8Gb |     |     | 16 Gb |     |  |

|----|----------------|-----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|-----|--|

|    | Width          | x4  | x8 | x16 | x4  | x8  | x16 | x4  | x8  | x16 | x4  | x8  | x16 | x4  | x8    | x16 |  |

|    | Banks          | 8   | 8  | 8   | 8   | 8   | 8   | 8   | 8   | 8   | 8   | 8   | 8   |     |       |     |  |

| R3 | Rows           | 14  | 14 | 13  | 15  | 15  | 14  | 16  | 16  | 15  | 16  | 16  | 16  |     |       |     |  |

|    | Columns        | 11  | 10 | 10  | 11  | 10  | 10  | 11  | 10  | 10  | 12  | 11  | 11  |     |       |     |  |

|    | Page Size (KB) | 1   | 1  | 2   | 1   | 1   | 2   | 1   | 1   | 2   | 2   | 2   | 2   |     |       |     |  |

|    | Banks          |     |    |     | 16  | 16  | 8   | 16  | 16  | 8   | 16  | 16  | 8   | 16  | 16    | 8   |  |

| R4 | Rows           |     |    |     | 15  | 14  | 14  | 16  | 15  | 15  | 17  | 16  | 16  | 18  | 17    | 17  |  |

|    | Columns        |     |    |     | 10  | 10  | 10  | 10  | 10  | 10  | 10  | 10  | 10  | 10  | 10    | 10  |  |

|    | Page Size (KB) |     |    |     | 0.5 | 1   | 2   | 0.5 | 1   | 2   | 0.5 | 1   | 2   | 0.5 | 1     | 2   |  |

# **DRAM Densities progression in LPDDR**

- LPDDR

-512Mb to 8Gb

- LPDDR2 -512Mb to 16Gb

- LPDDR3

- -4Gb to 32Gb

#### LPDDR4

-4Gb to 32Gb (2Gb to 16Gb per channel)

#### Modules DDR3 vs. DDR4

- U/RDIMM Pin count of 240 vs. 288, pin pitch of 1.0mm vs. 0.85mm

- Bottom edge flat vs. step ramp. Height & width increased by ~1mm

- DRAM ball count and ball pitch not changed

- DIMM topology of fly by for address/command bus not changed

- SoDIMM pin count of 204 vs. 260

- SoDIMM will have native ECC support vs. non-compatible pin out in DDR3

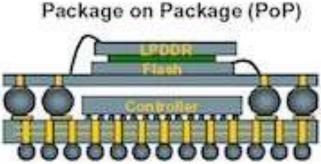

# **Burst Length**

- DDR4 normally has Burst Length of 8 (BL8)

- DDR4 also support pseudo Burst Length of 4 (BC4, OTF BC)

- LPDDR3 Burst Length of 8 (BL8)

- LPDDR4 Burst Length of 16 (BL16)

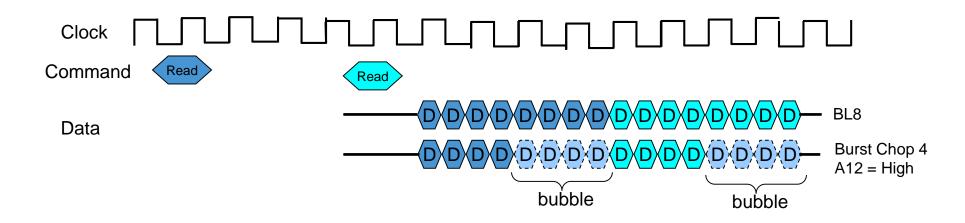

# **DDR4 Output Driver/Termination**

- Center tap termination is used in DDR3 receiver

- POD termination or pull up is used in DDR4 receiver

- Push-Pull driver in DDR3 and POD driver in DDR4

- Less power is consumed using POD driver & termination

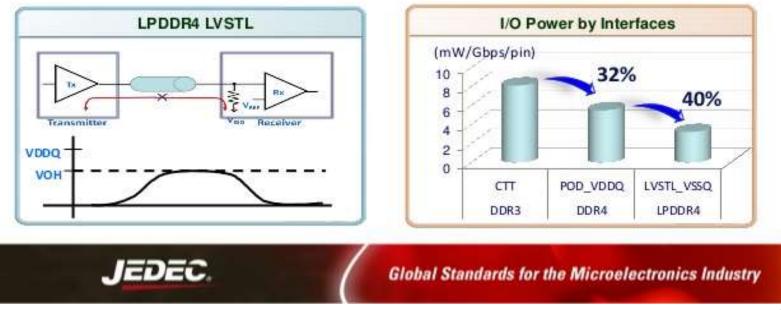

#### **LPDDR4 Output Driver/Termination**

#### LPDDR4 - Innovative Interface LVSTL

#### LVSTL (Low Voltage Swing Terminated Logic)

- High frequency operation with less IO power consumption

- No DC power consumption when driving "low"

- Lower Cio, small Xtalk and SSN, because of small swing

- Stronger reference plane

- Easy voltage scaling

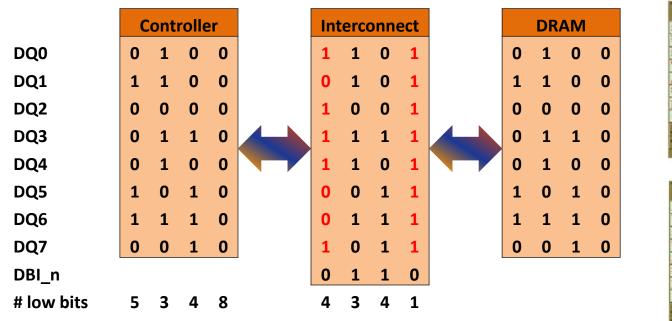

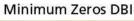

# New Pin: DBI\_n (Data Bus Inversion)

- Active low input/output for data bus inversion mode

- Available only on x8 and x16 DRAM

- **PROs:** Less noise, better data eye and lower power consumption

- CONs: Performance is affected due to data mask not being available and CAS\_LAT is increased by 2 clocks.

#### Data Bus Inversion - DBI

- If more than 4 bits of a byte lane are low, invert the data and drive the DBI\_n pin low

- If 4 or less bits of a byte lane are low, do not invert the data and drive the DBI\_n pin high

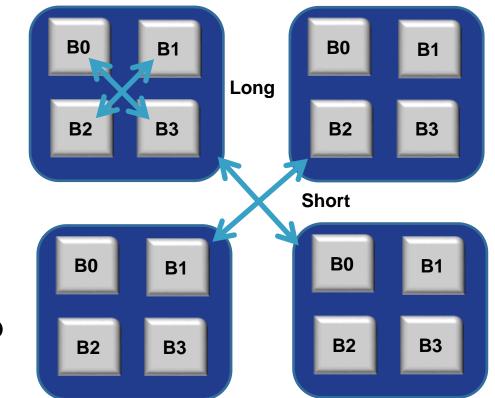

# New Pin: BGn (Bank Group Address)

- Different timing within a group and between groups

- -Active to active (tRRD\_L)

- -Write to read (tWTR\_L)

- -Read to read (tCCD\_L)

- -Write to write (tCCD\_L)

- Controller to maintain timing requirements for both within a group (long) and between groups (short)

| Data rate | 1600 | 1866 | 2133 | 2400 |

|-----------|------|------|------|------|

| tCCD_S    | 4    | 4    | 4    | 4    |

| tCCD_L    | 5    | 5    | 6    | 6    |

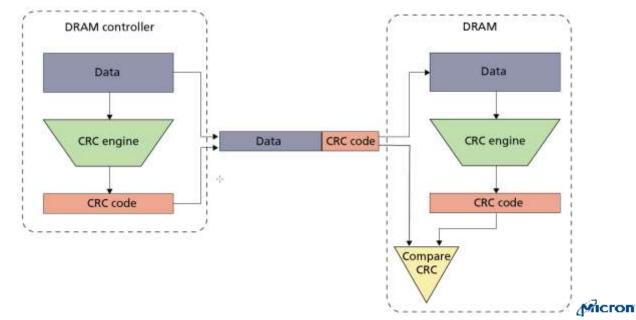

# New Pin: ALERT\_n & Cyclic Redundancy Check (CRC)

- Alert\_n Active low output signal that indicates an error event for reporting C/A parity and data write CRC errors

- Polynomial encoding is used to generate the CRC, 8-bits per write burst

- PROs: Better reliability by detecting data errors during write cycles

- CONs: Two beats added to the write burst to transfer the CRC header

\*Not the same as ECC

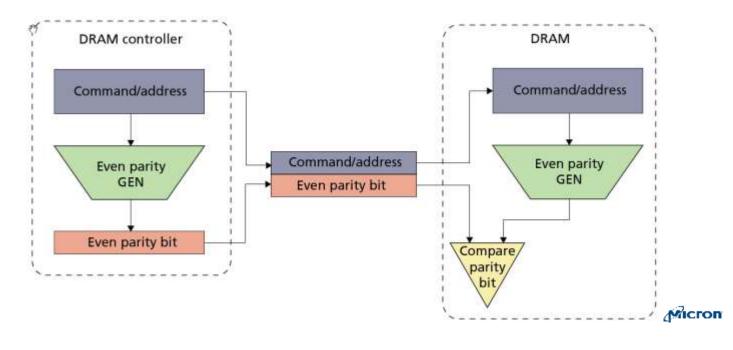

### New Pin: PAR (Address Bus Parity)

- C/A Parity signal (PAR) covers ACT\_n, RAS\_n, CAS\_n, WE\_n and the address bus. Control signals CKE, ODT, CS\_n are not included

- Commands must be qualified by CS\_n

- Alert\_n used to flag error to memory controller

- **PROs:** Better reliability

- CONs: PL (4clk for 2133, 5clk for 2400) is added to read latency

# Cyclic Redundancy Check (CRC)

- Alert\_n Active low output signal that indicates an error event for both the C/A Parity Mode and the CRC Data Mode

- CRC Data mode:

- To detect data errors during write cycles .

- Polynomial encoding is used to generate the CRC for every 8-bit

- -Two beats added to the write burst to transfer the CRC header

- DRAM generates a CRC checksum per each write burst and DQS lane

- DRM compares the generated checksum to controllers checksum

- If Data Mask is disabled, corrupt data is written, with the Alert\_n flag sent to controller to retry the write.

- If Data Mask is enabled, corrupt data is not written, with the Alert\_n flag sent to controller to retry the write.

#### **Data Write CRC**

- Example data mapping with CRC for 8-bit, 4-bit and 16-bit devices

- Note: not the same as ECC

|       | 0   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8    | 9 |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|------|---|

| DQ0   | d0  | d1  | d2  | d3  | d4  | d5  | d6  | d7  | CRC0 | 1 |

| DQ1   | d8  | d9  | d10 | d11 | d12 | d13 | d14 | d15 | CRC1 | 1 |

| DQ2   | d16 | d17 | d18 | d19 | d20 | d21 | d22 | d23 | CRC2 | 1 |

| DQ3   | d24 | d25 | d26 | d27 | d28 | d29 | d30 | d31 | CRC3 | 1 |

| DQ4   | d32 | d33 | d34 | d35 | d36 | d37 | d38 | d39 | CRC4 | 1 |

| DQ5   | d40 | d41 | d42 | d43 | d44 | d45 | d46 | d47 | CRC5 | 1 |

| DQ6   | d48 | d49 | d50 | d51 | d52 | d53 | d54 | d55 | CRC6 | 1 |

| DQ7   | d56 | d57 | d58 | d59 | d60 | d61 | d62 | d63 | CRC7 | 1 |

| DBI_n | d64 | d65 | d66 | d67 | d68 | d69 | d70 | d71 | 1    | 1 |

The following figure shows detailed bit mapping for a x8 device.

The following figure shows detailed bit mapping for a x4 device.

|     | 0   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8    | 9                    |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|----------------------|

| DQ0 | d0  | d1  | d2  | d3  | d4  | d5  | d6  | d7  | CRC0 | CRC4                 |

| DQ1 | d8  | d9  | d10 | d11 | d12 | d13 | d14 | d15 | CRC1 | CRC5                 |

| DQ2 | d16 | d17 | d18 | d19 | d20 | d21 | d22 | d23 | CRC2 | CRC6                 |

| DQ3 | d24 | d25 | d26 | d27 | d28 | d29 | d30 | d31 | CRC3 | CRC5<br>CRC6<br>CRC7 |

#### **Data Write CRC (continued)**

|        | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8     | 9 |

|--------|------|------|------|------|------|------|------|------|-------|---|

| DQ0    | d0   | d1   | d2   | d3   | d4   | d5   | d6   | d7   | CRC0  | 1 |

| DQ1    | d8   | d9   | d10  | d11  | d12  | d13  | d14  | d15  | CRC1  | 1 |

| DQ2    | d16  | d17  | d18  | d19  | d20  | d21  | d22  | d23  | CRC2  | 1 |

| DQ3    | d24  | d25  | d26  | d27  | d28  | d29  | d30  | d31  | CRC3  | 1 |

| DQ4    | d32  | d33  | d34  | d35  | d36  | d37  | d38  | d39  | CRC4  | 1 |

| DQ5    | d40  | d41  | d42  | d43  | d44  | d45  | d46  | d47  | CRC5  | 1 |

| DQ6    | d48  | d49  | d50  | d51  | d52  | d53  | d54  | d55  | CRC6  | 1 |

| DQ7    | d56  | d57  | d58  | d59  | d60  | d61  | d62  | d63  | CRC7  | 1 |

| DBIL_n | d64  | d65  | d66  | d67  | d68  | d69  | d70  | d71  | 1     | 1 |

| DQ8    | d72  | d73  | d74  | d75  | d76  | d77  | d78  | d79  | CRC8  | 1 |

| DQ9    | d80  | d81  | d82  | d83  | d84  | d85  | d86  | d87  | CRC9  | 1 |

| DQ10   | d88  | d89  | d90  | d91  | d92  | d93  | d94  | d95  | CRC10 | 1 |

| DQ11   | d96  | d97  | d98  | d99  | d100 | d101 | d102 | d103 | CRC11 | 1 |

| DQ12   | d104 | d105 | d106 | d107 | d108 | d109 | d110 | d111 | CRC12 | 1 |

| DQ13   | d112 | d113 | d114 | d115 | d116 | d117 | d118 | d119 | CRC13 | 1 |

| DQ14   | d120 | d121 | d122 | d123 | d124 | d125 | d126 | d127 | CRC14 | 1 |

| DQ15   | d128 | d129 | d130 | d131 | d132 | d133 | d134 | d135 | CRC15 | 1 |

| DBIU_n | d136 | d137 | d138 | d139 | d140 | d141 | d142 | d143 | 1     | 1 |

A x16 device is treated as two x8 devices. x16 device will have two identical CRC trees implemented. CRC(0-7) covers data bits d(0-71). CRC(8-15) covers data bits d(72-143).

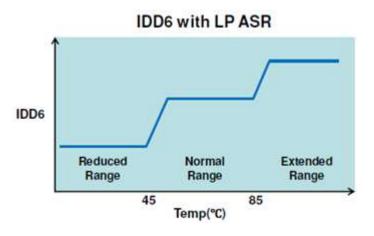

#### Low-Power Auto Self Refresh

- DDR4

- While DRAM is in self-refresh mode, four refresh mode options available:

- Manual mode, normal temperature (45C 85C)

- Manual mode, extended temperature (85C 95C)

- Manual mode, reduced temperature (0C 45C)

- Automatic mode: automatically switches between modes based on temperature sensor measurements

- Power savings by reducing refresh rate when possible

| Auto Self Refresh | DDR4      | DDR3      |  |  |

|-------------------|-----------|-----------|--|--|

| Extended Range    | 85°C-95°C | 85°C-95°C |  |  |

| Normal Range      | 45°C-85°C |           |  |  |

| Reduced Range     | 0°C-45°C  | 0°C-85°C  |  |  |

- LPDDR4

- Temperature-compensated self refresh (TCSR) mode

- Partial-array self refresh (PASR)

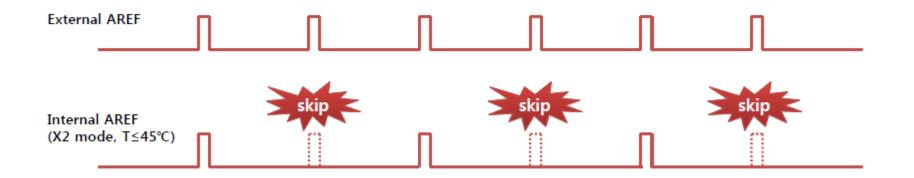

#### **Temperature Controlled Auto Refresh**

- Enabled or disabled in MR4

- In extended temp mode controller sends refresh commands every 3.9us

- DRAM based on the internal temp sensor will skip refresh commands automatically to save power

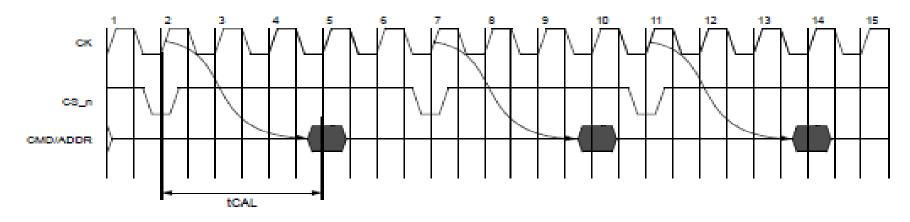

#### **Command Address Latency (CAL)**

- DDR4 supports CAL as a power savings feature

- In default mode, DRAM C/A input receivers are always on

- In CAL mode, only CS receiver is always on. All remaining C/A input receivers are kept in a low power state when not in use. CS signal is sent N number of cycles earlier to allow DRAM time to wake up C/A input receivers

Figure 34 — Definition of CAL

# Why DDR4 Over DDR3?

- Save on power and cost

- DDR4 can reduce power by up to 37%

- DDR4 price cross-over at the end of 2015

- Higher Data rates

- DDR4 offers double the data rate

- DDR4 doubles the number of internal banks, increased bandwidth

- New options to increase performance

- Better reliability & manufacturing capabilities

- Connectivity test

- Data bus inversion (DBI)

- Internal VREF calibration

- CRC on DATA & parity on ADDRESS bus

- Larger densities

# Why LPDDR4 Over PLDDR3?

- Save power

- LPDDR4 can reduce overall power by up to 37% over LPDDR3

- Many power savings mechanisms:

- Temperature-compensated self refresh (TCSR), Partial-array self refresh (PASR), Deep power-down (DPD), Programmable drive strength (DS), Programmable VOH signal level

- Higher Data rates

- Faster Clock rates

- Two-channel architecture

- Increased speed due dual channel die layout

- Shorter signal distances

- Flexible memory configurations

Better suite the application

- Larger densities

# General Hardware and Software Design Guidelines and Tips

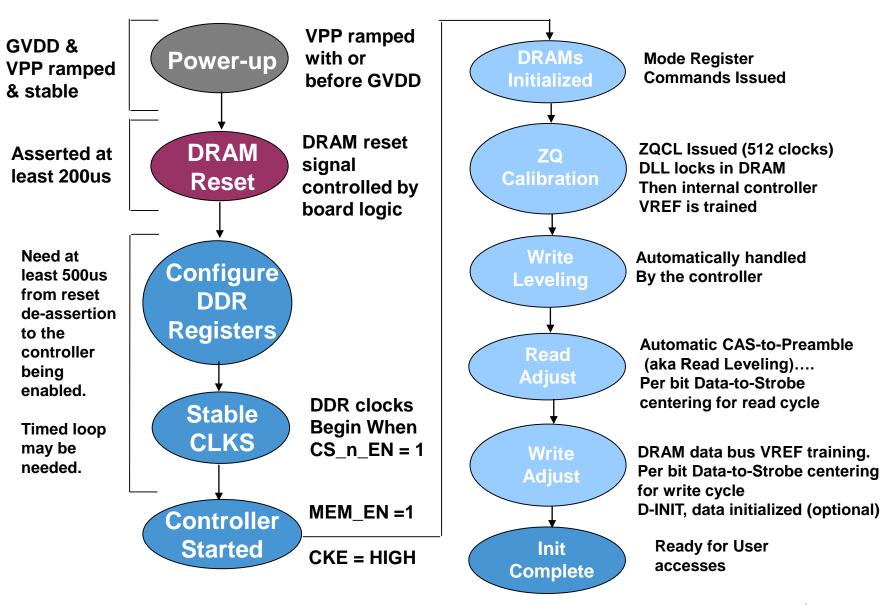

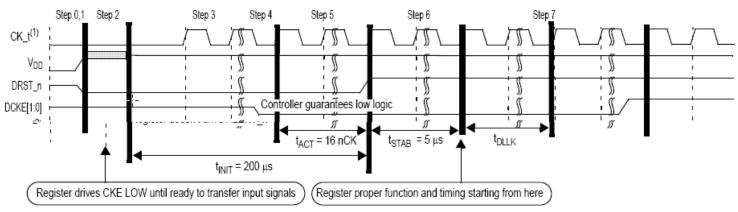

#### **DDR4 Initialization Flow**

#### **General Hardware Guidelines**

- Examine the DDR4 Layout Guidelines for QorIQ devices App. Note (AN5097)

- Run pre and post board simulation

- IBIS models are available for both controller and DRAM

- Employ industry standard practices

- Minimize Crosstalk, ISI, Vref noise, Impedance mismatches

- Eliminate return path discontinuities (RPD)

- Minimize the simultaneous switching output (SSO) effects

- Proper distribution of power and ground planes

- Proper capacitance decoupling

- Examine the reference design boards with DDR4 implemented

- Both discrete and DIMM DDR4 are available for QorIQ devices

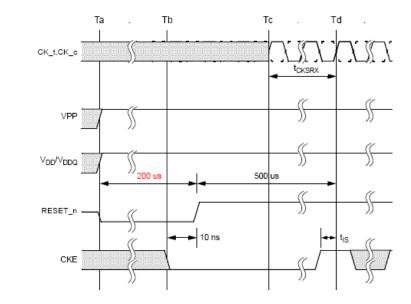

# Important HW Considerations for DDR4 Transition

- VPP supply

- VPP = 2.5V required for each DRAM

- Follow DRAM vendor specification for power/current requirements

- VPP ramped with or before GVDD

- VrefDQ reference input is removed

- New signals added to each DRAM

- ACT\_n

- DBI

- PAR

- TEN (Pull to GND when not used)

- ALERT

| QorlQ | with | DDR3  | L\DDR4 |

|-------|------|-------|--------|

| me    | mory | contr | oller  |

| DDR3L     | DDR4         |

|-----------|--------------|

| MRAS      | MRAS/ MA[16] |

| MCAS      | MCAS/ MA[15] |

| MWE       | MWE/ MA[14]  |

| MA[15]    | ACT_n        |

| MA[14]    | BG1          |

| MBA[2]    | BGO          |

| MDM[0-8]  | MDM / DBI    |

| MAPAR_ERR | Alert_n      |

| MAPAR_OUT | PAR          |

# **UDIMM vs. RDIMM DDR4 Reset**

- UDIMM requires CKE to be low before RESET is de-asserted.

- RDIMM requires CKE to be low and clock to be present before RESET is deasserted

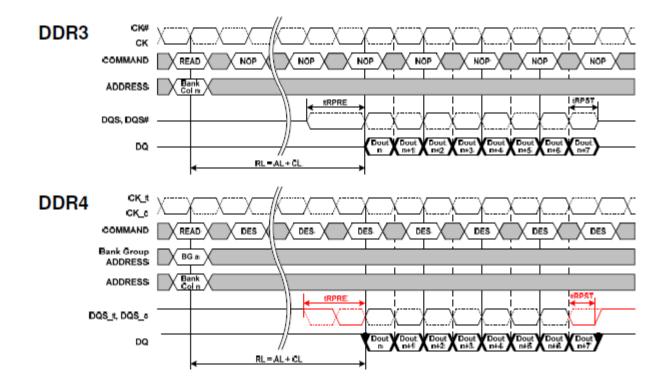

#### **DDR3 and DDR4 Preamble and Idle Signal Differences**

- DQ and DQS signals stay high during idle time

- DQS preamble is same for Read and Writes

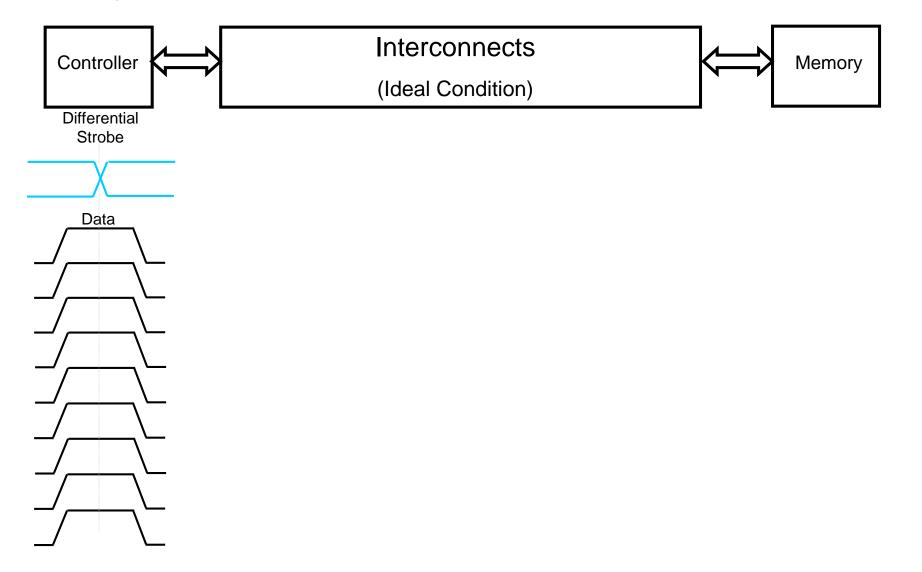

# **Timing Budget**

- UI, the max theoretical timing budget is divided between controller, DRAM and the interconnect.

- When using Timing from the datasheet

- Adjust datasheet values to simulated slew rates

- Datasheet values are based on 1V/ns slew rates

- Convert from VIH/Lac and VIH/Ldc to Vref values (A/C bus)

- Account for slew rate variation

- Data eyes are based on Vref values

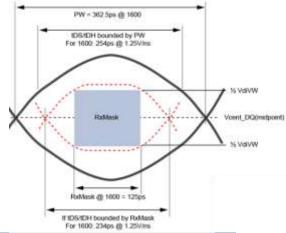

- Rx Mask modifies the READ and WRITE timing budgets calculation

Examples will clarifies the calculations

- tDVWp can be used for READ timing budget

# **Data Write Timing Budget Calculation**

- The example shows 152ps available for the interconnect at 2133

- For timing budget purpose, Rx mask can be the red dotted lines, but actual signal must be black lines

| Element      | Skew Component                 | DDR4  | -2133 | DDR4  | DDR4-2400 |    | Comments                                                                               |

|--------------|--------------------------------|-------|-------|-------|-----------|----|----------------------------------------------------------------------------------------|

|              |                                | Setup | Hold  | Setup | Hold      |    |                                                                                        |

| Clock        | Data/strobe chip PLL jitter    | 0     | 0     | 0     | 0         | ps | Input clock jitter does not affect data capture, can insert DQS to data offset, in any |

|              | DRAM tJITper                   | 23.5  | 23.5  | 21    | 21        | ps | Use what DRAM is tested for                                                            |

|              | Clock skew                     | 0     | 0     | 0     | 0         | ps | Potential clock to strobe to data skew                                                 |

| Transmitter  | Controller skew                | 77    | 77    | 73    | 73        | ps | Assume 70% of DRAM's                                                                   |

| Interconnect | DQ crosstalk and ISI1          | 0     | 0     | 0     | 0         | ps | 1 victim (1010), 4 aggressors (PRBS)                                                   |

|              | DQS crosstalk and ISI1         | 0     | 0     | 0     | 0         | ps | 1 shielded victim (1010), 2 aggressors (PRBS)                                          |

|              | VREF reduction                 | 0     | 0     | 0     | 0         | ps | Vref generated internally, not required                                                |

|              | REFF mismatch                  | 0     | 0     | 0     | 0         | ps | Vref generated internally, not required                                                |

|              | Path matching (board)          | 0     | 0     | 0     | 0         | ps | Within byte lane: 165 ps/in; mismatch within DQS to DQ                                 |

|              | Path matching (module)         | 0     | 0     | 0     | 0         | ps | Module routing skew (30% reduction with leveling)                                      |

|              | Input capacitance matching     | 0     | 0     | 0     | 0         | ps | Strobe to data variation, estimated                                                    |

|              | ODT skew (1%)                  | 0     | 0     | 0     | 0         | ps | Estimated                                                                              |

|              | Total interconnect             | 0.0   | 0.0   | 0.0   | 0.0       | ps |                                                                                        |

| Receiver     | DRAM skew                      | 80.9  | 80.9  | 75.8  | 75.8      | ps | DRAM spec, RX mask, cal per DQ, TdiPW met, 2V/ns                                       |

|              | VrefDQ Calibration Error       | 0     | 0     | 0     | 0         | ps | Assumes per DQ calibration (spec)                                                      |

|              | Total Receiver                 | 80.9  | 80.9  | 75.8  | 75.8      | ps | DBI not enabled                                                                        |

| Total loss   | Total skew                     | 157.6 | 157.6 | 148.5 | 148.5     | ps | Transmitter + receiver + interconnect skews                                            |

| MAX eye      | Time available                 | 234.3 | 234.3 | 208.3 | 208.3     | ps | Total time available                                                                   |

| Budget       | Timing margin for Interconnect | 76    | 76    | 59    | 59        | ps |                                                                                        |

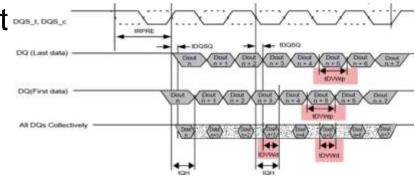

# **Data Read Timing Budget Calculation**

- - -Uses new tDVWp specification

- Requires per DQ calibration

| Element                  | Skew Component                 | DDR4-2133 |       | DDR4  | DDR4-2400 |    | Comments                                                                 |               |

|--------------------------|--------------------------------|-----------|-------|-------|-----------|----|--------------------------------------------------------------------------|---------------|

|                          |                                | Setup     | Hold  | Setup | Hold      |    |                                                                          |               |

| Clock                    | Data/strobe chip PLL jitter    | 19        | 19    | 17    | 17        | ps | estimated stargeted sigma (usuauly around 10-sigma)                      |               |

|                          | DRAM tJITper                   | 14.1      | 14.1  | 12.6  | 12.6      | ps | DRAM output timing assumes no clock jitter; must derate tJITduty below   | v             |

|                          | Clock skew                     | 4.9       | 4.9   | 4.4   | 4.4       | ps | Amount of clock period reduction not acocunt for in duty cycle reduction | ۱             |

| Transmitter <sup>1</sup> | tCK/2 - DVWp                   | 159.3     |       | 14    | 1.6       | ps | Controller trains per DQ                                                 |               |

|                          | tJITduty (measured)            | 19        | 19.74 |       | 17.64     |    | tJITduty measured, not specification; assume 70% of tJITper              |               |

|                          | Static duty cycle adjust 9.4   |           | .4    | 8.3   |           | ps | 0.5tCK to 0.49tCK                                                        |               |

|                          | Transmitter skew               | 94.2      | 94.2  | 83.8  | 83.8      | ps | total transmitter skew                                                   |               |

| 1                        | DQ crosstalk and ISI           | 0         | 0     | 0     | 0         | ps | 1 victim (1010), 4 aggressors (PRBS)                                     |               |

|                          | DQS crosstalk and ISI          | 0         | 0     | 0     | 0         | ps | 1 shielded victim (1010), 2 aggressors (PRBS)                            |               |

|                          | VREF reduction (input eye)     | 0         | 0     | 0     | 0         | ps | Vref generated internally, not required                                  |               |

|                          | REFFmismatch                   | 0         | 0     | 0     | 0         | ps | Vref generated internally, not required                                  |               |

|                          | Path matching (board)          | 0         | 0     | 0     | 0         | ps | Within byte lane: 165 ps/in, mismatch within DQS to DQ                   |               |

|                          | Path matching (module)         | 0         | 0     | 0     | 0         | ps | Module routing skew (30% reduction with leveling)                        |               |

|                          | Capacitance matching           | 0         | 0     | 0     | 0         | ps | Strobe to data variation                                                 |               |

|                          | ODT skew (1%)                  | 0         | 0     | 0     | 0         | ps | Estimated                                                                |               |

|                          | Total interconnect             | 0         | 0     | 0     | 0         | ps |                                                                          |               |

| Receiver                 | Memory controller skew         | 80.9      | 80.9  | 75.8  | 75.8      | ps | DRAM specification used, assume 2V/ns                                    |               |

|                          | VrefDQ Calibration Error       | 0         | 0     | 0     | 0         | ps | Assumes per DQ calibration, internal Vref                                |               |

|                          | Total Receiver                 | 80.9      | 80.9  | 75.8  | 75.8      | ps | DBI not enabled                                                          |               |

| Total loss               | Total skew                     | 180.0     | 180.0 | 164.0 | 164.0     | ps | Transmitter + receiver + interconnect skews                              | ~?            |

| MAX eye                  | Time available                 | 234.3     | 234.3 | 208.3 | 208.3     | ps | Total time available                                                     | Micro         |

| Budget                   | Timing margin for Interconnect | 54        | 54    | 44    | 44        | ps |                                                                          | 9-11 (Sec. 1) |

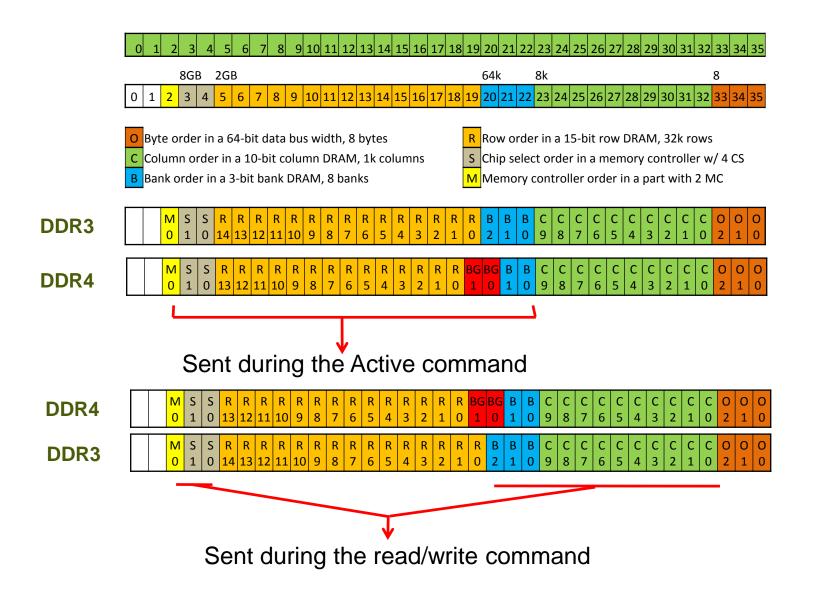

#### **Address Decoding for DDR**

#### **Software Use Case Considerations**

- Look-Up tables

- One write and many reads, 100% random access

- -Worst case is to access the data from the same bank

- Solution: copy identical table in two or more banks

- Statistics Counters

- Equal read to write ratio or read-modify write

- To maintain millions of counters

- Solution: Instead of reading and writing back to the same counter, read from many (a group of) counters and write back to many (a group of) counters.

# i.MX DRAM Register Programming Aid

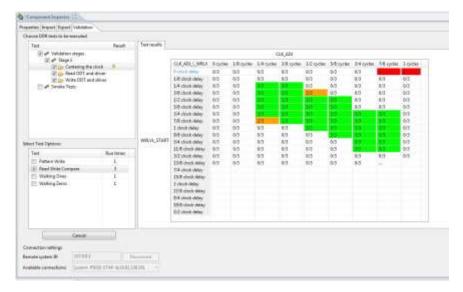

# **Tools for DRAM Bring-up and Debug**

#### DRAM Register Programming aid

| Run basic DDR initialization and test memory                         | Assuming the use of a JTAG debugger, run the <b>DDR</b><br><b>initialization</b> and open a debugger memory window pointing to<br>the DDR memory map starting address. Try writing a few words<br>and verify if they can be read correctly. If not, re-check the<br><b>DDR initialization</b> sequence and if the DDR has been correctly<br>soldered onto the board. It is also recommended to re-check the<br>schematic to ensure the DDR memory has been connected to the<br>SoC correctly. In some cases, a DRAM calibration routine may<br>need to be executed, see next row. |  |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Run DRAM Stress test (some SoC's include a DRAM calibration routine) | A unit test that focuses on the robustness of the DRAM<br>interface. Downloaded through JTAG debugger into internal<br>RAM. Some SoC's DRAM stress test, like MX6Q, includes<br>option to run DRAM calibration.                                                                                                                                                                                                                                                                                                                                                                   |  |

**DRAM Stress Test**

# **DRAM Register Programming Aid – Intro**

- Tool to help create DRAM init scripts for specific memory types

- Mainly used to help program JEDEC timing parameters

- tRCD, tRC, tRFC, etc...

- and for different DRAM parameters like rows, cols, and chip selects

- Internal tool: Customers told to contact FAE for information

- Excel spread sheet based, transparent, ease-of-use

- "Automatically" creates RVD init script (.inc file)

- To convert RVD to Lauterbach script format, Contact FAE.

- How to modify \*.inc script to \*.ds for use with D5-Stream:

- Change file name to \*.ds

- Substitute "mem set <reg\_add> 32 <reg\_val>"

- For "set mem /32 <reg\_add> = <reg\_val>"

## **DRAM Register Programming Aid – Intro (Continued)**

- Based on scripts provided by design/validation

- Anyone can use it, change it, fix it, etc...

- Each Programming Aid tool based on DRAM tech (DDR3, DDR2, LPDDR2, etc)

- · What's been created to date:

- -MX7D: DDR3, LPDDR3

- DDR3, LPDDR2; MX6DL: DDR3,LPDDR2; MX6SL: DDR3,LMX6DQ:PDDR2; MX6SX: DDR3, LPDDR2

- -MX50: mDDR, LPDDR2, DDR2

- -MX28: mDDR, DDR2

- -What about other i.MX? No plans yet, need to resource this if enough interest

# DRAM Register Programming Aid – Intro (Continued)

- Originated due to Denali controller on MX28 and MX50

- Denali controller complex, many registers to program

- Required use of Denali-specific tools available only to factory engineers (due to Denali license); burden on factory support

- Even with Denali tools, the DRAM init scripts required further "tweaking" due to i.MX design integration

- Register programming aid takes into account any "tweaking" and incorporates i.MX design specifics (based on scripts from design/validation)

- Register programming aid offers more visibility on how the DRAM controller is being programmed

- Register programming aid tool concept carried over to i.MX FIL base controllers, starting with MX53 and MX6 series

- Tools are available to customers through assigned FAE's

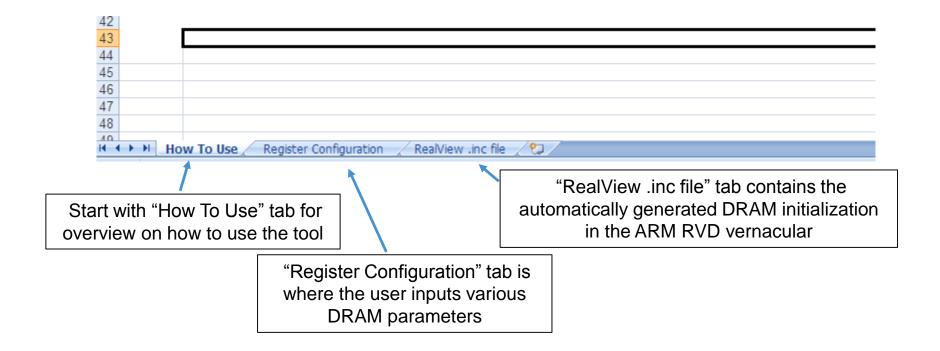

# **DRAM Register Programming Aid – Usage Overview**

- Programming aid tool Excel Spreadsheet based

- There are three tabs (worksheets)

How to use the DRAM register programming aid outline

How To Use / Register Configuration / RealView .inc file /

Step 1. Obtain the desired DRAM data sheet from the DRAM vendor

The following are to be completed in the Register Configuration Worksheet tab.

How To Use Register Configuration RealView .inc file

Step 2. Update the Device Information table to include the DRAM information and system usage

| Device Information             | to the second  |     |

|--------------------------------|----------------|-----|

| Memory type:                   | mDDR           |     |

| Manufacturer.                  | Micron         |     |

| Memory part number.            | MT46H64M16LF-5 |     |

| Memory timing info:            | 5.0ns          |     |

| Total DRAM Density per CS (Gb) | 1              | - 4 |

| Number of ROW Addresses        | 14             |     |

| Number of COLUMN Addresses     | 10             |     |

| Number of BANKS                | 4              |     |

| Number of Chip Selects used    | 1              |     |

| Total DRAM density (Gb)        | 1              |     |

| Bus Width                      | ×16            |     |

| Clock Cycle Freq (MHz)         | 200            | 6   |

| Clock Cycle Time (ns)          | 5              |     |

Step 3. Go through the various shaded cells in the spread sheet to update with data from the DRAM sheet (take special note of the "Legend" table to ascertain the meaning of different shaded cells; in many cases, the cells may not need to be updated).

| Instructions                                                                                                                                                                                                                                                                              | Legend                                                                                                                                                                                                                                                                  |                                  |                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------------|

|                                                                                                                                                                                                                                                                                           | On Register Configuration Tab, this color indicates the bitfields<br>that would commonly require updating.<br>On Register Configuration Tab, this color indicates the bitfields<br>that may be updated, but should typically not require it.                            |                                  | Pay attention to shaded cells – this is where |

| Shaded cells may require updating per the DRAM memory data sheet parameters. Certain<br>registers should not need to be modified by the user. If a register is not provided then it is<br>assumed this parameter is not to be changed eer the provided initialization scretch or that the | On Register Configuration Tab, this color indicates the bitfields<br>that are updated automatically from setting provided in the<br>"Device Information" table or other cells, and should not be<br>changed manually                                                    | Automatically<br>Updated Setting | you input data                                |

| register is read-only. Certain registers are provided though they may be noted as<br>recommended to not change.                                                                                                                                                                           | On Register Configuration Tab, an unshaded cell means that the<br>value should remain as is and should not be modified. In these<br>cases, the settings are provided for completeness.                                                                                  |                                  | Con't touch un-shaded cells                   |

|                                                                                                                                                                                                                                                                                           | On other tabs, this color indicates the cells that are affected by<br>changes on the Register Configuration tab. Note, this cell<br>shading should not used in this workshear Register Configuration<br>tab, only in other tabs that are affected by cells in this tab. |                                  | This is relevant to the "RealView .inc file"  |

The following refers to the RealView .inc file Worksheet tab. In this tab, the entire DRAM initialization can be obtained. This initialization can be used as a RealView include file (see below) or are reference for the bootloader DRAM initialization.

Step 4. Go to the RealView .inc file Worksheet tab and copy and paste this into a text document (make sure to rename the document with a ".inc" file ending); this is ready to use with the RealView development system.

Step 5. This .inc file can also be used as a reference for other debugger tools and bootloaders.

Note, each spread sheet is for a specific i.MX SoC and DRAM memory type.

| <ul> <li>These construction</li> <li>inputs value</li> </ul>                                    |                                         |                  |           |        |      |           |    | 1         |      | binary<br>setting |                                                                                                                                                     | How To Use                                                                                                                                                                                                     | Register Config | uration / F               | RealView .in | c file 🔪                                                                       |

|-------------------------------------------------------------------------------------------------|-----------------------------------------|------------------|-----------|--------|------|-----------|----|-----------|------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------|--------------|--------------------------------------------------------------------------------|

|                                                                                                 |                                         | m para           |           |        |      | ns 🕨      |    | clk       |      | within<br>reaiste | r description                                                                                                                                       |                                                                                                                                                                                                                | Register name   | Register<br>address (HEX) | Register     |                                                                                |

| Example tRC:<br>1. User inputs '55'<br>(in 'ns')                                                |                                         | TFAW (IFA        | M)        |        | 50   |           |    | 10        |      | GA000000          |                                                                                                                                                     | to maintain consistency<br>tialization, recommend to<br>affect on performance or                                                                                                                               | HW_DRAM_CTL39   | 0×800E009C                | 0×0A000000   |                                                                                |

| 2. Tool calculates<br>that 55ns=11clks*<br>3. Then configures<br>binary setting for<br>register |                                         | TMRD (tM8        | RD)       |        | ÷    |           |    | 2         |      | 82000000          | DRAM TMRD parameter in cycles. De<br>of cycles required between two mode i<br>This is the time required to complete th                              | register write commands<br>he write operation to the<br>parameter however, this                                                                                                                                | HW_DRAM_CTL40   | 0×800E00A0                | 0x02009C40   | <ul> <li>Regisivative values</li> <li>calculative automative values</li> </ul> |

| register<br>4. Tool takes all<br>binary settings to                                             |                                         | TINIT (UNI       | -25       | _      | 2000 | 00        | 4  | 0000      |      | 00009C40          | DRAM TPDEX parameter in cycles. Th                                                                                                                  | e this parameter.                                                                                                                                                                                              |                 | -                         |              | from u                                                                         |

| create final register                                                                           |                                         | TPDEX (IX        |           |        | ▼ 15 |           |    | 3         |      | 00020000          | DRAM TRCD parameter in cycles. De<br>CAS delay: in cycles                                                                                           |                                                                                                                                                                                                                | HW DRAM CTL41   | 0x800E00A4                | 0×0002030B   | • The                                                                          |

| Clock: 200MHz.                                                                                  |                                         | TRC (IRC         | 3         |        | 55   |           |    | 11        |      | 0000000B          | DRAM TRC parameter in cycles. Defin<br>between active commands for the sam<br>the sum of tRAS+tRP (for tRP, use the<br>tRP_AB for safer margin)     | e bank, in cycles. This is                                                                                                                                                                                     |                 |                           |              | values<br>also<br>automat                                                      |

| lock period: 5ns                                                                                |                                         | MAX (tRA         | 1         |        | 7000 |           | 1  | 4000<br>8 | -    | 00368000          | DRAM TRAS_MAX parameter in cycle<br>maximum row active time, in cycles<br>DRAM TRAS_MIN parameter in cycles<br>minimum row activate time, in cycles |                                                                                                                                                                                                                | HW_DRAM_CTL42   | 0x800E00A8                | 0×00368008   | update<br>the                                                                  |

| xample based on                                                                                 | 1995                                    | TRP (189         |           |        | 15   |           |    | 3         | 1.1  | 00000006          | DRAM TRP (single bank) parameter in                                                                                                                 | ycles.                                                                                                                                                                                                         |                 |                           |              | "RealV<br>.inc file                                                            |

| MX28                                                                                            |                                         | TRFC (RF         | <u>C)</u> |        | 110  | <u>x:</u> |    | 22        |      | 00160000          |                                                                                                                                                     | s is the auto refresh duty<br>sheets). This is the<br>refresh commands to<br>auto refresh commands are<br>R data sheet should<br>seconds). In some cases,<br>the DDR data sheet only<br>ammands in a 64ms time | HW_DRAM_CTL43   | 0x000E00AC                | 0x03160612   |                                                                                |

| ACTIVE-to-PRECHARGE<br>command                                                                  |                                         | 'RAS             | 40        | 70,000 | 42   | 70,000    | 42 | 70,000    | 45   | 70,000            | ns 22                                                                                                                                               |                                                                                                                                                                                                                |                 |                           |              | ,                                                                              |

| ACTIVE to ACTIVE/ACTI<br>TO REFRESH command                                                     | 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - | 'RC              | 55        | 5      | 58,2 | 7         | 60 | -         | 67.5 | -                 | ns                                                                                                                                                  | Example                                                                                                                                                                                                        | Micron mE       | DR dat                    | a sheet      | spec                                                                           |

| Active to read or write                                                                         | delay                                   | <sup>1</sup> RCD | 15        | -      | 16.2 | 14        | 18 | -         | 22.5 | -                 | ns                                                                                                                                                  |                                                                                                                                                                                                                |                 |                           |              |                                                                                |

PUBLIC 73

• Changing device information, automatic update to register fields

|                                                                                                                                                      | /                       | 1. Type in c           | levice p | arameter            | s here          | ]                                                                                                                                                     |          |                  |                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------|----------|---------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------------------|

| Device Information                                                                                                                                   |                         |                        |          |                     |                 |                                                                                                                                                       |          |                  |                      |

| Memory type:                                                                                                                                         | DDR3                    |                        |          |                     | 1               |                                                                                                                                                       |          |                  |                      |

| Manufacturer:                                                                                                                                        | Micron                  |                        |          | control bit setting | bit setting     |                                                                                                                                                       | Register |                  |                      |

| Memory part number:                                                                                                                                  | MT41J128M16HA-15        | MMDC Control Parameter | N/A      | (decimal)           | within register | Notes                                                                                                                                                 | name     | Register address | Register value (HEX) |

| Density of each DDR3 device                                                                                                                          | /                       |                        |          |                     |                 |                                                                                                                                                       |          |                  |                      |

| (Gb):                                                                                                                                                | 2                       | SDE_0                  | -        | 1                   | 80000000        | SDE_0: Enable Chip Select 0, set to 0 (disable) or 1 (enable)                                                                                         |          |                  |                      |

| Number of DRAM devices per<br>chip select                                                                                                            |                         | SDE_1                  | -        | 1                   | 4000000         | SDE_1: Enable Chip Select 1, set to 0 (disable) or 1 (enable)                                                                                         |          |                  |                      |

| Density per chip select (Gb)1:                                                                                                                       | 8                       | ROW                    | -        | 3                   | 03000000        | ROW: number of ROW addresses. NOTE: this value is taken<br>from the Device Information table above. Modify this value only<br>in the table above.     |          |                  |                      |

| Number of Chip Selects used <sup>2</sup><br>Total DRAM density (Gb)                                                                                  | 2                       | COL                    | -        | 1                   | 00100000        | COL number of Column addresses. NOTE: : this value is taken<br>from the Device Information table above. Modify this value only<br>in the table above. | MDCTL    | 0x021B0000       | 0xC31A0000           |

| Number of ROW Addresses <sup>2</sup>                                                                                                                 | 14                      | BL                     | -        | 1                   | 00080000        | BL: Burst length. For DDR3, set to 1 for burst length 8.                                                                                              |          |                  |                      |

| Number of COLUMN<br>Addresses <sup>2</sup>                                                                                                           | 10                      | DSIZ                   | -        | 2                   |                 | DSIZ: Data bus size. Note: this value is taken from the Device<br>Information table above. Modify this value only in the table<br>above.              |          |                  | $\setminus$          |

| Number of BANKS <sup>2</sup><br>Bus Width (input 16, 32, or 64<br>bits) <sup>2</sup><br>Clock Cycle Freq (MHz) <sup>3</sup><br>Clock Cycle Time (ns) | 8<br>64<br>533<br>1.876 | 2. Gets updat          | ed here  |                     | 1               | 3. Final r                                                                                                                                            | egiste   | r setting h      | nere                 |

| Device Information                                     |           | 1. ROW                 | . COL. E | Bus width           | are no          | w changed from above                                                                                                                     |          |                  |                      |

|--------------------------------------------------------|-----------|------------------------|----------|---------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------------------|

| Memory type:                                           | DDR3      |                        | ,        |                     |                 | in enteringe en renn enterie                                                                                                             |          |                  |                      |

| Manufacturer:                                          | someone   |                        |          | 1                   |                 |                                                                                                                                          | -        |                  |                      |

| Memory part number:                                    | something |                        |          | control bit setting | bit setting     |                                                                                                                                          | Register |                  |                      |

| Density of each DDR3 device<br>(Gb):                   | 2         | MMDC Control Parameter | N/A      | (decimal)           | within register |                                                                                                                                          | name     | Register address | Register value (HEX) |

| Number of DRAM devices per                             |           | SDE_0                  | -        | 1                   | 8000000         | SDE_0: Enable Chip Select 0, set to 0 (disable) or 1 (enable)                                                                            |          |                  |                      |

| chip select                                            | 4         | SDE_1                  | -        | 1                   | 4000000         | SDE_1: Enable Chip Select 1, set to 0 (disable) or 1 (enable)                                                                            |          |                  |                      |

| Density per chip select (Gb)1:                         | 8         | ROW                    | -        | 4                   | 04000000        | ROW: number of ROW addresses. NOTE: this value is taken<br>from the Device Information table above. Modify this value only               | 1        |                  |                      |

| Number of Chip Selects used <sup>2</sup>               | 2         | _                      |          |                     |                 | in the table above.                                                                                                                      | _        |                  |                      |

| Total DRAM density (Gb)                                | 16        | COL                    | -        | 2                   | 00200000        | COL number of Column addresses. NOTE: : this value is taken<br>from the Device Information table above. Modify this value only           | MDCTL    | 0x021B0000       | 0xC4290000           |

| Number of ROW Addresses <sup>2</sup>                   | 15        | 51                     |          |                     |                 | in the table above.                                                                                                                      | -        |                  |                      |

| Number of COLUMN                                       |           | BL                     | -        | 1                   |                 | BL: Burst length. For DDR3, set to 1 for burst length 8.                                                                                 | 1        |                  |                      |

| Addresses <sup>2</sup><br>Number of BANKS <sup>2</sup> |           | DSIZ                   | -        | 1                   | 00010000        | DSIZ: Data bus size. Note: this value is taken from the Device<br>Information table above. Modify this value only in the table<br>above. |          |                  |                      |

| Bus Width (input 16, 32, or 64 bits) <sup>2</sup>      | 32        |                        |          |                     | 1               | BTW, these cells                                                                                                                         |          |                  | , ,                  |

| Clock Cycle Freq (MHz) <sup>3</sup>                    | 533       | 2. Gets update         | ed here  |                     |                 | are automatically                                                                                                                        | updated  |                  | sly entered          |

| Clock Cycle Time (ns)                                  | 1.876     |                        |          |                     |                 |                                                                                                                                          | parame   | 51613            |                      |

PUBLIC 74

How To Use Register Configuration RealView .inc file

Another detailed look...

How To Use Register Configuration RealView .inc file

• Let's say on MX6DQ, you had only one chip select populated (CS0)

Before, the MX6DQ register was as follows for the validation board which has DDR3 on both chip selects

| MMDC Control Parameter | N/A | control bit setting<br>(decimal) | bit setting<br>within<br>register | Notes                                                                                                                                             | Register name | Register<br>address | Register<br>value (HEX) |

|------------------------|-----|----------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------|-------------------------|

| SDE_0                  | -   | 1                                | 80000000                          | SDE_0: Enable Chip Select 0, set to 0 (disable) or 1 (enable)                                                                                     |               |                     |                         |

| SDE_1                  | -   | 1                                | 4000000                           | SDE_1: Enable Chip Select 1, set to 0 (disable) or 1 (enable)                                                                                     |               |                     |                         |

| ROW                    |     | 3                                | 03000000                          | ROW: number of ROW addresses. NOTE: this value is taken<br>from the Device Information table above. Modify this value<br>only in the table above. |               |                     |                         |

| COL                    | -   | 1                                | 00100000                          | COL number of Column addresses. NOTE: : this value is taken from the Device Information table above. Modify this value only in the table above.   | MDCTL         | 0x021B0000          | 0xC31A0000              |

| BL                     | -   | 1                                | 00080000                          | BL: Burst length. For DDR3, set to 1 for burst length 8.                                                                                          |               |                     |                         |

| DSIZ                   | -   | 2                                | 00020000                          | DSIZ: Data bus size. Note: this value is taken from the Device<br>Information table above. Modify this value only in the table<br>above.          |               |                     |                         |

#### Now, after the change to enable CS0 only, here's what the register looks like

|                        |     | control bit setting |          |                                                                | Ň             | Register   | Register    |

|------------------------|-----|---------------------|----------|----------------------------------------------------------------|---------------|------------|-------------|

| MMDC Control Parameter | N/A | (decimal)           | register | Notes                                                          | Register name | address    | value (HEX) |

| SDE_0                  | -   | 1                   | 80000000 | SDE_0: Enable Chip Select 0, set to 0 (disable) or 1 (enable)  |               |            |             |

| SDE_1                  | -   | (0)                 | 00000000 | SDE_1: Enable Chip Select 1, set to 0 (disable) or 1 (enable)  |               |            |             |

|                        |     | 1                   |          | ROW: number of ROW addresses. NOTE: this value is taken        |               |            |             |

| ROW                    | -   | 3                   | 03000000 | from the Device Information table above. Modify this value     |               |            |             |

|                        |     |                     |          | only in the table above.                                       |               | <b>`</b> a |             |

|                        |     |                     |          | COL number of Column addresses. NOTE: : this value is          | MDCTL         | 0x021B0000 | 0x831A0000  |

| COL                    | - / | 1                   | 00100000 | taken from the Device Information table above. Modify this     | MDOTE         | 0.02100000 | 0,0017,0000 |

|                        |     |                     |          | value only in the table above.                                 |               |            | $\uparrow$  |

| BL                     | -   | 1 🗙                 | 00080000 | BL: Burst length. For DDR3, set to 1 for burst length 8.       |               |            |             |

|                        |     |                     |          | DSIZ: Data bus size. Note: this value is taken from the Device |               |            |             |

| DSIZ                   | - / | 2                   | 00020000 | Information table above. Modify this value only in the table   |               |            |             |

|                        |     |                     |          | above.                                                         |               |            |             |

Clearing this means we are not enabling chip select 1

Register setting gets automatically updated

Don't touch. When BL cleared, burst length is 4 which is setting for LPDDR2

PUBLIC 75

| // DDR Controller Regis                 |             |             |                                       |      |

|-----------------------------------------|-------------|-------------|---------------------------------------|------|

| // Manufacturer:                        | Micron      |             |                                       |      |

| // Device Part Number:                  |             |             |                                       |      |

| // Clock Freq.:                         | 200MHz      |             |                                       |      |

| // Density per CS (Gb):                 | LUUINIL     |             | • DI                                  | ٦ΛΙ  |

| // Chip Selects:                        | 1           |             | • DI                                  | ١AI  |

| // Number of Banks:                     | 4           |             |                                       |      |

| // Row address:                         | 14          |             | 14-                                   |      |