# i.MX6UL Low Power Consumption Application

The power-down mode power consumption is very important for i.MX6UL VDD\_SNVS\_IN battery powered applications. To get an idea power consumption figure, the following items shall be well considered in system design:

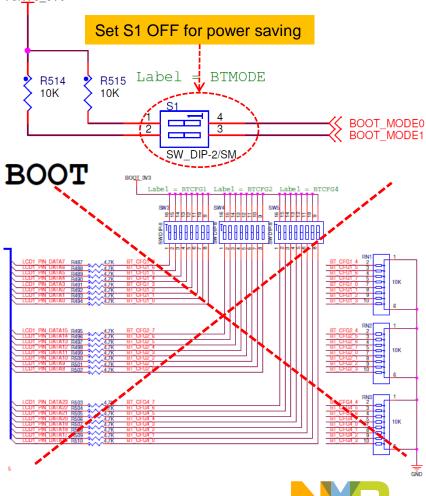

- □ BOOT\_MODE[1:0] pins connection.

- □ POR\_B and SNVS\_PMIC\_ON\_REQ pins connection.

- **Tamper pins connection.**

# i.MX6UL BOOT\_MODE[1:0] Pins Connection

- 1) There are  $100K\Omega$  pull-down resistors on BOOT\_MODE[1:0] pins internally.

- 2) If set BOOT\_MODE[1:0] = 01 for Serial Downloader, or set BOOT\_MODE[1:0] = 10 for Internal Boot with the external  $10K\Omega$ resistor pulled up to VDD\_SNVS\_IN (VSNVS\_3V0), it will cause around [3.0V / ( $100K\Omega + 10K\Omega$ ) = 27uA] consumption current from VDD\_SNVS\_IN (VSNVS\_3V0).

- In system power-down mode, VDD\_SNVS\_IN (VSNVS\_3V0) is powered from battery. 27uA consumption current from the battery is too large. To reduce it, it is better to set BOOT\_MODE[1:0] = 00 for Boot From Fuses.

- 4) While the system boots from Fuses, the external bootstraps on LCD IF could be removed to optimize the PCB layout.

### Table 95. 14x14 mm Functional Contact Assignments

| Ball Name  | 14x14<br>Ball | Power<br>Group | Ball<br>Type | Out of Reset Condition |                     |                  |                     |

|------------|---------------|----------------|--------------|------------------------|---------------------|------------------|---------------------|

|            |               |                |              | Default<br>Mode        | Default<br>Function | Input/<br>Output | Value               |

| BOOT_MODE0 | T10           | VDD_SNVS_IN    | GPIO         | ALT5                   | BOOT_MODE0          | Input            | 100 kΩ<br>pull-down |

| BOOT_MODE1 | U10           | VDD_SNVS_IN    | GPIO         | ALT5                   | BOOT_MODE1          | Input            | 100 kΩ<br>pull-down |

VSNVS\_3V0

### i.MX6UL POR\_B and SNVS\_PMIC\_ON\_REQ Pins Connection

- 1) There are 100KΩ resistors pulled up to VDD\_SNVS\_IN on POR\_B and SNVS\_PMIC\_ON\_REQ pins internally.

- 2) In system power-down mode, VDD\_SNVS\_IN is powered from battery.

- To prevent power leakage from the battery in system power-down mode, external POR\_B shall be open drain output, and SNVS\_PMIC\_ON\_REQ shall be connected to high impedance input.

| Table 95. 14x14 mm Functional Contact Assignments |                  |               |             |              |                        |                     |                  |                   |  |  |  |  |  |

|---------------------------------------------------|------------------|---------------|-------------|--------------|------------------------|---------------------|------------------|-------------------|--|--|--|--|--|

|                                                   | Ball Name        | 14x14<br>Ball | Power       | Ball<br>Type | Out of Reset Condition |                     |                  |                   |  |  |  |  |  |

|                                                   |                  |               | Group       |              | Default<br>Mode        | Default<br>Function | Input/<br>Output | Value             |  |  |  |  |  |

|                                                   | POR_B            | P8            | VDD_SNVS_IN | GPIO         | ALT0                   | POR_B               | Input            | 100 kΩ<br>pull-up |  |  |  |  |  |

|                                                   | SNVS_PMIC_ON_REQ | Т9            | VDD_SNVS_IN | GPIO         | ALTO                   | SNVS_PMIC_ON_REQ    | Output           | 100 kΩ<br>pull-up |  |  |  |  |  |

#### POR B R512 1.5K 1% R511\_ R501\_ 0 DNP **⊾**1K DCDC\_3V3 U501 UM803RS<sup>65</sup> 202 # Open Drair C503 DNP C501 2 =0.1uF RESET 0.1uF 25V GND 0402 CC 25V 0402 CC -**Open Drain Output** GÑD GÑD GÑD L701 # 2.5V-to-5.5V 2 VIN vsys-SW 1uH C711 C712 C713 OUT R717 :10uF :10uF 0.1uF 10V R716 U703 180K 10V 25V 0603 CC 0603 CC 0402 CC 100K 1% DNP MP2144GJ GND 7 Vfb=0.6V FB 10K 8 R733, PMIC\_ON\_REQ >> EN # R1/R2 = 9/2 C737 PGND 0.22UF 6 AGND 10V R718 # PG pin is pulled up to 40.2K 0402 cc VIN by the internal 1% GND **High Impedance Input** GND resistor 500K OHM

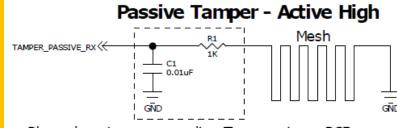

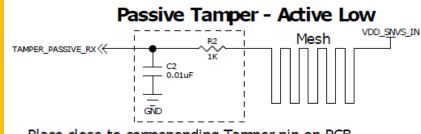

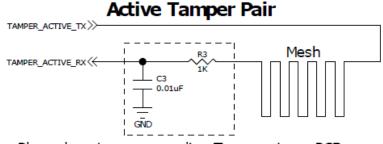

### i.MX6UL Tamper Pins Connection

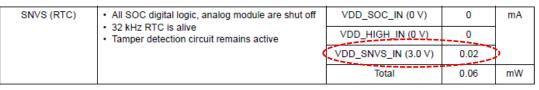

- 1) In system power-down mode, VDD\_SNVS\_IN is powered from battery.

- 2) When system is power-down, the only consumption current from VDD\_SNVS\_IN is around 20uA with Tamper detections disabled.

- When system is power-down, the only consumption current from VDD\_SNVS\_IN is around 22uA - 23uA with all Passive Tamper and/or Active Tamper detections enabled.

- 4) When Tamper detection is enabled and tamper input pin is left floating (attack detected), it will cause 50uA – 60uA consumption current on each tamper input because they are high impedance input and are high sensitive to noises.

- 5) Since the Mesh traces connected to tamper input s are very long, this makes them induce high noises on the corresponding pins sensitively.

- 6) To reduce the consumption current when attack detected and improve the system EMC immunity, RC filters shall be added on tamper detection inputs and they shall be placed close to the corresponding tamper pins on the PCB.

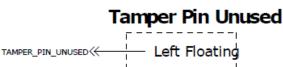

- 7) For i.MX6UL G3 chip, all tamper pins are fused as tamper detection function, they can not be reassigned as GPIOs. For unused tamper pins, they can be just left floating.

### Table 15. Low Power Mode Current and Power Consumption (continued)

Place close to corresponding Tamper pin on PCB

Place close to corresponding Tamper pin on PCB

# SECURE CONNECTIONS FOR A SMARTER WORLD