Document Number: MQXBSPEXUG Rev. 1, 11/2014

# Freescale MQX<sup>™</sup> RTOS BSP Porting Example User's Guide

| PRODUCT:         | Freescale MQX™ RTOS                    |

|------------------|----------------------------------------|

| PRODUCT VERSION: | 4.2.0                                  |

| DESCRIPTION:     | Freescale MQX RTOS BSP Porting Example |

| RELEASE DATE:    | November, 2014                         |

© 2014 Freescale Semiconductor, Inc. All rights reserved.

#### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions

Freescale , the Freescale logo, Kinetis, Processor Expert, and CodeWarrior are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Tower is a trademark of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. ARM, ARM Powered logo, and Cortex are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. © 2008-2014 Freescale Semiconductor, Inc. All rights reserved.

# **Table of Contents**

| 1 Introduction                                                             | 2  |

|----------------------------------------------------------------------------|----|

| 2 Example                                                                  | 2  |

| 3 Cloning the BSP                                                          | 3  |

| 4 Using Processor Expert (PEx) in the BSP                                  | 3  |

| 4.1 Setting up BSP for PEx with IAR EW-ARM                                 |    |

| 5 Changing MCU derivative in MQX projects                                  | 15 |

| 5.1 Changing the PEx Package                                               |    |

| 5.2 Changing the PEx CPU Component.                                        |    |

| 5.3 Specify MCU derivative in MQX<br>5.4 Modifying Driver Derivative Files |    |

| 6 Clock Configuration                                                      |    |

| 6.1 Changing Clock Configuration with PEx                                  |    |

| 6.2 Changing Clock Configuration without PEx                               | 26 |

| 7 BSP include files                                                        | 27 |

| 7.1 <board_name>.h File</board_name>                                       |    |

| 7.2 BSP.h                                                                  |    |

| 7.3 user_config.h                                                          |    |

| 8 BSP Initialization files                                                 |    |

| 8.1 init_bsp.c<br>8.2 init HW.c                                            |    |

| 8.3 init_GPIO.c                                                            |    |

| 8.4 bsp_cm.c                                                               | 34 |

| 9 BSP Driver Changes                                                       | 34 |

| 9.1 init_enet.c                                                            |    |

| 9.2 init_flashx.c<br>9.3 init_SAI.c                                        |    |

| 9.4 init_SCI.c                                                             |    |

| 9.5 Remove Driver Source files from BSP Project                            |    |

| 9.6 Add Driver source files to BSP                                         |    |

| 10 BSP Memory Map and Linker files                                         |    |

| 10.1 CodeWarrior GCC Linker File<br>10.2 CodeWarrior Freescale Linker File |    |

| 10.3 IAR EW-ARM Linker File                                                |    |

| 10.4 Keil uVision Linker File                                              |    |

| 11 Post-Link Batch Files                                                   | 39 |

| 12 CodeWarrior Debugger Memory File                                        | 40 |

| 13 Porting Example Applications                                            | 40 |

| 13.1 Testing CustomBSP                                                     | 41 |

| 14 Conclusion                                                              | 41 |

# 1 Introduction

This document uses a specific example with detailed steps for porting a BSP to a different board and follows the porting process outlined in the *Freescale MQX<sup>TM</sup> RTOS BSP Porting Guide* (document MQXBSPPG).

# 2 Example

First, TWR-K60D100M BSP is ported to a different development board TWR-K40D100M. While MQX RTOS already includes a BSP for the TWR-K40D100M board, this guide provides the detailed steps for that BSP port. The example ports to a different Freescale Kinetis MCU derivative: from a 100 MHz K60 to a 100M Hz K40. While these derivatives are similar, there are several differences between the derivatives and the boards which require the following changes in the ported BSP:

- Different Peripherals

- o K60 includes an Ethernet MAC peripheral, the K40 does not

- The K40 has a Segment LCD peripheral, the K60 does not

- Different memory map and sizes

- $\circ$  The K60 has 512 KB of Program Flash, this K40 has 256 KB

- $\circ$  The K60 has 128 KB of system SRAM, this K40 has 64 KB

- The K40 includes FlexMemory with 256 KB of FlexNVM, this K60 has no FlexMemory

- Different drivers and driver configurations

- Different UART peripherals are used for the RS-232 communication of the board

- Low-power settings for UARTs with LPM driver are different because the different UARTs are used

- Different pins

- GPIO pins used for:

- LEDs

- Input switches

- USB regulator enable

- Accelerometer IRQ

- SD Card socket

- $\circ$  UART Tx and Rx, and hardware flow control pins

- o I2C pins

- o SAI (I2S)

- o FlexBus

- Different clock setup

- The clock source on the K60 board is a 50 MHz external oscillator, the K40 board uses a 8 MHz crystal

- The K60 BSP uses a PLL output of 96 MHz, the customized K40 BSP uses a PLL output of 48 MHz to show implications of this change including the USB clock divider

In this porting example, the name of the customized ported BSP is **CustomBSP**. The example was done with Freescale MQX RTOS version 4.0.2, using the tool chain releases specified in the MQX RTOS Release Notes for CodeWarrior for Microcontrollers, IAR Embedded Workbench<sup>®</sup> for ARM<sup>®</sup>, Freescale MQX<sup>™</sup> RTOS BSP Porting Guide, Rev. 1, 11/2014

and MDK-ARM Keil<sup>™</sup>. In the porting example, only the Debug build configurations are modified and tested. The Release build configurations can be modified with the same porting steps. The example software MQXPORTEXSW.zip is available at freescale.com.

# 3 Cloning the BSP

For the Kinetis derivative MK40DX256VMD10, this example starts with the TWR-K60D100M MQX BSP provided in the MQX release. Cloning is done with the BSP Cloning Wizard. The name for the new clone is **CustomBSP** and the board base to clone is TWR-K60D100M. These steps modify **CustomBSP** to port it to the TWR-K40D100M board.

| 👹 MQX BSP             | Clone Wizard  |  |  |

|-----------------------|---------------|--|--|

| MQX BSP Clone Wizard  |               |  |  |

| Clone MQX BSP Project |               |  |  |

| Name:                 | CustomBSP     |  |  |

| MQX Base:             | MQX 4.0.2 -   |  |  |

| Board Base:           | twrk60d100m 👻 |  |  |

|                       |               |  |  |

|                       |               |  |  |

|                       | Finish Cancel |  |  |

|                       |               |  |  |

#### Figure-1 BSP Cloning Wizard Settings

# 4 Using Processor Expert (PEx) in the BSP

Using PEx in the MQX BSP is optional. This section explains how to add PEx into a BSP project for IAR or Keil. The CodeWarrior projects for the Kinetis MQX BSPs already include PEx support. The projects are released with the PEx components included, but the PEx source code is not generated. Building the projects as released does not use PEx. However, the PEx code can be easily generated within the project and no user integration is required to include PEx in the BSP. Skip to Section Changing the PEx Package to use PEx in a CodeWarrior BSP project.

# 4.1 Setting up BSP for PEx with IAR EW-ARM

Since MQX RTOS version 4.0.2, the BSP project did not include PEx support. These steps show how to use the PEx Driver Suite and add PEx support to the BSP.

#### 4.1.1 Adding PEx Driver Suite Project

- 1. In PEx, create a new PEx project using the menu File->New->Processor Expert Project

- 2. Name the project the same name as the BSP project, in this case bsp\_CustomBSP

- 3. Do not use the default location. Instead, create the project in the BSP project directory for IAR, in this case \mqx\build\iar\bsp\_CustomBSP. Note that the tool defaults to creating a subdirectory under bsp\_CustomBSP with the same name. Be sure to correct the path so that the PEx project is created in the same directory as the IAR project. The warning caused by this is OK.

| New Proo | cessor Expert Project                                                                         |

|----------|-----------------------------------------------------------------------------------------------|

|          | rocessor Expert Project<br>e location for the new project                                     |

| -        | me: bsp_CustomBSP                                                                             |

|          | C:\Freescale\Freescale_MQX_4_0\mqx\build\iar\bsp_CustomBSP Browse Choose file system: default |

|          |                                                                                               |

| ?        | < <u>B</u> ack <u>N</u> ext > <u>Finish</u> Cancel                                            |

#### Figure-2 New PEx BSP Project

- 4. Select the device for the original BSP, in this case MK60DN512xxx10. This device is changed later.

- 5. Choose desired perspective. If unsure, use current perspective.

- 6. Select the IAR compiler and Finish.

#### 4.1.2 Re-Use the PEx settings from CodeWarrior project

The CodeWarrior BSP project already has the CPU component setup for the cloned BSP. It's easiest to re-use that setup, and then modify as desired.

- 7. In PEx, close the **bsp\_CustomBSP** project, by right-clicking on the project and select **Close Project**.

- 8. Copy the ProcessorExpert.pe file from the CodeWarrior BSP project directory to the IAR BSP project directory, overriding the file just created in the new project. In this case copy:

\mqx\build\cw10\bsp\_CustomBSP\ProcessorExpert.pe

to

\mqx\build\iar\bsp\_CustomBSP\ProcessorExpert.pe

- 9. Re-open the project in PEx by right-clicking the project and selecting **Open Project**.

- 10. Eclipse may give an error, such as **Resource is out of sync with the file system**. Rightclick the project and click **Refresh**.

- 11. Copying the CodeWarrior file changed the compiler settings. To change it back, select the CPU component in the Components View. In the Component Inspector, select the **Build options** tab. Change the Compiler to IAR.

| Properties Methods Events Build options Resources |                               |         |  |

|---------------------------------------------------|-------------------------------|---------|--|

| Name                                              | Value                         | Details |  |

| Compiler                                          | IAR ARM C Compiler            |         |  |

|                                                   | One handler for all           |         |  |

| Unhandled int code                                | 2 line(s) Select to view/edit |         |  |

| FLASH registers initialization                    | Enabled                       |         |  |

| Juser initialization                              |                               |         |  |

| User data declarations                            | 0 line(s) Select to view/edit |         |  |

| User code before PE initializat                   | 0 line(s) Select to view/edit |         |  |

| User code after PE initializatio                  | 0 line(s) Select to view/edit |         |  |

| Generate ICF file                                 | no                            |         |  |

Figure-3 Change compiler in PEx to IAR

#### 4.1.3 Generate the PEx code for the BSP

- 12. The file **ProcessorExpert.c** in the sources folder conflicts with MQX RTOS. Remove it from the project by right-clicking on it and selecting **Delete**.

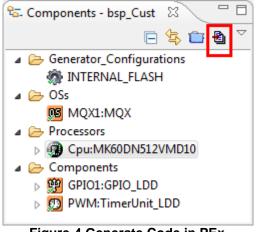

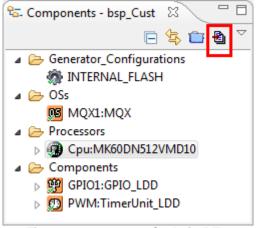

- 13. Click the Generate Code button.

Figure-4 Generate Code in PEx

#### 4.1.4 Update the IAR BSP project to use PEx

IAR has a feature called Project Connection that allows IAR to import an XML file from PEx with most of the project settings. However, as of EWARM v6.50.2, there are still several things to manually change in the project.

- 14. Open the custom BSP workspace in IAR, in this case \build\CustomBSP\iar\build\_libs.eww

- 15. Be sure that the BSP project is the active project. If not bold, right-click on the project and select **Set as Active**.

- 16. Enable Project Connections in IAR. Use the menu **Tools->Options**. Check the box **Enable Project Connects** in the project options. Click **OK** to save.

| IDE Options                                                                                                           |                                                                                                                                                                                                                                                                                                                                | ×                                 |

|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Common Fonts<br>Key Bindings<br>Language<br>Editor<br>Messages<br>Project<br>Source Code Control<br>Debugger<br>Stack | Stop build operation on:<br>Save editor windows before building:<br>Save workspace and projects before<br>building:<br>Make before debugging:<br>Reload last workspace at startup<br>Play a sound after build operations<br>Generate browse information<br>No source browser and build status up<br>Plable project connections | Never Always Always Always Always |

|                                                                                                                       |                                                                                                                                                                                                                                                                                                                                | OK Cancel Apply Help              |

Figure-5 Enable Project Connections in IAR

- 17. Add a connection to PEx using the menu **Project->Add Project Connection**.

- 18. Connect using Freescale Processor Expert.

- Browse to the ProjectInfo.xml file generated by PEx. In this case, \mqx\build\iar\bsp\_CustomBSP\ProjectInfo.xml. Click Open. This has added the source files from PEx and the compiler paths to the project.

- 20. Update compiler search path ordering. PEx adds definitions and functions already included in the BSP, so it is important to set up the toolchain to use the PEx generated code instead of the existing files. Right-click the BSP project and select **Options**. The project connection has already added the two paths below in the **C/C++Compiler->Preprocessor settings**. They need to be moved to the top of the include directories to ensure that the compiler finds the PEx headers first:

\mqx\build\iar\bsp\_CustomBSP\Sources\

\mqx\build\iar\bsp\_CustomBSP\Generated\_Code\

| Options for node "bsp_0                                                                                         | CustomBSP"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Category:<br>General Options<br>C/C++ Compiler<br>Assembler<br>Custom Build<br>Build Actions<br>Library Builder | Factory Settings         Multi-file Compilation         Discard Unused Publics         Language 2       Code         Optimizations       Output         Ignore standard include directories         Additional include directories:         (one per line)         x/build/var/bsp_CustomBSP//.//mqx/source/psp/cortex_m/cpu         x/build/var/bsp_CustomBSP//.//mqx/source/psp/cortex_m/core         Preinclude file:            Defined symbols: (one per line) |

|                                                                                                                 | OK Cancel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Figure-6 IAR BSP Preprocessor Setting Changes

#### 4.1.5 Update IAR BSP Batch File for PEx

MQX RTOS uses batch files to copy the header files required by the applications to the **lib** folder. The BSP batch file needs to be updated to copy the PEx files to the lib folder. The code from the CodeWarrior section can be re-used.

- 21. Edit the BSP batch file, in this case \mqx\build\bat\bsp\_CustomBSP.bat. Note that in Windows, double-clicking on the batch file executes it. To edit it, right-click and select Edit.

- 22. Find the CodeWarrior section under the **label :tool\_cw10**. Find the lines related to **%OUTPUTDIR%\Generated\_Code and %OUTPUTDIR%\Sources** and copy those lines.

- 23. Find the IAR section under the **label :tool\_iar**. Paste the lines from above at the top of this section.

- 24. Modify the paths. Replace cw10 with iar. Modify the filenames of the linker files. In this example, the modified IAR section looks like this:

```

:tool_iar

IF NOT EXIST %OUTPUTDIR%\Generated_Code mkdir %OUTPUTDIR%\Generated_Code

for /R %MQXROOTDIR%\mqx\build\iar\bsp_CustomBSP\Generated_Code %%f in (*.h) do copy %%f

%OUTPUTDIR%\Generated_Code\

IF NOT EXIST %OUTPUTDIR%\Sources mkdir %OUTPUTDIR%\Sources

for /R %MQXROOTDIR%\mqx\build\iar\bsp_CustomBSP\Sources %%f in (*.h) do copy %%f

%OUTPUTDIR%\Sources\

copy %MQXROOTDIR%\mqx\source\bsp\CustomBSP\iar\intflash.icf %OUTPUTDIR%\intflash.icf /Y

copy %MQXROOTDIR%\mqx\source\bsp\CustomBSP\iar\ram.icf %OUTPUTDIR%\ram.icf /Y

goto copy_end

```

25. Save the batch file.

# 4.1.6 Build the MQX Libraries

Test the changes are correct by building all MQX libraries for the **CustomBSP**. Freescale MQX™ RTOS BSP Porting Guide, Rev. 1, 11/2014

- 26. If the BSP project has already been built, it may need to be cleaned for the changes to take effect. Right-click the BSP project and select **Clean**.

- 27. Build the workspace using the menu **Project->Batch Build**. Select **Debug**, and hit the **Make** button. There should be no errors in these project builds.

- 28. Verify that the PEx headers are included in the **lib** folder for the applications. **Events.h** should be in the sources directory below, and there should be several files in the **Generated\_Code** directory. If these files are missing, check the batch file, save it, clean the BSP, and rebuild it. In this case, the lib paths are: **\lib\CustomBSP.iar\debug\bsp\Generated\_Code \lib\CustomBSP.iar\debug\bsp\Sources**

#### 4.1.7 Test PEx changes with pe\_demo

MQX RTOS provides an application demo to work with PEx in the BSP. These modifications to the BSP can be tested using the **pe\_demo** application. At this point, the MCU derivative has not been changed from the original BSP. Therefore, the **pe\_demo** can be run on the board associated with the original BSP to test it, in this case the TWR-K60D100M board.

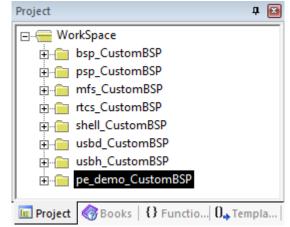

29. Add the **pe\_demo** project to the IAR workspace. Use menu **Project->Add Existing Project**. Browse to the **pe\_demo** project for the custom BSP, in this case \demo\pe\_demo\iar\pe\_demo\_CustomBSP\pe\_demo\_CustomBSP.ewp. Click Open.

| Workspace                                    |     | ×  |

|----------------------------------------------|-----|----|

| pe_demo_CustomBSP - Int Flash Debug          |     | •  |

| Files                                        | 23  | D: |

| 🖻 🖸 build_libs                               |     |    |

| – 🕀 🗇 bsp_CustomBSP - Debug                  | ~   |    |

| ├─⊞ 🗇 pe_demo_CustomBSP - Int Flash Debug    | ¥ . |    |

| –⊕ 🗇 psp_CustomBSP - Debug                   | ×   |    |

| ├─⊞ 🗇 rtcs_CustomBSP - Debug                 | ×   |    |

| –⊞ 🗇 mfs_CustomBSP - Debug                   | ¥   |    |

| ├─⊞ 🗇 shell_CustomBSP - Debug                | ¥   |    |

| ├── 🗇 usbd_CustomBSP - Debug                 | ¥   |    |

| └─⊞ 🗇 usbh_CustomBSP - Debug                 | ~   |    |

| Figure-7 pe_demo project added to IAR worksp | ace |    |

30. Add PEx header paths. The applications need two paths added that point to header files located in the PEx Driver Suite installation. These two paths are already included in the BSP project settings from the Project Connection. Copy the two paths below from the BSP project and add to the **pe\_demo** project settings in **C/C++Compiler->Preprocessor**, at the top of the list. Click **OK** to save.

<PEx Driver Suite Installation>\eclipse\ProcessorExpert\lib\Kinetis\iofiles\ <PEx Driver Suite Installation>\eclipse\ProcessorExpert\lib\Kinetis\pdd\inc\

| Options for node "pe_de                                                                                                                                                                                                                                                                                                        | mo_CustomBSP"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Category:<br>General Options<br>C/C++ Compiler<br>Assembler<br>Output Converter<br>Custom Build<br>Build Actions<br>Linker<br>Debugger<br>Simulator<br>Angel<br>GDB Server<br>IAR ROM-monitor<br>I-jet/JTAGjet<br>J-Link/J-Trace<br>TI Stellaris<br>Macraigor<br>PE micro<br>RDI<br>ST-LINK<br>Third-Party Driver<br>TI XDS100 | Factory Settings         Multi-file Compilation         Discard Unused Publics         Language 2       Code       Optimizations       Output       List       Preprocessor         Ignore standard include directories         Additional include directories: (one per line)         Freescale VPExDry v10.2/eclipse VProcessorExpert Vib VKinetis Vofiles \         You Jol Rs//.//.ib/Custom BSP.iar/debug/psp         You Jol Rs////.ib/Custom BSP.iar/debug/psp         You Jol Rs////.ib/Custom BSP.iar/debug/psp         You Jol Rs////.ib/Custom BSP.iar/debug/psp         You Jol Rs/ |

|                                                                                                                                                                                                                                                                                                                                | OK Cancel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

#### Figure-8 PEx paths added to pe\_demo in IAR

- 31. Build the **pe\_demo** project. There should be no errors.

- 32. Download and test **pe\_demo** on the board for the original BSP, in this case TWR-K60D100M board.

# 4.2 Setting up BSP for PEx with Keil µVision<sup>®</sup>

As of MQX RTOS version 4.0.2, the BSP project did not include PEx support. These steps show how to use the PEx Driver Suite and add PEx support to the BSP.

# 4.2.1 Adding PEx Driver Suite Project

- 1. In PEx, create a new PEx project using the menu File->New->Processor Expert Project

- 2. Name the project the same name as the BSP project, in this case bsp\_CustomBSP

- Do not use the default location, instead create the project in the BSP project directory for Keil, in this case \mqx\build\uv4\bsp\_CustomBSP. NOTE: the tool will default to creating a subdirectory under bsp\_CustomBSP with the same name. Be sure to correct the path so the PEx project is created in the same directory as the Keil project. The warning caused by this is OK.

| New Proc         | cessor Expert Project                                                                                                                   |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

|                  | rocessor Expert Project<br>e location for the new project                                                                               |

| Use de Location: | me: bsp_CustomBSP<br>fault location<br>C:\Freescale\Freescale_MQX_4_0\mqx\build\uv4\bsp_CustomBSP Browse<br>Choose file system: default |

| ?                | < <u>B</u> ack <u>N</u> ext > <u>F</u> inish Cancel                                                                                     |

Figure-9 New PEx BSP Project for Keil

- 4. Select the device for the original BSP, in this case MK60DN512xxx10. This device will be changed later.

- 5. Choose desired perspective, if unsure, use current perspective.

- 6. Select the Keil compiler and Finish.

#### 4.2.2 Re-Use the PEx settings from CodeWarrior project

The CodeWarrior BSP project already has the CPU component setup for the cloned BSP. It's easiest to re-use that setup, and then modify as desired.

- 7. In PEx, close the **bsp\_CustomBSP** project, by right-clicking on the project and select **Close Project**.

- 8. Copy the **ProcessorExpert.pe** file from the CodeWarrior BSP project directory to the Keil BSP project directory overriding the file just created in the new project. In this case copy:

# \mqx\build\cw10\bsp\_CustomBSP\ProcessorExpert.pe to

#### \mqx\build\uv4\bsp\_CustomBSP\ProcessorExpert.pe

- 9. Re-open the project in PEx by right-clicking the project and selecting **Open Project**.

- 10. Eclipse may give an error, such as **Resource is out of sync with the file system**. Rightclick the project and click **Refresh**.

- 11. Copying the CodeWarrior file changed the compiler settings. To change it back, select the CPU component in the Components View. In the Component Inspector, select the **Build options** tab. Change the compiler to Keil.

| 📎 *Component Inspector - Cpu 🖂     |                                                   |  |  |  |

|------------------------------------|---------------------------------------------------|--|--|--|

|                                    | Basic Advanced Expert 🚹 🗸                         |  |  |  |

| Properties Methods Events Build or | Properties Methods Events Build options Resources |  |  |  |

| Name                               | Value                                             |  |  |  |

| Compiler                           | Keil ARM C/C++ Compiler                           |  |  |  |

| Unhandled vectors                  | One handler for all                               |  |  |  |

| Unhandled int code                 | 2 line(s) Select to view/edit                     |  |  |  |

| User initialization                |                                                   |  |  |  |

| User data declarations             | 0 line(s) Select to view/edit                     |  |  |  |

| User code before PE initializat    | 0 line(s) Select to view/edit                     |  |  |  |

| User code after PE initializatio   | 0 line(s) Select to view/edit                     |  |  |  |

| ⊿ Startup                          |                                                   |  |  |  |

| Add startup file                   | yes                                               |  |  |  |

| Generate SCF file                  | no                                                |  |  |  |

| <                                  | •                                                 |  |  |  |

Figure-10 Change compiler in PEx to Keil

#### 4.2.3 Generate the PEx code for the BSP

- 12. The file **ProcessorExpert.c** in the Sources folder conflicts with MQX RTOS. Remove it from the project by right-clicking on it, and select **Delete**.

- 13. Click the **Generate Code** button.

Figure-11 Generate Code in PEx

#### 4.2.4 Update the Keil BSP project to use PEx

- 14. Open the custom BSP workspace in Keil, in this case \build\CustomBSP\uv4\build\_libs.uvmpw

- 15. Be sure that the BSP project is the active project. If not highlighted, right-click on the project and select **Set as Active Project**.

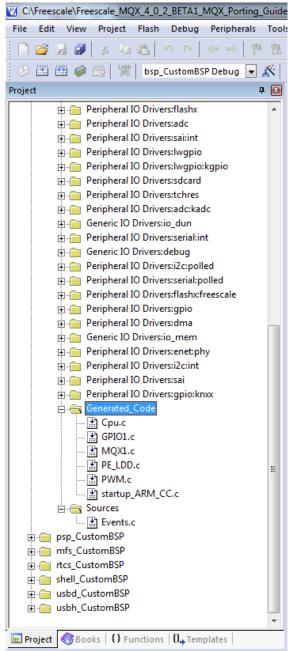

- 16. Add the PEx source files to the BSP project. Right-click the build configuration bsp\_CustomBSP Debug and select Add Group. Find New Group added to the bottom of the list of groups in the project. Rename it by selecting, hit F2, and rename to Generated\_Code. Right-click on Generated\_Code group and select Add files to group Generated\_Code. Navigate to the PEx Generated\_Code directory, in this case \mqx\build\uv4\bsp\_CustomBSP\Generated\_Code. Add all source files in this directory.

17. Navigate to the directory

\mqx\build\uv4\bsp\_CustomBSP\Project\_Settings\Startup\_Code and add the source file startup\_ARM\_CC.c. Then click the Close button.

18. Repeat the steps above to add the group Sources, and add the file **Events.c** in the directory \mqx\build\uv4\bsp\_CustomBSP\Sources.

Figure-12 PEx source files added to Keil BSP project

- 19. Open the **ProjectInfo.xmI** file. PEx generates an XML file with the files and paths used by PEx to be added to the tool chain project. For Keil, it can be a useful reference to find the paths required. In this case, use a text editor to open the file \mqx\build\uv4\bsp\_CustomBSP\ProjectInfo.xmI.

- 20. Copy the PEx include paths. There are two paths used by PEx header files. These paths need to be added to the compiler include paths. In **ProjectInfo.xml**, find these two include

paths:

#### <PEx Driver Suite Installation>\eclipse\ProcessorExpert\lib\Kinetis\iofiles\ <PEx Driver Suite Installation>\eclipse\ProcessorExpert\lib\Kinetis\pdd\inc\

- 21. Modify the Keil compiler include paths. In Keil, open the options for the BSP project. Right-click the build configuration bsp\_CustomBSP Debug, select Options for bsp\_CustomBSP. Click the C/C++ tab. Place the cursor at the beginning of the Include Paths field. Copy and paste the two paths in the step above from the XML file into the include paths in Keil. Place a semicolon after each path. NOTE: be sure that these paths contain no spaces.

- 22. Add the PEx generated header file paths to the project. After the include paths added in the step above, add these include paths with semicolons after each path. In this case, the four paths to copy to the Include Paths field are like this:

C:\Freescale\PExDrv\_v10.2\eclipse\ProcessorExpert\lib\Kinetis\iofiles\;C:\Freescale\P ExDrv\_v10.2\eclipse\ProcessorExpert\lib\Kinetis\pdd\inc\;.\Generated\_Code;.\ Sources;

23. Verify the include paths. Click the browse button to the right of the Include Paths field. The PEx paths should be first in the list, similar to this image:

| Folder Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             | 2 | X          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---|------------|

| Setup Compiler Include Paths:                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>*</b> ") | × | <b>↓</b> ↓ |

| C:\Freescale\PExDrv_v10.2\eclipse\ProcessorExpert\lib\Kinetis\iofiles\<br>C:\Freescale\PExDrv_v10.2\eclipse\ProcessorExpert\lib\Kinetis\pdd\inc\<br>.\Generated_Code<br>.\Sources<br>///mqx/source/io/adc/kadc<br>///mqx/source/io/flashx/freescale<br>///mqx/source/io/adc<br>///mqx/source/io/pm<br>///mqx/source/io/serial<br>///mqx/source/io/pcb<br>///mqx/source/io/i2c/polled<br>///mqx/source/io/pipe<br>///mqx/source/io/pipe<br>///mqx/source/psp/cortex_m |             |   | * III *    |

| OK Cancel                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |   |            |

Figure-13 PEx include paths added to Keil

24. Click the **OK** button twice to save the project settings.

# 4.2.5 Update Keil BSP Batch File for PEx

MQX RTOS uses batch files to copy the header files required by the applications to the **lib** folder. The BSP batch file needs to be updated to copy the PEx files to the lib folder. The code from the CodeWarrior section can be re-used.

- 25. Edit the BSP batch file, in this case **\mqx\build\bat\bsp\_CustomBSP.bat**. Note that in Windows double-clicking on the batch file executes it. To edit it, right-click and select **Edit**.

- 26. Find the CodeWarrior section under the **label :tool\_cw10**. Find the lines related to **%OUTPUTDIR%\Generated\_Code and %OUTPUTDIR%\Sources**, and copy those lines.

- 27. Find the Keil section under the **label :tool\_uv4**. Paste the lines from above at the top of this section.

28. Modify the paths. Replace cw10 with uv4. Modify the filenames of the linker files. In this example, the modified Keil section looks like this:

```

:tool_uv4

IF NOT EXIST %OUTPUTDIR%\Generated_Code mkdir %OUTPUTDIR%\Generated_Code

for /R %MQXROOTDIR%\mqx\build\uv4\bsp_CustomBSP\Generated_Code %%f in (*.h) do copy %%f

%OUTPUTDIR%\Generated_Code\

IF NOT EXIST %OUTPUTDIR%\Sources mkdir %OUTPUTDIR%\Sources

for /R %MQXROOTDIR%\mqx\build\uv4\bsp_CustomBSP\Sources %%f in (*.h) do copy %%f

%OUTPUTDIR%\Sources\

copy %MQXROOTDIR%\mqx\source\bsp\CustomBSP\uv4\intflash.scf %OUTPUTDIR%\intflash.scf /Y

goto copy_end

```

29. Save the batch file.

#### 4.2.6 Build the MQX Libraries

Test the changes are correct by building all MQX libraries for the CustomBSP.

- 30. If the BSP project has already been built, it may need to be cleaned for the changes to take effect. Use the menu **Project->Clean bsp\_CustomBSP(bsp\_CustomBSP Debug)**.

- 31. Build the workspace using the menu **Project->Batch Build**. In this case, only the Debug build targets need to be built.

- 32. Verify the PEx headers are included in the lib folder for the applications. Events.h should be in the Sources directory, and there should be several files in the Generated\_Code directory. If these files are missing, check the batch file, save it, clean the BSP, and rebuild it. In this case, the lib paths are:

\lib\CustomBSP.uv4\debug\bsp\Generated\_Code

\lib\CustomBSP.uv4\debug\bsp\Sources

#### 4.2.7 Test PEx changes with pe\_demo

MQX RTOS provides an application demo to work with PEx in the BSP. These modifications to the BSP can be tested using the **pe\_demo** application. At this point, the MCU derivative has not been changed from the original BSP. Therefore, the **pe\_demo** can run on the board associated with the original BSP to test it, in this case the TWR-K60D100M board.

33. Add the pe\_demo project to the Keil workspace. Use the menu Project->Manage->Multi-Project Workspace. Click the New button. Browse to the pe\_demo project for the custom BSP, in this case

\demo\pe\_demo\uv4\pe\_demo\_CustomBSP\pe\_demo\_CustomBSP.uvproj. Click Open. Click OK to save the workspace.

Figure-14 pe\_demo project added to Keil workspace

34. Add PEx header paths. The applications will need two paths added that point to header files located in the PEx Driver Suite installation. These are the same paths added earlier to the BSP. Copy the two paths from the BSP project and add to the **pe\_demo** project in the compiler Include Paths. Click **OK** twice to save.

<PEx Driver Suite Installation>\eclipse\ProcessorExpert\lib\Kinetis\iofiles\ <PEx Driver Suite Installation>\eclipse\ProcessorExpert\lib\Kinetis\pdd\inc\

| Folder Setup                                                                                                                                     |    | ? | ×            |

|--------------------------------------------------------------------------------------------------------------------------------------------------|----|---|--------------|

| Setup Compiler Include Paths:                                                                                                                    | ٣) | × | <del>)</del> |

| C:\Freescale\PExDrv_v10.2\eclipse\ProcessorExpert\lib\Kinetis\iofiles\<br>C:\Freescale\PExDrv_v10.2\eclipse\ProcessorExpert\lib\Kinetis\pdd\inc\ |    |   |              |

| ///lib/CustomBSP.uv4/debug/bsp/Sources<br>///lib/CustomBSP.uv4/debug                                                                             | I  |   |              |

| ///ib/CustomBSP.uv4/debug/psp<br>///ib/CustomBSP.uv4/debug/bsp/Generated_Code                                                                    |    |   |              |

| ///lib/CustomBSP.uv4/debug/bsp                                                                                                                   |    |   |              |

|                                                                                                                                                  |    |   |              |

|                                                                                                                                                  |    |   |              |

|                                                                                                                                                  |    |   |              |

|                                                                                                                                                  |    |   |              |

| OK Cancel                                                                                                                                        |    |   |              |

Figure-15 PEx paths added to pe\_demo in Keil

- 35. Build the **pe\_demo** project. There should be no errors.

- 36. Download and test **pe\_demo** on the board for the original BSP, in this case TWR-K60D100M board.

# 5 Changing MCU derivative in MQX projects

If the device used in the customized BSP is different than the original BSP, the MCU derivative needs to be changed.

# 5.1 Changing the PEx Package

If PEx is used, PEx may be able to change the package instead of the CPU Component. This minimizes the steps in using PEx with the BSP because the original BSP CPU properties are preserved. To change the package, select the CPU Component in the Components View. In the Component Inspector, under the Properties Tab, select the CPU type property. The available packages for that device are shown. If the desired part number is not available, the CPU Component needs to be changed, detailed in the next section.

| Scomponent Inspector - Cpu S | Components Library Basic  | Advanced Expert    |   |

|------------------------------|---------------------------|--------------------|---|

| Properties Methods Events E  | Build options Resources   |                    |   |

| Name                         | Value                     | Details            |   |

| CPU type                     | D10 in MAPBGA 144-pin pac | kage 🔺             |   |

| Clock settings               | MK60DN512VMD10 in MAPB    | GA 144-pin package |   |

| Initialization priority      | MK60DN512VLQ10 in LQFP 1  | 44-pin package     |   |

| Watchdog disable             | MK60DN512VMC10 in MAPB    | GA 121-pin package |   |

| > CPU interrupts/resets      | MK60DN512VLL10 in LQFP 10 | 0-pin package      |   |

| External Bus                 | Disabled                  |                    |   |

| Clock configurations         | 3                         |                    |   |

| •                            | III                       | 1                  | 4 |

#### Figure-16 Changing Package in PEx

# 5.2 Changing the PEx CPU Component

If PEx is used, these steps describe changing the MCU derivative in the MQX BSP. In addition, these documents installed with MQX RTOS have further details about managing the BSP project with PEx.

- How-to Change Default Clock Settings in Kinetis BSPs located in \doc\tools\cw.

- CW for Microcontrollers V10 and MQX<sup>™</sup> RTOS, located in: doc\tools\cw\MQX\_CW10\_Getting\_Started.pdf (Windows menu: Tools Documentation \CodeWarrior\Getting Started CW for Microcontrollers v10.x and MQX).

Unfortunately, this step loses the CPU settings from the original CPU component. Use the original CPU component as a reference.

1. Open the PEx BSP project.

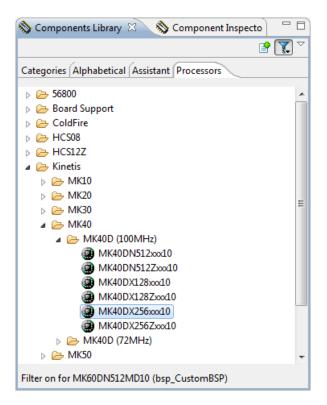

2. Add a new CPU component. In the Component Library View, under the Processors Tab, navigate to the new CPU. In this case, MK40DX256xxx10. Double-click the component to add to the project.

Figure-17 New CPU component in Components Library

- Select the desired package, in this case MK40DX256VMD10 144-pin MAPBGA. The CPU configurations are not important in this project since MQX RTOS doesn't use PEx to generate the linker command files. Click Next.

- 4. Select the desired compiler. Click Finish.

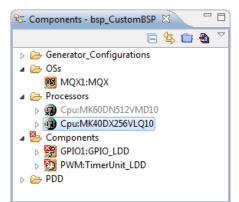

- 5. The new CPU component is added to the project and the old one is still present but disabled. The old component's settings can still be viewed for guidance on setting up the new component.

Figure-18 New CPU Component in BSP project

6. Change the internal peripheral settings. To avoid conflicts with MQX source code, some features setup by PEx should be disabled. In the Component Inspector View, under the

Properties Tab, expand the Internal Peripherals group. Disable the NMI pin and Flash Configuration properties:

| 🔉 *Component Inspector - Cpu 🛛        |               | - 6 |

|---------------------------------------|---------------|-----|

| Basic Ad                              | vanced Expert | Ъ   |

| Properties Methods Events Build optic | ons Resources |     |

| Name                                  | Value         | *   |

|                                       |               |     |

| NMI pin                               | Disabled      |     |

| Reset control                         | Enabled       | -   |

| Debug interface (JTAG)                |               | Ξ   |

| Flash memory organization             |               |     |

| Flexible memory controller            | Disabled      |     |

| Flash configuration field             | Disabled      |     |

| MPU settings                          | Disabled      |     |

| AXBS settings                         | Disabled      |     |

| AIPS0 settings                        | Disabled      |     |

| AIPS1 settings                        | Disabled      |     |

| MCM settings                          | Disabled      |     |

| System control block settings         | Disabled      |     |

| Power management controller           |               |     |

| System Integration Module             |               | -   |

| < III                                 |               |     |

Figure-19 PEx Internal Peripheral Settings

- 7. The existing peripheral components may have errors after the CPU change, caused by changes in pin names and clock frequencies. Clean up the errors, or remove the unnecessary components. In this case, fix the counter frequency of the PWM component if needed, and change the pins used in the GPIO1 component as shown in this list:

- LED1 PTC7

- LED2 PTC8

- LED3 PTC9

- LED4 PTC11

- 8. Generate the PEx code.

# 5.3 Specify MCU derivative in MQX RTOS

MQX RTOS uses macros for the MCU derivative, board specifics, and derivative header files.

- 9. Find driver files dependent on the MCU derivative. User\_config.h uses the macro MQX\_CPU to define the derivative in the BSP. In this case, the derivative is defined as PSP\_CPU\_MK60D100M. The file \mqx\source\psp\cortex\_m\kinetis.h uses this derivative to include the correct header file. In this case, the header file is \mqx\source\psp\cortex\_m\cpu\MK60D10.h. The top of this header file defines an MCU derivative, in this case MCU\_MK60D10. Search the BSP project to find driver files that reference this macro and make a note of these files because they may need to be modified after the derivative is changed (see Section <u>5.4 Modifying Driver Derivative Files</u>). In this case, there is one driver file below that references MCU\_MK60D10: \mqx\source\io\sai\sai\_mk60.c

- 10. Modify MCU derivative in user\_config.h. MQX RTOS already has a list of several supported derivatives in \Freescale\_MQX\_4\_0\mqx\source\psp\cortex\_m\kinetis.h. Find the derivative macro for the customized BSP and update user\_config.h with this derivative. In this case, the line below in user\_config.h is modified for the desired K40:

#define MQX\_CPU

PSP\_CPU\_MK40DX256

11. If the desired derivative is not in the list in **kinetis.h**, it can be added. An example is the device MK20DN512VLK10. A BSP for this derivative can also be cloned from TWR-K60D100M, but the MQX release has no support for this derivative. In this case, the lines below are added to kinetis.h:

#elif (MQX\_CPU == PSP\_CPU\_MK20DN512)

#include "MK20D10.h"

- 12. If the desired derivative header file is missing from the MQX release, add it. Find the desired header file in the toolchain directory listed below. Copy the header file to **\mqx\source\psp\cortex\_m\cpu**.

- <CodeWarrior Installation>\MCU\lib\wizard\_data\ARM\DataBase\derivatives

- IAR: <IAR Installation>\arm\inc\Freescale

- Keil: <Keil Installation>\ARM\INC\Freescale\Kinetis

- 13. Update the PSP batch file if the derivative header file is changed. In this example, modify the batch file found at **\mqx\build\bat\psp\_CustomBSP.bat**:

copy %MQXROOTDIR%\mqx\source\psp\cortex\_m\cpu\MK40D10.h %OUTPUTDIR%\MK40D10.h /Y

14. If the PSP\_CPU\_ macro used in user\_config.h was newly added to kinetis.h, there is one more step to define the new macro. Edit \mqx\source\psp\cortex\_m\psp\_cpudef.h and add a new entry for the new CPU Identification macro, like this:

#define PSP\_CPU\_MK20DN512

(PSP\_CPU\_NUM(PSP\_CPU\_ARCH\_ARM\_CORTEX\_M4, PSP\_CPU\_GROUP\_KINETIS\_K2X, 0xE))

# 5.4 Modifying Driver Derivative Files

- 15. Review the derivative specific driver source files for the desired derivative. If needed, modify the files, or change the BSP project to use a different source file for the desired sub-family. In this case, the source files used in the BSP are changed as follows:

- \mqx\source\io\sai\sai\_mk40.c instead of sai\_mk60.c

# 6 Clock Configuration

In this example, the BSP needs the clock source changed from a 50 MHz oscillator to an 8 MHz crystal. Also, the example changes the PLL output from 96 MHz to 48 MHz, to force a change to the USB clock dividers, and detail these steps.

# 6.1 Changing Clock Configuration with PEx

These steps assume PEx is already included in the BSP project, see Using Processor Expert (PEx) in the BSP.

| 📎 Components Library 🚫 Comp  | onent Inspector - Cpu 🛛 🗌 🗖 |

|------------------------------|-----------------------------|

|                              | Basic Advanced Expert h 🗸   |

| Properties Methods Events Bu | ild options Resources       |

| Name                         | Value                       |

| Component name               | Сри                         |

| CPU type                     | MK40DX256VLQ10              |

| ⊿ Clock settings             | -                           |

| <                            | 4                           |

Figure-20 Expert Mode in Component Inspector

It is recommended to use Expert mode in the Component Inspector to see all property options for the PEx component. To use Expert mode, click the Expert button in the upper right corner of the Component Inspector View.

#### 6.1.1 Configure the Clock Settings

Use the Component Inspector View to configure the CPU component. Expand the Clock Settings properties group.

- 1. Internal Oscillator: these settings generally do not need to be changed. This example leaves them in their default settings.

- 2. RTC Oscillator: If the BSP uses the RTC peripheral with the 32 kHz oscillator, this oscillator needs to be enabled. In this example, the TWR-K40D100M board includes a 32 kHz crystal, and the RTC oscillator is enabled with no load capacitors added.

- System Oscillator 0: this should be enabled and configured if any external clock source is used. In this example, the BSP requires an external clock source for USB. The TWR-K40D100M board uses an 8 MHz crystal. No load capacitors are added and set oscillator operating mode to Low Power.

|                                        | Basic Adva       | nced Expert    | 1 |

|----------------------------------------|------------------|----------------|---|

| roperties Methods Events Build options | Resources        |                |   |

| Name                                   | Value            | Details        | - |

| Clock settings                         |                  |                | h |

| ▲ Internal oscillator                  |                  |                |   |

| Slow internal reference clock [kHz]    | 32.768           | 32.768 kHz     | Ξ |

| Initialize slow trim value             | no               |                |   |

| Fast internal reference clock [MHz]    | 4.0              | 4 MHz          |   |

| Initialize fast trim value             | no               |                |   |

| ⊿ RTC oscillator                       | Enabled          |                |   |

| Clock frequency [MHz]                  | 0.032768         | 0.032768 MHz   |   |

| Capacitor load                         | 0pF              |                |   |

|                                        | Enabled          |                |   |

| ▲ Clock source                         | External crystal |                |   |

| Clock input pin                        |                  |                |   |

| Pin name                               | EXTAL0/PTA18/F   | EXTAL0/PTA18/F |   |

| Pin signal                             |                  |                |   |

| Clock output pin                       |                  |                |   |

| Pin name                               | XTAL0/PTA19/FT   | XTAL0/PTA19/FT |   |

| Pin signal                             |                  |                |   |

| Clock frequency [MHz]                  | 8.0              | 8 MHz          |   |

| Capacitor load                         | 0pF              |                |   |

| Oscillator operating mode              | Low power        |                | Ŧ |

#### Figure-21 PEx Clock Settings

4. Clock Source Settings: the Kinetis BSPs in MQX RTOS are enabled for low-power modes. To enable this, there are generally two Clock Source Settings. The first is for Run mode with the clock frequencies running at their maximum for the BSP. The second is for VLPR mode, running from the internal fast oscillator. In this example, the BSP uses these two Clock Source Settings. Change the number of Clock Source Settings to 2. 5. Clock Source Setting 0: this is the setting for RUN mode. In this example, it uses the 8 MHz crystal. Use the MCG in PEE mode to multiply the PLL Output clock up to 48 MHz.

| Properties | Methods Events Build options R | esources               |                            |

|------------|--------------------------------|------------------------|----------------------------|

| Name       |                                | Value                  | Details                    |

| Clock s    | ettinas                        |                        |                            |

|            | ernal oscillator               |                        |                            |

| P          | oscillator                     | Enabled                |                            |

| P.         | tem oscillator 0               | Enabled                |                            |

| -          | ck source settings             | 2                      |                            |

|            | Clock source setting 0         |                        |                            |

| 4          | Internal reference clock       |                        |                            |

|            | MCGIRCLK clock                 | Disabled               |                            |

|            | MCGIRCLK in stop               | Disabled               |                            |

|            | MCGIRCLK source                | Slow                   |                            |

|            | MCGIRCLK clock [MHz]           | 0.0                    | 0 MHz; IRCLK is not enable |

| 4          | External reference clock       |                        |                            |

|            | OSC0ERCLK clock                | Enabled                |                            |

|            | OSC0ERCLK in stop              | Enabled                |                            |

|            | OSC0ERCLK clock [MHz]          | 8.0                    | 8 MHz                      |

|            | ERCLK32K clock source          | RTC oscillator         | 0.032768 MHz               |

|            | ERCLK32K. clock [kHz]          | 0.032768               | 0.032768 MHz               |

| 4          | MCG settings                   |                        |                            |

|            | MCG mode                       | PEE                    |                            |

|            | MCG output clock               | PLL clock              |                            |

|            | MCG output [MHz]               | 48.0                   | 48 MHz                     |

|            | MCG external ref. clock sour   | ce System oscillator 0 |                            |

|            | MCG external ref. clock [MH    | z] 8.0                 | 8 MHz                      |

|            | Clock monitor                  | Enabled                |                            |

|            | FLL settings                   |                        |                            |

|            | FLL module                     | Disabled               |                            |

|            | FLL output [MHz]               | 0.0                    | 0 MHz; FLL is disabled.    |

|            | MCGFFCLK clock [kHz]           | 15.625                 | 15.625 kHz                 |

|            | ⊿ Reference clock source       | External clock         |                            |

|            | Reference clock divid          |                        | 256                        |

|            | FLL reference clock [kHz]      |                        | 31.25 kHz                  |

|            | Multiplication factor          | Auto select            | 640                        |

|            | PLL 0 settings                 |                        |                            |

|            | PLL module                     | Enabled                |                            |

|            | PLL module in Stop             | Disabled               |                            |

|            | PLL output [MHz]               | 48.0                   | 48 MHz                     |

|            | Reference clock divider        | Auto select            | 4                          |

|            | PLL reference clock [MH        |                        | 2 MHz                      |

|            | Multiplication factor          | Auto select            | 24                         |

|            | Loss of lock interrupt         | Disabled               |                            |

#### Figure-22 PEx Clock Source Setting 0

6. Clock Source Setting 1: this is the setting for the VLPR low-power mode. In this example, it uses the fast internal oscillator in BLPI mode with a 2 MHz output clock from the MCG.

| Properties Methods Events Build options Reso | urces               |                                                    |

|----------------------------------------------|---------------------|----------------------------------------------------|

| lame                                         | Value               | Details                                            |

| Clock settings                               |                     |                                                    |

| Internal oscillator                          |                     |                                                    |

| RTC oscillator                               | Enabled             |                                                    |

| System oscillator 0                          | Enabled             |                                                    |

| Clock source settings                        | 2                   |                                                    |

| Clock source setting 0                       |                     |                                                    |

| ▲ Clock source setting 1                     |                     | Warning: This source clock configuration is not us |

| ▲ Internal reference clock                   |                     |                                                    |

| MCGIRCLK clock                               | Enabled             |                                                    |

| MCGIRCLK in stop                             | Enabled             |                                                    |

| MCGIRCLK source                              | Fast                |                                                    |

| Reference divider                            | 2                   |                                                    |

| MCGIRCLK clock [MHz]                         | 2.0                 | 2 MHz                                              |

| External reference clock                     |                     |                                                    |

| OSC0ERCLK clock                              | Disabled            |                                                    |

| OSC0ERCLK in stop                            | Disabled            |                                                    |

| OSC0ERCLK clock [MHz]                        | 0.0                 | 0 MHz; System oscillator ERCLK is disabled.        |

| ERCLK32K clock source                        | Auto select         | RTC oscillator                                     |

| ERCLK32K. clock [kHz]                        | 0.032768            | 0.032768 MHz                                       |

| ▲ MCG settings                               |                     |                                                    |

| MCG mode                                     | BLPI                |                                                    |

| MCG output clock                             | Internal clock      |                                                    |

| MCG output [MHz]                             | 2.0                 | 2 MHz                                              |

| MCG external ref. clock source               | System oscillator 0 |                                                    |

| MCG external ref. clock [MHz]                | 8.0                 | 8 MHz                                              |

| Clock monitor                                | Disabled            |                                                    |

| ⊿ FLL settings                               |                     |                                                    |

| FLL module                                   | Disabled            |                                                    |

| FLL output [MHz]                             | 0.0                 | 0 MHz; FLL is disabled.                            |

| MCGFFCLK clock [kHz]                         | 16.384              | 16.384 kHz                                         |

| Reference clock source                       | Slow internal clock |                                                    |

| FLL reference clock [kHz]                    | 32.768              | 32.768 kHz                                         |

| Multiplication factor                        | Auto select         | 640                                                |

| ⊿ PLL 0 settings                             |                     |                                                    |

| PLL module                                   | Disabled            |                                                    |

| PLL module in Stop                           | Disabled            |                                                    |

| PLL output [MHz]                             | 0.0                 | 0 MHz; PLL is disabled                             |

| Reference clock divider                      | Auto select         |                                                    |

| PLL reference clock [MHz]                    | 1.0                 | 1 MHz                                              |

| Multiplication factor                        | Auto select         |                                                    |

| Loss of lock interrupt                       | Disabled            |                                                    |

#### Figure-23 PEx Clock Source Setting 1

#### 6.1.2 Clock Configurations

PEx allows for multiple clock configurations to dynamically change the clock settings. The MQX BSP takes advantage of this for low-power optimizations. In this example, the BSP uses 3 Clock Configurations.

7. Set the number of Clock Configurations to 3.

8. Clock Configuration 0: this is the main configuration for RUN mode, setting the Core Clock to 48 MHz, peripheral Bus Clock to 48 MHz, External Bus Clock to 48 MHz, and Flash Clock to 24 MHz using the PLL Clock.

| Properties Methods Events Build option | s Resources      |                             |

|----------------------------------------|------------------|-----------------------------|

| Name                                   | Value            | Details                     |

| Component name                         | Сри              |                             |

| CPU type                               | MK40DX256VLQ10   |                             |

| Clock settings                         |                  |                             |

| Initialization priority                | minimal priority | 15                          |

| Watchdog disable                       | yes              |                             |

| > Internal peripherals                 |                  |                             |

| CPU interrupts/resets                  |                  |                             |

| External Bus                           | Disabled         |                             |

| ⊿ Low power mode settings              |                  |                             |

| Allowed low power modes                |                  |                             |

| LLWU settings                          | Disabled         |                             |

| Operation mode settings                |                  |                             |

| Clock configurations                   | 3                |                             |

| Clock configuration 0                  |                  |                             |

| Very low power mode                    | Disabled         |                             |

| ▲ Clock source setting                 | configuration 0  |                             |

| MCG mode                               | PEE              |                             |

| MCG output [MHz]                       | 48.0             | 48 MHz                      |

| MCGIRCLK clock [MHz]                   | 0                | 0 MHz; IRCLK is not enabled |

| OSCERCLK clock [MHz]                   | 8                | 8 MHz                       |

| ERCLK32K. clock [kHz]                  | 0.032768         | 0.032768 MHz                |

| MCGFFCLK [kHz]                         | 15.625           | 15.625 kHz                  |

| ⊿ System clocks                        |                  |                             |

| Core clock prescaler                   | Auto select      | 1                           |

| Core clock                             | 48.0             | 48 MHz                      |

| Bus clock prescaler                    | Auto select      | 1                           |

| Bus clock                              | 48.0             | 48 MHz                      |

| External clock prescaler               | Auto select      | 1                           |

| External bus clock                     | 48.0             | 48 MHz                      |

| Flash clock prescaler                  | Auto select      | 2                           |

| Flash clock                            | 24.0             | 24 MHz                      |

| ⊿ PLL/FLL clock selection              | PLL clock        |                             |

| Clock frequency [MHz]                  | 48.0             | 48 MHz                      |

Figure-24 PEx Clock Configuration 0

9. Clock Configuration 1: this configuration is used for the MCGAutoTrim method, which requires the Peripheral Bus Clock to be in that range of 8-16 MHz. This configuration uses the PLL Clock, and sets the Core Clock, Peripheral Bus Clock, External Bus Clock, and Flash Clock all to 12 MHz.

| Properties Methods Events Build option | s Resources      |                            |

|----------------------------------------|------------------|----------------------------|

| Name                                   | Value            | Details                    |

| Component name                         | Сри              |                            |

| CPU type                               | MK40DX256VLQ10   |                            |

| Clock settings                         |                  |                            |

| Initialization priority                | minimal priority | 15                         |

| Watchdog disable                       | yes              |                            |

| b Internal peripherals                 |                  |                            |

| CPU interrupts/resets                  |                  |                            |

| External Bus                           | Disabled         |                            |

| Low power mode settings                |                  |                            |

| Allowed low power modes                |                  |                            |

| LLWU settings                          | Disabled         |                            |

| Operation mode settings                |                  |                            |

| Clock configurations                   | 3                |                            |

| Clock configuration 0                  |                  |                            |

| Clock configuration 1                  |                  |                            |

| b Very low power mode                  | Disabled         |                            |

| Clock source setting                   | configuration 0  |                            |

| MCG mode                               | PEE              |                            |

| MCG output [MHz]                       | 48.0             | 48 MHz                     |

| MCGIRCLK clock [MHz]                   | 0                | 0 MHz; IRCLK is not enable |

| OSCERCLK clock [MHz]                   | 8                | 8 MHz                      |

| ERCLK32K. clock [kHz]                  | 0.032768         | 0.032768 MHz               |

| MCGFFCLK [kHz]                         | 15.625           | 15.625 kHz                 |

| ⊿ System clocks                        |                  |                            |

| Core clock prescaler                   | Auto select      | 4                          |

| Core clock                             | 12.0             | 12 MHz                     |

| Bus clock prescaler                    | Auto select      | 4                          |

| Bus clock                              | 12.0             | 12 MHz                     |

| External clock prescaler               | Auto select      | 4                          |

| External bus clock                     | 12.0             | 12 MHz                     |

| Flash clock prescaler                  | Auto select      | 4                          |

| Flash clock                            | 12.0             | 12 MHz                     |

| PLL/FLL clock selection                | PLL clock        |                            |

| Clock frequency [MHz]                  | 48.0             | 48 MHz                     |

Figure-25 PEx Clock Configuration 1