# How to switch to int. OSC when ext.OSC is lost?

Target on S08PA/PT

Moris Hsu | MCU FAE

Jan/2015

#### External Use

## Agenda

- Trouble Shooting

- Test Result

- Conclusion

## **Trouble Shooting**

- Q: How to switch to internal OSC for keeping application execution if the external OSC clock signal is gone?

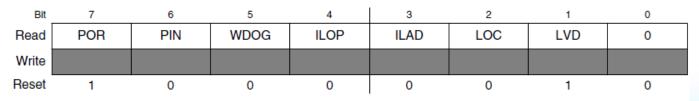

- A: Consider to use external clock monitor to reset MCU but checked the S08PA RM that there is a SYS\_SRS[CLK] error as below:

#### 8.2.3.2 External reference clock monitor

In FBE, FEE, or FBI modes, if ICS\_C4[CME] bit is written to 1, the clock monitor is enabled. If the external reference falls below a certain frequency, such as f<sub>loc\_high</sub> or f<sub>loc\_low</sub> depending on the ICS\_OSCSC[RANGE] bit, the MCU will reset. The SYS\_SRS[CLK] bit will be set to indicate the error.

In FBELP or FBILP modes, the FLL is not on, so the external reference clock monitor will not function even if ICS\_C4[CME] bit is written to 1.

External reference clock monitor uses FLL as the internal reference clock. The FLL must be functional before ICS\_C4[CME] bit is set.

Address: 3000h base + 0h offset = 3000h

SYS\_SRS field descriptions

## **Trouble Shooting**

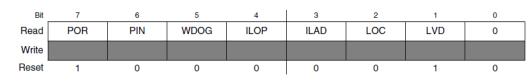

There is a clue in RM to indicate that SYS\_SRS[CLK] bit should be SYS\_SRS[LOC] bit:

Address: 3000h base + 0h offset = 3000h

This device has the following sources for reset:

• Power-on reset (POR)

• Low-voltage detect (LVD)

Watchdog (WDOG) timer

• Illegal opcode detect (ILOP)

SYS SRS field descriptions

LOC

132

Internal Clock Source Module Reset

Reset was caused by an ICS module reset.

Table continues on the next page...

#### MC9S08PA16 Reference Manua

Freescale Semiconductor, Inc.

MC9S08PA16 Reference Manual, Rev. 2, 08/2014

#### System options

- Illegal address detect (ILAD)

- Background debug forced reset

- External reset pin (RESET)

- Internal clock source module reset (CLK)

#### SYS SRS field descriptions (continued)

| Field | Description                     |

|-------|---------------------------------|

|       | Reset not caused by ICS module. |

|       | Reset caused by ICS module.     |

### **Test Result**

- Tested on TWR-S08PT60, ICS\_S[LOLS] may not working including interrupt when we remove ext. OSC in FBE mode.

- Observe that FEE can switch to FEI automatically, but not sure that FBE can auto switch to FBI due to the internal OSC is only 31.25KHz which is far from the 8MHz external OSC.

## Conclusion

- Consult with Freescale product expert that:

- The ICS\_S[LOLS] is not used for this purpose, it is used to determine FLL lock status when switch to one of FLL active clock mode.

- It is a RM error on SYS\_SRS[CLK] bit, it should be SYS\_SRS[LOC] bit.

- If you do not enable CME in external clock mode, you will find it will automatically switch to FEI mode from FEE.

- For FBE, it is not switched to FBI. It is stalling in this mode until external clock is active as system has no clock, after external clock active, program resumes execution.

- For high precision clock requirement application, set ICS\_C4[CME] to reset MCU automatically then check SYS\_SRS[LOC] to see whether it is lost of external clock is a safety way.

www.Freescale.com